# Am9511A

### Arithmetic Processor

### DISTINCTIVE CHARACTERISTICS

- 2, 3 and 4MHz operation; fixed point 16-bit and 32-bit operations

- · Floating point 32-bit operations; binary data formats

- Add, Subtract, Multiply and Divide; trigonometric and inverse trigonometric functions

- Square roots, logarithms, exponentiation; float to fixed and fixed to float conversions

- Stack-oriented operand storage; DMA or programmed I/O data transfers

- End signal simplifies concurrent processing; Synchronous/Asynchronous operations

- General purpose 8-bit data bus interface; standard 24pin package

- +12 volt and +5 volt power supplies; advanced Nchannel silicon gate MOS technology

### **GENERAL DESCRIPTION**

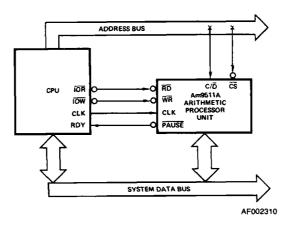

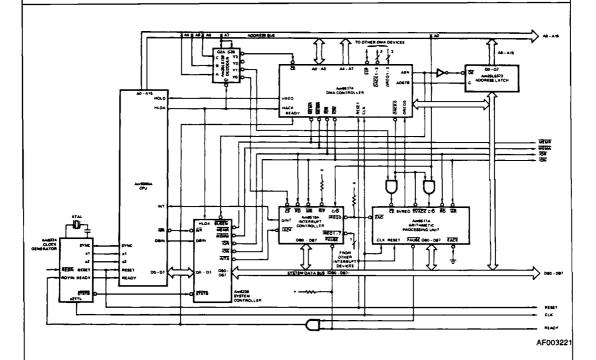

The Am9511A Arithmetic Processing Unit (APU) is a monolithic MOS/LSI device that provides high performance fixed and floating point arithmetic and a variety of floating point trigonometric and mathematical operations. It may be used to enhance the computational capability of a wide variety of processor-oriented systems.

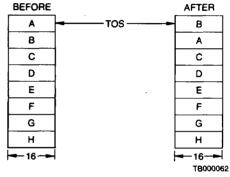

All transfers, including operand, result, status and command information, take place over an 8-bit bidirectional data bus. Operands are pushed onto an internal stack, and a command is issued to perform operations on the data in

the stack. Results are then available to be retrieved from the stack, or additional commands may be entered.

Transfers to and from the APU may be handled by the associated processor using conventional programmed I/O or may be handled by a direct memory access controller for improved performance. Upon completion of each command, the APU issues an end of execution signal that may be used as an interrupt by the CPU to help coordinate program execution.

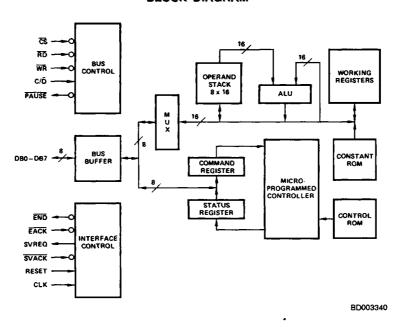

### **BLOCK DIAGRAM**

01892B

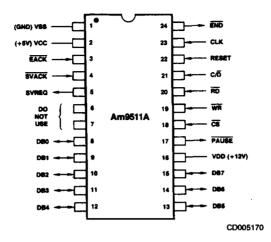

### CONNECTION DIAGRAM Top View D-24-2

Note: Pin 1 is marked for orientation

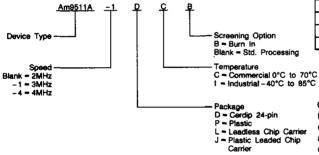

### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Combinations |                   |  |  |  |  |  |  |

|--------------------|-------------------|--|--|--|--|--|--|

| Am9511A            | DC, DCB, DI, DIB, |  |  |  |  |  |  |

| Am9511A-1          | LC, LCB, LI, LIB, |  |  |  |  |  |  |

| Am9511A-4          | /BJA              |  |  |  |  |  |  |

#### Valid Combinations

Consult the local AMD sales office to confirm availability of specific valid combinations, check for newly released valid combinations and/or obtain additional data on AMD's standard military grade product.

### PIN DESCRIPTION

| Pin No. | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1/0 |                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2       | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | +5V Pov                                                     | ver Sup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ply.                   |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 16      | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | + 12V Po                                                    | wer Su                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | pply.                  |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 1       | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | Ground.                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 23      | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I   |                                                             | (Clock). An external timing source connected to the CLK input provides the necessary clocking. The CLK input can be asynchronous to the $\overline{\text{AD}}$ and $\overline{\text{WR}}$ control signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 22      | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   | clears the<br>stack ma<br>reset the<br>the RESE             | Reset). A HIGH on this input causes initialization. Reset terminates any operation in progress and clears the status register to zero. The internal stack pointer is initialized, and the contents of the stack may be affected, but the command register is not affected by the reset operation. After a reset the END output will be HIGH, and the SVREO output will be LOW. For proper initialization, the RESET input must be HIGH for at least five CLK periods following stable power supply voltages and stable clock.                                                                                                                                                                                                                    |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 21      | C/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        | The $C/\overline{D}$ input, with the $\overline{RD}$ and $\overline{WR}$ inputs, determines the type of on the data bus as follows:                                                                                                      |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | C/D                                                         | RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | WR                     | Function                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | L                                                           | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                      | Push data byte into the stack                                                                                                                                                                                                            |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | L                                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Н                      | Pop data byte from the stack                                                                                                                                                                                                             |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | Н                                                           | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                      | Enter command byte from the data bus                                                                                                                                                                                                     |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | Н                                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Н                      | Read Status                                                                                                                                                                                                                              |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | X                                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                      | Undefined                                                                                                                                                                                                                                |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | L = LOW<br>H = HIG<br>X = DOM                               | H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RE                     |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 24      | END                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | complete. read or w output wii up to +5 Reading I read or w | [End of Execution]. A LOW on this output indicates that execution of the current command is complete. This output will be cleared HIGH by activating the <u>EACK</u> input LOW or performing any read or write operation or device initialization using the RESET. If <u>EACK</u> is tied LOW, the <u>END</u> output will be a pulse (see <u>EACK</u> description). This is an open drain output and requires a pull up to +5V.  Reading the status register while a command execution is in progress is allowed. However, any read or write operation clears the flip-flop that generates the <u>END</u> output. Thus, such continuous reading could conflict with internal logic setting the <u>END</u> flip-flop at the completion of command |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 3       | ÉACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ţ   | LOW on<br>derived fr<br>is clocked                          | (End Acknowledge). This input when LOW makes the END output go HIGH. As mentioned earlier, LOW on the END output signals completion of a command execution. The END output signal is derived from an internal flip-flop which is clocked at the completion of a command. This flip-flop is clocked to the reset state when EACK is LOW. Consequently, if the EACK is tied LOW, the END output will be a pulse that is approximately one CLK period wide.                                                                                                                                                                                                                                                                                         |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 5       | SVREQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0   | output is<br>completion<br>This bit in<br>activating        | (Service Request). A HIGH on this output indicates completion of a command. In this sense, this output is same as the END output. However, whether the SVREO output will go HIGH at the completion of a command or not is determined by a service request bit in the command register. This bit must be 1 for SVREO to go HIGH. The SVREO can be cleared (i.e., go LOW) by activating the SVACK input LOW or initializing the device using the RESET. Also, the SVREO will be automatically cleared after completion of any command that has the service request bit as 0.                                                                                                                                                                       |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 4       | SVACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   | the SVRE<br>setting of                                      | Q outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ut. If the             | A LOW on this input activates the reset input of the flip-flop generating<br>SVACK input is permanently fied LOW, it will conflict with the internal<br>generate the SVREQ output. Thus the SVREQ indication cannot be<br>K is tied LOW. |  |  |  |  |  |  |

| 8-15    | DB0-D87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1/0 | operand i                                                   | nformatie most                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | tion betw<br>significa | These eight bidirectional lines are used to transfer command, status and veen the device and the host processor. D80 is the least significant, and ant bit position. HIGH on the data bus line corresponds to 1, and LOW                 |  |  |  |  |  |  |

|         | on the stack using the data bus, the least significant byte must be gnificant byte last. When popping the stack to read the result of an ficant byte will be available on the data bus first, and the least significant reover, for pushing operands and popping results, the number of ual to the proper number of bytes appropriate for the chosen format, yte pointer will not be aligned properly. The Am9511A single precision double precision and floating-point formats require 4 bytes. |     |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |

### PIN DESCRIPTION (Cont.)

| Pin No. | Name  | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | CS    | '   | (Chip Select). This input must be LOW to accomplish any read or write operation to the Am9511A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

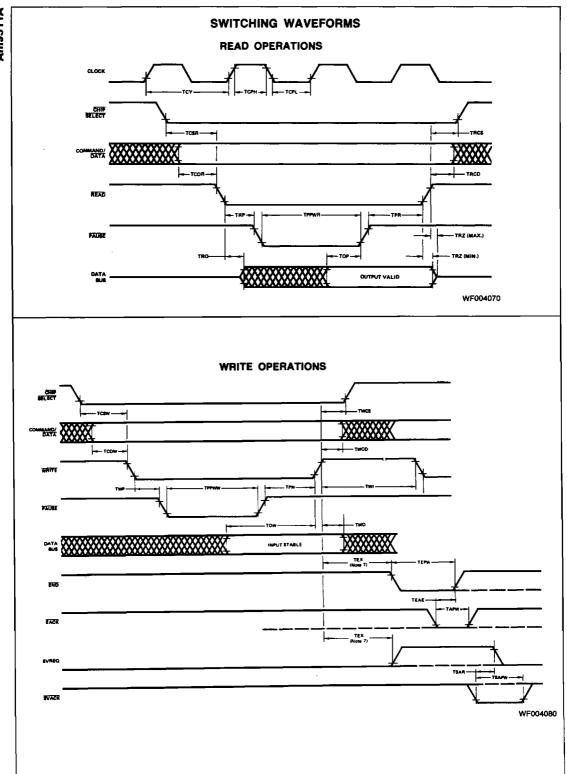

|         |       |     | To perform a write operation, data is presented on DB0 through DB7 lines, C/D is driven to an appropriate level and the CS input is made LOW. However, actual writing into the Am9511A cannot start until WR is made LOW. After initiating the write operation by a WR HIGH-to-LOW transition, the PAUSE output will go LOW momentarily (TPPWW).                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |       |     | The WR input can go HIGH after PAUSE goes HIGH. The data lines, C/D input and the CS input can change when appropriate hold time requirements are satisfied. See Write Timing diagram for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |       |     | To perform a read operation, an appropriate logic level is established on the C/D input, and CS is made LOW. The read operation does not start until the RD input goes LOW. PAUSE will go LOW for a period of TPPWR. When PAUSE goes back HIGH again, it indicates that the read operation is complete, and the required information is available on the DB0 through DB7 lines. This information will remain on the data lines as long as the RD input is LOW. The RD input can return HIGH anytime after PAUSE goes HIGH. The CS input and C/D inputs can change anytime after RD returns HIGH. See Read Timing diagram for details.                                                                                                                                                         |

| 20      | ŘĎ    | l   | (Read). A LOW on this input is used to read information from an internal location and gate that information on to the data bus. The CS input must be LOW to accomplish the read operation. The C/D input determines what internal location is of interest. See C/D, CS input descriptions and Read Timing diagram for details. If the END output was LOW, performing any read operation will make the END output go HIGH after the HIGH-to-LOW transition of the RO input (assuming CS is LOW).                                                                                                                                                                                                                                                                                               |

| 19      | WA    | ·   | (Write). A LOW on this input is used to transfer information from the data bus into an internal location. The $\overline{CS}$ must be LOW to accomplish the write operation. The $C/\overline{D}$ determines which internal location is to be written. See $C/\overline{D}$ , $\overline{CS}$ input descriptions and Write Timing diagram for details.  If the $\overline{END}$ output was LOW, performing any write operation will make the $\overline{END}$ output go HIGH after the LOW-to-HIGH transition of the $\overline{WR}$ input (assuming $\overline{CS}$ is LOW).                                                                                                                                                                                                                 |

| 17      | PAUSE | 0   | (Pause). This output is a handshake signal used while performing read or write transactions with the Am9511A. A LOW at this output indicates that the Am9511A has not yet completed its information transfer with the host over the data bus. During a read operation, after CS went LOW, the PAUSE will become LOW shortly (TRP) after RD goes LOW. PAUSE will return high only after the data bus contains valid output data. The CS and RD should remain LOW when PAUSE is LOW. The RD may go high anytime after PAUSE goes HIGH. During a write operation, after CS went LOW, the PAUSE will be LOW for a very short duration (TPPWN) after WR goes LOW. Since the minimum of TPPWW is 0, the PAUSE may not go LOW at all for fast devices. WR may go HIGH anytime after PAUSE goes HIGH. |

### **DETAILED DESCRIPTION**

Major functional units of the Am9511A are shown in the block diagram. The Am9511A employs a microprogram controlled stack oriented architecture with 16-bit wide data paths.

The Arithmetic Logic Unit (ALU) receives one of its operands from the Operand Stack. This stack is an 8-word by 16-bit 2-port memory with last in-first out (LIFO) attributes. The second operand to the ALU is supplied by the internal 16-bit bus. In addition to supplying the second operand, this bidirectional bus also carries the results from the output of the ALU when required. Writing into the Operand Stack takes place from this internal 16-bit bus when required. Also connected to this bus are the Constant ROM and Working Registers. The ROM provides the required constants to perform the mathematical operations (Chebyshev Algorithms), while the Working Registers provide storage for the intermediate values during command execution.

Communication between the external world and the Am9511A takes place on eight bidirectional input/output lines DB0 through DB7 (Data Bus). These signals are gated to the internal eight-bit bus through appropriate interface and buffer circuitry. Multiplexing facilities exist for bidirectional communication between the internal eight- and sixteen-bit buses. The Status Register and Command Register are also accessible via the eight-bit bus.

The Am9511A operations are controlled by the microprogram contained in the Control ROM. The Program Counter supplies the microprogram addresses and can be partially loaded from the Command Register. Associated with the Program Counter is the Subroutine Stack where return addresses are held during subroutine calls in the microprogram. The Microinstruction Register holds the current microinstruction being execut-

ed. This register facilitates pipelined microprogram execution. The Instruction Decode logic generates various internal control signals needed for the Am9511A operation.

The Interface Control logic receives several external inputs and provides handshake related outputs to facilitate interfacing the Am9511A to microprocessors.

### **Command Format**

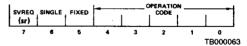

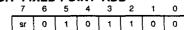

Each command entered into the Am9511A consists of a single 8-bit byte having the format illustrated below:

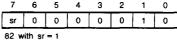

Bits 0 - 4 select the operation to be performed as shown in the table. Bits 5 - 6 select the data format for the operation. If bit 5 is a 1, a fixed point data format is specified. If bit 5 is a 0, floating point format is specified. Bit 6 selects the precision of the data to be operated on by fixed point commands (if bit 5 = 0, bit 6 must be 0). If bit 6 is a 1, single-precision (16-bit) operands are indicated; if bit 6 is a 0, double-precision (32-bit) operands are indicated. Results are undefined for all illegal combinations of bits in the command byte. Bit 7 indicates whether a service request is to be issued after the command is executed. If bit 7 is a 1, the service request output (SVREQ) will go HIGH at the conclusion of the command and will remain HIGH until reset by a LOW level on the service acknowledge pin (SVACK) or until completion of execution of a succeeding command where bit 7 is 0. Each command issued to the Am9511A requests post execution service based upon the state of bit 7 in the command byte. When bit 7 is a 0, SVREQ remains LOW.

|          |       |     |          |          |     |          |          |              | COMMAND SUMMARY                                                                                                              |

|----------|-------|-----|----------|----------|-----|----------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------|

|          | (     | Com | mar      | nd C     | ode |          |          | Command      | Command Description                                                                                                          |

| 7        | 6     | 5   | 4        | 3        | 2   | 1        | 0        | Mnemonic     |                                                                                                                              |

|          |       |     |          |          |     |          |          |              | FIXED-POINT 16-BIT                                                                                                           |

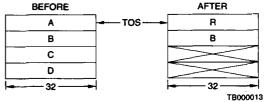

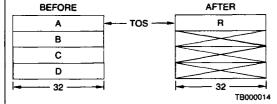

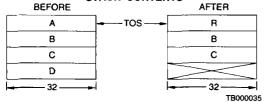

| ST       | 1     | 1   | 0        | 1        | 1   | 0        | 0        | SADD         | Add TOS to NOS. Result to NOS. Pop Stack.                                                                                    |

| sr       | 1     | 1   | 0        | 1        | 1   | 0        | 1 0      | SSUB<br>SMUL | Subtract TOS from NOS. Result to NOS. Pop Stack.  Multiply NOS by TOS. Lower half of result to NOS. Pop Stack.               |

| Sr<br>Sr | i     | ;   | 1        | å        | H   | ;        | 0        | SMUU         | Multiply NOS by TOS. Lower half of result to NOS. Pop Stack.  Multiply NOS by TOS. Upper half of result to NOS. Pop Stack.   |

| sr       | 1     | 1   | ó        | 1        | j , | i        | Ĭ,       | SDIV         | Divide NOS by TOS. Result to NOS. Pop Stack.                                                                                 |

|          |       |     |          |          |     |          |          |              | FIXED-POINT 32-BIT                                                                                                           |

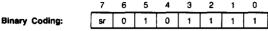

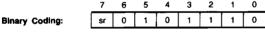

| sr       | 0     | 1   | 0        | 1        | 1   | 0        | 0        | DADD         | Add TOS to NOS. Result to NOS. Pop Stack.                                                                                    |

| sr       | 0     | 1 1 | 0        | 1 1      | 1   | 0        | 1 1      | DSUB         | Subtract TOS from NOS. Result to NOS. Pop Stack.                                                                             |

| sr<br>sr | 0     | 1   | 0        | 0        | 1 1 | 1        | 0        | DMUL<br>DMUU | Multiply NOS by TOS. Lower half of result to NOS. Pop Stack.  Multiply NOS by TOS. Upper half of result to NOS. Pop Stack.   |

| St       | 0     | 1   | ò        | 1        | 1   | Ιi       | 1        | DDIV         | Divide NOS by TOS. Result to NOS. Pop Stack.                                                                                 |

|          |       |     |          |          |     |          |          |              | FLOATING-POINT 32-BIT                                                                                                        |

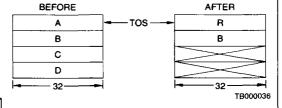

| sr       | 0     | 0   | 1        | 0        | 0   | 0        | 0        | FADD         | Add TOS to NOS. Result to NOS. Pop Stack.                                                                                    |

| sr       | 0     | 0   | 1        | 0        | 0   | 0        | 1        | FSUB         | Subtract TOS from NOS. Result to NOS. Pop Stack.                                                                             |

| sr       | 0 0   | 0   | 1        | 0        | 0   | 1        | 0        | FMUL<br>FDIV | Multiply NOS by TOS. Result to NOS. Pop Stack.                                                                               |

| sr       | 0     |     | <u> </u> | <u> </u> | 10  | <u>'</u> | <u>'</u> |              | Divide NOS by TOS. Result to NOS. Pop Stack.  ED FLOATING-POINT FUNCTIONS                                                    |

|          | _     | -   | _        | ٦,       | ١.  |          |          |              |                                                                                                                              |

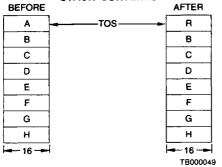

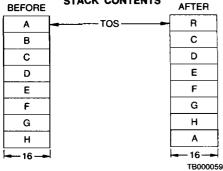

| sr<br>sr | 0     | 0   | 0        | 0        | 0   | 0        | 1 0      | SQRT<br>SIN  | Square Root of TOS. Result in TOS. Sine of TOS. Result in TOS.                                                               |

| sr       | ŏ     | ۱ŏ  | ŏ        | lő       | ۱ŏ  | i        | l ĭ l    | cos          | Cosine of TOS. Result in TOS.                                                                                                |

| sr       | 0     | 0   | ō        | o        | 1   | 0        | 0        | TAN          | Tangent of TOS. Result in TOS.                                                                                               |

| sr       | 0     | 0   | 0        | 0        | 1   | 0        | 1        | ASIN         | Inverse Sine of TOS. Result in TOS.                                                                                          |

| Sf       | 0     | 0   | 0        | 0        | 1   | 1        | 1        | ACOS<br>ATAN | Inverse Cosine of TOS. Result in TOS. Inverse Tangent of TOS, Result in TOS.                                                 |

| sr<br>sr | ŏ     | lő  | 0        | 1        | ló  | ľó       | ò        | LOG          | Common Logarithm (base 10) of TOS. Result in TOS.                                                                            |

| sr       | ŏ     | ۱ŏ  | ō        | 1        | ١ŏ  | ŏ        | Ĭĭ       | LN           | Natural Logarithm (base e) of TOS. Result in TOS.                                                                            |

| sr       | 0     | Ó   | 0        | 1        | 0   | 1        | 0        | EXP          | Exponential (ex) of TOS. Result in TOS.                                                                                      |

| Sr       | 0     | 0   | 0        | 1        | 0   | 1        | 1        | PWR          | NOS raised to the power in TOS. Result in NOS. Pop Stack.                                                                    |

|          |       |     |          |          |     |          |          |              | A MANIPULATION COMMANDS                                                                                                      |

| sr       | 0     | 0   | 0        | 0        | 0   | 0        | 0        | NOP<br>FIXS  | No Operation.                                                                                                                |

| sr<br>sr | 0     | 0   | 1        | 1 1      | 1   | 1        | 0        | FIXD         | Convert TOS from floating-point to 16-bit fixed-point format.  Convert TOS from floating-point to 32-bit fixed-point format. |

| Sr       | ŏ     | lŏ  | i        | Ιi       | Ιi  | Ιċ       | ĭ        | FLTS         | Convert TOS from 16-bit fixed-point to floating-point format.                                                                |

| sr       | ō     | ō   | 1        | 1        | 1   | o        | 0        | FLTD         | Convert TOS from 32-bit fixed-point to floating-point format.                                                                |

| Sr       | ] 1 ] | 1   | 1        | 0        | 1   | 0        | 0        | CHSS         | Change sign of 16-bit fixed-point operand on TOS.                                                                            |

| şr       | 0     | 1   | 1        | 0        | 1 1 | 0        | 0        | CHSD         | Change sign of 32-bit fixed-point operand on TOS.                                                                            |

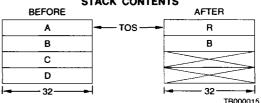

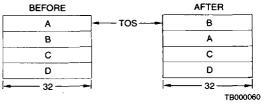

| St       | 0 1   | 0   | 1        | 0        | 1   | 0        | 1        | CHSF<br>PTOS | Change sign of floating-point operand on TOS.  Push 16-bit fixed-point operand on TOS to NOS. (Copy.)                        |

| sr<br>sr | o.    | l i | 1        | lő       | Ιi  | Ι'n      |          | PTOD         | Push 32-bit fixed-point operand on TOS to NOS. (Copy.)                                                                       |

| sr       | ŏ     | ò   | l i      | ŏ        | 1   | 1        | 1        | PTOF         | Push floating-point operand on TOS to NOS. (Copy.)                                                                           |

| sr       | 1     | 1   | 1        | 1        | 0   | 0        | 0        | POPS         | Pop 16-bit fixed-point operand from TOS. NOS becomes TOS.                                                                    |

| sr       | 0     | 1   | 1        | 1        | 0   | 0        | 0        | POPD         | Pop 32-bit fixed-point operand from TOS. NOS becomes TOS.                                                                    |

| SF       | 0     | 0   | 1        | 1        | 0   | 0        | 0        | POPF<br>XCHS | Pop floating-point operand from TOS. NOS becomes TOS, Exchange 16-bit fixed-point operands TOS and NOS.                      |

| S/<br>S/ | 1 0   | 1   | 1        | 1        | 0   | ١٥       | ] ;      | XCHS         | Exchange 18-bit fixed-point operands 105 and NOS.  Exchange 32-bit fixed-point operands TOS and NOS.                         |

| sr       | lő    | o   | i        | 1        | ŏ   | ŏ        | ] i      | XCHF         | Exchange floating-point operands TOS and NOS.                                                                                |

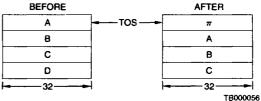

| sr       | ō     | ŏ   | 1        | l i      | ō   | 1        | 0        | PUPI         | Push floating-point constant "π" onto TOS. Previous TOS becomes NOS.                                                         |

- Notes: 1. TOS means Top of Stack. NOS means Next on Stack.

2. AMD Application Brief "Algorithm Details for the Am9511A APU" provides detailed descriptions of each command function, including data ranges, accuracies, stack configurations, etc.

- 3. Many commands destroy one stack location (bottom of stack) during development of the result. The derived functions may destroy several stack locations. See Application Brief for details.

- 4. The trigonometric functions handle angles in radians, not degrees.

- 5. No remainder is available for the fixed-point divide functions.

- 6. Results will be undefined for any combination of command coding bits not specified in this table.

### Command Initiation

After properly positioning the required operands on the stack, a command may be issued. The procedure for initiating a command execution is as follows:

- 1. Enter the appropriate command on the DB0 DB7 lines.

- 2. Establish HIGH on the C/D input.

- 3. Establish LOW on the CS input.

- 4. Establish LOW on the WR input after an appropriate set-up time (see Timing diagrams).

- 5. Sometime after the HIGH-to-LOW level transition of WR input, the PAUSE output will become LOW. After a delay of TPPWW, it will go HIGH to acknowledge the write operation. The WR input can return to HIGH anytime after PAUSE going HIGH. The DB0 - DB7, C/D and CS inputs are allowed to change after the

hold time requirements are satisfied (see Timing diagram).

An attempt to issue a new command while the current command execution is in progress is allowed. Under these circumstances, the PAUSE output will not go HIGH until the current command execution is completed.

#### Operand Entry

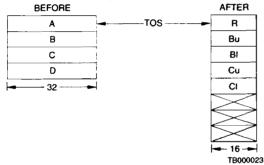

The Am9511A commands operate on the operands located at the TOS and NOS, and results are returned to the stack at NOS and then popped to TOS. The operands required for the Am9511A are one of three formats - single precision fixedpoint (2 bytes), double precision fixed-point (4 bytes) or floating-point (4 bytes). The result of an operation has the same format as the operands except for float to fix or fix to float commands.

Operands are always entered into the stack least significant byte first and most significant byte last. The following procedure must be followed to enter operands onto the stack:

- The lower significant operand byte is established on the DB0 - DB7 lines.

- A LOW is established on the C/D input to specify that data is to be entered into the stack.

- 3. The CS input is made LOW.

- After appropriate set-up time (see Timing diagrams), the WR input is made LOW. The PAUSE output will become LOW.

- Sometime after this event, the PAUSE will return HIGH to indicate that the write operation has been acknowledged.

- Anytime after the PAUSE output goes HIGH, the WR

input can be made HIGH. The DB0 DB7, C/D and

CS inputs can change after appropriate hold time requirements are satisfied (see Timing diagrams).

The above procedure must be repeated until all bytes of the operand are pushed onto the stack. It should be noted that for single precision fixed-point operands, 2 bytes should be pushed and 4 bytes must be pushed for double precision fixed-point or floating-point. Not pushing all the bytes of a quantity will result in byte pointer misalignment.

The Am9511A stack can accommodate 8 single precision fixed-point quantities or 4 double precision fixed-point or floating-point quantities. Pushing more quantities than the capacity of the stack will result in loss of data which is usual with any LIFO stack.

### **Data Removal**

Result from an operation will be available at the TOS. Results can be transferred from the stack to the data bus by reading the stack. When the stack is popped for results, the most significant byte is available first and the least significant byte last. A result is always of the same precision as the operands that produced it except for format conversion commands. Thus when the result is taken from the stack, the total number of bytes popped out should agree with the precision — single precision results are 2 bytes, and double precision and floating-point results are 4 bytes. The following procedure must be used for reading the result from the stack:

- A LOW is established on the C/D input.

- 2. The CS input is made LOW.

- After appropriate set-up time (see Timing diagrams), the RD input is made LOW. The PAUSE will become LOW.

- Sometime after this, PAUSE will return HIGH, indicating that the data is available on the DB0 - DB7 lines. This data will remain on the DB0 - DB7 lines as long as the RD input remains LOW.

- Anytime after PAUSE goes HIGH, the RD input can return HIGH to complete transaction.

- The CS and C/D inputs can change after appropriate hold time requirements are satisfied (see Timing diagram).

- Repeat this procedure until all bytes appropriate for the precision of the result are popped out.

Reading of the stack does not alter its data; it only adjusts the byte pointer. If more data is popped than the capacity of the stack, the internal byte pointer will wrap around and older data will be read again, consistent with the LIFO stack.

#### Status Read

The Am9511A status register can be read without any regard to whether a command is in progress or not. The only implication that has to be considered is the effect this might have on the END output discussed in the signal descriptions.

The following procedure must be followed to accomplish status register reading:

- 1. Establish HIGH on the C/D input.

- 2. Establish LOW on the CS input.

- After appropriate set-up time (see Timing diagram) RD input is made LOW. The PAUSE will become LOW.

- Sometime after the HIGH-to-LOW transition of RD input, the PAUSE will become HIGH, indicating that status register contents are available on the DB0 – DB7 lines. The status data will remain on DB0 – DB7 as long as RD input is LOW.

- The RD input can be returned HIGH anytime after PAUSE goes HIGH.

- The C/D input and CS input can change after satisfying appropriate hold time requirements (see Timing diagram).

#### **Data Formats**

The Am9511A Arithmetic Processing Unit handles operands in both fixed-point and floating-point formats. Fixed-point operands may be represented in either single (16-bit operands) or double precision (32-bit operands), and are always represented as binary, two's complement values.

#### 16-BIT FIXED-POINT FORMAT

TB00064M

### 32-BIT FIXED-POINT FORMAT

TB00065M

The sign (positive or negative) of the operand is located in the most significant bit (MSB). Positive values are represented by a sign bit of zero (S = 0). Negative values are represented by the two's complement of the corresponding positive value with a sign bit equal to 1 (S = 1). The range of values that may be accommodated by each of these formats is -32,767 to +32,767 for single precision and -2,147,483,647 for double precision.

Floating point binary values are represented in a format that permits arithmetic to be performed in a fashion analogous to operations with decimal values expressed in scientific notation.

$$(5.83 \times 10^2)(8.16 \times 10^1) = (4.75728 \times 10^4)$$

In the decimal system, data may be expressed as values between 0 and 10 times 10 raised to a power that effectively shifts the implied decimal point right or left the number of places necessary to express the result in conventional form (e.g., 47,572.8). The value-portion of the data is called the mantissa. The exponent may be either negative or positive.

The concept of floating point notation has both a gain and a loss associated with it. The gain is the ability to represent the significant digits of data with values spanning a large dynamic range limited only by the capacity of the exponent field. For

example, in decimal notation if the exponent field is two digits wide and the mantissa is five digits, a range of values (positive or negative) from 1.000 x  $10^{-99}$  to 9.9999 x  $10^{+99}$  can be accommodated. The loss is that only the significant digits of the value can be represented. Thus there is no distinction in this representation between the values 123451 and 123452, for example, since each would be expressed as: 1.2345 x  $10^5$ . The sixth digit has been discarded. In most applications where the dynamic range of values to be represented is large, the loss of significance, and hence accuracy of results, is a minor consideration. For greater precision a fixed point format could be chosen, although with a loss of potential dynamic range.

The Am9511 is a binary arithmetic processor and requires that floating point data be represented by a fractional mantissa value between .5 and 1 multiplied by 2 raised to an appropriate power. This is expressed as follows:

For example, the value 100.5 expressed in this form is  $0.11001001 \times 2^7$ . The decimal equivalent of this value may be computed by summing the components (powers of two) of the mantissa and then multiplying by the exponent as shown below:

value =

$$(2^{-1} + 2^{-2} + 2^{-5} + 2^{-8}) \times 2^7$$

=  $(0.5 + 0.25 + 0.03125 + 0.00290625) \times 128$

=  $0.78515625 \times 128$

= 100.5

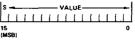

#### Floating Point Format

The format for floating-point values in the Am9511A is given below. The mantissa is expressed as a 24-bit (fractional) value; the exponent is expressed as an unbiased two's complement 7-bit value having a range of −64 to +63. The most significant bit is the sign of the mantissa (0 = positive, 1 = negative), for a total of 32 bits. The binary point is assumed to be to the left of the most significant mantissa bit (bit 23). All floating-point data values must be normalized. Bit 23 must be equal to 1, except for the value zero, which is represented by all zeros.

The range of values that can be represented in this format is  $\pm (2.7 \times 10^{-20} \text{ to } 9.2 \times 10^{18})$  and zero.

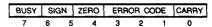

#### Status Register

The Am9511A contains an eight bit status register with the following bit assignments:

BUSY: Indicates that Am9511A is currently executing a command (1 = Busy).

SIGN: Indicates that the value on the top of stack is negative (1 = Negative).

ZERO: Indicates that the value on the top of stack is zero (1 = Value is zero).

#### ERROR

CODE: This field contains an indication of the validity of the result of the last operation. The error codes are:

> 0000 - No error 1000 - Divide by error

0100 - Square root or log of negative number

1100 - Argument of inverse sine, cosine, or e<sup>X</sup> too large

XX10 - Underflow XX01 - Overflow

CARRY: Previous operation resulted in carry or borrow from most significant bit (1 = Carry/Borrow, 0 = No Carry/No Borrow).

If the BUSY bit in the status register is a one, the other status bits are not defined; if zero, indicating not busy, the operation is complete, and the other status bits are defined as given above.

| Command<br>Mnemonic | Hex Code<br>(sr = 1) | Hex Code<br>(sr = 0) | Execution<br>Cycles | Summary                                                                |

|---------------------|----------------------|----------------------|---------------------|------------------------------------------------------------------------|

| MINERIONIC          | (8) - 1)             | (ar – v)             |                     | Description VED POINT OPERATIONS                                       |

| SADD                | EC                   | 6C                   | 16-18               | XED-POINT OPERATIONS                                                   |

| SSUB                | ED                   | 6D                   | 30-32               | Add TOS to NOS. Result to NOS. Pop Stack.                              |

| SMUL                | EE                   | 6E                   | 84-94               | Subtract TOS from NOS. Result to NOS. Pop Stack.                       |

| SMUU                | F6                   | 76                   | 80-98               | Multiply NOS by TOS. Lower result to NOS. Pop Stack.                   |

| SDIV                | EF                   | 6F                   | 84-94               | Multiply NOS by TOS. Upper result to NOS. Pop Stack.                   |

| SDIV                | EF                   | QF                   |                     | Divide NOS by TOS. Result to NOS. Pop Stack.  XED-POINT OPERATIONS     |

| DADD                | AC                   | 2C                   | 20-22               | Add TOS to NOS. Result to NOS. Pop Stack.                              |

| DSUB                | AD                   | 2D                   | 38-40               | Subtract TOS from NOS. Result to NOS. Pop Stack.                       |

| DMUL                | AE                   | 2E                   | 194-210             | Multiply NOS by TOS. Lower result to NOS. Pop Stack.                   |

| DMUU                | B6                   | 36                   | 182-218             | Multiply NOS by TOS. Upper result to NOS. Pop Stack.                   |

| DDIV                | AF                   | 2F                   | 196-210             | Divide NOS by TOS. Result to NOS. Pop Stack.                           |

| 0011                |                      |                      |                     | 3-POINT PRIMARY OPERATIONS                                             |

| FADD                | 90                   | 10                   | 54-368              | Add TOS to NOS. Result to NOS. Pop Stack.                              |

| FSUB                | 91                   | 11                   | 70-370              | Subtract TOS from NOS. Result to NOS. Pop Stack.                       |

| FMUL                | 92                   | 12                   | 146-168             | Multiply NOS by TOS. Result to NOS. Pop Stack.                         |

| FDIV                | 93                   | 13                   | 154-184             | Divide NOS by TOS. Result to NOS. Pop Stack.                           |

| 1014                |                      | Ļ                    |                     | G-POINT DERIVED OPERATIONS                                             |

| SQRT                | 81                   | 01                   | 782-870             | Square Root of TOS. Result to TOS.                                     |

| SIN                 | 82                   | 02                   | 3796-4808           | Sine of TOS. Result to TOS.                                            |

| cos                 | 83                   | 03                   | 3840-4878           | Cosine of TOS. Result to TOS.                                          |

| TAN                 | 84                   | 04                   | 4894-5886           | Tangent of TOS. Result to TOS.                                         |

| ASIN                | 85                   | 05                   | 6230-7938           | Inverse Sine of TOS. Result to TOS.                                    |

| ACOS                | 86                   | 06                   | 6304-8284           | Increase Cosine of TOS. Result to TOS.                                 |

| ATAN                | 87                   | 07                   | 4992-6536           | Inverse Tangent of TOS. Result to TOS.                                 |

| ŁOG                 | 88                   | 08                   | 4474-7132           | Common Logarithm of TOS. Result to TOS                                 |

| LN                  | 89                   | 09                   | 4296-6956           | Natural Logarithm of TOS. Result to TOS.                               |

| EXP                 | ВА                   | 0A                   | 3794-4878           | e raised to power in TOS. Result to TOS.                               |

| PWR                 | 88                   | ОВ                   | 8290-12032          | NOS raised to power in TOS. Result to NOS. Pop Stack.                  |

|                     |                      | DAT                  |                     | K MANIPULATION OPERATIONS                                              |

| NOP                 | 80                   | 00                   | 4                   | No Operation. Clear or set SVREQ.                                      |

| FIXS                | 9F                   | 1F                   | 90-214              |                                                                        |

| FIXD                | 9€                   | 1E                   | 90-336              | Convert TOS from floating-point format to fixed-point format.          |

| FLTS                | 9D                   | 1D                   | 62-156              |                                                                        |

| FLTD                | 9C                   | 1C                   | 56-342              | Convert TOS from fixed-point format to floating-point format.          |

| CHSS                | F4                   | 74                   | 22-24               |                                                                        |

| CHSD                | B4                   | 34                   | 26-28               | Change sign of fixed-point operand on TOS.                             |

| CHSF                | 95                   | 15                   | 16-20               | Change sign of floating-point operandon TOS.                           |

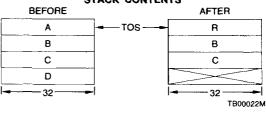

| PTOS                | F7                   | 77                   | 16                  |                                                                        |

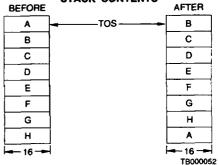

| PTOD                | 87                   | 37                   | 20                  | Push stack. Duplicate NOS in TOS.                                      |

| PTOF                | 97                   | 17                   | 20 J                |                                                                        |

| POPS                | F8                   | 78                   | 10                  |                                                                        |

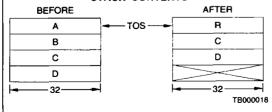

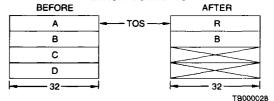

| POPD                | 88                   | 38                   | 12                  | Pop stack. Old NOS becomes new TOS. Old TOS rotates to bottom.         |

| POPF                | 98                   | 18                   | 12                  |                                                                        |

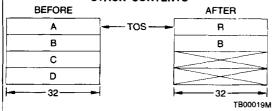

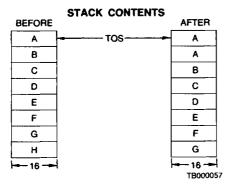

| XCHS                | F9                   | 79                   | 18                  |                                                                        |

| XCHD                | 89                   | 39                   | 26                  | Exchange TOS and NOS.                                                  |

| XCHF                | 99                   | 19                   | 26                  |                                                                        |

| PUPI                | 9A                   | 1A                   | 16                  | Push floating-point constant $\pi$ onto TOS. Previous TOS becomes NOS. |

#### COMMAND DESCRIPTIONS

This section contains detailed descriptions of the APU commands. They are arranged in alphabetical order by command mnemonic. In the descriptions, TOS means Top Of Stack, and NOS means Next On Stack.

All derived functions except Square Root use Chebyshev polynomial approximating algorithms. This approach is used to help minimize the internal microprogram, to minimize the maximum error values and to provide a relatively even distribution of errors over the data range. The basic arithmetic operations are used by the derived functions to compute the various Chebyshev terms. The basic operations may produce error codes in the status register as a result.

Execution times are listed in terms of clock cycles and may be converted into time values by multiplying by the clock period used. For example, an execution time of 44 clock cycles when running at a 3MHz rate translates to 14 microseconds

$(44 \times 32\mu s = 14\mu s)$ . Variations in execution cycles reflect the data dependency of the algorithms.

In some operations exponent overflow or underflow may be possible. When this occurs, the exponent returned in the result will be 128 greater or smaller than its true value.

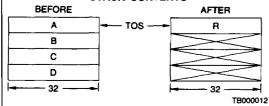

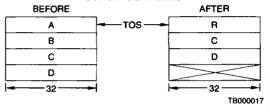

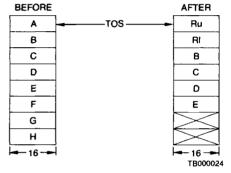

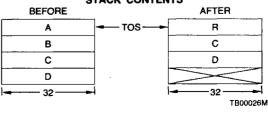

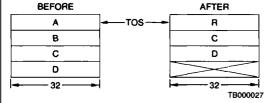

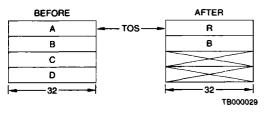

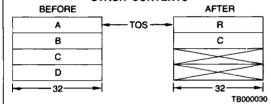

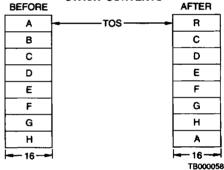

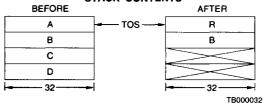

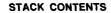

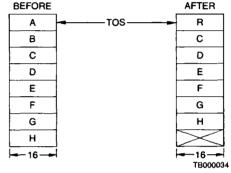

Many of the functions use portions of the data stack as scratch storage during development of the results. Thus, previous values in those stack locations will be lost. Scratch locations destroyed are listed in the command descriptions and shown with the crossed-out locations in the Stack Contents After diagram.

Table 1 is a summary of all the Am9511A commands. It shows the hex codes for each command, the mnemonic abbreviation, a brief description and the execution time in clock cycles. The commands are grouped by functional classes.

The command mnemonics in alphabetical order are shown below in Table 2.

Table 2.

Command Mnemonics in Alphabetical Order.

| ACOS | ARCCOSINE                       | LOG  | COMMON LOGARITHM           |

|------|---------------------------------|------|----------------------------|

| ASIN | ARCSINE                         | LN   | NATURAL LOGARITHM          |

| ATAN | ARCTANGENT                      | NOP  | NO OPERATION               |

| CHSD | CHANGE SIGN DOUBLE              | POPD | POP STACK DOUBLE           |

| CHSF | CHANGE SIGN FLOATING            | POPF | POP STACK FLOATING         |

| CHSS | CHANGE SIGN SINGLE              | POPS | POP STACK SINGLE           |

| cos  | COSINE                          | PTOD | PUSH STACK DOUBLE          |

| DADD | DOUBLE ADD                      | PTOF | PUSH STACK FLOATING        |

| DDIV | DOUBLE DIVIDE                   | PTOS | PUSH STACK SINGLE          |

| DMUL | DOUBLE MULTIPLY LOWER           | PUPI | PUSH $\pi$                 |

| DMUU | DOUBLE MULTIPLY UPPER           | PWR  | POWER (X <sup>Y</sup> )    |

| DSUB | DOUBLE SUBTRACT                 | SADD | SINGLE ADD                 |

| EXP  | EXPONENTATION (e <sup>x</sup> ) | SDIV | SINGLE DIVIDE              |

| FADD | FLOATING ADD                    | SIN  | SINE                       |

| FDIV | FLOATING DIVIDE                 | SMUL | SINGLE MULTIPLY LOWER      |

| FIXD | FIX DOUBLE                      | SMUU | SINGLE MULTIPLY UPPER      |

| FIXS | FIX SINGLE                      | SQRT | SQUARE ROOT                |

| FLTD | FLOAT DOUBLE                    | SSUB | SINGLE SUBTRACT            |

| FLTS | FLOAT SINGLE                    | TAN  | TANGENT                    |

| FMUL | FLOATING MULTIPLY               | XCHD | EXCHANGE OPERANDS DOUBLE   |