Wired Communications

Edition 2001-02-20

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# SICOFI<sup>®</sup>2-µC Two Channel Codec Filter with PCM and Microcontroller Interface

PEB 2266 Version 2.2

PEF 2266 Version 2.2

Wired Communications

#### **PEB 2266**

| Revision History:                                 |  | Current Version 2001-02-20                                                                | DS 1 |

|---------------------------------------------------|--|-------------------------------------------------------------------------------------------|------|

| Previous Version:                                 |  | Data Sheet 07.97 DS1 (V 1.1) Delta Sheet 11.98 DS2 (V 1.4) Errata Sheet 05.98 DS1 (V 1.4) |      |

| Page Subjects (major changes since last revision) |  |                                                                                           |      |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com/

ABM<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ARCOFI<sup>®</sup>-BA, ARCOFI<sup>®</sup>-SP, DigiTape<sup>®</sup>, EPIC<sup>®</sup>-1, EPIC<sup>®</sup>-S, ELIC<sup>®</sup>, FALC<sup>®</sup>54, FALC<sup>®</sup>56, FALC<sup>®</sup>-E1, FALC<sup>®</sup>-LH, IDEC<sup>®</sup>, IOM<sup>®</sup>, IOM<sup>®</sup>-1, IOM<sup>®</sup>-2, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>-P, ISAC<sup>®</sup>-S, ISAC<sup>®</sup>-S TE, ISAC<sup>®</sup>-P TE, ITAC<sup>®</sup>, IWE<sup>®</sup>, MUSAC<sup>®</sup>-A, OCTAT<sup>®</sup>-P, QUAT<sup>®</sup>-S, SICAT<sup>®</sup>, SICOFI<sup>®</sup>, SICOFI<sup>®</sup>-2, SICOFI<sup>®</sup>-4, SICOFI<sup>®</sup>-4μC, SLICOFI<sup>®</sup> are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

| Table of                                                                                                                    | f Contents                                                                                                                                                                                                                                                                                                                                                | Page |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                             | Preface                                                                                                                                                                                                                                                                                                                                                   | 1    |

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                               | OverviewFeaturesLogic SymbolTypical Applications                                                                                                                                                                                                                                                                                                          |      |

| <b>2</b><br>2.1<br>2.2                                                                                                      | Pin Descriptions                                                                                                                                                                                                                                                                                                                                          | 6    |

| <b>3</b><br>3.1<br>3.1.1<br>3.1.2<br>3.2                                                                                    | Functional Description Functional Blocks Fixed Blocks Programmable Blocks Other Functions                                                                                                                                                                                                                                                                 |      |

| <b>4</b><br>4.1<br>4.2                                                                                                      | Operational Description                                                                                                                                                                                                                                                                                                                                   |      |

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.4.1<br>5.4.2<br>5.4.3 | Interface Description Analog Interface PCM Interface PCM Clock Speeds Transmit and Receive Slopes Transmitter Driving Mode PCM Frame Delay Time Slot Assignment Signaling Interface Signaling Pins and Registers Debouncing Functions Interrupt Handling Clock Output Signals Serial Microcontroller Interface Write Access Read Access Three-Wire Access |      |

| 6<br>6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2                                                                                  | Programming the SICOFI®2-μC  Programming Overview                                                                                                                                                                                                                                                                                                         |      |

| Table c | of Contents                                              | Page |

|---------|----------------------------------------------------------|------|

| 6.3     | Channel-Specific Configuration Registers (SOP Command)   |      |

| 6.3.1   | CR0 Configuration Register 0                             |      |

| 6.3.2   | CR1 Configuration Register 1                             |      |

| 6.3.3   | CR2 Configuration Register 2                             |      |

| 6.3.4   | CR3 Configuration Register 3                             |      |

| 6.3.5   | CR4 Configuration Register 4                             |      |

| 6.3.6   | CR5 Configuration Register 5                             |      |

| 6.4     | Common Configuration Registers (XOP Command)             |      |

| 6.4.1   | XR0 Extended Register 0                                  |      |

| 6.4.2   | XR1 Extended Register 1                                  |      |

| 6.4.3   | XR2 Extended Register 2                                  |      |

| 6.4.4   | XR3 Extended Register 3                                  | 45   |

| 6.4.5   | XR4 Extended Register 4                                  |      |

| 6.4.6   | XR5 Extended Register 5                                  | 47   |

| 6.4.7   | XR6 Extended Register 6                                  | 48   |

| 6.4.8   | XR7 Extended Register 7                                  | 49   |

| 6.5     | Coefficients for the Programmable Filters (COP Commands) | 49   |

| 6.5.1   | Programming the General Filter Coefficients              | 50   |

| 6.5.2   | Programming the Channel-Specific Filter Coefficients     | 50   |

| 6.6     | Command Summary                                          | 51   |

| 6.7     | Command Examples                                         | 52   |

| 7       | Application Hints                                        | 56   |

| 7.1     | Support Tools                                            | 56   |

| 7.1.1   | QSICOS Software                                          | 56   |

| 7.1.2   | EASY 2466 Tool Package                                   | 59   |

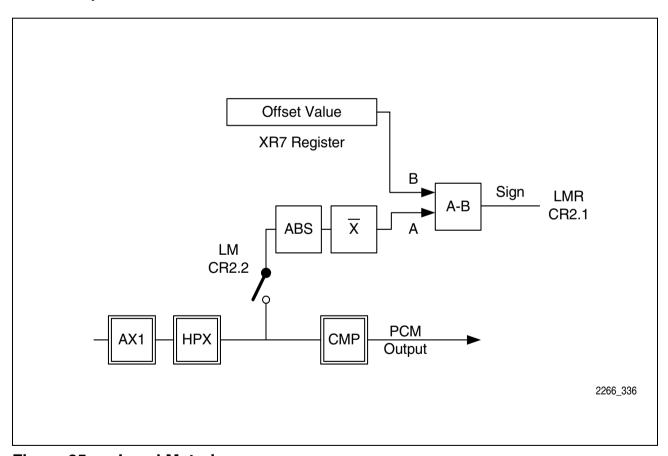

| 7.2     | Level Metering Function                                  | 60   |

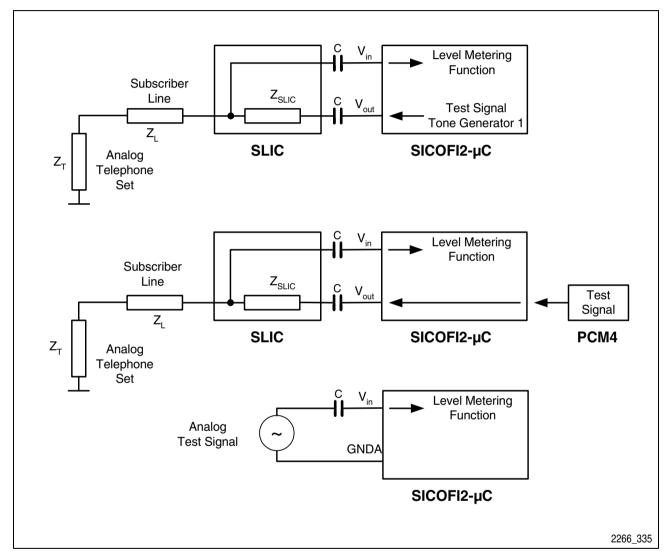

| 7.3     | Programming the SICOFI®2-µC Tone Generators              | 61   |

| 8       | Test Modes                                               | 63   |

| 8.1     | Analog Loops                                             | 63   |

| 8.2     | Digital Loops                                            | 64   |

| 8.3     | Cut-Off's                                                |      |

| 9       | Glossary                                                 | 66   |

|         | Index                                                    | 67   |

| List of Figu | res                                                           | Page |

|--------------|---------------------------------------------------------------|------|

| Figure 1     | Programmable Two Channel Codec Filter                         | 2    |

| Figure 2     | SICOFI®2-µC Logic Symbol                                      | 4    |

| Figure 3     | Pin Configuration of SICOFI®2-μC                              | 6    |

| Figure 4     | SICOFI®2-µC Detailed Flow Diagram                             |      |

| Figure 5     | SICOFI®2-µC State Diagram                                     | 16   |

| Figure 6     | PCM Offset Programming with Bits in XR6.2 to XR6.0            | 22   |

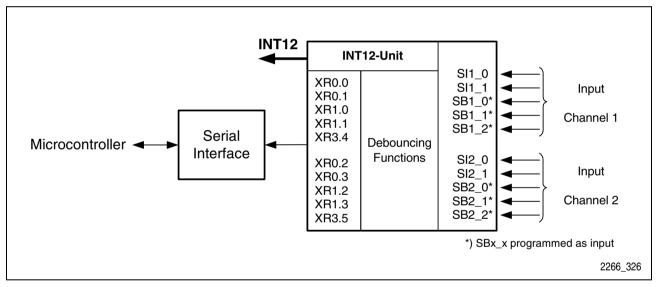

| Figure 7     | Signaling Example for two Subscriber Lines                    | 25   |

| Figure 8     | Access to the Signaling Inputs and Outputs Through XR0        | 26   |

| Figure 9     | Bi-directional Pin Configuration and Access via XR1, XR2, XR3 | 26   |

| Figure 10    | Signal Debouncing, Interrupt Generation and Register Updates  | 27   |

| Figure 11    | Interrupt Handling                                            | 28   |

| Figure 12    | Serial Microcontroller Interface                              | 30   |

| Figure 13    | Example for a Two-Byte Write Access                           | 31   |

| Figure 14    | Example for a One-Byte Read Access                            | 31   |

| Figure 15    | Example for a Read Access, with Byte-by-Byte Transfer         | 32   |

| Figure 16    | Bi-Directional Data Signal with DIN and DOUT Strapped Togethe | r32  |

| Figure 17    | Channel Specific and Common Coefficients                      | 36   |

| Figure 18    | Storage of Coefficients in CRAM                               | 50   |

| Figure 19    | QSICOS Output Example (TEST.SUC)                              | 55   |

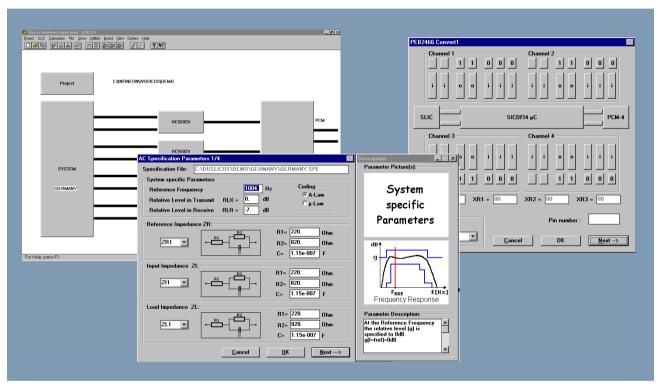

| Figure 20    | Dialogs of the QSICOS Coefficients Software                   | 56   |

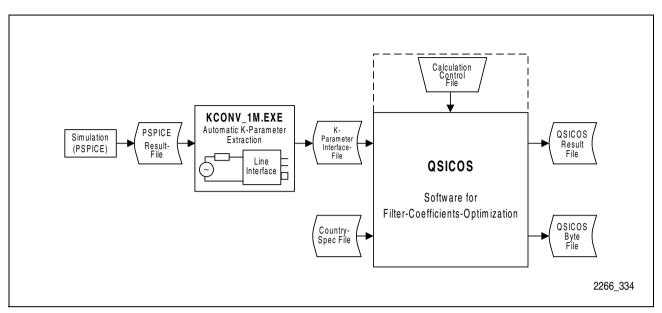

| Figure 21    | Input Files of QSICOS                                         | 57   |

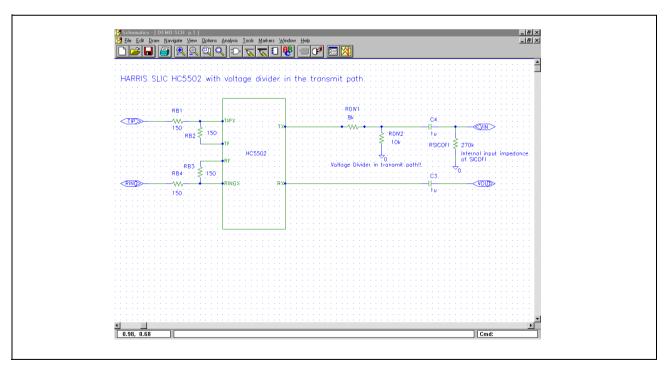

| Figure 22    | PSpice Schematic Editor                                       | 57   |

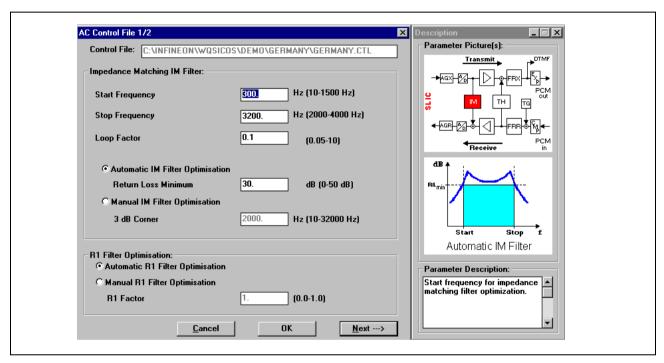

| Figure 23    | Parameter Settings of the Control File                        | 58   |

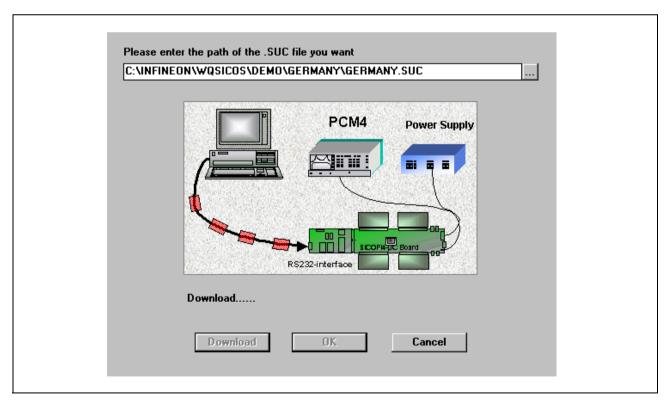

| Figure 24    | Dialog for Programming the Evaluation Board                   | 59   |

| Figure 25    | Level Metering                                                | 60   |

| Figure 26    | Level Metering with different Test Signal Sources             | 61   |

| Figure 27    | Analog Loops                                                  | 63   |

| Figure 28    | Digital loops                                                 | 64   |

| Figure 29    | Cut Off's                                                     | 65   |

| List of Tab | oles                                                           | Page  |

|-------------|----------------------------------------------------------------|-------|

| Table 1     | Pin Definitions and Functions                                  | 7     |

| Table 2     | Default Settings during Reset State                            | 17    |

| Table 3     | Configurable PCM Features and Functions                        | 19    |

| Table 4     | PCM Clocking and Data Rates                                    |       |

| Table 5     | Typical PCM Data Rates, Time Slots, and Clock Modes            | 20    |

| Table 6     | Transmitting and Receiving Bit 7 in Time Slot 0                | 21    |

| Table 7     | Transmitter Driving Modes                                      | 22    |

| Table 8     | PCM Offset in Single Clock Mode                                | 23    |

| Table 9     | PCM Offset in Double Clock Mode                                | 23    |

| Table 10    | CHCLK1 Programming                                             | 29    |

| Table 11    | CHCLK2 Programming                                             | 29    |

| Table 12    | Serial Microcontroller Interface Pins and Functions            | 30    |

| Table 13    | Register Model                                                 | 33    |

| Table 14    | Read Access to Common Configuration Register (XR) Map          | 34    |

| Table 15    | Write Access to Common Configuration Register (XR) Map         | 34    |

| Table 16    | Channel-Specific Configuration Register (CR) Map (Read & Write | e) 34 |

| Table 17    | Coefficient RAM (CRAM) Structure per Channel                   | 35    |

| Table 18    | Coefficient RAM (CRAM) Structure per Set                       | 35    |

| Table 19    | Types of Commands and Data Bytes                               | 36    |

| Table 20    | Signal Debouncing                                              | 46    |

| Table 21    | Configuration of CHCLK1                                        | 46    |

| Table 22    | All Possible Command Sequences                                 | 51    |

| Table 23    | Sample Tone Generators and Bandpass Filters Byte Sequences.    | 62    |

#### **Preface**

This document provides detailed programming information about the SICOFI®2-µC. It is intended for software engineers and those system designers who need detailed information on programming and configuring the device. All content applies to both the standard PEB 2266 and the extended temperature version, PEF 2266, unless specified.

#### **Organization of this Document**

This *Programmer's Reference Manual* is organized as follows:

- Chapter 1, Overview

Includes a general description, feature list, logic symbol, and typical applications.

- Chapter 2, Pin Descriptions

Illustrates the Pin Configuration and provides detailed descriptions of the pins and their associated symbols and functions.

- Chapter 3, Functional Description

Provides a detailed flow diagram, identifies the major functional blocks, and provides details on each of the programmable filter blocks.

- Chapter 4, Operational Description

Includes a state diagram and description of the operating states of all two channels and a brief summary of transmission characteristics.

- Chapter 5, Interface Descriptions

Discusses the Analog, PCM, Signaling, and Microcontroller Interfaces and interrupts.

- Chapter 6, Programming the SICOFI<sup>®</sup>2-μC

Illustrates the memory structure, provides a register model and summary, and describes the command sequences and registers in detail.

- Chapter 7, Application Hints

Indicates the support tools available for the PEB 2266 and includes a detailed discussion of the QSICOS Coefficient Calculation and Register Configuration Software.

- Chapter 8,Test Configuration

Describes the various on-chip test features and illustrates a proposed test circuit.

- The Appendix Includes a glossary and an index.

#### **Related Documentation**

Additional documentation for the PEB 2266 includes a *Product Brief*, a *Product Overview*, a *Hardware Reference Manual*, and assorted *Application Notes*.

Documentation is also available for other SICOFI codec devices including the PEB 2466, PSB 2132, and PSB 2134. Documentation is available by accessing our website: http://www.infineon.com/sicofi

Overview

#### 1 Overview

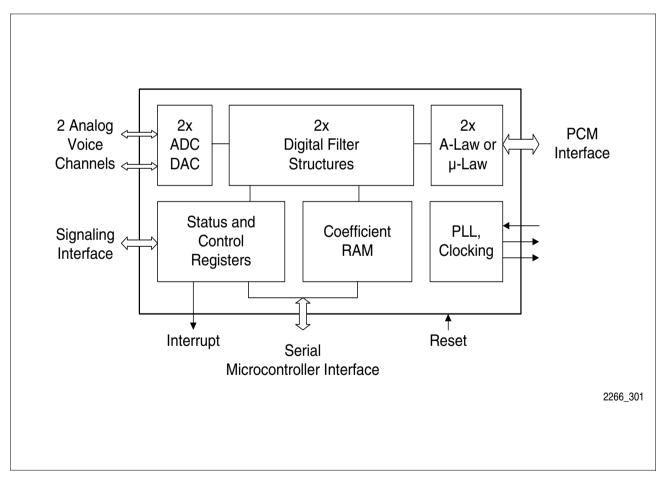

The SICOFI®2-µC is a programmable DSP-based two-channel codec filter device to fulfill worldwide voice telephony standards. An easy to use serial microcontroller interface provides access to 288 bytes of Coefficient RAM (CRAM) and to 32 registers. The values stored in the CRAM determine the filter characteristics of the embedded DSP. Writing to the registers allows control of features such as mode settings, enabling and disabling of filters, tone generators, and test loops, PCM data rates, and signaling and clock output control. Reading from the registers provides status information about the signaling inputs and level metering results.

This document provides detailed information on filter coefficient programming, register configuration settings, and the programming interface. The PEB 2266 is available for standard temperature range applications (0 °C to +70 °C); the PEF 2266 is available for extended temperature range applications (-40 °C to +85 °C).

Figure 1 Programmable Two Channel Codec Filter

# Two Channel Codec Filter with PCM and Microcontroller Interface SICOFI®2-µC

PEB 2266 PEF 2266

Version 2.2 CMOS

#### 1.1 Features

- Two-channel single chip codec and filter fulfills the ITU-T Q.552, G.712, and all country-specific requirements

- High analog driving capability (300  $\Omega$ , 50 pF) for direct driving of transformers

- Digital Signal Processing (DSP) technique

- Programmable digital filters to adapt transmission behavior, especially for:

- AC impedance matching

- Transhybrid balancing

- Frequency response

- Gain

- A/μ-Law compression and expansion

- High performance ADC and DAC for excellent linearity and dynamic gain

- Programmable Analog Interface to electronic SLICs or transformer solutions

- Seven SLIC-signaling I/O pins per channel with programmable debouncing

- Two PCM Highways accessible by on-chip PCM Interface

- Programmable time slot assignment and variable data rates from 128 kbit/s to 8 Mbit/s

- Easy to use 4-pin Serial Microcontroller Interface for (SPI compatible) read/write access

- Single supply voltage (5 V)

- Advanced low-power mixed-signal CMOS technology

- Two programmable tone generators per channel (DTMF possible)

- Level metering function for system tests and for analog input signal testing

- · Advanced on-chip functions for device and system diagnostics and manufacturing test

- Five digital loops

- Four analog loops

- Support tools include:

- Hardware development board STUT 2466

- QSICOS Coefficient Calculation and Register Configuration Software

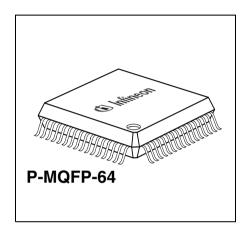

- Standard P-MQFP-64 package

| Туре                 | Package   |

|----------------------|-----------|

| PEB 2266 Version 2.2 | P-MQFP-64 |

| PEF 2266 Version 2.2 | P-MQFP-64 |

Overview

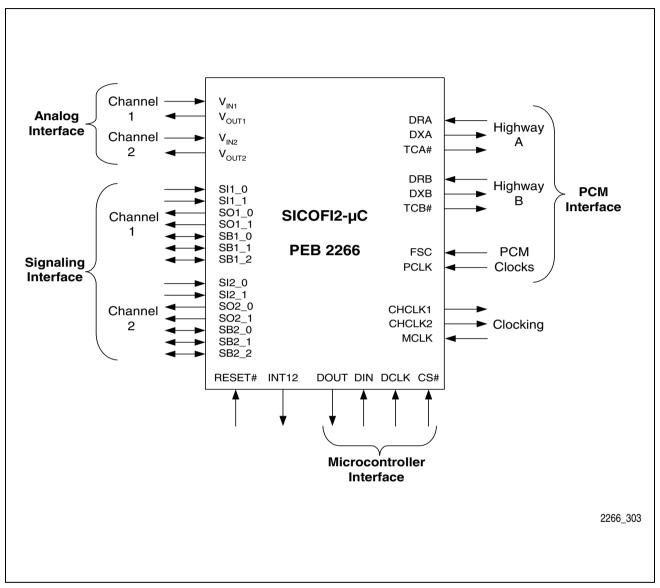

# 1.2 Logic Symbol

Figure 2 SICOFI®2-μC Logic Symbol

**Overview**

# 1.3 Typical Applications

Many applications will benefit from the versatility of the SICOFI®2-µC codec and filter. The inherent flexibility enables several products to be developed around one basic architecture, thus affording potentially significant savings in time to market, inventory costs, and support administration.

The following list represents some of the typical applications for which the SICOFI<sup>®</sup>2-μC codec was designed: Analog linecards for Central Offices and PBXs, Small PBX or Key Systems, Digital Loop Carrier (DLC) Systems, Digital Added Main Lines (DAML) Systems, Fiber-to-the-Curb (FTTC) Systems, Radio-in-the-Loop (RITL) Systems, and any multichannel, digital voice processing, storage, or communication applications.Refer to the *Product Overview*, **Chapter 5 Application Hints** for more information.

# 2 Pin Descriptions

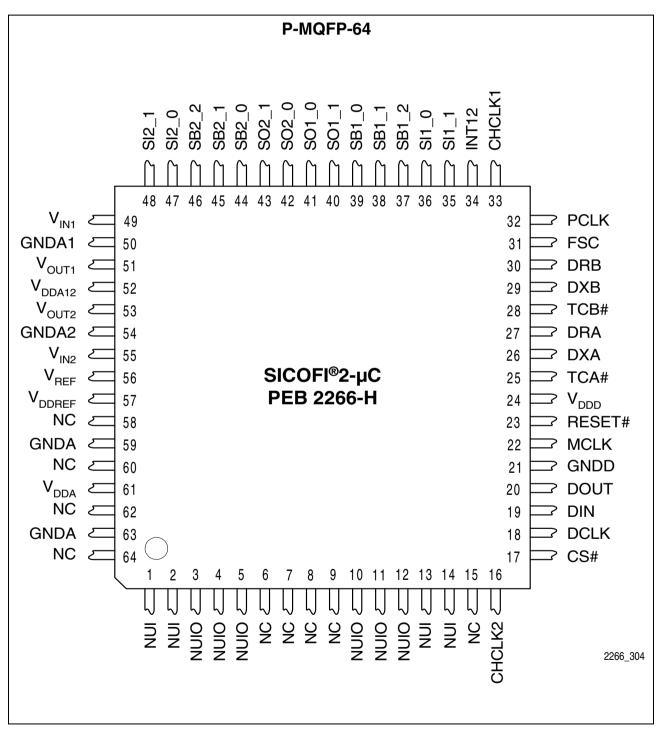

#### 2.1 Pin Diagram

(top view)

Figure 3 Pin Configuration of SICOFI<sup>®</sup>2-μC

# 2.2 Pin Definitions and Functions

Table 1 Pin Definitions and Functions

| Pin              | Symbol | Туре | Function                                                                                                                                                             | Ch.  |

|------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1, 2             | NUI    | I    | Non Usable Input Pins must be tied directly to digital ground (Pin 21).                                                                                              |      |

| 3,4,             | NUIO   | I/O  | Non Usable Input/Output Pins must be tied via a pull-down resistor to digital ground (Pin 21).                                                                       |      |

| 6,7,<br>8, 9     | NC     |      | Not Connected Pins are not connected in this device.                                                                                                                 |      |

| 10,<br>11,<br>12 | NUIO   | I/O  | Non Usable Input/Output Pins must be tied via a pull-down resistor to digital ground (Pin 21).                                                                       |      |

| 13,<br>14        | NUI    | I    | Non Usable Input Pins must be tied directly to digital ground (Pin 21).                                                                                              |      |

| 15               | NC     |      | Not Connected Pin is not connected in this device.                                                                                                                   |      |

| 16               | CHCLK2 | 0    | Chopper Clock Output 2 Provides 256, 512, or 16,384 kHz signal; sync. to MCLK. Configured with Register Bits XR5.2 and XR5.3.                                        | both |

| 17               | CS#    | I    | Chip Select Microcontroller Interface chip select, enable to read or write; active low.                                                                              |      |

| 18               | DCLK   | I    | Data Clock Microcontroller Interface data clock, shifts data from or to device; maximum clock rate 8192 kHz.                                                         |      |

| 19               | DIN    | I    | Data Input Microcontroller Interface control data input pin; DCLK determines data rate.                                                                              | both |

| 20               | DOUT   | 0    | Data Output Microcontroller Interface control data output pin; DCLK determines data rate: DOUT is high impedance "Z" if no data is transmitted from the SICOFI®2-µC. |      |

| 21               | GNDD   | I    | <b>Digital Ground</b> Ground reference for all digital signals. Internally isolated from GNDA1 (Pin50), GNDA2 (Pin 54), and GNDA (Pins 59 and 63).                   | both |

| Pin | Symbol    | Туре | Function                                                                                                                                                                                    | Ch.  |

|-----|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 22  | MCLK      | I    | Master Clock Input<br>1536, 2048, 4096 or 8192 kHz signal must be applied for<br>any operation (select frequency in Register Bits XR5.6<br>and XR5.7). MCLK, PCLK, FSC must be synchronous. | both |

| 23  | RESET#    | I    | Reset Input Forces the device into default setting mode; active low.                                                                                                                        | both |

| 24  | $V_{DDD}$ | I    | Digital Supply Voltage<br>+5 V supply for digital circuits (use 100 nF blocking cap.).                                                                                                      | both |

| 25  | TCA#      | 0    | Transmit Control Output A PCM Interface: active if data is transmitted via DXA; active low, open drain.                                                                                     | both |

| 26  | DXA       | 0    | Data Transmit to PCM-Highway A PCM Interface: PCM data for each channel is transmitted in 8-bit bursts every 125 µs.                                                                        | both |

| 27  | DRA       | I    | Data Receive from PCM-Highway A PCM Interface: PCM data for each channel is received in 3-bit bursts every 125 µs.                                                                          |      |

| 28  | TCB#      | 0    | Transmit Control Output B PCM Interface: active if data is transmitted via DXB; active low, open drain.                                                                                     |      |

| 29  | DXB       | 0    | Data Transmit to PCM-highway B PCM Interface: data for each channel is transmitted in 8-bit bursts every 125 µs.                                                                            |      |

| 30  | DRB       | I    | Data Receive from PCM-highway B PCM Interface: data for each channel is received in 8-bit bursts every 125 µs.                                                                              |      |

| 31  | FSC       | I    | Frame Synchronization Clock 8 kHz; reference for individual time slots, indicates start of PCM frame; MCLK, PCLK, FSC must be synchronous.                                                  | both |

| 32  | PCLK      | I    | PCM Data Clock 128 to 8192 kHz; determines the rate at which PCM data is shifted into or out of the PCM-ports. MCLK, PCLK, FSC must be synchronous.                                         |      |

| 33  | CHCLK1    | 0    | Chopper Clock Output 1 Configurable output clock (T = 2 28 ms), sync. to MCLK. Programmed in Register Bits XR4.0 to XR4.3.                                                                  | both |

| Pin | Symbol | Туре | Function                                                                                                     | Ch.  |

|-----|--------|------|--------------------------------------------------------------------------------------------------------------|------|

| 34  | INT12  | 0    | Interrupt Output, Channels 1 and 2 Active high.                                                              | both |

| 35  | SI1_1  | I    | Signaling Input Channel 1, Pin 1 Read logic status from Register Bit XR0.1.                                  | 1    |

| 36  | SI1_0  | I    | Signaling Input Channel 1, Pin 0 Read logic status from Register Bit XR0.0.                                  | 1    |

| 37  | SB1_2  | I/O  | <b>Bi-directional Signaling, Channel 1 Pin 2</b> Set direction in XR3.0, read/write value from/to Bit XR3.4. | 1    |

| 38  | SB1_1  | I/O  | Bi-directional Signaling, Channel 1 Pin 1 Set direction in XR2.1, read/write value from/to Bit XR1.1.        | 1    |

| 39  | SB1_0  | I/O  | Bi-directional Signaling, Channel 1 Pin 0 Set direction in XR2.0, read/write value from/to Bit XR1.0.        | 1    |

| 40  | SO1_1  | 0    | Signaling Output, Channel 1, Pin 1 Write output value to Register Bit XR0.1.                                 | 1    |

| 41  | SO1_0  | 0    | gnaling Output, Channel 1, Pin 0 rite output value to Register Bit XR0.0.                                    |      |

| 42  | SO2_0  | 0    | Signaling Output, Channel 2, Pin 0 Write output value to Register Bit XR0.2.                                 | 2    |

| 43  | SO2_1  | 0    | Signaling Output, Channel 2, Pin 1 Write output value to Register Bit XR0.3.                                 | 2    |

| 44  | SB2_0  | I/O  | Bi-directional Signaling, Channel 2 Pin 0 Set direction in XR2.2, read/write value from/to Bit XR1.2.        | 2    |

| 45  | SB2_1  | I/O  | <b>Bi-directional Signaling, Channel 2 Pin 1</b> Set direction in XR2.3, read/write value from/to Bit XR1.3. | 2    |

| 46  | SB2_2  | I/O  | <b>Bi-directional Signaling, Channel 2 Pin 2</b> Set direction in XR3.1, read/write value from/to Bit XR3.5. | 2    |

| 47  | SI2_0  | I    | Signaling Input, Channel 2, Pin 0 Read logic status from Register Bit XR0.2.                                 | 2    |

| 48  | SI2_1  | I    | Signaling Input, Channel 2, Pin 1 Read logic status from Register Bit XR0.3.                                 | 2    |

| Pin | Symbol      | Туре | Function                                                                                                                                       | Ch. |

|-----|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 49  | $V_{IN1}$   | I    | Analog Voice (Voltage) Input, Channel 1 Requires a coupling capacitor >39 nF to the SLIC.                                                      | 1   |

| 50  | GNDA1       | I    | Analog Ground, Channel 1 Not internally connected to GNDD, GNDA2, or GNDA.                                                                     | 1   |

| 51  | $V_{OUT1}$  | 0    | Analog Voice (Voltage) Output, Channel 1 Requires a coupling capacitor to the SLIC. The capacitor value depends on the SLIC's input impedance. | 1   |

| 52  | $V_{DDA12}$ | I    | Analog Supply Voltage, Channels 1 and 2<br>+5 V (100 nF blocking capacitor required).                                                          | 1,2 |

| 53  | $V_{OUT2}$  | 0    | Analog Voice (Voltage) Output, Channel 2 Requires a coupling capacitor to the SLIC. The capacitor value depends on the SLIC's input impedance. | 2   |

| 54  | GNDA2       | I    | Analog Ground, Channel 2 Not internally connected to GNDD, GNDA1,or GNDA.                                                                      | 2   |

| 55  | $V_{IN2}$   | I    | Analog Voice (Voltage) Input, Channel 2 Requires a coupling capacitor >39 nF to the SLIC.                                                      |     |

| 56  | $V_{REF}$   | I/O  | Reference Voltage Must connect to a 220 nF cap. to ground.                                                                                     |     |

| 57  | $V_{DDREF}$ | I    | Analog Supply Reference Voltage 5 V (100 nF blocking capacitor required).                                                                      |     |

| 58  | NC          |      | Not Connected Pin is not connected in this device.                                                                                             |     |

| 59  | GNDA        | I    | Analog Ground Not internally connected to GNDD or GNDA1,2.                                                                                     |     |

| 60  | NC          |      | Not Connected Pin is not connected in this device.                                                                                             |     |

| 61  | $V_{DDA}$   | I    | Analog Supply Voltage<br>+5 V (100 nF blocking capacitor required).                                                                            |     |

| 62  | NC          |      | Not Connected Pin is not connected in this device.                                                                                             |     |

| 63  | GNDA        | I    | Analog Ground Internally isolated from GNDD (Pin 21), GNDA1 (Pin 50), and GNDA2 (Pin 54).                                                      |     |

| 64  | NC          |      | Not Connected Pin is not connected in this device.                                                                                             |     |

# 3 Functional Description

The general architecture of the PEB 2266 is discussed in the **Product Overview**, **Chapter 2**. This *Programmer's Reference Manual* describes the signal processing functions performed by the PEB 2266 and provides detailed information on those blocks and features that are programmable to meet country-specific telephone line requirements, and to adapt to the system environment:

- Analog Amplification/Attenuation,

- · Impedance Matching,

- · Transhybrid Balancing,

- Digital Amplification/Attenuation,

- Frequency Response Correction,

- Programmable A- or μ-Law Companding,

- Level Metering Functions,

- Two Tone Generators,

- 14 Programmable Input and Output Signals (Signaling Interface),

- Programmable Data Rate of PCM Highway,

- Programmable Time Slots for PCM Highway,

- · 4 Analog and 5 Digital Configurable Test Loops, and

- Programmable Clock Outputs.

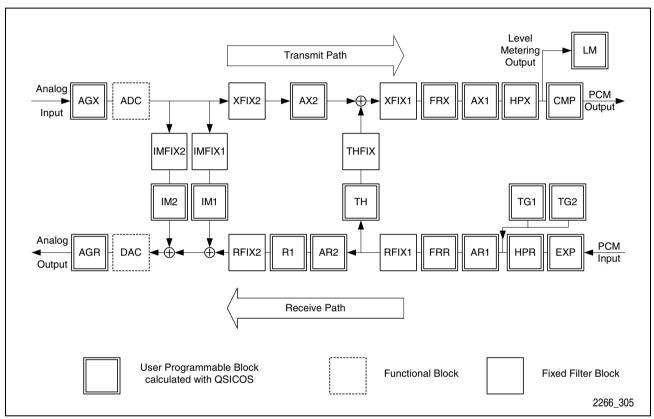

#### 3.1 Functional Blocks

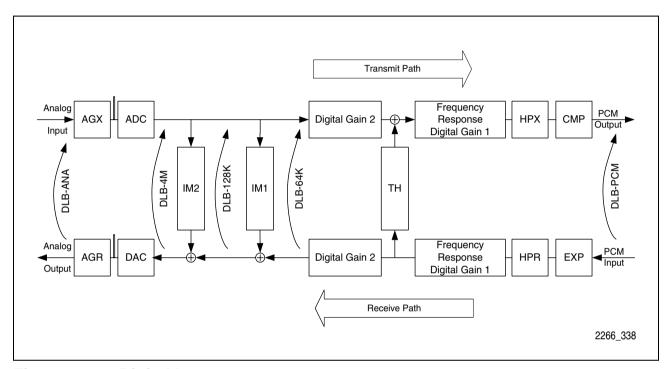

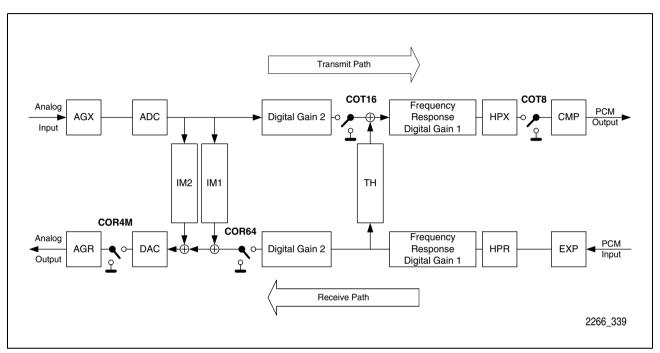

Based on an advanced digital filter concept, the PEB 2266 provides excellent transmission performance and high flexibility. The PEB 2266 includes both Fixed Blocks and Programmable Blocks. The new filter concept maximizes independence of the different filter blocks. The blocks are illustrated in **Figure 4**.

#### 3.1.1 Fixed Blocks

The fixed blocks (IMFIX1, IMFIX2, XFIX1, XFIX2, RFIX1, RFIX2 and THFIX) describe the transfer functions of the non-programmable blocks of the SICOFI<sup>®</sup>2-μC.

The fixed blocks in the transmit path (XFIX1 and XFIX2) include the transfer functions of the anti-aliasing prefilter, digital hardware filter, and decimation units.

The fixed blocks in the receive path (RFIX1 and RFIX2) include the transfer functions of the post filter, digital hardware filters, and interpolation blocks. The digital hardware filters are fast, hardwired logic circuits which reduce the amount of data and thus the workload of the DSP. IMFIX1, IMFIX2, and THFIX include functions like fixed delays, interpolation, and decimation blocks for the IM and TH filters.

#### 3.1.2 Programmable Blocks

The following paragraphs characterize the programmable filter blocks, including the numbers of bits used for programming each filter. These bits must be stored in the SICOFI®2-µC Coefficient RAM. A utility program (QSICOS) is available for calculation and optimization of the coefficients. QSICOS is described and discussed in **Chapter 7** "Application Hints" on page 56.

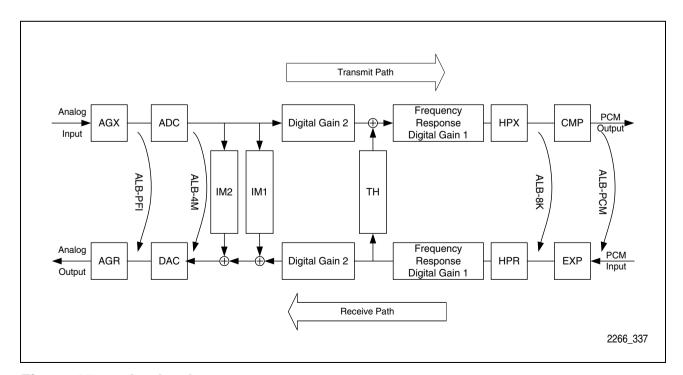

Figure 4 SICOFI®2-µC Detailed Flow Diagram

#### Analog Amplification/Attenuation (AGX, AGR) Block

In the transmit direction, an amplification of 6.02 dB can be enabled or disabled (CR2.2). In the receive direction, an attenuation of 6.02 dB can be enabled or disabled (CR2.3).

# Impedance Matching (IM) Filter

The Impedance Matching (IM) Filters can achieve a return loss better than 30 dB. They consist of 3 different loops: IM2 and the IIR and FIR filters internal to IM1.

The IM2 block works at a sampling rate of 4 MHz and is implemented with a fixed and a programmable element. 12 bits are needed for programming IM2.

The programmable IM1 block has two filter blocks internally which work in parallel: A Wave Digital Filter at 128 kHz for improved low frequency response, and a Finite Impulse Response Filter (FIR) at 64kHz for fine tuning.

The Wave Digital Filter is programmed with 60 bits. It is an Infinite Impulse Response Filter (IIR) with guaranteed passive behavior and excellent stability. The FIR Filter is programmed with 48 bits.

The real part of the termination impedance is positive under all conditions. The filters also show an improved overflow performance for transients.

When the channel is in operating mode the IM Filters have to be enabled by setting bit CR0.6 to "1" (see **Chapter 6.3.1** ). The IM filter coefficients are programmed with the COP\_4 and COP\_5 command (see **Chapter 6.5** for details). These command sequences also contain the coefficients for the R1 block.

#### **Transhybrid Balancing (TH) Filter**

The flexible implementation of the Transhybrid Balancing (TH) Filter allows optimization over a wide impedance range. The resulting Transhybrid Loss can achieve 30 dB (typically better than 40 dB; PEB/PEF 2266 without connecting a SLIC).

The programmable block TH is internally implemented by two filter blocks that work in parallel: A second order Wave Digital Filter (IIR) and a 7-tap FIR Filter. The Wave Digital Filter improves the low frequency response. It is programmed with 106 bits. The 7-tap FIR Filter is programmed with 7\*3 nibbles (84 bits) and is used for fine tuning. Both filter blocks work at a sampling frequency of 16 kHz.

The coefficients for the TH Filters are programmed with the COP\_0, COP\_1 and COP\_2 commands (see **Chapter 6.5** for details). For easy adaptation to different lines, two independent coefficient sets can be stored in the CRAM. The TH Filter behavior can be changed quickly by selecting either set with the bits CR0.0 and CR0.1. Bit CR0.7 enables/disables the TH path.

#### Frequency Response Correction (FRR and FRX) Filters

Frequency Response Correction (FRR and FRX) Filters are provided for line equalization and compensation of attenuation distortion. The use of minimum phase filters instead of linear phase filters improves the Group Delay Distortions. The Frequency Response Receive (FRR) Filter corrects distortions of the receive path, the Frequency Response Transmit (FRX) Filter performs the same function in transmit direction. Both are implemented as 5-tap programmable FIR filters operating at 8 kHz. Each of them is programmed with 5\*3 nibbles (60 bits). Their frequency response is better than 0.1 dB. FRX and FRR coefficients are programmed with the COP\_6 and COP\_7 commands (see **Chapter 6.5** ). Bit CR0.5 enables/disables FRX, Bit CR0.4 enables/disables FRR.

The R1 Filter is also used to compensate the frequency response in the receive path. The programming bits for the R1 Filter are part of the programming sequence for the Impedance Matching Filters (COP\_4, COP\_5).

#### Amplification/Attenuation Filters (AX1, AX2, AR1, AR2)

There are two separate filters in the transmit path and in the receive path, improving the level adjustment in both directions. These blocks allow optimal adjustment of the digital dynamic range. They further improve the transhybrid balancing results and allow gain adjustments independent of the TH Filters.

The Amplification/Attenuation Filters AX1 and AR1 are programmed with 5 nibbles each (20 bits each). The AX2 and AR2 Filters use 3 nibbles (12 bits) each for programming. This results in 32-bit programming information for the AX1 and AX2, and the same number of bits for the AR1 and AR2 filters. As shown below, the granularity of the gain adjustments is very fine.

• Amplification/Attenuation Receive (AR1, AR2) Filter

| Range            | Step Size       |

|------------------|-----------------|

| +3 dB to -14 dB  | 0.02 to 0.05 dB |

| -14 dB to -24 dB | 0.05 dB         |

Amplification/Attenuation Transmit (AX1, AX2) Filter

| Range            | Step Size       |

|------------------|-----------------|

| -3 dB to +14 dB  | 0.02 to 0.05 dB |

| +14 dB to +24 dB | 0.05 dB         |

The coefficients for AX1/AX2 and AR1/AR2 are programmed with the COP\_8 and COP\_9 commands (see **Chapter 6.5**). Bit CR0.3 enables/disables AX1 and AX2, CR0.2 enables/disables AR1 and AR2.

# **Total Range for Amplification/Attenuation**

The amplification/attenuation of the transmit and receive paths are determined by the accumulated effect of the following blocks:

Attenuation receive: AR = AR1 + FRR + AR2 + R1

Amplification transmit: AX = AX2 + FRX + AX1

The transmission characteristics of the SICOFI®2-µC (see *Hardware Reference Manual* Chapter 4.2) is guaranteed for the following range of total amplification/attenuation:

Receive characteristics: -9 dB < AR < 0 dB

Transmit characteristics: 0 dB < AX < 9 dB with A-Law coding

0 dB < AX < 7 dB with  $\mu$ -Law coding

Attenuation below -9 dB in receive direction and amplification above +9 dB in the transmit path will decrease the signal-to-noise performance due to the quantization effects in the D/A and A/D converters.

#### **Highpass Filters (HPX, HPR)**

The Highpass Filters suppress low-frequency noise (e.g. power-line noise) and are required to fulfill the ITU-Frequency masks. For special applications (e.g. modem transmission) the highpass filters may be disabled by programming bits CR3.1 and CR3.0.

#### A- or μ-Law Compander (CMP, EXP)

These units convert the 16-bit linear data format of the DSP to A-Law or  $\mu$ -Law PCM codes, and vice versa. A-Law or  $\mu$ -Law coding can be selected for each channel independently through register bit CR1.3.

#### **Tone Generators (TG1, TG2)**

The Tone Generators can be enabled or disabled (CR1.6 TG2, CR1.7 TG1), and will work with a fixed frequency of 1 kHz or with a programmable frequency (CR1.5 TG2, CR1.4 TG1). The programmed tone frequencies are determined by coefficients stored in CRAM through commands COP\_C (TG1) and COP\_D (TG2). (see **Chapter 7.3** "Programming the SICOFI®2-µC Tone Generators" on page 61)

#### **Level Metering (LM)**

The Level Metering unit can be enabled with bit CR2.2. It compares the signal level in the transmit path with a programmable threshold value in register XR7. Bit CR2.1 indicates if the measured level is higher or lower than the threshold (see **Chapter 7.2**).

#### 3.2 Other Functions

There are various functions provided by the PEB 2266 which are discussed in subsequent chapters. These include the programmable input and output signals, the programmable PCM data rates and time slots, the configurable analog and digital test loops, and the programmable clock outputs.

#### **Operational Description**

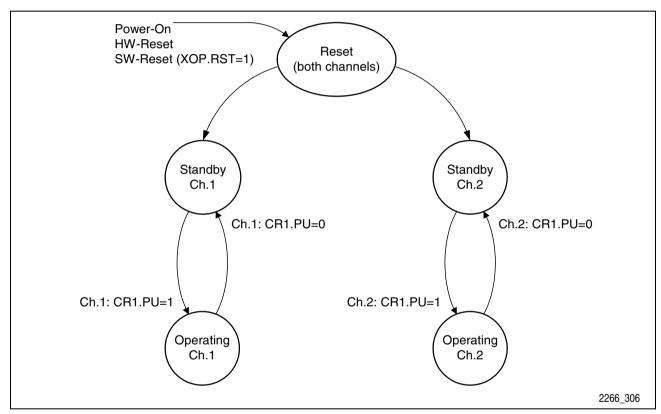

# 4 Operational Description

Upon initial application of the supply voltage  $V_{\rm DDD}$  to the PEB 2266 (Power-On), all registers of both channels will be initialized to "0" and all pins will be in a defined state (Reset State). For proper default settings, the supply voltage must be present before any voltage is applied to the input pins.

Pulling pin RESET# to low-level (HW-Reset) or setting bit RST in the XOP command byte (SW-Reset) also forces the SICOFI®2-µC into the Reset State.

#### 4.1 Operating States

Figure 5 SICOFI®2-µC State Diagram

# Reset (Default Setting)

During Reset (Default Setting), the command stack for SOP-, XOP-, and COP-command sequences is cleared. The Coefficient RAM content remains unchanged. The default register values and pin behavior are shown in **Table 2**. After pin RESET# is released, the device will leave the Reset State and enter the Standby State.

# **Operational Description**

Table 2 Default Settings during Reset State

| Affected Registers and Pins | State after Reset |

|-----------------------------|-------------------|

| CR0CR4                      | 00 <sub>H</sub>   |

| XR0XR7                      | 00 <sub>H</sub>   |

| DIN                         | Ignored           |

| DOUT                        | High impedance    |

| $V_{OUT1,}V_{OUT2}$         | High impedance    |

| SBx_y Input                 |                   |

| SOx_y                       | GNDD              |

#### Standby

Standby is a power-saving state. After Reset, both channels will be in Standby State. An individual channel can be brought to Standby State from Operating State by programming bit CR1.PU to "0". Keeping an unused channel in this mode will reduce overall system power dissipation.

In Standby State, signals on the analog inputs  $(V_{\rm INx})$  and PCM receive pins (DRA, DRB) are ignored. The analog outputs  $(V_{\rm OUTx})$  and the PCM transmit pins (DXA, DXB) are in high impedance state. The Serial Microcontroller Interface is ready to receive and transmit commands and data. Registers and the Coefficient RAM can be written and read. The Signaling Interface and the debouncing functions are working. Signaling status changes will generate interrupts (if enabled) and the signaling status can be read through the Microcontroller Interface.

#### **Operating**

In this state, the embedded DSP processes voice data according to the programmed filter characteristics in the Coefficient-RAM (CRAM) and the settings of the configuration registers. This mode can be enabled for individual channels by setting bit CR1.PU to "1". Pins  $V_{\rm OUTx}$  and  $V_{\rm INx}$  are transmitting and receiving analog signals. The PCM Interface is active during the time slots assigned to the channel. The tone generators, test functions, and level metering functions can also be enabled while the channel is in Operating State.

#### 4.2 Transmission Characteristics

The specifications to which the SICOFI<sup>®</sup>2-μC are tested are tighter than the ITU-T Q.552 specification to guardband various SLIC implementations. The guaranteed transmission characteristics of the SICOFI<sup>®</sup>2-μC under test conditions ensure that the final linecard design will meet the ITU-T specification. The transmission characteristics are discussed in detail in the SICOFI<sup>®</sup>2-μC *Hardware Reference Manual*.

# 5 Interface Description

The SICOFI<sup>®</sup>2-µC provides four interfaces:

- · Analog Interface,

- PCM Interface,

- · Signaling Interface, and

- Serial Microcontroller Interface.

A general description of these interface is given in the *Product Overview*, Chapter 4. Refer to the *Hardware Reference Manual* for a more detailed information on timings and AC and DC characteristics of these interfaces.

The subsequent chapters in this manual explain the configuration and operation of the four interfaces.

#### 5.1 Analog Interface

The Analog Interface in combination with a Subscriber Line Interface Circuit (SLIC) forms a configurable tip & ring (t/r) telephone line. The AC transmission characteristic of the SICOFI®2- $\mu$ C—SLIC combination can be controlled by programming the digital filter structures inside the SICOFI®2- $\mu$ C. The correct filter coefficients are determined by the targeted AC transmission behavior (e.g. Telco specification) and by the transfer functions of the SLIC. QSICOS Coefficient Calculation and Register Configuration Software is available for the SICOFI®2- $\mu$ C (see **Chapter 7.1**).

The SICOFI®2- $\mu$ C can be interfaced directly to electronic SLICs or transformer solutions. The high driving capability of up to 300 Ohms eliminates the need for an external amplifier that is normally used with transformer SLICs.

#### 5.2 PCM Interface

The SICOFI®2-µC provides an industry-standard PCM Interface with access to two PCM highways. The PCM Interface has the following features:

- Data rate from 128 kbit/s to 8 Mbit/s per highway.

- 2 to 128 time slots per frame per highway,

- PCM data format serialized 8 bits with MSB first,

- Configurable A-Law or μ-Law coding,

- Independently configurable time slot and highway for each channel and direction,

- PCM clock speeds of once or twice the bit rates.

- Programmable sampling slopes, and

- Programmable frame delay.

When the SICOFI<sup>®</sup>2- $\mu$ C is transmitting data on DXA (DXB), pin TCA# (TCB#) is activated to control an external driving device.

Table 3 Configurable PCM Features and Functions

| Features and Functions             | Register | Bit    | Label             |

|------------------------------------|----------|--------|-------------------|

| Single or double bit clock         | XR6      | 7      | C-MODE            |

| Transmit slope                     | XR6      | 6      | X-S               |

| Receive slope                      | XR6      | 5      | R-S               |

| Transmitter driving mode           | XR6      | 4      | DRV_0             |

| PCM frame delay                    | XR6      | 3 to 0 | Shift, PCM-OFFSET |

| Receive highway selection          | CR4      | 7      | R-WAY             |

| Receive time slot assignment       | CR4      | 6 to 0 | RS                |

| Transmit highway selection         | CR5      | 7      | X-WAY             |

| Transmit time slot assignment      | CR5      | 6 to 0 | XS                |

| A-Law or μ-Law coding and decoding | CR1      | 3      | LAW               |

# 5.2.1 PCM Clock Speeds

The data rate and the number of time slots on each highway depend on the PCM Clock input (PCLK) frequency and on the setting of the C-MODE bit in register XR6:

Table 4 PCM Clocking and Data Rates

|                      | Clock Mode                                           |                                      |

|----------------------|------------------------------------------------------|--------------------------------------|

|                      | C-MODE (XR6.7) = 0<br>(Single Clock)                 | C-MODE (XR6.7) = 1<br>(Double Clock) |

| PCLK / Bit           | PCLK period  Bit length                              | PCLK period   Bit length             |

|                      | 2266_307                                             | 2266_308                             |

| Data Rate            | f <sub>PCLK</sub> f <sub>PCLK</sub> /2               |                                      |

| Number of Time Slots | $f_{PCLK}$ $f_{PCLK}/2$ $f_{PCLK}/64$ $f_{PCLK}/128$ |                                      |

**Table 5** shows some typical PCM configurations:

Table 5 Typical PCM Data Rates, Time Slots, and Clock Modes

| Data Rate     | Time Slots    | PCLK Frequency                            |                                           |

|---------------|---------------|-------------------------------------------|-------------------------------------------|

| (per highway) | (per highway) | C_MODE (XR6.7) = 0<br>(Single Clock Mode) | C_MODE (XR6.7) = 1<br>(Double Clock Mode) |

| 128 kbit/s    | 2             | 128 kHz                                   | 256 kHz                                   |

| 256 kbit/s    | 4             | 256 kHz                                   | 512 kHz                                   |

| 512 kbit/s    | 8             | 512 kHz                                   | 1024 kHz                                  |

| 768 kbit/s    | 12            | 768 kHz                                   | 1536 kHz                                  |

| 1024 kbit/s   | 16            | 1024 kHz                                  | 2048 kHz                                  |

| 1536 kbit/s   | 24            | 1536 kHz                                  | 3072 kHz                                  |

| 2048 kbit/s   | 32            | 2048 kHz                                  | 4096 kHz                                  |

| 4096 kbit/s   | 64            | 4096 kHz                                  | 8192 kHz                                  |

| 8192 kbit/s   | 128           | 8192 kHz                                  | not allowed                               |

# 5.2.2 Transmit and Receive Slopes

Transmission of data bits on DXA and DXB is synchronous to the rising edge or the falling edge of PCLK. Received bits on DRA and DRB are latched with either the falling edge or the rising edge of PCLK. This feature allows easy adaptations to different PCM highway timing conditions and helps to avoid bit overlaps with other devices.

**Transmit** slope configured with bit **X-S** (XR6.6)

| 0 | Rising  | Edge of PCLK initiates the transmission  |

|---|---------|------------------------------------------|

| 1 | Falling | Luge of FOLIX initiates the transmission |

**Receive** slope configured with bit **R-S** (XR6.5)

| 0 | Falling | Edge of PCLK latches the receive level |

|---|---------|----------------------------------------|

| 1 | Rising  | Lage of 1 Octobries the receive level  |

**Table 6** shows the combinations of X-S, R-S and C\_MODE settings, and the resulting positions of the transmit slope and the receive slope with reference to the start of a PCM frame (rising edge of FSC).

Table 6 Transmitting and Receiving Bit 7 in Time Slot 0

|                   | Sampling Slope         |                         | Clock Mode                                 |                                            |

|-------------------|------------------------|-------------------------|--------------------------------------------|--------------------------------------------|

| (XR6.0-<br>XR6.4) | R-S (XR6.5)<br>Receive | X-S (XR6.6)<br>Transmit | C-MODE (XR6.7) = 0<br>(Single Clock)       | C-MODE (XR6.7) = 1<br>(Double Clock)       |

|                   |                        |                         | FSC                                        | FSC                                        |

| 00000             | 0                      | 0                       | PCLK A                                     | PCLK A                                     |

| 00000             | ¥                      | <u> </u>                | DXA DXB                                    | DXA X                                      |

|                   |                        |                         | DRA V// VVV<br>DRB /// ////                | DRA \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\   |

|                   |                        |                         | FSC                                        | FSC                                        |

|                   | 1                      | 0                       | PCLK A                                     | PCLK A                                     |

| 00000             |                        | <u> </u>                | DXA DXB                                    | DXA DXB                                    |

|                   |                        |                         | DRA W//// W/DRB ////// M                   | DRA W///// W/DRB /////// //                |

|                   |                        |                         | FSC                                        | FSC                                        |

| 00000             | 0                      | 1                       | PCLK                                       | PCLK T                                     |

| 00000             | ¥                      | •                       | DXA<br>DXB                                 | DXA DXB                                    |

|                   |                        |                         | DRA DRB                                    | DRA V// \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

|                   |                        |                         | FSC                                        | FSC                                        |

| 00000             | 1                      | 1 ,                     | PCLK T                                     | PCLK T                                     |

| UUUUU             |                        |                         | DXA<br>DXB                                 | DXA DXB                                    |

|                   |                        |                         | DRA V// \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | DRA V//// V<br>DRB ////// //               |

# 5.2.3 Transmitter Driving Mode

In single clock mode, the transmit outputs for bit 0 DXA and DXB can be programmed to drive the PCM highway only during the first half of a PCLK cycle. The outputs will go to high impedance state during the second half of PCLK cycle.

Table 7 Transmitter Driving Modes

| Logic State       | C-MODE (XR6.7) = 0<br>(Single Clock Mode) | C-MODE (XR6.7) = 1<br>(Double Clock Mode) |

|-------------------|-------------------------------------------|-------------------------------------------|

| DRV_0 (XR6.4) = 0 | PCLK DXA DXB                              | PCLK DXA DXB                              |

| DRV_0 (XR6.4) = 1 | DXA DXB Bit 1 Bit 0                       | Not applicable                            |

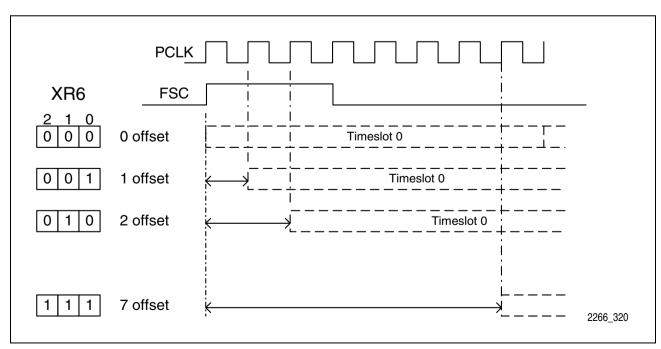

### 5.2.4 PCM Frame Delay

By default, the rising edge of the FSC signal indicates the start of a PCM frame (time slot 0). An extra delay of up to 7 clock periods, valid for all channels, may be programmed in register XR6 (see **Figure 6**).

Figure 6 PCM Offset Programming with Bits in XR6.2 to XR6.0

Table 8 PCM Offset in Single Clock Mode

| Shift (XR6.3) | Offset (XR6.20) | No. of PCLK Cycles | Number of Bits |

|---------------|-----------------|--------------------|----------------|

|               | 000             | 0                  | 0              |

|               | 001             | 1                  | 1              |

|               | 010             | 2                  | 2              |

| 0             | 011             | 3                  | 3              |

| U             | 100             | 4                  | 4              |

|               | 101             | 5                  | 5              |

|               | 110             | 6                  | 6              |

|               | 111             | 7                  | 7              |

| 1             | xxx             | not v              | alid           |

Table 9 PCM Offset in Double Clock Mode

| Shift (XR6.3) | Offset (XR6.20) | No. of PCLK Cycles | Number of Bits |

|---------------|-----------------|--------------------|----------------|

|               | 000             | 0                  | 0              |

|               | 001             | 2                  | 1              |

|               | 010             | 4                  | 2              |

| 0             | 011             | 6                  | 3              |

| 0             | 100             | 8                  | 4              |

|               | 101             | 10                 | 5              |

|               | 110             | 12                 | 6              |

|               | 111             | 14                 | 7              |

|               | 000             | 1                  | 1/2            |

|               | 001             | 3                  | 1 1/2          |

|               | 010             | 5                  | 2 1/2          |

| 1             | 011             | 7                  | 3 1/2          |

| ı             | 100             | 9                  | 4 1/2          |

|               | 101             | 11                 | 5 1/2          |

|               | 110             | 13                 | 6 1/2          |

|               | 111             | 15                 | 7 1/2          |

#### 5.2.5 Time Slot Assignment

#### **Receive Direction**

The receive highway and time slot for each channel are configured in the channel specific register CR4.

| Register CR4             | Receive Time Slot Assignment                          |

|--------------------------|-------------------------------------------------------|

| <b>R-WAY</b> (CR4.7)     | 0: Receive PCM data on DRA 1: Receive PCM data on DRB |

| RS6 RS0<br>(CR4.6 CR4.0) | Receive time slot<br>0 - 127                          |

#### **Transmit Direction**

The transmit highway and time slot for each channel are configured in the channel specific register CR5.

| Register CR5         | Transmit Time Slot Assignment                           |

|----------------------|---------------------------------------------------------|

| <b>X-WAY</b> (CR5.7) | 0: Transmit PCM data on DXA 1: Transmit PCM data on DXB |

|                      | Transmit time slot<br>0 - 127                           |

Both channels must have different transmit time slots or highways assigned. If both channels try to drive the same time slot on the same transmit output, both channels will be disabled and a crash bit in common register XR5 will indicate the contention (CRSH\_A for DXA, CRSH\_B for DXB). The crash condition can be cleared by reprogramming the values in CR5 and reading XR5.

# 5.3 Signaling Interface

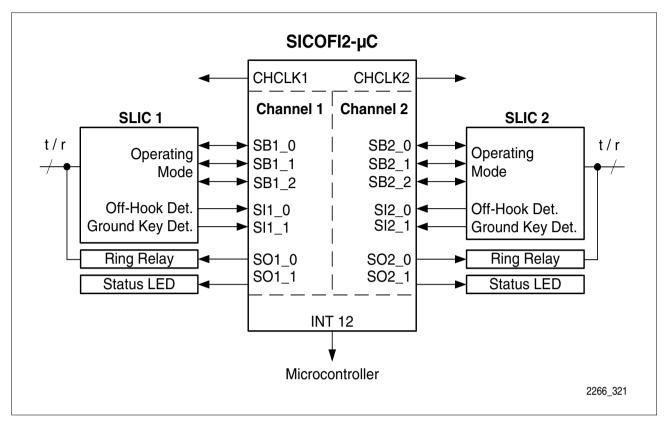

The SICOFI®2-µC can accumulate and manage the I/O status of four SLICs—one per channel— through its Signaling Interface (see **Figure 7**).

The Signaling Interface handles line and SLIC status and control, ringing relays, etc. with the following:

- 14 Signaling pins (2 input pins, 2 output pins, and 3 user-configurable bi-directional pins per channel),

- Debouncing functions,

- 2 Interrupts (one for each channel-pair), and

- 2 Clock output signals (user configurable).

Figure 7 Signaling Example for two Subscriber Lines

# 5.3.1 Signaling Pins and Registers

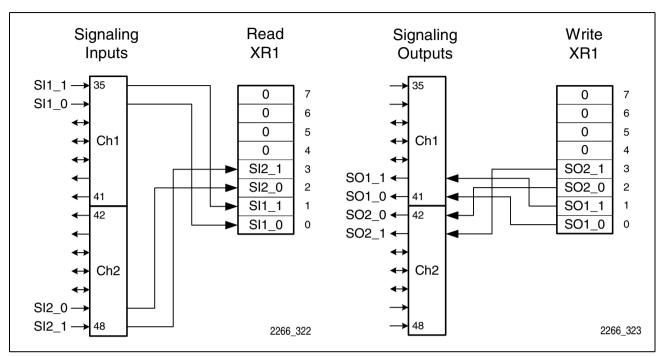

The function of common register XR0 depends on the type of access:

| Reading from XR0                                                                           | Writing to XR0                                                                |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Provides status information on the eight signaling input pins Slx_y (see <b>Figure 8</b> ) | Determines logic level of the signaling outputs SO_x_y (see <b>Figure 8</b> ) |

Figure 8 Access to the Signaling Inputs and Outputs Through XR0

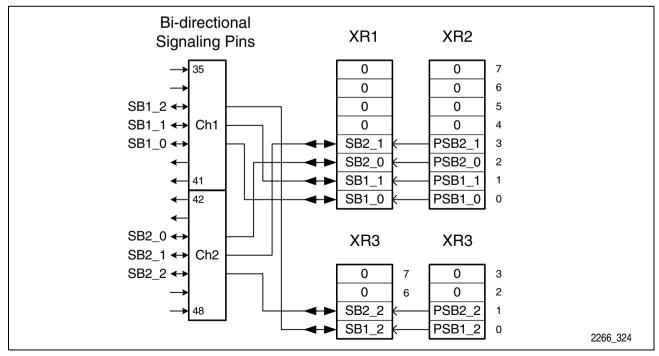

The bi-directional signaling pins SBx\_y are configured through common register XR2 and through bits 0 to 3 in XR3. Reading from registers XR1 and XR3 provides status information on those bi-directional pins that have been configured as inputs. Writing to register XR1 and XR3 sets the logic levels of those bi-directional pins operating as outputs (see **Figure 9**).

Figure 9 Bi-directional Pin Configuration and Access via XR1, XR2, XR3

#### 5.3.2 Debouncing Functions

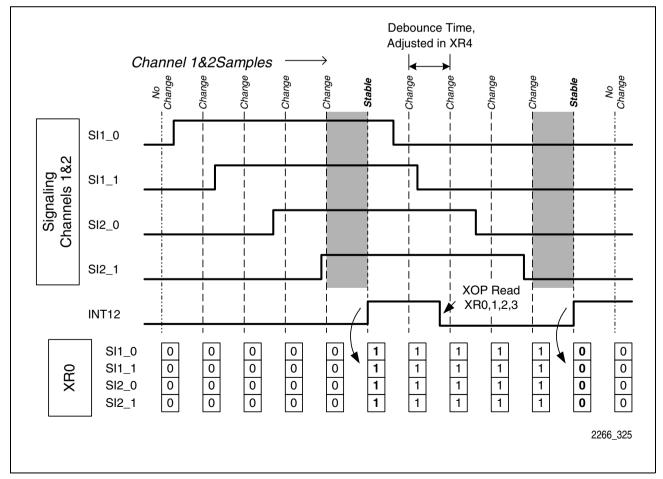

The SICOFI<sup>®</sup>2-μC offers programmable debouncing functions for improved immunity against spurious signals and glitches applied to the signaling inputs (SIx\_y and SBx\_y, if configured as inputs). If debounce is enabled, the input pins are sampled in intervals between 0.5ms and 26ms.

| Field N<br>(XR4, Bits 7 to 4) | Debounce Sampling Period                     |

|-------------------------------|----------------------------------------------|

| 0000 (default)                | Debouncing and interrupt generation disabled |

| 1111                          | Sampling period = 0.5 ms                     |

| 0001 to 1101                  | Sampling period = N * 2 ms (2 to 26 ms)      |

| 1110                          | Reserved                                     |

In order to detect status changes, all signaling inputs must be stable for two successive samples. Under this condition, an interrupt is generated and the signaling input values are stored in the corresponding registers.

Figure 10 shows an example for this scheme when SBx\_x are programmed as outputs.

Figure 10 Signal Debouncing, Interrupt Generation and Register Updates

#### 5.3.3 Interrupt Handling

With the debouncing functions enabled, changes on the Signaling Interface are indicated by the interrupt signal INT12 for the channel pair.

#### INT12 (Channels 1 and 2)

| Logic State | Changes at the Signaling Interface Inputs         |

|-------------|---------------------------------------------------|

| 0           | No signaling change                               |

| 1           | Input level changed on at least one signaling pin |

The interrupt signals can be used to alert the microcontroller to signaling changes (e.g. subscriber line off-hook detection). The logic levels of the signaling inputs are reflected in the common registers XR0, XR1 and XR3. One of the XOP\_3 to XOP\_7 commands must be used to access all three registers inside the interrupt service routine. The read access releases the interrupt signal.

Figure 11 Interrupt Handling

Signal debouncing and interrupt generation can be disabled in register XR4. In this case, the microcontroller can check the signaling status by polling the signaling registers.

# 5.3.4 Clock Output Signals

For special purposes, two Chopper Clock output signals are provided by the PEB 2266:

- CHCLK1 (Pin 33) is configured in register XR4. Field T (bits XR4.3 to XR4.0)

- CHCLK2 (Pin 16) is configured in register XR5.CHCLK2 (bits XR5.3 and XR5.2)

Note: Both chopper clock output signals are available only if a valid master clock signal is applied to pin MCLK.

Table 10 CHCLK1 Programming

| XR4.Field T | CHCLK1 Output)       |

|-------------|----------------------|

| 0000        | High level (+5V)     |

| 0001        | Clock period = 2 ms  |

| 0010        | Clock period = 4 ms  |

| 0011        | Clock period = 6 ms  |

| 0100        | Clock period = 8 ms  |

| 0101        | Clock period = 10 ms |

| 0110        | Clock period = 12 ms |

| 0111        | Clock period = 14 ms |

| 1000        | Clock period = 16 ms |

| 1001        | Clock period = 18 ms |

| 1010        | Clock period = 20 ms |

| 1011        | Clock period = 22 ms |

| 1100        | Clock period = 24 ms |

| 1101        | Clock period = 26 ms |

| 1110        | Clock period = 28 ms |

| 1111        | Low level (0V)       |

Table 11 CHCLK2 Programming.

| XR5.CHCLK2 | CHCLK2 Output                                                                  |

|------------|--------------------------------------------------------------------------------|

| 00         | High level (+5V)                                                               |

| 01         | 512 kHz signal                                                                 |

| 10         | 256 kHz signal                                                                 |

| 11         | 16,384 kHz signal (at least one of the two channels must be in POWER-UP state) |

#### 5.4 Serial Microcontroller Interface

The internal configuration registers, the signaling registers, and the Coefficient RAM (CRAM) of the SICOFI®2-µC are accessible through a Serial Microcontroller Interface.

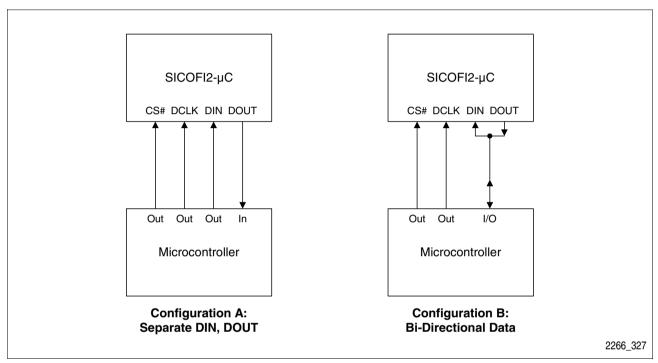

The Serial Microcontroller Interface consists of four lines (CS#, DCLK, DIN, and DOUT) as shown in **Figure 12**:

Figure 12 Serial Microcontroller Interface

Table 12 Serial Microcontroller Interface Pins and Functions

| Symbol | Pin | Function                                                                                                                                                                                  |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#    | 17  | Chip Select, active low. The falling edge initiates the read or write access to the SICOFI®2-μC. The rising edge terminates the read or write access.                                     |

| DCLK   | 18  | Data Clock: Bit synchronous clock; maximum clock rate is 8192kHz.                                                                                                                         |

| DIN    | 19  | Data Input: Serialized data bytes with MSB first. Data bits are latched with the rising edge of DCLK.                                                                                     |

| DOUT   | 20  | Data Output: Serialized data bytes with MSB first.  Data bits are driven with the falling edge of DCLK as a response to a read command. Otherwise, DOUT is in high impedance ("Z") state. |

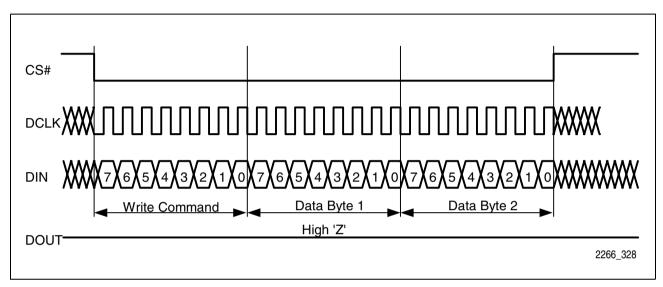

#### 5.4.1 Write Access

Following a falling edge of CS#, the first eight bits received on DIN specify the type of command. The data bytes following a write command are stored in the selected configuration registers or the selected part of the Coefficient RAM. The number of data bytes depend on the type of command.

Figure 13 Example for a Two-Byte Write Access

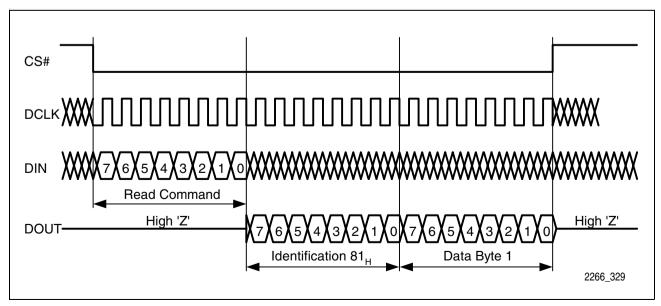

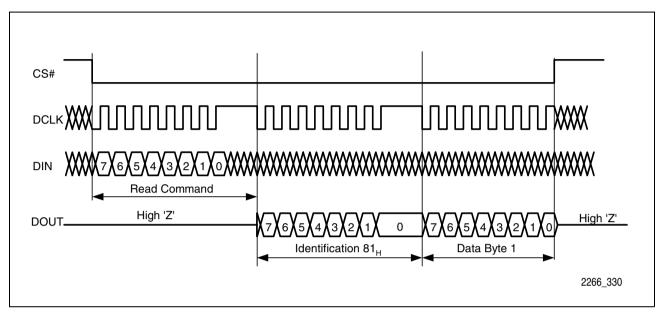

#### 5.4.2 Read Access

If the first eight bits received via DIN represent a read command, the SICOFI<sup>®</sup>2-µC will initiate its response via DOUT. An identification byte (81<sub>H</sub>) is followed by the requested number of data bytes (contents of configuration registers or contents of the CRAM). During execution of a read command, the device will ignore data on DIN.

Figure 14 Example for a One-Byte Read Access

For byte-by-byte transfer, the high time of DCLK can be prolonged, resulting in a user defined 'waiting time' between bytes. This mechanism can be used for writing to and reading from the device.

Figure 15 Example for a Read Access, with Byte-by-Byte Transfer

Read and write commands can be chained by leaving CS# low after the completion of each command sequence.

For read or write access to individual registers, the command sequence may be terminated by rising CS# after the transmission of any number of bytes.

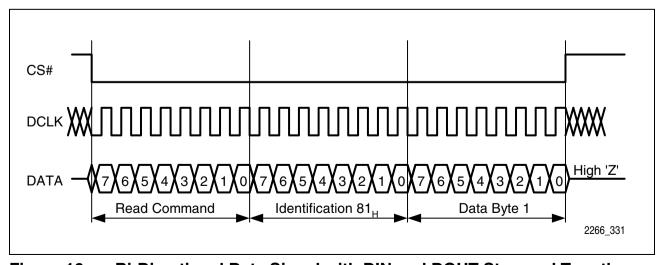

#### 5.4.3 Three-Wire Access

DIN and DOUT may be strapped together and connected to a single I/O pin of the microcontroller. The interface remains fully functional with only 3 wire connections.

Figure 16 Bi-Directional Data Signal with DIN and DOUT Strapped Together

# 6 Programming the SICOFI®2-μC

The transmission characteristics and interfaces of the PEB 2266 can be adapted to various environments. Configuring the functional blocks and programming the digital filter behavior is accomplished by loading values to the Configuration Registers and the Coefficient RAM (CRAM). Software utilities are available to determine the appropriate register and CRAM values (see **Chapter 7.1** "Support Tools" on page 56).

# 6.1 Programming Overview

The SICOFI®2-µC has eight Common Configuration Registers (XR0 to XR7). Settings in these registers affect all two channels.

Each of the two channels has six Channel-Specific Configuration Registers (CR0 to CR5). Settings in these registers affect only the designated channel.

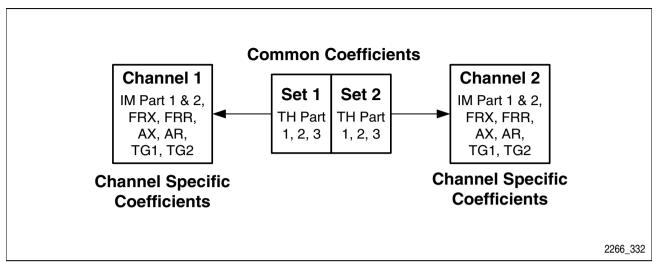

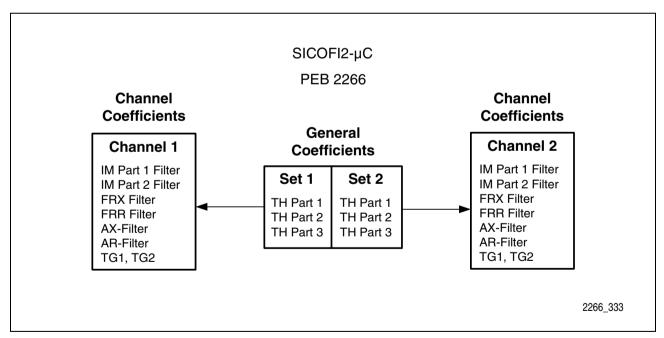

The filters of each channel are individually programmable through channel-specific coefficients in CRAM. There are two global sets of TH Filter coefficients that can be assigned to either channel. All of the filter blocks are described in **Chapter 3** and their locations are illustrated in **Figure 4**.

## 6.1.1 Register Model

Channel-specific and common configuration registers and coefficients are shown in **Table 13**.

Table 13 Register Model

| Configuration Registers and CRAM              | Channel Usage    |  |  |

|-----------------------------------------------|------------------|--|--|

| XR0 to XR7 (8 bytes)                          | common           |  |  |

| CR0 to CR5 (6 bytes)                          |                  |  |  |

| IM/R1 Coefficients (16 bytes)                 | channel appoific |  |  |

| FRR, FRX Coefficients (16 bytes)              | channel-specific |  |  |

| AR1, AR2, AX1, and AX2 Coefficients (8 bytes) |                  |  |  |

| TG1 and TG2 Coefficients (8 bytes)            |                  |  |  |

| TH Coefficient Set 1 (24 bytes)               | either           |  |  |

| TH Coefficient Set 2 (24 bytes)               | either           |  |  |

# 6.1.2 Register Maps

Table 14 Read Access to Common Configuration Register (XR) Map

|     | Bit 7                 | Bit 6    | Bit 5   | Bit 4  | Bit 3          | Bit 2      | Bit 1  | Bit 0  |

|-----|-----------------------|----------|---------|--------|----------------|------------|--------|--------|

| XR0 | 0                     | 0        | 0       | 0      | SI2_1          | SI2_0      | SI1_1  | SI1_0  |

| XR1 | 0                     | 0        | 0       | 0      | SB2_1          | SB2_0      | SB1_1  | SB1_0  |

| XR2 | 0                     | 0        | 0       | 0      | PSB2_1         | PSB2_0     | PSB1_1 | PSB1_0 |

| XR3 | 0                     | 0        | SB2_2   | SB1_2  | 0              | 0          | PSB2_2 | PSB1_2 |

| XR4 |                       | Signal D | ebounce |        | CHCLK1         |            |        |        |

| XR5 | MCLK-SEL CRSH-A CRSH- |          |         | CRSH-B | CHCLK2 Version |            |        | sion   |

| XR6 | C-Mode                | X-S      | R-S     | DRV_0  | Shift          | PCM-OFFSET |        |        |

| XR7 | OF7                   | OF6      | OF5     | OF4    | OF3            | OF2        | OF1    | OF0    |

# Table 15 Write Access to Common Configuration Register (XR) Map

|     | Bit 7           | Bit 6    | Bit 5   | Bit 4  | Bit 3          | Bit 2      | Bit 1  | Bit 0  |

|-----|-----------------|----------|---------|--------|----------------|------------|--------|--------|

| XR0 | 0               | 0        | 0       | 0      | SO2_1          | SO2_0      | SO1_1  | SO1_0  |

| XR1 | 0               | 0        | 0       | 0      | SB2_1          | SB2_0      | SB1_1  | SB1_0  |

| XR2 | 0               | 0        | 0       | 0      | PSB2_1         | PSB2_0     | PSB1_1 | PSB1_0 |

| XR3 | 0               | 0        | SB2_2   | SB1_2  | 0              | 0          | PSB2_2 | PSB1_2 |

| XR4 |                 | Signal D | ebounce |        | CHCLK1         |            |        |        |

| XR5 | MCLK-SEL CRSH-A |          |         | CRSH-B | CHCLK2 Version |            |        | sion   |

| XR6 | C-Mode          | X-S      | R-S     | DRV_0  | Shift          | PCM-OFFSET |        |        |

| XR7 | OF7             | OF6      | OF5     | OF4    | OF3            | OF2        | OF1    | OF0    |

# Table 16 Channel-Specific Configuration Register (CR) Map (Read & Write)

|     | Bit 7      | Bit 6        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-----|------------|--------------|-------|-------|-------|-------|--------|-------|

| CR0 | TH         | TH IM/R1 FRX |       | FRR   | AX    | AR    | TH-SEL |       |

| CR1 | ETG2       | ETG1         | PTG2  | PTG1  | LAW   | 0     | 0      | PU    |

| CR2 | COT/R      |              |       | 0     | IDR   | LM    | LMR    | V+T   |

| CR3 | TEST-Loops |              |       |       | AGX   | AGR   | D-HPX  | D-HPR |

| CR4 | R-way      | RS6          | RS5   | RS4   | RS3   | RS2   | RS1    | RS0   |

| CR5 | X-way      | XS6          | XS5   | XS4   | XS3   | XS2   | XS1    | XS0   |

#### 6.1.3 CRAM Structure

Coefficient RAM (CRAM) is used to store the individual coefficients calculated for each channel. The coefficients can be written and read through the Microcontroller Interface. The IM, FRX, FRR, AX, AR, TG1, and TG2 coefficients are accessed through COP-Command Sequences which include the channel address (see **Chapter 6.5**).

Table 17 Coefficient RAM (CRAM) Structure per Channel

| <u> </u>  |                     |                     |  |  |  |  |  |  |  |

|-----------|---------------------|---------------------|--|--|--|--|--|--|--|

| IM Part 1 | 8 Coefficient Bytes |                     |  |  |  |  |  |  |  |

| IM Part 2 | 8 Coeffici          | ent Bytes           |  |  |  |  |  |  |  |

| FRX       | 8 Coeffici          | 8 Coefficient Bytes |  |  |  |  |  |  |  |

| FRR       | 8 Coeffici          | 8 Coefficient Bytes |  |  |  |  |  |  |  |

| AX        | 4 Coefficient Bytes |                     |  |  |  |  |  |  |  |

| AR        | 4 Coefficient Bytes |                     |  |  |  |  |  |  |  |

| TG1       | 4 Coefficient Bytes |                     |  |  |  |  |  |  |  |

| TG2       | 4 Coefficient Bytes |                     |  |  |  |  |  |  |  |

CRAM also contains four sets of TH coefficients. Each set can be assigned to either of the two channels.

Table 18 Coefficient RAM (CRAM) Structure per Set

| TH Part 1 | 8 Coefficient Bytes |

|-----------|---------------------|

| TH Part 2 | 8 Coefficient Bytes |