# 74ABT162245 16-Bit Transceiver with TRI-STATE® Outputs

## **General Description**

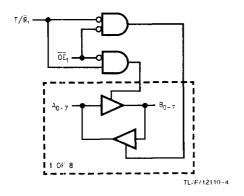

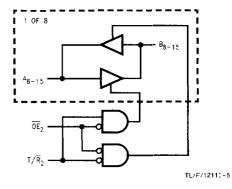

The 'ABT162245 contains sixteen non-inverting bidirectional buffers with TRI-STATE outputs and is intended for bus oriented applications. The device is byte controlled. Each byte has separate control inputs which can be shorted together for full 16-bit operation. The T/Ā inputs determine the direction of data flow through the device. The OE inputs disable both the A and B ports by placing them in a high impedance state.

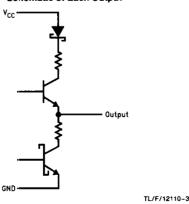

The  $25\Omega$  series resistors in the outputs reduce ringing and eliminate the need for external resistors.

#### **Features**

- Bidirectional non-inverting buffers

- Separate control logic for each byte

- 16-bit version of the 'ABT2245

- A and B output sink capability of 64 mA, source capability of 32 mA

- Guaranteed output skew

- Guaranteed latchup protection

- High impedance glitch free bus loading during entire power up and power down cycle

- Non-destructive hot insertion capability

## **Logic Symbol**

## **Pin Description**

| Pin Names                       | Description                      |

|---------------------------------|----------------------------------|

| ŌĒn                             | Output Enable Input (Active Low) |

| T/Rn                            | Transmit/Receive Input           |

| A <sub>0</sub> -A <sub>15</sub> | Side A Inputs/Outputs            |

| B <sub>0</sub> -B <sub>15</sub> | Side B Inputs/Outputs            |

#### **Schematic of Each Output**

#### **Connection Diagram**

#### Pin Assignment for SSOP

TL/F/12110-2

# **Functional Description**

The 'ABT162245 contains sixteen non-inverting bidirectional buffers with TRI-STATE outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation.

## **Truth Tables**

| Inputs          |                  | Outputs                                                                         |

|-----------------|------------------|---------------------------------------------------------------------------------|

| ŌĒ <sub>1</sub> | T/R <sub>1</sub> | Outputs                                                                         |

| L               | L                | Bus B <sub>0</sub> -B <sub>7</sub> Data to Bus A <sub>0</sub> -A <sub>7</sub>   |

| L               | Н                | Bus A <sub>0</sub> -A <sub>7</sub> Data to Bus B <sub>0</sub> -B <sub>7</sub>   |

| Н               | Х                | HIGH-Z State on A <sub>0</sub> -A <sub>7</sub> , B <sub>0</sub> -B <sub>7</sub> |

| Inputs          |      | Outputs                                                                           |

|-----------------|------|-----------------------------------------------------------------------------------|

| ŌĒ <sub>2</sub> | T/R2 |                                                                                   |

| L               | L    | Bus B <sub>8</sub> -B <sub>15</sub> Data to Bus A <sub>8</sub> -A <sub>15</sub>   |

| L               | Н    | Bus A <sub>8</sub> -A <sub>15</sub> Data to Bus B <sub>8</sub> -B <sub>15</sub>   |

| Н               | Χ    | HIGH-Z State on A <sub>8</sub> -A <sub>15</sub> , B <sub>8</sub> -B <sub>15</sub> |

H = High Voltage Level

- L = Low Voltage Level

- X Immaterial

- Z = High Impedance

# **Logic Diagrams**