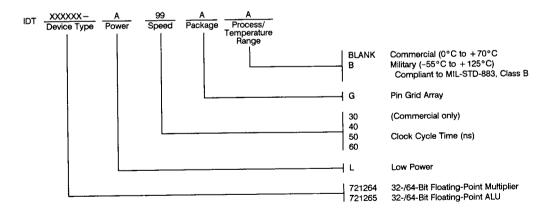

# 32-BIT AND 64-BIT IEEE FLOATING-POINT MULTIPLIER AND ALU

IDT721264 IDT721265

### FEATURES:

- Conforms to the requirements of IEEE Standard 754, 1985 version, for full 32-bit and 64-bit multiply and arithmetic operations

- · Very high-speed operation

- 16.7 megaflops (60ns) pipelined ALU operation (Add/Subtract/Convert/Compare)

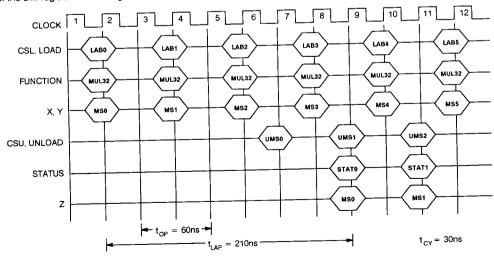

- 16.7 megaflops (60ns) pipelined 32-bit (single precision) multiplications

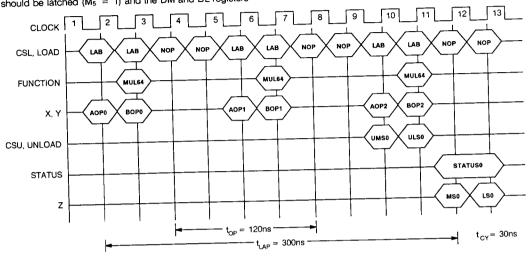

- 8.0 megaflops (120ns) pipelined 64-bit (double precision) multiplications

- Full floating-point function arithmetic logic unit including:

- Add

- Subtract

- Absolute Value

- Compare

- Conversion to and from two's complement integer

- Performs 2-A to support Newton-Raphson division

- · Low-power (500mW typical per device) operation

- Single 5 volt supply—no need for two supplies

- Advanced CEMOS<sup>™</sup> technology

- Flexible system design

- Three 32-bit ports allow two data inputs and one resoutput every clock cycle

- One, two or three port architectures support

- Single phase, edge-triggered clock interfactoring registered TTL-compatible inputs and puts.

- Full commercial and military ranges available

- Standard 144-pin grid array packa

- Pin and functionally compatit

## **DESCRIPTION:**

The IDT721264 floating-point multiplier and the IDT721265 floating-point ALU provide high speed 32-bit and 64-bit floating-point processing capability.

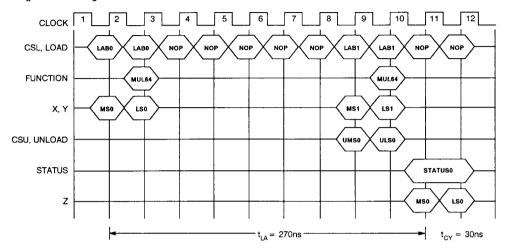

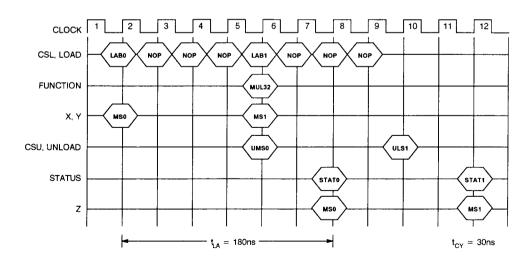

The IDT721264/65 are abricated using IDT's advanced CEMOS technology and are a pable of a total flow-through multiply latency (time require from the input of the operand until the result can be used by a considerable of 180ns for single precision and 270ns for doubt recision multiplications. This ultra-high-speed performance is a considerable over the combining both state-of-the-art CEMOS technology and as inced circuit design techniques.

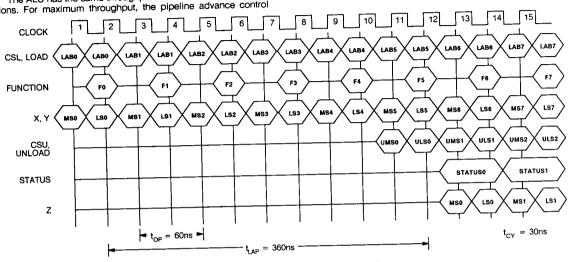

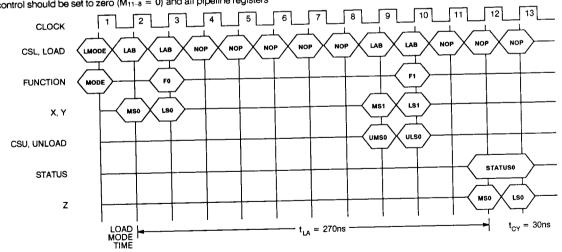

applications, where higher throughout For signal ations including the function specificaspeeds are rec or single precision multiplications, new tion can b d and a product unloaded every 60ns, while operands c multiplies can be accomplished at a 120ns double 1265 ALU executes all operations at a 60ns rating. put. All operations, including the function specire pipelined so there is no penalty for interleaving various e on-chip pipeline is automatically advanced, using ar inners, so explicit pipeline flushing is not required.

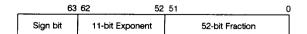

Mexible two-chip set operates in full conformance with the uirements of IEEE standard 754, 1985 version. It performs opens on single (32-bit) and double (64-bit) precision operands, as Well as conversion to 32-bit two's complement integers (IDT721265 only). The IDT721264/65 accommodates all rounding nodes, infinity and reserved operand representations and the treatment of exceptions such as overflow, underflow, invalid and inexact operations. Exact conformance to the standards ensures complete software portability between prototype development and final application. A "FAST" mode eliminates the time penalty for denormalized numbers by substituting zero for a denormalized number.

The flexible input/output architecture of these devices allows them to be used in systems with one, two or three 32-bit buses, or one 64-bit bus. Fully registered inputs and outputs, separately controlled, are loaded on each rising edge of the clock.

A 64-bit function control determines the arithmetic function to be performed while a 4-bit status output flags arithmetic exceptions and conditions. Both the function inputs and status outputs propagate along with the data to ease system design timing.

Military grade product is manufactured in compliance with the latest revision of MIL-STD-883C, Class B.

CEMOS is a trademark of Integrated Device Technology, Inc.

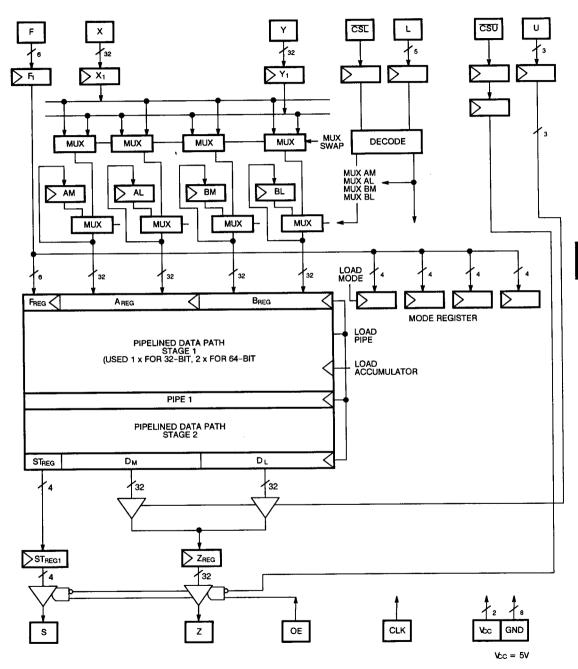

# FUNCTIONAL BLOCK DIAGRAM IDT721264 FLOATING-POINT MULTIPLIER

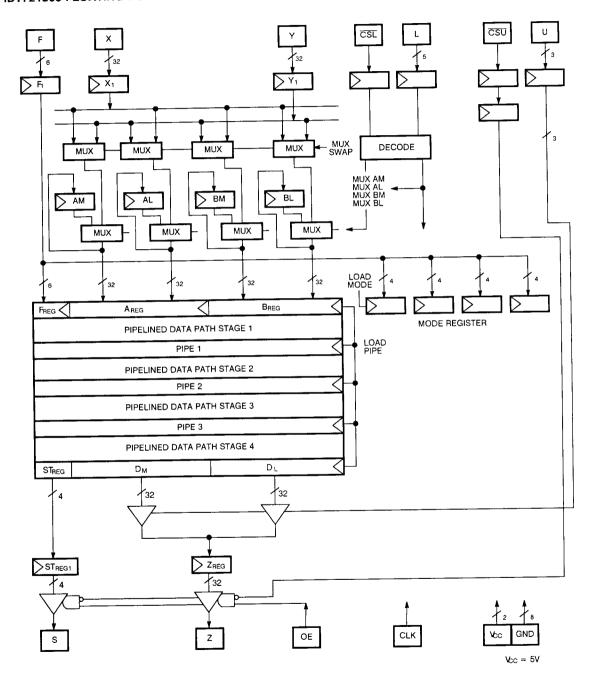

# FUNCTIONAL BLOCK DIAGRAM IDT721265 FLOATING-POINT ALU

# 7

### **PIN CONFIGURATION**

| 15 | GND             | Yo              | Y <sub>17</sub> | Y <sub>18</sub> | Y <sub>4</sub> | Y <sub>21</sub> | Y <sub>6</sub>  | Y <sub>7</sub>  | Y <sub>24</sub> | Y <sub>9</sub>  | Y <sub>11</sub> | Y <sub>12</sub> | Y <sub>28</sub> | Y <sub>30</sub> | GND             |

|----|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 14 | Z <sub>1</sub>  | V <sub>CC</sub> | GND             | Y <sub>16</sub> | Y <sub>2</sub> | Y <sub>19</sub> | Y <sub>20</sub> | Y <sub>22</sub> | Y <sub>25</sub> | Y <sub>10</sub> | Y <sub>27</sub> | Y <sub>13</sub> | Y <sub>14</sub> | NC              | X <sub>0</sub>  |

| 13 | Z <sub>3</sub>  | Z <sub>17</sub> | Z <sub>0</sub>  | NC              | Y <sub>1</sub> | Y <sub>3</sub>  | Y <sub>5</sub>  | Y <sub>23</sub> | Y <sub>8</sub>  | Y <sub>26</sub> | Y <sub>29</sub> | Y <sub>15</sub> | Y <sub>31</sub> | NC              | X <sub>17</sub> |

| 12 | Z <sub>19</sub> | Z <sub>18</sub> | Z <sub>16</sub> |                 |                |                 |                 |                 |                 |                 |                 |                 | NC              | X <sub>16</sub> | X <sub>18</sub> |

| 11 | Z <sub>20</sub> | Z <sub>4</sub>  | Z <sub>2</sub>  |                 |                |                 |                 |                 |                 |                 |                 |                 | X <sub>1</sub>  | X <sub>2</sub>  | X <sub>4</sub>  |

| 10 | Z <sub>22</sub> | Z <sub>21</sub> | Z <sub>5</sub>  |                 |                |                 |                 |                 |                 |                 |                 |                 | Х3              | X <sub>19</sub> | X <sub>21</sub> |

| 9  | Z <sub>7</sub>  | Z <sub>6</sub>  | Z <sub>23</sub> |                 |                |                 |                 |                 |                 |                 |                 |                 | X <sub>5</sub>  | X <sub>20</sub> | X <sub>6</sub>  |

| 8  | Z <sub>24</sub> | Z <sub>9</sub>  | Z <sub>8</sub>  |                 |                |                 |                 | G144-1          |                 |                 |                 |                 | X <sub>23</sub> | X <sub>22</sub> | X <sub>7</sub>  |

| 7  | Z <sub>25</sub> | Z <sub>11</sub> | Z <sub>26</sub> |                 |                |                 |                 |                 |                 |                 |                 |                 | X <sub>8</sub>  | X <sub>25</sub> | X <sub>24</sub> |

| 6  | Z <sub>10</sub> | Z <sub>12</sub> | Z <sub>28</sub> |                 |                |                 |                 |                 |                 |                 |                 |                 | X <sub>26</sub> | X <sub>10</sub> | Χg              |

| 5  | Z <sub>27</sub> | Z <sub>29</sub> | Z <sub>30</sub> |                 |                |                 |                 |                 |                 |                 |                 |                 | X <sub>29</sub> | X <sub>27</sub> | X <sub>11</sub> |

| 4  | Z <sub>13</sub> | Z <sub>15</sub> | NC              |                 |                |                 |                 |                 |                 |                 |                 |                 | X <sub>15</sub> | X <sub>13</sub> | X <sub>12</sub> |

| 3  | Z <sub>14</sub> | v <sub>cc</sub> | NC              | NC              | S <sub>1</sub> | U <sub>1</sub>  | NC              | GND             | F <sub>1</sub>  | L <sub>4</sub>  | Lo              | NC              | X <sub>31</sub> | X <sub>14</sub> | X <sub>28</sub> |

| 2  | Z <sub>31</sub> | NC              | S <sub>2</sub>  | S <sub>0</sub>  | csu            | Uo              | CLK             | F <sub>4</sub>  | Fo              | NC              | L <sub>2</sub>  | NC              | GND             | NC              | X <sub>30</sub> |

| 1  | GND             | S <sub>3</sub>  | GND             | OE              | U <sub>2</sub> | NC              | NC              | F <sub>5</sub>  | F <sub>3</sub>  | F <sub>2</sub>  | NC              | L <sub>3</sub>  | L1              | CSL             | GND             |

|    | A               | В               | С               | D               | Ε              | F               | G               | н               | J               | К               | L               | М               | N               | Р               | R               |

PIN 1 DESIGNATOR

PIN GRID ARRAY TOP VIEW

# ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| TBIAS             | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to + 155 | °C   |

| lout              | DC Output Current                          | 50           | 50           | mA   |

### NOTE:

# RECOMMENDED DC OPERATING CONDITIONS

| SYMBOL           | PARAMETER                 | MIN. | TYP. | MAX. | UNIT |

|------------------|---------------------------|------|------|------|------|

| V <sub>ССМ</sub> | Military Supply Voltage   | 4.5  | 5.0  | 5.5  | ν_   |

| Vcc              | Commercial Supply Voltage | 4.75 | 5.0  | 5.25 | ٧    |

| GND              | Supply Voltage            | 0    | 0    | 0    | ٧    |

| V <sub>IH</sub>  | Input High Voltage        | 2.0  | _    |      | ٧    |

| V <sub>IL</sub>  | Input Low Voltage         | -    | _    | 0.8  | V    |

#### NOTE:

# DC ELECTRICAL CHARACTERISTICS

(Commercial Vcc = 5V  $\pm$  5%, TA = 0°C to 70°C, Military Vcc = 5V  $\pm$ 10%, TA = -55°C to +125°C)

| SYMBOL                   | PARAMETER                            | TEST CONDITIONS                                                                               | COMM<br>MIN. | ERCIAL<br>MAX. | MILI | TARY<br>MAX. | UNIT   |

|--------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|--------------|----------------|------|--------------|--------|

| l <sub>lu</sub> l        | Input Leakage Current                | $V_{CC} = Max., V_{IN} = 0 \text{ to } V_{CC}$                                                | T            | 10             |      | 20           | μA     |

| ll <sub>LO</sub> I       | Output Leakage Current               | Hi Z, Vcc = Max., VouT = 0 to Vcc                                                             | _            | 10             | -    | 20           | μA     |

| 1 <sub>cc</sub> (1)      | Operating Power Supply Current       | Outputs Open, V <sub>CC</sub> = Max.                                                          | -            | 100            | _    | 120          | mA     |

| l <sub>cco</sub>         | Quiescent Power Supply Current       | $V_{\text{IN}} \ge V_{\text{CC}} - 0.2V, V_{\text{IN}} \le 0.2V, V_{\text{CC}} = \text{Max}.$ | -            | 5              | _    | 5            | mA     |

| I <sub>CC</sub> /f (1.2) | Increase in Power Supply Current/MHz |                                                                                               | -            | 4              | -    | 6            | mA/MHz |

| V <sub>OH</sub>          | Output High Voltage                  | Vcc = Min., loH = -2.0mA                                                                      | 2.4          |                | 2.4  | -            | ٧      |

| V <sub>OL</sub>          | Output Low Voltage                   | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8mA                                                 | -            | 0.4            |      | 0.4          | V      |

1. loc is measured at 10MHz and V<sub>IN</sub> = TTL voltages. For frequencies greater than 10MHz, the following equation is used for the commercial range: loc = 100 + 4(f-10)mA, where f = operating frequency in MHz. For the military range, loc = 120 + 6(f-10) where f = operating frequency in MHz.

2. For frequencies greater than 10MHz.

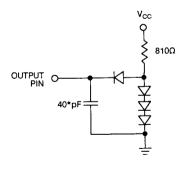

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 3ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 1 |

| Oupar 2002                    |              |

\*Includes scope and jig.

Figure 1. Output Load

NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1, 1.5</sup>V under shoots are allowed for 10ns once per cycle.

### **OPERATING CONDITIONS**

(Commercial  $V_{CC} = 5V \pm 5\%$ ,  $T_A = 0$ °C to 70°C, Military  $V_{CC} = 5V \pm 10\%$ ,  $T_A = -55$ °C to + 125°C)

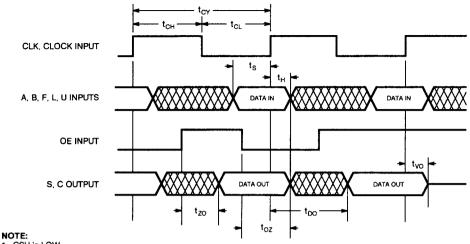

| SYMBOL          | PARAMETER         | t <sub>CY</sub> :<br>MIN. | = 30ns<br>MAX. | t <sub>CY</sub> = | = 40ns<br>MAX. | t <sub>CY</sub> = | 50ns<br>MAX. | t <sub>CY</sub> = | 60ns<br>MAX. | UNIT |

|-----------------|-------------------|---------------------------|----------------|-------------------|----------------|-------------------|--------------|-------------------|--------------|------|

| t <sub>CY</sub> | Clock Cycle Time  | 30                        | _              | 40                | -              | 50                | _            | 60                |              | ns   |

| t <sub>CH</sub> | Clock HIGH Time   | 12                        |                | 15                | -              | 20                |              | 25                |              | ns   |

| t <sub>CL</sub> | Clock LOW Time    | 12                        | _              | 15                |                | 20                |              | 25                | -            | ns   |

| ts              | Input Set-up Time | 11                        | -              | 13                |                | 15                | _            | 15                | -            | ns   |

| t <sub>H</sub>  | Input Hold Time   | 2                         | _              | 3                 | _              | . 3               |              | 3                 | _            | ns   |

### **AC ELECTRICAL CHARACTERISTICS**

(Commercial  $V_{CC} = 5V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ , Military  $V_{CC} = 5V \pm 10\%$ ,  $T_A = -55^{\circ}C$  to

| SYMBOL                    | PARAMETER                                                                                                                                                    | t <sub>CY</sub><br>MIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | = 30ns<br>MAX.    | t <sub>CY</sub> :<br>MIN. | = 40ns<br>M       | t <sub>CY</sub><br>MIN. | MAX.              | t <sub>CY</sub><br>MIN. | = 60ns<br>MAX.    | UNIT           |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------|-------------------|-------------------------|-------------------|-------------------------|-------------------|----------------|

| t <sub>DO</sub>           | Output Delay Time                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                | -                         |                   |                         | 35                | _                       | 35                | ns             |

| t <sub>VO</sub>           | Output Data Valid                                                                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                 | 5                         |                   |                         |                   | 5                       |                   | ns             |

| toz                       | Output Disable Time                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                | -                         | 3                 |                         | 35                |                         | 35                | ns             |

| t <sub>zo</sub>           | Output Enable Time                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                | _                         |                   | _                       | 35                | _                       | 35                | ns             |

| t <sub>LA</sub>           | Total Latency Time IDT721265 ALU All Functions IDT721264 MPY 32-Bit Functions IDT721264 MPY 64-Bit Functions                                                 | 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 270<br>186<br>70  |                           | 360<br>240<br>360 | 111                     | 450<br>300<br>450 | 1 1 1                   | 540<br>360<br>540 | ns<br>ns<br>ns |

| t <sub>OP</sub>           | Pipelined Time per Stage<br>IDT721265 ALU All Functions<br>IDT721264 MPY 32-Bit Functions<br>IDT721264 MPY 64-Bit Functions                                  | -<br>-<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60<br>60<br>60    | 1                         | 80<br>80<br>160   | 111                     | 100<br>100<br>200 | 1 -                     | 120<br>120<br>240 | ns<br>ns<br>ns |

| t <sub>LAP</sub>          | Pipelined Total Latency IDT721265 ALU All Functions IDT721264 MPY 32-Bit Functions IDT721264 MPY 64-Bit Functions                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 360<br>210<br>300 | _<br>_<br>_               | 480<br>280<br>400 |                         | 600<br>350<br>500 | 1 1 1                   | 720<br>420<br>600 | ns<br>ns<br>ns |

| Array Time<br>(IDT721265) | A, B register to Z register, pipeline registers transparent                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100               | -                         | 120               | _                       | 150               | -                       | 180               | ns             |

| Array Time<br>(IDT721264) | Time to Make One Pass Throt<br>Multiplier Array for 64-Bit or 32                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                | _                         | 80                | _                       | 100               | ı                       | 120               | ns             |

| t <sub>P64</sub>          | Time for a 64-Bit Result to from the Pipeline Register to be Input Register of the Z-Reg Transparent)                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90                | ı                         | 120               | -                       | 150               | l                       | 180               | ns             |

| t <sub>P32</sub>          | Time for a 32-5 deep go from the Pipeline Region of the DM,                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                | -                         | 80                | _                       | 100               | -                       | 120               | ns             |

| t <sub>FLOW64</sub>       | Time Require 64-Bit Data to Make One Part Strong to Array and the Transcript Peline Registers and Transcript DL to the Input of the                          | and the same of th | 120               | -                         | 160               |                         | 200               | -                       | 240               | ns             |

| t <sub>FLOW32</sub>       | Requed for 32-Bit Data to Make<br>One Pass Through the Array and the<br>ransparent Pipeline Registers and<br>Transparent DM, DL to the Input of<br>the Z-Req | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 120               | _                         | 160               | _                       | 200               | -                       | 240               | ns             |

### SIGNAL DESCRIPTIONS:

### INPUTS:

X<sub>0-31</sub> (Input Operand) X operand inputs, 32-bit.

Y<sub>0-31</sub> (Input Operand) Y operand inputs, 32-bit.

### CONTROL:

### Lo-4 (Load Control)

The input configuration of the IDT721264 and IDT721265 can be configured through the use of the 5-bit load control to specify the destination of the data from the X and Y inputs to the AM, AL, BM, BL registers or the arithmetic array.

### F<sub>0-5</sub> (Function Control)

The function configuration of the IDT721264 and IDT721265 can be configured through the use of the 6-bit function control to specify the operation to be performed. See Tables 3 and 4 for the specific function controls for the multiplier and ALU.

### U<sub>0-2</sub> (Unload Control)

The unload control  $(U_{0-2})$  chooses the source of the output.

### CSL (Input Enable)

When CSL is low, input ports X and Y are enabled. Input data buses may be shared with the ALU and multiplier with CSL.

### CSU (Synchronous Output Enable)

When  $\overline{\text{CSU}}$  is low, output port Z is enabled. Therefore, microcode can control the three-stating of the Z output. Since  $\overline{\text{CSL}}$  is pipelined, it takes effect 2 clock cycles after it is asserted.

### OE (Asynchronous Output Enable)

When  $\overline{OE}$  is high, output port Z is enabled. When  $\overline{OE}$  is high, the Z output is enabled if  $\overline{CSU}$  is low.

### CLK (Clock)

The clock input.

### OUTPUTS:

### Z<sub>0-31</sub> (Result)

The Z result output, 32-bit, three-state.

### S<sub>0-3</sub> (Status)

The 4-bit status output indicates any exceptions which resulted from multiplier or ALU operations.

### POWER SUPPLY:

### V<sub>CC</sub> (Power Supply)

Two power supply pins, 5V.

### GND (Ground)

Eight ground pins, 0V.

### GENERAL OPERATING MODES

Both the Multiplier and the ALU are architected identically with two input ports and one output port that surround the pipelined arithmetic array. The function control (6-bits) controls the selection of the arithmetic operations with the input and output ports controlled by a total of 8 bits of the load and unload control registers.

### INPUT PORTS

The IDT721264 multiplier and the IDT721265 ALU have identical input and control structures that handle data on two 32-bit buses (X and Y). The on-chip registers (AL, AM, BL, BM) can be written from either of the buses or data can be passed from the inputs directly into the arithmetic unit.

Both devices can be used in a range of bus configurations for operations in both 32-bit and 64-bit by configuring the input data in combination with the high bandwidth output. Transfers of data input and output can be made at twice the pipeline rate. The input buses are fully registered and can be configured for one or two 32-bit inputs or one 64-bit output. These registers are loaded on each LOW-to-HIGH transition of the clock provided  $\overline{\text{CSL}}$  is held LOW.

### LOAD CONTROL

The Load Control ( $L_{0-4}$ ) is used to transfer data from the input ports to the internal registers or the arithmetic array. Lo controls the initiation of an operation. When this input is LOW only a data transfer occurs while, when it is held HIGH, data is transferred and an operation is begun. The sequence of events is as follows: two registers (AREG and BREG) are loaded from the specified AL, AM, BL, BM register and the X and Y ports and the FREG is loaded from port F while, on the next cycle, the specified operation in the FREG begins with the data already loaded into the AREG and BREG. The X and Y ports can be used as single operand operations and must be loaded into the AREG. The configuration of these ports can be accomplished by using the Mode bits  $M_{15}$  and  $M_{14}$  for 16-, 32- and 64-bit data. The most significant halves of the AREG and BREG must be loaded with any 32-bit operands.

### **UNLOAD CONTROL**

The Unload Control ( $U_{0-2}$ ) chooses whether the DM or DL register is sent to the Z register. The DM register stores the result of 32-bit floating-point operations. With 64-bit operations, the most significant 32 bits are stored in the DM register; the least significant half is stored in the DL register. A 32-bit result is sent from the Z register to the Z output port on each clock cycle.

### **TABLE 1. LOAD CONTROL TRUTH TABLE**

| IABLE          | I. LUAL        | CONT           | NOL II         | 1011117 | ADLL |                                                                                                                       |

|----------------|----------------|----------------|----------------|---------|------|-----------------------------------------------------------------------------------------------------------------------|

| L <sub>4</sub> | L <sub>3</sub> | L <sub>2</sub> | L <sub>1</sub> | Lo      |      | LOAD OPERATION                                                                                                        |

| 0              | 0              | 0              | 0              | 0       | (0)  | (NOP)                                                                                                                 |

| 0              | 0              | 0              | 0              | 1       | (1)  | AM, AL → AREG; BM, BL → BREG; F1 → FREG                                                                               |

| 0              | 0              | 0              | 1              | 0       | (2)  | Load Mode                                                                                                             |

| 0              | 0              | 0              | 1              | 1       | (3)  | - Reserved                                                                                                            |

| 0              | 0              | 1              | 0              | 0       | (4)  | Y1 → AL; X1 → BL                                                                                                      |

| 0              | 0              | 1              | 0              | 1       | (5)  | $Y1 \rightarrow AL; X1 \rightarrow BL; AM, Y1 \rightarrow AREG; BM, X1 \rightarrow BREG; F1 \rightarrow FREG$         |

| 0              | 0              | 1              | 1              | 0       | (6)  | Y1 → AM; X1 → BM                                                                                                      |

| 0              | 0              | 1              | 1              | 1       | (7)  | Y1 $\rightarrow$ AM; X1 $\rightarrow$ BM; Y1, AL $\rightarrow$ AREG; X1, BL $\rightarrow$ BREG; F1 $\rightarrow$ FREG |

| 0              | 1              | 0              | 0              | 0       | (8)  | X1 → BM; Y1 → BL                                                                                                      |

| 0              | 1              | 0              | 0              | 1       | (9)  | $X1 \rightarrow BM; Y1 \rightarrow BL; AM, AL \rightarrow AREG; X1, Y1 \rightarrow BREG; F1 \rightarrow FREG$         |

| 0              | 1              | 0              | 1              | 0       | (10) | $X1 \rightarrow AM; Y1 \rightarrow AL$                                                                                |

| 0              | 1              | 0              | 1              | 1       | (11) | $X1 \rightarrow AM; Y1 \rightarrow AL; X1, Y1 \rightarrow AREG; BM, BL \rightarrow BREG; F1 \rightarrow FREG$         |

| 0              | 1              | 1              | 0              | 0       | (12) | $X1 \rightarrow AL; Y1 \rightarrow BL$                                                                                |

| 0              | 1              | 1              | 0              | 1       | (13) | $X1 \rightarrow AL; Y1 \rightarrow BL; AM, X1 \rightarrow AREG; BM, Y1 \rightarrow BREG; F1 \rightarrow FREG$         |

| 0              | 1              | 1              | 1              | 0       | (14) | $X1 \rightarrow AM; Y1 \rightarrow BM$                                                                                |

| 0              | 1              | 1              | 1              | 1       | (15) | $X1 \rightarrow AM; Y1 \rightarrow BM; X1, AL \rightarrow AREG; Y1, BL \rightarrow BREG; F1 \rightarrow FREG$         |

| 1              | 0              | 0              | 0              | 0       | (16) | Y1 → BM                                                                                                               |

| 1              | 0              | 0              | 0              | 1       | (17) | Y1 $\rightarrow$ BM; AM, AL $\rightarrow$ AREG; Y1, BL $\rightarrow$ BREG; F1 $\rightarrow$ FREG                      |

| 1              | 0              | 0              | 1              | 0       | (18) | Y1 → BL                                                                                                               |

| 1              | 0              | 0              | 1              | 1       | (19) | Y1 $\rightarrow$ BL; AM, AL $\rightarrow$ AREG; BM, Y1 $\rightarrow$ BREG; F1 $\rightarrow$ FREG                      |

| 1              | 0              | 1              | 0              | 0       | (20) | Y1 → AL                                                                                                               |

| 1              | 0              | 1              | 0              | 1       | (21) | Y1 $\rightarrow$ AL; AM, Y1 $\rightarrow$ AREG; BM, BL $\rightarrow$ BREG; F1 $\rightarrow$ FREG                      |

| 1              | 0              | 1              | 1              | 0       | (22) | Y1 → AM                                                                                                               |

| 1              | 0              | 1              | 1              | 1       | (23) | Y1 → AM; Y1, AL → AREG; BM, BL → BREG; F1 → FREG                                                                      |

| 1              | 1              | 0              | 0              | 0       | (24) | X1 → BM                                                                                                               |

| 1              | 1              | 0              | 0              | 1       | (25) | $X1 \rightarrow BM$ ; AM, AL $\rightarrow$ AREG; X1, BL $\rightarrow$ BREG; F1 $\rightarrow$ FREG                     |

| 1              | 1              | 0              | 1              | 0       | (26) | X1 → BL                                                                                                               |

| 1              | 1              | 0              | 1              | 1       | (27) | $X1 \rightarrow BL$ ; AM, AL $\rightarrow$ AREG; BM, $X1 \rightarrow$ BREG; F1 $\rightarrow$ FREG                     |

| 1              | 1              | 1              | 0              | 0       | (28) | X1 → AL                                                                                                               |

| 1              | 1              | 1              | 0              | 1       | (29) | X1 → AL; AM, X1 → AREG; BM, BL → BREG; F1 → FREG                                                                      |

| 1              | 1              | 1              | 1              | 0       | (30) | X1 → AM                                                                                                               |

| 1              | 1              | 1              | 1              | 1       | (31) | X1 → AM; X1, AL → AREG; BM, BL → BREG; F1 → FREG                                                                      |

|                |                |                |                |         |      |                                                                                                                       |

### **LOAD SEQUENCES**

### 32-BIT OPERATIONS WITH TWO 32-BIT PORTS

| OPERATION                                                                                                             | L4 | Lз | L2 | Ŀ | Lo | INST# |

|-----------------------------------------------------------------------------------------------------------------------|----|----|----|---|----|-------|

| LOAD MODE(1)                                                                                                          | 0  | 0  | 0  | 1 | 0  | (2)   |

| Y1, AL $\rightarrow$ AREG; X1, BL $\rightarrow$ BREG; F1 $\rightarrow$ FREG; Y1 $\rightarrow$ AM; X1 $\rightarrow$ BM | 0  | 0  | 1  | 1 | 1  | (7)   |

### NOTE:

### 64-BIT OPERATIONS USING THE X AND Y PORTS AS A SINGLE 64-BIT PORT

| OPERATION                                                                                                             | L4 | La | L2 | Lı | Lo | INST# |

|-----------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|-------|

| LOAD MODE                                                                                                             | 0  | 0  | 0  | 1  | 0  | (2)   |

| X1 → AM; Y1 → AL                                                                                                      | 0  | 1  | 0  | 1  | 0  | (10)  |

| AM, AL $\rightarrow$ AREG; X1, Y1 $\rightarrow$ BREG; F1 $\rightarrow$ FREG; X1 $\rightarrow$ BM; Y1 $\rightarrow$ BL | 0  | 1  | 0  | 0  | 1  | (9)   |

If the mode does not change between operations, it does not need to be reloaded.

TABLE 2. UNLOAD CONTROL TRUTH TABLE

| CSU      | U <sub>2</sub>                                   | U <sub>1</sub> | Uo           | EDGE #1                                          | EDGE #2                                                                 |

|----------|--------------------------------------------------|----------------|--------------|--------------------------------------------------|-------------------------------------------------------------------------|

| 0        | n                                                | 0              | 0            | $DM_{31-0} \rightarrow ZREG$                     | STREG1 $\rightarrow$ S <sup>+</sup> , ZREG $\rightarrow$ Z <sup>+</sup> |

| 0        | 0                                                | 1              | 0            | DM <sub>31-16</sub> , DL <sub>31-16</sub> → ZREG | STREG1 $\rightarrow$ S <sup>+</sup> , ZREG $\rightarrow$ Z <sup>+</sup> |

| 0        | 1                                                | <u> </u>       | 0            | DL <sub>31-0</sub> → ZREG                        | STREG1 $\rightarrow$ S <sup>+</sup> , ZREG $\rightarrow$ Z <sup>+</sup> |

| 0        | <u></u>                                          |                |              | $DM_{15-0}$ , $DL_{15-0} \rightarrow ZREG$       | STREG1 $\rightarrow$ S <sup>+</sup> , ZREG $\rightarrow$ Z <sup>+</sup> |

| <u>-</u> | <del>                                     </del> |                | <del>_</del> |                                                  | S+ and Z+ Tri-Stated                                                    |

# TABLE 3. FUNCTION CONTROLS FOR FLOATING-POINT MULTIPLIER

| F <sub>2</sub> | F,           | F <sub>0</sub> |     | OPERATION  | MNEMONIC | DESCRIPTION                    |

|----------------|--------------|----------------|-----|------------|----------|--------------------------------|

| 0              | 0            | 0              | (0) | F32 x F32  | MUL32    | Single Multiply                |

| 0              |              | 1              | (1) | F64 x F64  | MUL64    | Double Multiply                |

| 0              | 1            | 0              | (2) | W32 x F32  | MULAW32  | Single Multiply, A Wrapped     |

| <del>-</del>   | <u>_</u>     | 1              | (3) | W64 x F64  | MULAW64  | Double Multiply, A Wrapped     |

| 1              | 0            | 0              | (4) | F32 x W32  | MULBW32  | Single Multiply, B Wrapped     |

| <u>-</u>       | 0            | 1              | (5) | F64 x W64  | MULBW64  | Double Multiply, B Wrapped     |

| 1              | 1            | 0              | (6) | W32 x W32  | MULABW32 | Single Multiply, A & B Wrapped |

| 1              | 1            | 1              | (7) | W64 x W64  | MULABW64 | Double Multiply, A & B Wrapped |

|                |              |                |     |            |          |                                |

| F <sub>5</sub> | F,           | F <sub>3</sub> | 1   | OPERATION  | MNEMONIC | DESCRIPTION                    |

| <u> </u>       | <del>_</del> | <del>0</del>   | (0) | AxB        | MUL      | Multiply                       |

| 0              | 0            | 1              | (1) | A  x B     | MULABSA  | B Times Magnitude of A         |

| 0              |              | 0              | (2) | A x  B     | MULABSB  | A Times Magnitude of B         |

| 0              | 1            | 1              | (3) | A  ×  B    | MULABSAB | Magnitude of A Times B         |

| 1              | 0            | 0              | (4) | -(A x B)   | MULNEG   | Multiply and Negate            |

| 1              | 0            |                | (5) | (- A ) x B | MULNEGA  | B Times Negative Value of A    |

| <u>.</u>       |              | 0              | (6) | A x (- B ) | MULNEGB  | A Times Negative Value of B    |

|                | •            |                |     |            | MULNEGAB | Negative Value of A Times B    |

### **MULTIPLIER OPERATION: IDT721264**

The IDT721264 has exception detection handling circuitry, a  $56 \times 28$ -bit multiplier array, an exponent adder circuit, a normalizing shifter and a rounding circuit for IEEE format adjustment.

The exception detection circuit is at the beginning of the multiplier. Exceptions can be Not-a-Number (NaN) or a denormalized input and timings are handled like normal numbers.

A clocked 54 x 28-bit multiplier array multiplies the mantissa portion of the floating-point number. A single precision multiply takes one pass through the array; a double precision multiply takes two passes. Each pass through the array takes two clock cycles.

Partial results are stored in the accumulator (an adder and a transparent latch). The cycle time determines the number of clock cycles required to complete a multiplication. A long cycle time requires fewer clock cycles to complete the operation. A clock time of 30ns calls for four cycles to perform a double precision multiply. In the first two clock cycles, the operands are multiplied in the array. On the second cycle, the accumulator register must be latched to retain the results. On the fourth cycle the accumulator register must be transparent so that the results are passed to the pipeline register. An accumulator timer can be set to latch or pass results one to four clock cycles after the beginning of the operation. The timer is reset at the beginning of each operation.

### MULTIPLIER FUNCTION CONTROL

The multiplier controls are given in Table 3. The multiplier functions can be considered briefly in the following manner:

| F <sub>5</sub> | F <sub>4</sub> | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| cs             | мв             | MA             | WB             | ВА             | SD             |

CS: 1-> Complement sign of result

MB: 1-> Magnitude of B

MA: 1-> Magnitude of A

WB: 1-> Operand B is wrapped

WA: 1-> Operand A is wrapped

SD: 0-> Single precision operationSD: 1-> Double precision operation

The Mode Control bits are loaded from the  $F_{0-3}$  function control bits. The  $F_{5-4}$  function control bits determine which of the four 4-bit mode control subsets is loaded.

|                | load control dabbata to roadea. |        |                        |  |

|----------------|---------------------------------|--------|------------------------|--|

| F <sub>5</sub> | F <sub>4</sub>                  | EDGE 0 | EDGE 1                 |  |

| 0              | 0                               | F → F1 | F → M <sub>3-0</sub>   |  |

| 0              | 1                               | F → F1 | F → M <sub>7-4</sub>   |  |

| 1              | 0                               | F → F1 | F → M <sub>11-8</sub>  |  |

| 1              | 1                               | F → F1 | F → M <sub>15-12</sub> |  |

### **MULTIPLIER MODE CONTROL**

### **IEEE OR FAST MODE**

Mode bit  $M_0$  controls the way denormalized numbers are handled. If  $M_0$  is 0, the IEEE format is used. The multiplier generates denormalized operand exceptions and produces UNRM values on underflow exceptions. The denormalized operands are sent to the ALU to be wrapped; the wrapped numbers (WNRMs) can then be multiplied. The IEEE Compatibility section discusses this in detail.

If M<sub>0</sub> is 1, the Fast mode is used in order to achieve the maximum performance, by eliminating the direct handling of denormalized numbers. The multiplier flushes denormalized

operands (DNRMs) to zero and rounds underflow or unnormalized results (UNRMs) to zero. Mode bit  $M_2$  must be set to zero in the Fast mode.

| Mo | DESCRIPTION |

|----|-------------|

| 0  | IEEE Mode   |

| 1  | Fast Mode   |

#### ROUNDING MODE

Mode bits  $M_1$ ,  $M_2$  and  $M_3$  select the Rounding mode. Renormalization and IEEE rounding functions are performed between the pipeline register and the DM and DL registers.

| M <sub>3</sub> | M <sub>2</sub> | DESCRIPTION                                                   |

|----------------|----------------|---------------------------------------------------------------|

| 0              | 0              | Round to nearest value or if a tie, round to even significand |

| 0              | 1              | Round to zero                                                 |

| 1              | 0              | Round towards positive infinity                               |

| 1              | 1              | Round towards negative infinity                               |

### PIPELINE CONFIGURATION

Mode bit  $M_4$  controls whether the DM and DL registers are transparent. Mode bit  $M_5$  controls whether the pipeline register is transparent.

|   | M <sub>4</sub> | DESCRIPTION        |

|---|----------------|--------------------|

|   | 0              | Transparent DM, DL |

|   | 1              | Latched DM, DL     |

| • |                |                    |

| M <sub>5</sub> | DESCRIPTION                   |

|----------------|-------------------------------|

| 0              | Transparent pipeline register |

| 1              | Latched pipeline register     |

### ACCUMULATOR ADVANCE CONTROL

Mode bits  $M_{7-6}$  control the timing of the partial product accumulator. The accumulator is alternately latched and made transparent every N+1 cycles, where N is the value of  $M_{7-6}$ . The accumulator timer is reset at the beginning of each operation. The accumulator timer is used to achieve maximum throughput.

| M <sub>7</sub> | M <sub>6</sub> | DESCRIPTION    |

|----------------|----------------|----------------|

| 0              | 0              | N = 1, Clock/1 |

| 0              | 1              | N = 2, Clock/2 |

| 1              | 0              | N = 3, Clock/3 |

| 1              | 1              | N = 4, Clock/4 |

### PIPELINE ADVANCE CONTROL

Mode bits  $M_{11-8}$  control the pipeline advance control of the pipeline registers. If  $M_{11-8}$  are all zeros, the pipeline registers will only be latched at the beginning of an operation. If  $M_{11-8}$  are non-zero values, N, the pipeline registers will be clocked at the beginning of every operation and every N cycles after the beginning of every operation. The internal pipeline advance timer is reset at the beginning of every operation.

For example, if N=4 and operations are started on cycles 0, 6 and 10, pipeline advances will occur on cycles 0, 4, 6, 10, 14, 18 and so on. The pipeline advance control is used to achieve maximum throughput.

7

| M <sub>11</sub> | M <sub>10</sub> | Mg       | M <sub>8</sub> | DESCRIPTION                                                                                    |  |

|-----------------|-----------------|----------|----------------|------------------------------------------------------------------------------------------------|--|

| 0               | 0               | 0        | 0              | N = 0, pipeline registers are latched                                                          |  |

| 0               | 0               | 0        | 1              | N = 1, pipeline registers are clocked<br>1 cycle after first operation                         |  |

| 0               | 0               | 1        | 0              | N = 2, pipeline registers are clocked<br>2 cycles after first operation                        |  |

| 0               | 0               | 1        | 1              | <ul><li>N = 3, pipeline registers are clocked</li><li>3 cycles after first operation</li></ul> |  |

|                 |                 | <u> </u> |                |                                                                                                |  |

|                 |                 |          |                |                                                                                                |  |

| 1               | 1               | 1        | 1              | N = 15, pipeline registers are clocked<br>15 cycles after first operation                      |  |

### **BUS BANDWIDTH CONTROL**

Mode bits  $M_{13-12}$  are not used. Mode bits  $M_{15-14}$  control the input bus bandwidth of the X and Y input ports. When  $M_{15-14}$  are set to zero, the X1 and Y1 registers are loaded every clock cycle from the X and Y ports.

| M 15 | M <sub>14</sub> | DESCRIPTION       | DATA PATH      |

|------|-----------------|-------------------|----------------|

| 0    | 0               | N = 1, 32-but bus | X-> X1; Y-> Y1 |

| 0    | 1               | N = 2, Reserved   |                |

| 1    | 0               | N = 3, Unused     |                |

| 1    | 1               | N = 4, Unused     |                |

## **ALU OPERATION: IDT721265**

The IDT721265 ALU has five basic components: exception detection circuitry, a shifter to normalize the smaller of the two input operands, a 57-bit adder, a shifter to renormalize the result and IEEE rounding circuitry. The IDT721265 is easily considered as an ALU with multiple internal pipeline registers. The internal pipeline registers and the DM and DL registers can be made transparent by mode bits M7-4.

The pipeline registers are clocked at the beginning of each operation and every N cycles thereafter, when N is given a value by mode bits M<sub>11-8</sub>.

## **ALU FUNCTION CONTROL**

The IDT721265's function controls are shown in Table 4. The IDT superset functions are highlighted in Table 5.

The Mode Control bits are loaded from the  $F_{3-0}$  function control bits. The  $F_{5-4}$  function control bits determine which of the four 4-bit mode control subsets is loaded.

| F <sub>5</sub> | F <sub>4</sub> | EDGE 0 | EDGE 1                  |

|----------------|----------------|--------|-------------------------|

| 0              | 0              | F → F1 | F1 → M <sub>3-0</sub>   |

| 0              | 1              | F → F1 | F1 → M <sub>7-4</sub>   |

| 1              | 0              | F → F1 | F1 → M <sub>11-8</sub>  |

| 1              | 1              | F → F1 | F1 → M <sub>15-12</sub> |

### ALU MODE CONTROL

### IEEE OR FAST MODE

Mode bit  $M_0$  controls the way denormalized numbers are handled. If  $M_0$  is 0, the IEEE format is used. The ALU generates denormalized operand exceptions and produces UNRM values on underflow exceptions. The IEEE Compatibility section discusses this in detail.

If  $M_0$  is 1, the Fast mode is used in order to achieve the maximum performance by eliminating the direct handling of denormalized numbers. The ALU flushes denormalized operands (UNRMs) to zero and rounds underflow or unnormalized results (UNRMs) to zero. Mode bit  $M_2$  must be set to zero in the Fast mode.

| Mo | DESCRIPTION |

|----|-------------|

| 0  | IEEE Mode   |

| 1  | Fast Mode   |

### **ROUNDING MODE**

Mode bits  $M_1$ ,  $M_2$  and  $M_3$  select the Rounding mode. Renormalization and IEEE rounding functions are performed between the pipeline register and the DM and DL registers.

| M <sub>3</sub> M <sub>2</sub> M <sub>1</sub> |   | M <sub>1</sub> | DESCRIPTION                                                   |  |

|----------------------------------------------|---|----------------|---------------------------------------------------------------|--|

| 0                                            | 0 | 0              | Round to nearest value or if a tie, round to even significand |  |