# **TN100**

## High performance CSS transceiver enabling location awareness

Preliminary Data

## Features

- Single-chip solution for ISM 2.45 GHz RF transceiver

- Built-in ranging capability for link distance estimation

- Modulation technique: chirp spread spectrum (CSS)

- FDMA support: 7 channels, 3 non-overlapping

- Data rates: 2 and 1 Mbps; 500, 250 and 125 kbps

- Adjustable output power from -33 dBm to 0 dBm

- Receiver sensitivity: -97 dBm @ 250 kbps, FEC, and BER=10-3

- In-band carrier-to-interference C/I = 0 to 3 dB

@ 250 kbps & C=-80 dBm

- Supports external power amplifier to increase output power

- High precision ranging: 2 m indoors and 1 m outdoors

- Supply voltage range from 2.3 V to 2.7 V

- Current consumption: 27 mA (RX), 30 mA (TX)

@ 0 dBm

- Standby current with active RTC: 2 µA

- RSSI sensitivity: -95 dBm

- 32.768 kHz clock available for external MCU

- Integrated fast SPI interface (27 Mbps)

- Integrated MAC controller with FEC, CRC checking

- CSMA/CA, FDMA, and TDMA modes

- Automatic retransmission and acknowledgement

- Automatic address matching

- Industrial temperature range from -40°C to +85°C

- VFQFPN2-48 ECOPACK® package

## Description

The TN100 transceiver is a highly integrated mixed signal chip that uses the wireless communication technology CSS (chirp spread spectrum) developed by Nanotron Technologies.

With its unique ranging capability, TN100 can measure the link distance between two nodes. Thus, TN100 supports location awareness applications including location based services (LBS) and asset tracking (2D/3D RTLS). Ranging is performed during regular data communication and does not require additional infrastructure, power, and/or bandwidth.

For an even better ranging accuracy, a high precision mode is provided. SDS-TWR algorithm (symmetrical double-sided two-way ranging) allows superior accuracy even with the use of low cost crystals for the oscillators.

September 2008

Rev 1

## Contents

| Summary description |                                                                                                                                                                                                                                                                                                 |                                                    |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| TN1                 | 00 block diagram                                                                                                                                                                                                                                                                                | 14                                                 |  |  |  |

| Кеу                 | Key features                                                                                                                                                                                                                                                                                    |                                                    |  |  |  |

| 3.1                 | Built-in ranging capability                                                                                                                                                                                                                                                                     | 15                                                 |  |  |  |

| 3.2                 | Channelization using FDMA for improved coexistence                                                                                                                                                                                                                                              | 15                                                 |  |  |  |

| 3.3                 | Incorporated digital dispersive delay-line (DDDL)                                                                                                                                                                                                                                               | 15                                                 |  |  |  |

| 3.4                 | Selectable symbol durations and symbol rates                                                                                                                                                                                                                                                    | 15                                                 |  |  |  |

| Arch                | nitecture                                                                                                                                                                                                                                                                                       | 16                                                 |  |  |  |

| 4.1                 | Analog part - TX and RX                                                                                                                                                                                                                                                                         | 16                                                 |  |  |  |

| 4.2                 | Digital part - programming interface                                                                                                                                                                                                                                                            | 16                                                 |  |  |  |

|                     | 4.2.1 Digital part – ON Section                                                                                                                                                                                                                                                                 | 16                                                 |  |  |  |

|                     | 4.2.2 Digital part – PWD section                                                                                                                                                                                                                                                                | 16                                                 |  |  |  |

| 4.3                 | Signal flow                                                                                                                                                                                                                                                                                     | 17                                                 |  |  |  |

| 4.4                 | Commonly used set of register default values                                                                                                                                                                                                                                                    | 17                                                 |  |  |  |

| 4.5                 | Programmable pull-resistors                                                                                                                                                                                                                                                                     | 17                                                 |  |  |  |

| Pino                | Pin description                                                                                                                                                                                                                                                                                 |                                                    |  |  |  |

| 5.1                 | Input and/or output pins                                                                                                                                                                                                                                                                        | 20                                                 |  |  |  |

| 5.2                 | Configuring the digital I/O pins – D0 to D3 (pins 19 to 22)                                                                                                                                                                                                                                     | 21                                                 |  |  |  |

| 5.3                 | Configuring the IRQ Pin – $\mu$ CIRQ (pin 27)                                                                                                                                                                                                                                                   | 22                                                 |  |  |  |

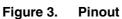

| 5.4                 | Power-on reset – /POnReset (pin 30)                                                                                                                                                                                                                                                             | 22                                                 |  |  |  |

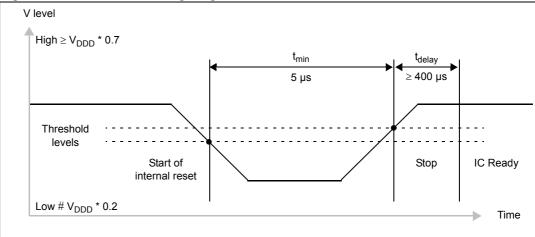

| Mem                 | nory map                                                                                                                                                                                                                                                                                        | 23                                                 |  |  |  |

| 6.1                 | Selecting a memory address                                                                                                                                                                                                                                                                      | 24                                                 |  |  |  |

| 6.2                 | 128-byte programmable register block                                                                                                                                                                                                                                                            | 25                                                 |  |  |  |

|                     | 6.2.1 Accessing a register address location                                                                                                                                                                                                                                                     | 25                                                 |  |  |  |

|                     | 6.2.2 Setting a shadow variable for the RAM access register                                                                                                                                                                                                                                     | 26                                                 |  |  |  |

| 6.3                 | Correlator RAM access                                                                                                                                                                                                                                                                           | 26                                                 |  |  |  |

| 6.4                 | Chirp sequencer RAM access                                                                                                                                                                                                                                                                      | 26                                                 |  |  |  |

|                     | <ul> <li>TN1</li> <li>Key</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Arch</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>Pin of</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Mem</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | <ul> <li>3.1 Built-in ranging capability</li></ul> |  |  |  |

| 7 | Clocking structure |           |                                                                              |  |

|---|--------------------|-----------|------------------------------------------------------------------------------|--|

|   | 7.1                | Overview  |                                                                              |  |

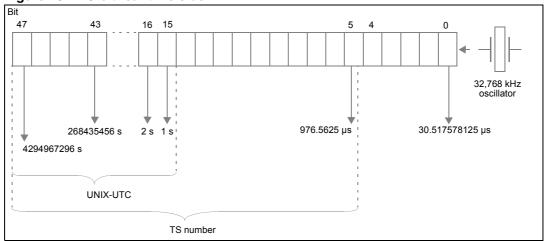

|   | 7.2                | 32.786 kH | Hz real-time clock (RTC)                                                     |  |

|   |                    | 7.2.1 l   | Jpdating and reading the RTC through software                                |  |

|   |                    | 7.2.2 N   | Manually or automatically updating the RTC using TimeB packets $\ldots$ . 29 |  |

|   |                    | 7.2.3 l   | Jsing the RTC as wake-up event                                               |  |

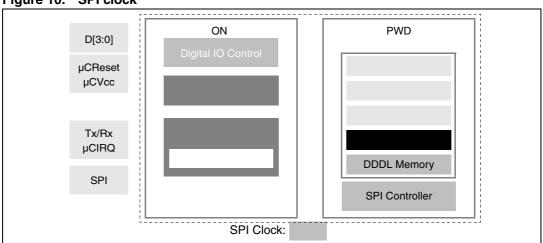

|   | 7.3                | SPI clock |                                                                              |  |

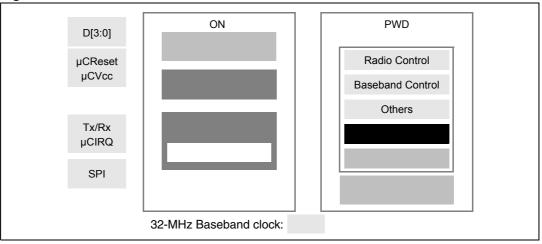

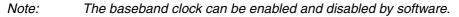

|   | 7.4                | 32-MHz b  | aseband clock                                                                |  |

|   |                    | 7.4.1     | Stopping / enabling the 32-MHz baseband clock                                |  |

|   | 7.5                | CSQ (Chi  | irp Sequencer) clock                                                         |  |

|   |                    | 7.5.1 \$  | Stopping / enabling the Chirp Sequencer clock (CSQ)                          |  |

|   |                    | 7.5.2 l   | Jsing the default matrix for transmission                                    |  |

| 8 | Powe               | r manage  | ement                                                                        |  |

|   | 8.1                | Power ma  | anagement states 34                                                          |  |

|   | 8.2                | Power ma  | anagement module – ON and PWD sections                                       |  |

|   | 8.3                | Power ma  | anagement state model                                                        |  |

|   | 8.4                | Power ma  | anagement fields                                                             |  |

|   | 8.5                | PowerDov  | wnModeFull state                                                             |  |

|   | 8.6                | PowerDov  | wnModePad state                                                              |  |

|   | 8.7                | PowerUp   | state                                                                        |  |

|   | 8.8                | Standby s | state                                                                        |  |

|   | 8.9                | Ready sta | ate                                                                          |  |

|   | 8.10               | Powering  | off the chip                                                                 |  |

| 9 | Progr              | ammina    | interface (SPI)                                                              |  |

| Ū | 9.1                | •         | oller                                                                        |  |

|   | 5.1                |           | SPI controller and power management                                          |  |

|   |                    |           | SPI controller and registers                                                 |  |

|   | 9.2                |           | dering                                                                       |  |

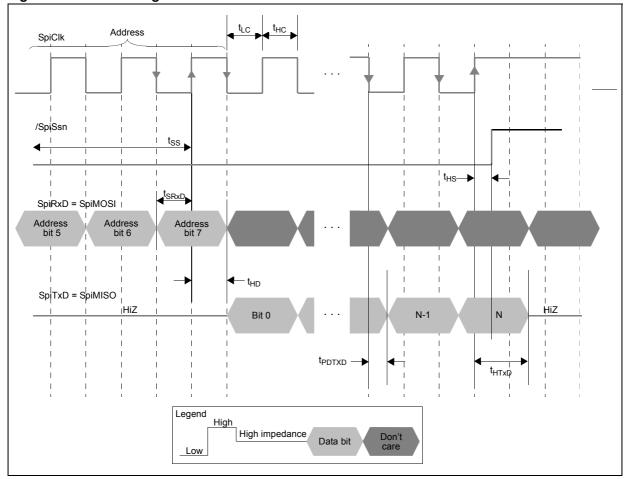

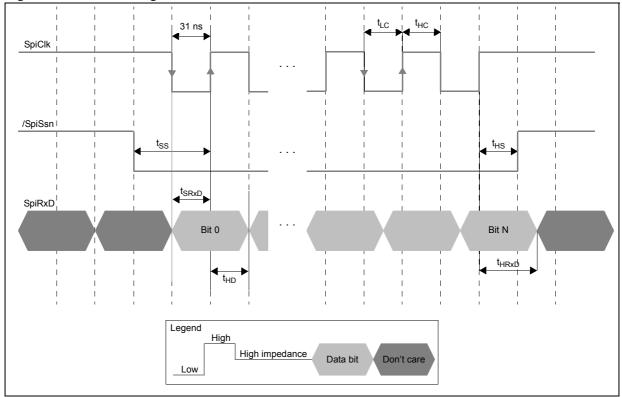

|   | 9.3                |           | .ls: SpiClk, SpiSsn, SpiTxD, SpiRxD                                          |  |

|   | 9.4                | -         | output driver                                                                |  |

|   | 9.5                |           | ming values                                                                  |  |

|   | 9.6                |           | fer rate                                                                     |  |

|   | 0.0                |           | Aaximum transfer rate                                                        |  |

|   |                    |           |                                                                              |  |

|    |       | 9.6.2          | Bytes per transfer                            |  |  |

|----|-------|----------------|-----------------------------------------------|--|--|

|    | 9.7   | SPI inte       | rface connections 45                          |  |  |

|    |       | 9.7.1          | Four-wire configuration                       |  |  |

|    |       | 9.7.2          | Three-wire configuration                      |  |  |

|    |       | 9.7.3          | Multiple slave configuration                  |  |  |

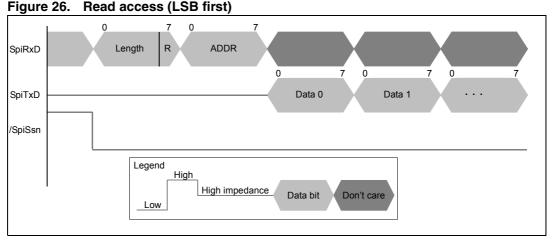

|    | 9.8   | Read tir       | ning of the SPI bus                           |  |  |

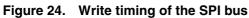

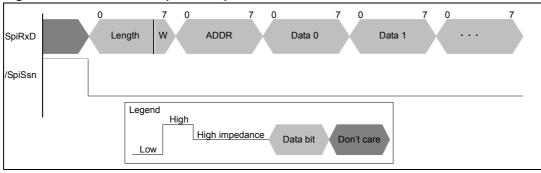

|    | 9.9   | Write tin      | ning of the SPI bus                           |  |  |

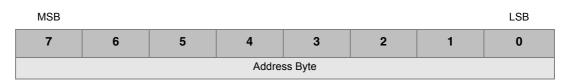

|    | 9.10  | SPI add        | ress format                                   |  |  |

|    |       | 9.10.1         | Byte 1: instruction                           |  |  |

|    |       | 9.10.2         | Byte 2: address                               |  |  |

|    |       | 9.10.3         | N Bytes: data payload                         |  |  |

|    | 9.11  | SPI read       | d operations                                  |  |  |

|    | 9.12  | SPI writ       | e operations                                  |  |  |

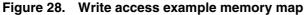

|    |       | 9.12.1         | Write access example                          |  |  |

| 10 | Chirp | sequer         | ncer (CSQ)                                    |  |  |

|    | 10.1  | Purpose        | e of the Chirp sequencer 53                   |  |  |

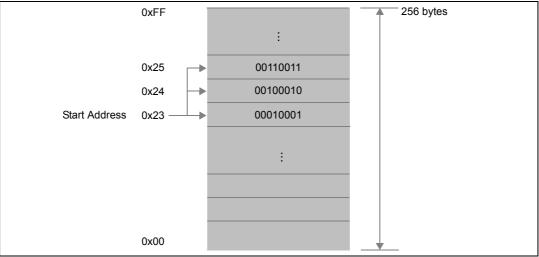

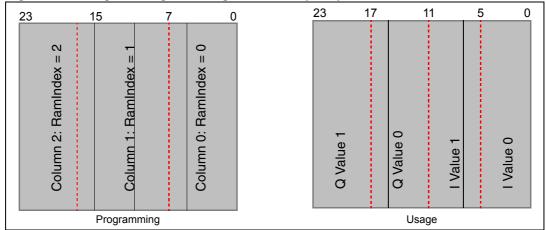

|    | 10.2  | Formatt        | ing the I and Q values                        |  |  |

|    | 10.3  | CSQ wr         | iting example                                 |  |  |

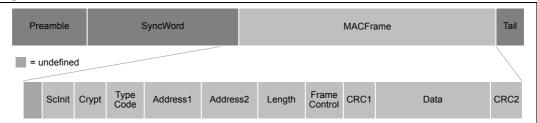

| 11 | Packe | t and M        | ACFrames                                      |  |  |

|    | 11.1  | General        | packet format                                 |  |  |

|    | 11.2  | General        | packet types                                  |  |  |

|    | 11.3  | Preamb         | le field                                      |  |  |

|    | 11.4  | SyncWo         | ord field                                     |  |  |

|    | 11.5  | MACFrame field |                                               |  |  |

|    |       | 11.5.1         | MACFrame of a data packet                     |  |  |

|    |       | 11.5.2         | MACFrame of an acknowledgement (Ack) Packet61 |  |  |

|    |       | 11.5.3         | MACFrame of a broadcast (Brdcast) packet61    |  |  |

|    |       | 11.5.4         | Time beacon packet (TimeB) MACFrame62         |  |  |

|    |       | 11.5.5         | Request to send (Req2S) packet MACFrame63     |  |  |

|    |       | 11.5.6         | Clear to send (Clr2S) packet MACFrame63       |  |  |

|    | 11.6  | Tail field     |                                               |  |  |

| 12 | Frame | e contro       | ol scheme                                     |  |  |

|    | 12.1                                   | Logical channels                                     | <u>3</u> 5  |  |  |  |  |

|----|----------------------------------------|------------------------------------------------------|-------------|--|--|--|--|

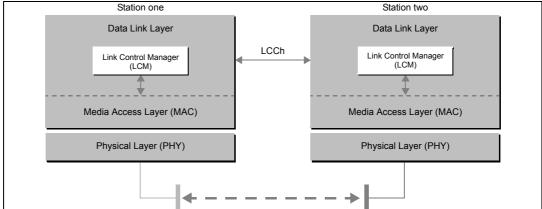

|    |                                        | 12.1.1 Link control channel                          | 35          |  |  |  |  |

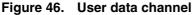

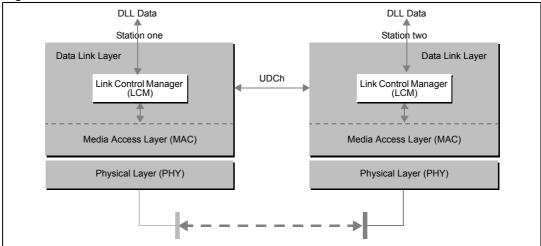

|    |                                        | 12.1.2 User data channel                             | 36          |  |  |  |  |

|    | 12.2                                   | Link control management                              | 36          |  |  |  |  |

| 13 | MACI                                   | Frame configuration (Auto/Transparent) 6             | <b>\$</b> 7 |  |  |  |  |

|    | 13.1                                   | Field for setting MACFrame auto and transparent mode | 37          |  |  |  |  |

|    | 13.2                                   | MACFrame auto mode                                   | 37          |  |  |  |  |

|    |                                        | 13.2.1 Setting MACFrame auto mode (default)          | 38          |  |  |  |  |

|    | 13.3                                   | MACFrame transparent mode                            | 38          |  |  |  |  |

|    |                                        | 13.3.1 Setting MACFrame transparent mode             | 38          |  |  |  |  |

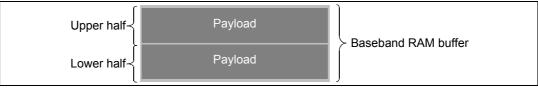

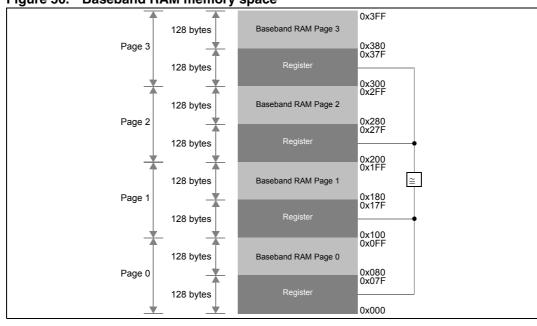

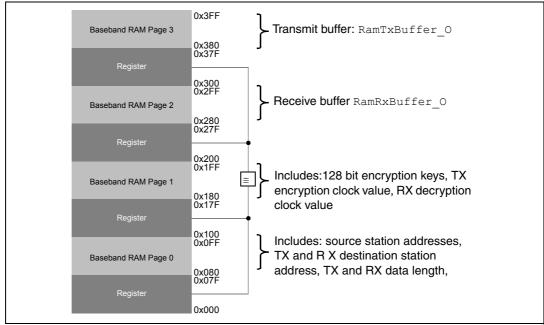

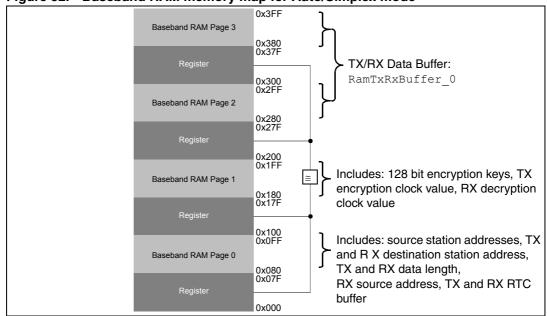

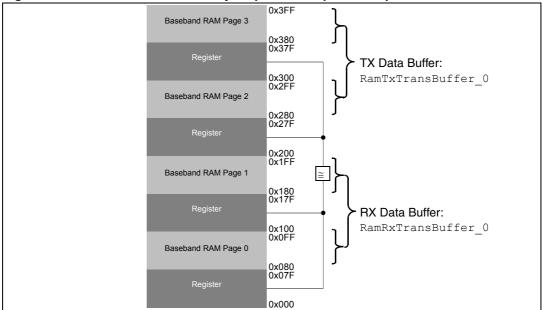

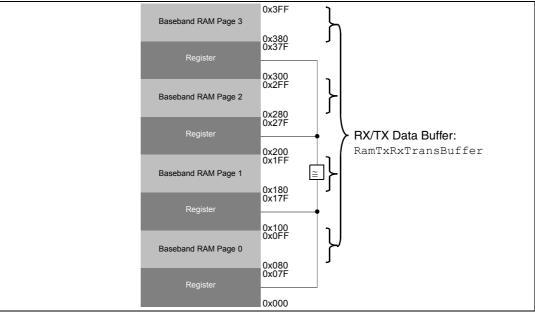

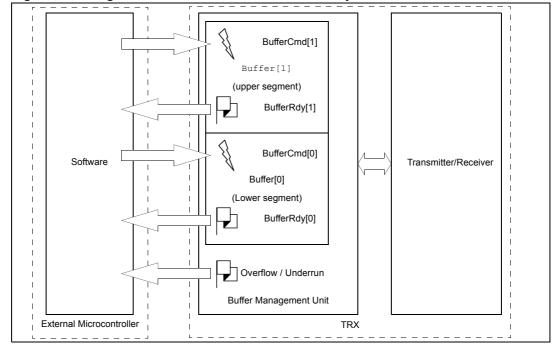

| 14 | Baseband RAM configuration             |                                                      |             |  |  |  |  |

|    | 14.1                                   | Overview                                             | 39          |  |  |  |  |

|    |                                        | 14.1.1 Configurable spaces                           | 39          |  |  |  |  |

|    | 14.2                                   | Memory usage                                         | 70          |  |  |  |  |

|    | 14.3                                   | Auto/Duplex mode                                     | 70          |  |  |  |  |

|    |                                        | 14.3.1 Setting Auto/Duplex mode                      | 71          |  |  |  |  |

|    |                                        | 14.3.2 Start addresses of the RX/TX data buffers     | 71          |  |  |  |  |

|    | 14.4                                   | Auto/Simplex mode                                    | 71          |  |  |  |  |

|    |                                        | 14.4.1 Setting Auto/Simplex mode                     | 72          |  |  |  |  |

|    |                                        | 14.4.2 Start addresses of the RX/TX data buffer      | 72          |  |  |  |  |

|    | 14.5                                   | Transparent/Duplex mode                              | 72          |  |  |  |  |

|    |                                        | 14.5.1 Setting Transparent/Duplex mode               | 73          |  |  |  |  |

|    |                                        | 14.5.2 Start addresses of the RX/TX data buffers     | 73          |  |  |  |  |

|    | 14.6                                   | Transparent/Simplex mode                             | 74          |  |  |  |  |

|    |                                        | 14.6.1 Setting Transparent/Simplex mode              | 74          |  |  |  |  |

|    |                                        | 14.6.2 Start addresses of the RX/TX data buffer      | 75          |  |  |  |  |

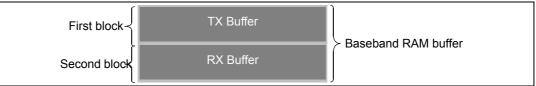

| 15 | Buffer configuration (simplex/duplex)7 |                                                      |             |  |  |  |  |

|    | 15.1                                   | Overview                                             | 76          |  |  |  |  |

|    | 15.2                                   | Field for setting duplex and simplex mode            | 76          |  |  |  |  |

|    | 15.3                                   | Duplex mode (default)                                | 76          |  |  |  |  |

|    |                                        | 15.3.1 Configuring the baseband RAM for Duplex mode  | 76          |  |  |  |  |

|    | 15.4                                   | Simplex mode                                         | 77          |  |  |  |  |

|    |                                        | 15.4.1 Configuring the baseband RAM for Simplex mode | 77          |  |  |  |  |

|    |                                        |                                                      |             |  |  |  |  |

57

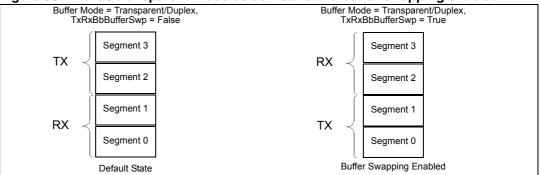

| 16 | Buffe                 | swapping between TX and RX buffers                                |  |  |  |  |  |

|----|-----------------------|-------------------------------------------------------------------|--|--|--|--|--|

|    | 16.1                  | Enabling buffer swapping (duplex mode only)                       |  |  |  |  |  |

|    | 16.2                  | Buffer swapping in auto / duplex mode                             |  |  |  |  |  |

|    | 16.3                  | Buffer swapping in transparent / duplex mode                      |  |  |  |  |  |

|    | 16.4                  | Buffer swapping and frame forwarding                              |  |  |  |  |  |

|    | 16.5                  | Buffer swapping and short MACFrames 80                            |  |  |  |  |  |

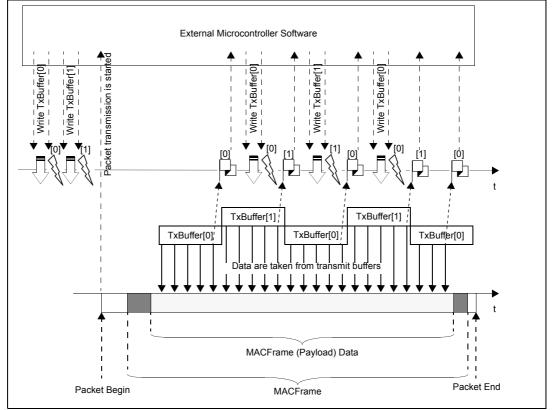

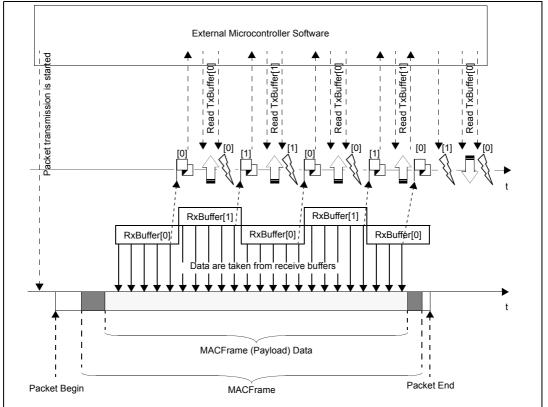

| 17 | Buffer control timing |                                                                   |  |  |  |  |  |

|    | 17.1                  | Transmit buffer control timing 81                                 |  |  |  |  |  |

|    | 17.2                  | Receive buffer control timing 82                                  |  |  |  |  |  |

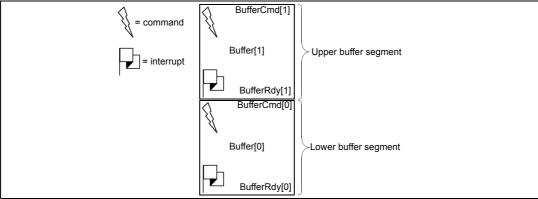

| 18 | Buffe                 | access synchronization83                                          |  |  |  |  |  |

|    | 18.1                  | Flags and commands                                                |  |  |  |  |  |

|    | 18.2                  | Receive and transmit flags 83                                     |  |  |  |  |  |

|    | 18.3                  | Receive and transmit commands 84                                  |  |  |  |  |  |

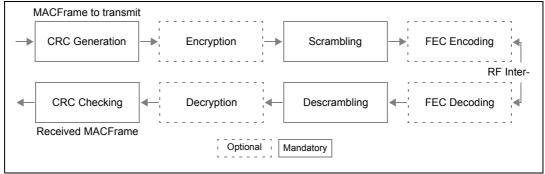

| 19 | Bit pr                | cessing                                                           |  |  |  |  |  |

|    | 19.1                  | Bit stream processes                                              |  |  |  |  |  |

|    | 19.2                  | Cyclic redundancy check (CRC) 86                                  |  |  |  |  |  |

|    |                       | 19.2.1 CRC1 field                                                 |  |  |  |  |  |

|    |                       | 19.2.2 CRC2 field                                                 |  |  |  |  |  |

|    |                       | 19.2.3 CRC types 1, 2, and 3                                      |  |  |  |  |  |

|    | 19.3                  | Bit scrambling                                                    |  |  |  |  |  |

|    | 19.4                  | Forward error correction (FEC) 88                                 |  |  |  |  |  |

|    | 19.5                  | Encryption                                                        |  |  |  |  |  |

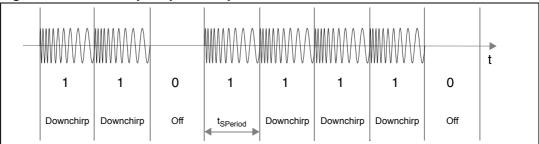

| 20 | Chirp modulation      |                                                                   |  |  |  |  |  |

|    | 20.1                  | Chirp spread spectrum (CSS) 89                                    |  |  |  |  |  |

|    | 20.2                  | Secondary modulation systems 89                                   |  |  |  |  |  |

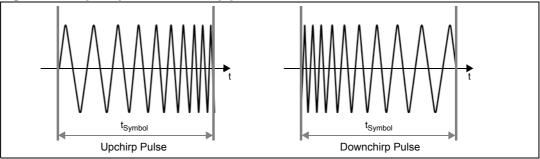

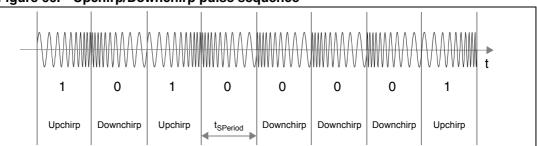

|    |                       | 20.2.1 Upchirp/downchirp modulation system                        |  |  |  |  |  |

|    |                       | 20.2.2 Upchirp/off modulation system90                            |  |  |  |  |  |

|    |                       | 20.2.3 Downchirp/off modulation system                            |  |  |  |  |  |

|    |                       | 20.2.4 Physical channels and the on-off keying modulation systems |  |  |  |  |  |

| 21 | Local                 | oscillator                                                        |  |  |  |  |  |

|    | 21.1   | Purpose of the local oscillator                                 |  |  |  |  |

|----|--------|-----------------------------------------------------------------|--|--|--|--|

|    | 21.2   | Calibrating the local oscillator frequency                      |  |  |  |  |

|    |        | 21.2.1 Fields for updating the local oscillator                 |  |  |  |  |

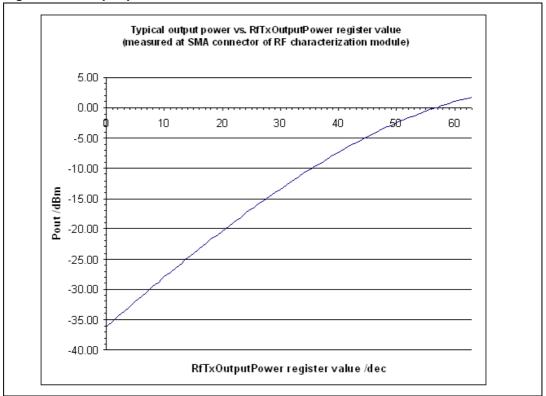

| 22 | RF tra | ansmitter                                                       |  |  |  |  |

|    | 22.1   | Adjusting the baseband filter frequency                         |  |  |  |  |

|    | 22.2   | Setting the power amplifier bias current                        |  |  |  |  |

|    | 22.3   | Adjusting the transmitter output power                          |  |  |  |  |

|    |        | 22.3.1 Output power control                                     |  |  |  |  |

|    |        | 22.3.2 Fields for adjusting the RF Transmitter                  |  |  |  |  |

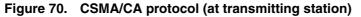

| 23 | Media  | a access control methods98                                      |  |  |  |  |

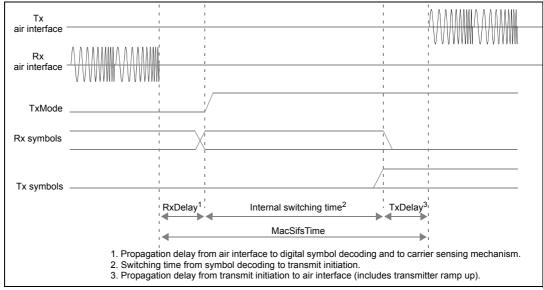

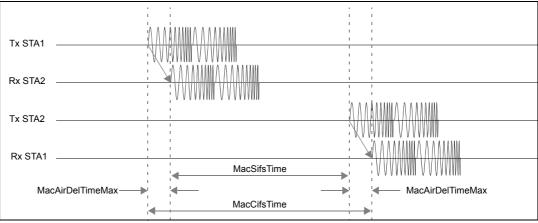

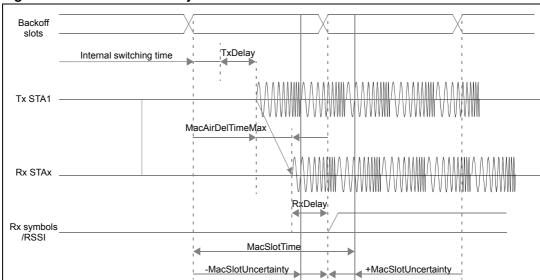

|    | 23.1   | Symbol definitions                                              |  |  |  |  |

|    | 23.2   | Direct access (DA) mode 98                                      |  |  |  |  |

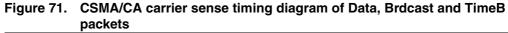

|    | 23.3   | Random access (CSMA/CA) mode                                    |  |  |  |  |

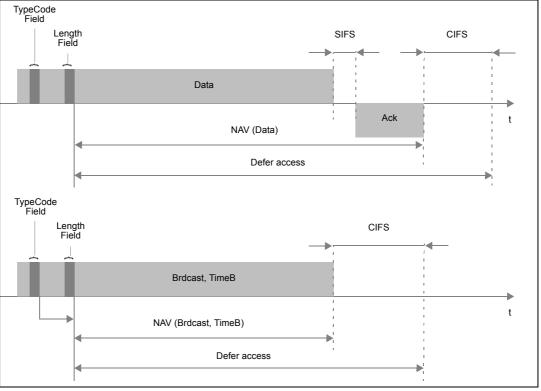

|    |        | 23.3.1 General description                                      |  |  |  |  |

|    |        | 23.3.2 Carrier sensing                                          |  |  |  |  |

|    |        | 23.3.3 Backoff time                                             |  |  |  |  |

|    |        | 23.3.4 Retransmissions                                          |  |  |  |  |

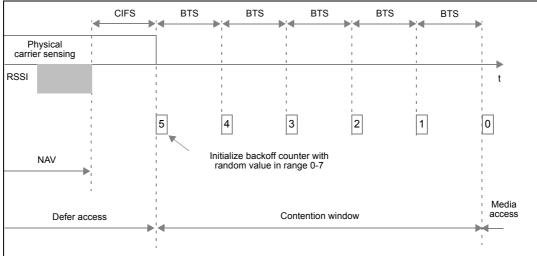

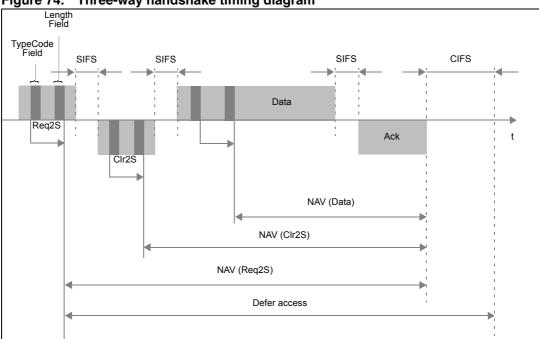

|    |        | 23.3.5 Three-way handshake 102                                  |  |  |  |  |

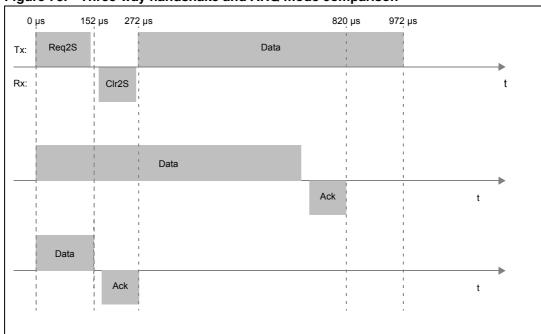

|    |        | 23.3.6 Three-way handshake and ARQ mode                         |  |  |  |  |

|    |        | 23.3.7 Adjusting transmit power levels for three-way handshakes |  |  |  |  |

|    |        | 23.3.8 Prioritized access                                       |  |  |  |  |

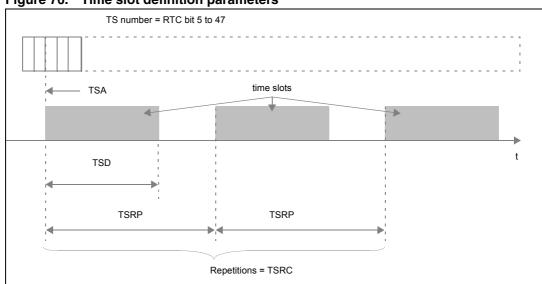

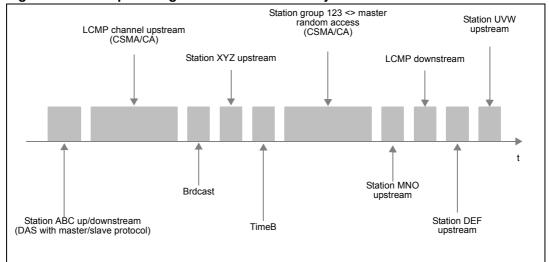

|    | 23.4   | Time slotted access (TDMA) 106                                  |  |  |  |  |

|    |        | 23.4.1 General description                                      |  |  |  |  |

|    |        | 23.4.2 Time slots                                               |  |  |  |  |

|    |        | 23.4.3 Logical channels 107                                     |  |  |  |  |

|    |        | 23.4.4 Real-time clock                                          |  |  |  |  |

|    | 23.5   | FDMA 109                                                        |  |  |  |  |

|    |        | 23.5.1 Field for enabling FDMA 109                              |  |  |  |  |

| 24 | Data   | Data transmission control methods                               |  |  |  |  |

|    | 24.1   | Symbol definitions 110                                          |  |  |  |  |

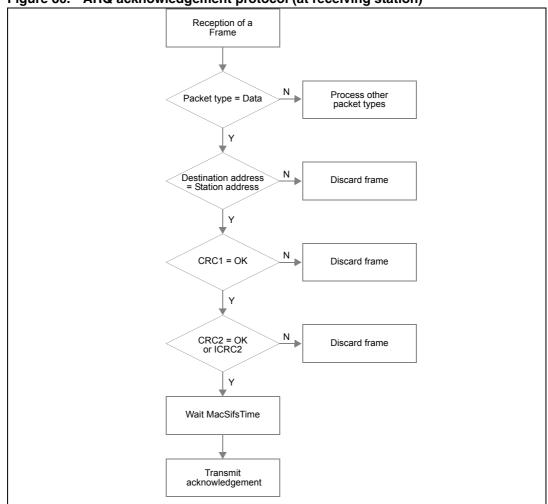

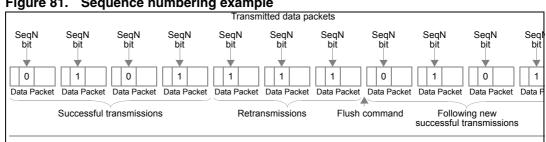

|    | 24.2   | Error correction (ARQ scheme) 110                               |  |  |  |  |

|    | 24.3   | Retransmit filtering                                            |  |  |  |  |

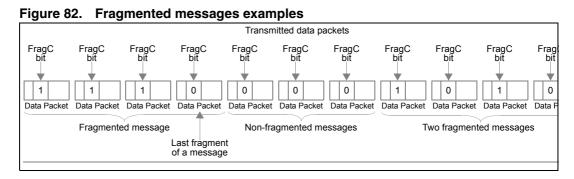

|    | 24.4   | Fragmentation control                                           |  |  |  |  |

|    |        |                                                                 |  |  |  |  |

|    | 24.5  | Unconfi  | rmed data transmission 114                                         |

|----|-------|----------|--------------------------------------------------------------------|

| 25 | Addre | ess forn | nats                                                               |

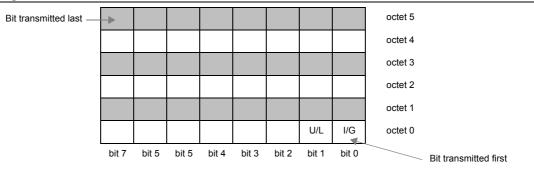

|    | 25.1  | General  | address format / addressing 115                                    |

|    | 25.2  | Address  | sing 116                                                           |

| 26 | Chip  | register | s                                                                  |

|    | 26.1  | Chip reg | gister mapping                                                     |

|    | 26.2  | Descrip  | tion of chip registers 125                                         |

|    |       | 26.2.1   | 0x00 – SPI bit order and IRQ pad configuration                     |

|    |       | 26.2.2   | Configuring SPI transfers when the bit order is unknown            |

|    |       | 26.2.3   | 0x01 – Digital controller version number and wake-up time byte 127 |

|    |       | 26.2.4   | 0x02 – Digital controller revision number and wake-up time         |

|    |       | 26.2.5   | 0x03 – Battery management 128                                      |

|    |       | 26.2.6   | 0x04 – Digital I/O controllers and digital I/O alarm status        |

|    |       | 26.2.7   | 0x05 – Write enable digital I/O port                               |

|    |       | 26.2.8   | 0x06 – Power management                                            |

|    |       | 26.2.9   | 0x07 – Reset digital baseband/baseband clock and power down 133    |

|    |       | 26.2.10  | 0x08 – Power on/off baseband crystal and clock                     |

|    |       | 26.2.11  | 0x09 – Setting SPI pads as pull-up or pull-down                    |

|    |       | 26.2.12  | 0x0A – Setting additional pads as pull-up or pull-down             |

|    |       | 26.2.13  | 0x0B – Writing pull-up/pull-down settings to pads                  |

|    |       | 26.2.14  | 0x0E – Baseband memory access                                      |

|    |       | 26.2.15  | 0x0F – LO, BBTimer, RX/TX IRQ event status and enabling 139        |

|    |       | 26.2.16  | 0x10 - TX raw interrupt status and reset [Index]141                |

|    |       | 26.2.17  | 0x11 – RX Raw Interrupt Status and Reset [Index]142                |

|    |       | 26.2.18  | 0x12 – LO and BBTimer raw interrupt status and reset [Index] 143   |

|    |       | 26.2.19  | 0x13 – Enable transmitter interrupts [Index]                       |

|    |       | 26.2.20  | 0x14 - Receiver interrupt enable [Index] 145                       |

|    |       | 26.2.21  | 0x15 – Local oscillator interrupt enable [index]147                |

|    |       | 26.2.22  | 0x16 to 0x18 – RF local oscillator RX capacitors                   |

|    |       | 26.2.23  | 0x19 to 0x1B – RF local oscillator TX capacitors                   |

|    |       | 26.2.24  | RF local oscillator controls                                       |

|    |       | 26.2.25  | 0x1D to 0x1E – RF local oscillator target value                    |

|    |       | 26.2.26  | 0x1F - AGC threshold 1                                             |

|    |       | 26.2.27  | 0x20 – AGC threshold 2                                             |

|    |       | 26.2.28  | 0x21 – AGC hold frame/bit synchronization controls                 |

| 26.2.29 | 0x22 – AGC change gain length 151                                                  |

|---------|------------------------------------------------------------------------------------|

| 26.2.30 | 0x23 to 0x24 – AGC integration time                                                |

| 26.2.31 | 0x25 – AGC value                                                                   |

| 26.2.32 | 0x26 – RF AGC controls                                                             |

| 26.2.33 | 0x27 – RC oscillator tuning153                                                     |

| 26.2.34 | 0x28 to 0x29 – Baseband timer start value                                          |

| 26.2.35 | 0x2A to 0x2B – ToaOffset for received Ack packet                                   |

| 26.2.36 | 0x2C to 0x2D – Round trip time                                                     |

| 26.2.37 | 0x2E – Phase offset for RX data and Ack packets                                    |

| 26.2.38 | 0x2F to 0x30 – ToaOffset for received data packet (read only) 156                  |

| 26.2.39 | 0x2A to 0x31 – Transceiver SyncWord (write only)156                                |

| 26.2.40 | 0x31 – Receiver mode controls (read only) 157                                      |

| 26.2.41 | 0x32 – Receive correlator error controls                                           |

| 26.2.42 | 0x33 to 0x34 – Transmit time slot start (write only)158                            |

| 26.2.43 | 0x35 to 0x36 – Transmit time slot end (write only)                                 |

| 26.2.44 | 0x33 – Receiver encryption (read only)                                             |

| 26.2.45 | 0x34 to 0x35 – Receive FEC single bit error count (read only) 160                  |

| 26.2.46 | 0x37 – Transmitter and receiver time slot control (TDMA)161                        |

| 26.2.47 | 0x38 to 0x39 – RX packet slot (read only)161                                       |

| 26.2.48 | 0x38 to 0x39 – RX time slot start and packet slot (write only) $\ldots \ldots 162$ |

| 26.2.49 | 0x3A to 0x3B - RX time slot end162                                                 |

| 26.2.50 | 0x3C – ARQ                                                                         |

| 26.2.51 | 0x3D – RF chirp generator controls                                                 |

| 26.2.52 | 0x3F – Correlator controls                                                         |

| 26.2.53 | 0x40 – Frame synchronization and bit synchronization                               |

| 26.2.54 | 0x41 – Bit synchronization                                                         |

| 26.2.55 | 0x42 – Local oscillator, chirp sequencer and external PA controls 166              |

| 26.2.56 | $0x43-RF\ Rx$ low noise amplifier and TX power amplifier bias $\ldots\ldots$ 167   |

| 26.2.57 | 0x44 – Transmitter output power (Data, TimeB, and BrdCast) 168                     |

| 26.2.58 | 0x45 – Transmitter output power (Ack, Req2S, and Clr2S)168                         |

| 26.2.59 | 0x46 – Quantization threshold for I                                                |

| 26.2.60 | 0x47 – Quantization threshold for Q169                                             |

| 26.2.61 | 0x48 – Symbol duration, symbol rate, and modulation system 169                     |

| 26.2.62 | 0x49 – CRC2, CRC2 encryption, FEC, and encryption clock mode 170                   |

| 26.2.63 | 0x4A – Baseband buffer and MACFrame configuration                                  |

| 26.2.64 | 0x4B to 0x4C – Transceiver chirp matrix                                            |

| 26.2.65 | 0x4D – TX underrun, CIFS waiting, and preamble/tail sequences 174                  |

|      | 26.2.66 | 0x4E – Media access control for transmitter                                      |

|------|---------|----------------------------------------------------------------------------------|

|      | 26.2.67 | 0x4F - Back-off seed for back-off time                                           |

|      | 26.2.68 | 0x50 – Transmission encryption178                                                |

|      | 26.2.69 | 0x51 – Transmit scrambler 179                                                    |

|      | 26.2.70 | 0x52 to 0x53 – TX data size in transparent mode                                  |

|      | 26.2.71 | 0x54 – Packet type for auto mode and TX source address                           |

|      | 26.2.72 | $0x55$ – Start/stop transmissions and TX buffer fill command $\ldots \ldots 181$ |

|      | 26.2.73 | 0x56 - Start/stop receptions and RX buffer fill command 182                      |

|      | 26.2.74 | 0x57 – Receiver decryption sequence reset                                        |

|      | 26.2.75 | 0x58 to 0x59 – RX data size in transparent mode                                  |

|      | 26.2.76 | $0x5A-RX\ ES$ and IS address matching, CRC1, CRC2, and ARQ $\ldots$ 183          |

|      | 26.2.77 | 0x5B - RX Data, Brdcast, TimeB, address mode, and ranging pulses 185             |

|      | 26.2.78 | 0x5C – Delay detection tuning 187                                                |

|      | 26.2.79 | 0x5D - Receive bit detector controls (bit detectors)                             |

|      | 26.2.80 | 0x5E – Bit detection gate size and adjustment                                    |

|      | 26.2.81 | 0x5F - Bit synchronization/unsynchronization thresholds 190                      |

|      | 26.2.82 | 0x60 - Real-time clock TimeB transmission delay adjustment 190                   |

|      | 26.2.83 | 0x61 – Real-time clock TimeB reception delay adjustment 191                      |

|      | 26.2.84 | 0x62 – Real-time clock                                                           |

|      | 26.2.85 | 0x63 – AGC amplitude 192                                                         |

|      | 26.2.86 | 0x64 – Alternative AGC and AGC range offset                                      |

| Base | band re | gisters 194                                                                      |

| 27.1 | Baseba  | nd register mapping                                                              |

|      | 27.1.1  | Auto/duplex mode                                                                 |

|      | 27.1.2  | Auto/simplex mode                                                                |

|      | 27.1.3  | Transparent/duplex mode                                                          |

|      | 27.1.4  | Transparent/simplex mode                                                         |

| 27.2 | Descrip | tion of baseband registers 197                                                   |

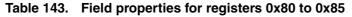

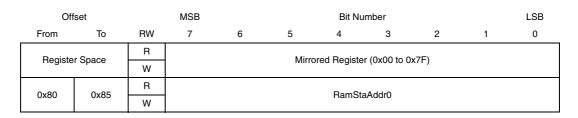

|      | 27.2.1  | Auto/duplex [Pg 0] 0x80 to 0x85 – source station address 0 197                   |

|      | 27.2.2  | Auto/duplex [Pg 0] 0x88 to 0x8D – source station address 1 197                   |

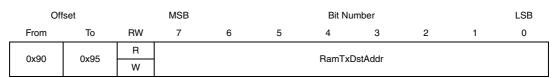

|      | 27.2.3  | Auto/duplex [Pg 0] 0x90 to 0x95 – TX destination address                         |

|      | 27.2.4  | Auto/duplex [Pg 0] 0x98 to 0x99 – TX data length and bits for sw usage .<br>198  |

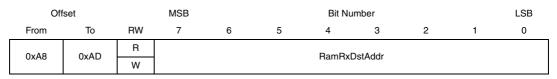

|      | 27.2.5  | Auto/duplex [Pg 0] 0xA8 to 0xAD - RX destination address                         |

|      | 27.2.6  | Auto/duplex [Pg 0] 0xB0 to 0xB5 – RX source address                              |

|      |         |                                                                                  |

27

|    |                      | 27.2.7 Auto/duplex [Pg 0] 0xB8 to 0xB9 – RX data length and bits for SW usage 200                                                                                          |

|----|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                      | 27.2.8 Auto/duplex [Pg 0] 0xE0 to 0xE5 – TX Real-time clock buffer 20                                                                                                      |

|    |                      | 27.2.9 Auto/duplex [Pg 0] 0xE8 to 0xED - RX Real-Time Clock buffer 20                                                                                                      |

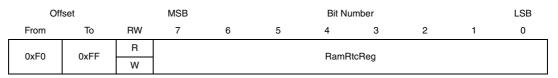

|    |                      | 27.2.10 Auto/duplex [Pg 0] 0xF0 to 0xFF - RX Real-Time Clock buffer 20                                                                                                     |

|    |                      | 27.2.11 Auto/duplex [Pg 1] 0x100 to 0x17F - register (mirrored) 20                                                                                                         |

|    |                      | 27.2.12 Auto/duplex [Pg 1] 0x180 to 0x1BF – encryption key                                                                                                                 |

|    |                      | 27.2.13 Auto/duplex [Pg 1] 0x1C0 to 0x1CF - TX encryption clock value 20                                                                                                   |

|    |                      | 27.2.14 Auto/duplex [Pg 1] 0x1E0 to 0x1EF - RX decryption clock value 20                                                                                                   |

|    |                      | 27.2.15 Auto/duplex [Pg 2] 0x200 to 0x27F - register (mirrored) 20                                                                                                         |

|    |                      | 27.2.16 Auto/duplex [Pg 2] 0x280 to 0x2FF – RX data buffer                                                                                                                 |

|    |                      | 27.2.17 Auto/duplex [Pg 3] 0x300 to 0x37F - register (mirrored) 20                                                                                                         |

|    |                      | 27.2.18 Auto/duplex [Pg 3] 0x380 to 0x3FF – TX data buffer                                                                                                                 |

|    |                      | 27.2.19 Auto/simplex [Pg 0] 0x80/0x0FF - same as auto/duplex [Pg 0] 20                                                                                                     |

|    |                      | 27.2.20 Auto/simplex [Pg 1] 0x180/0xEFF - same as auto/duplex [Pg 1] 20                                                                                                    |

|    |                      | 27.2.21 Auto/simplex [Pg 2/3] 0x280 to 0x3FF – TX/RX data buffer                                                                                                           |

|    |                      | 27.2.22 Transparent/duplex page [Pg 0/1] 0x080 to 0x1FF - RX data buffer 20                                                                                                |

|    |                      | 27.2.23 Transparent/duplex page [Pg 2/3] 0x280 to 0x3FF - TX data buffer 20                                                                                                |

|    |                      | 27.2.24 Transparent/simplex [Pg 0/1/2/3] 0x080/0x3FF - RX/TX data buffer 20                                                                                                |

| 28 | Orde                 | ring information                                                                                                                                                           |

| 29 | Elect                | rical characteristics                                                                                                                                                      |

|    | 29.1                 | Absolute maximum ratings 21                                                                                                                                                |

|    | 29.2                 | Nominal conditions                                                                                                                                                         |

|    | 29.3                 | General DC parameters 21                                                                                                                                                   |

|    | 29.4                 | Transmitter (TX)                                                                                                                                                           |

|    | -                    | 29.4.1 General parameters                                                                                                                                                  |

|    |                      | 29.4.2 Programmable RAM for chirp sequencer                                                                                                                                |

|    |                      | 29.4.3 Chirp specification (CSS)                                                                                                                                           |

|    | 29.5                 | Receiver (RX)                                                                                                                                                              |

|    | 2010                 | 29.5.1 General parameters                                                                                                                                                  |

|    |                      | 29.5.2 Radio signal strength indicator (RSSI)                                                                                                                              |

|    |                      |                                                                                                                                                                            |

|    | 29.6                 | Dynamic performance 21                                                                                                                                                     |

|    | 29.6<br>20.7         | Dynamic performance    21      Quartz controlled oscillator for reference frequency    21                                                                                  |

|    | 29.6<br>29.7<br>29.8 | Dynamic performance       21         Quartz controlled oscillator for reference frequency       21         Quartz-controlled oscillator for real-time clock (RTC)       21 |

29.9

TN100

|          | 29.11   | Digital interface to sensor/actor       Interface to digital controller         Interface to digital controller       Interface to digital controller         Power supply for the external digital microcontroller       Interface to digital controller | 218 |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

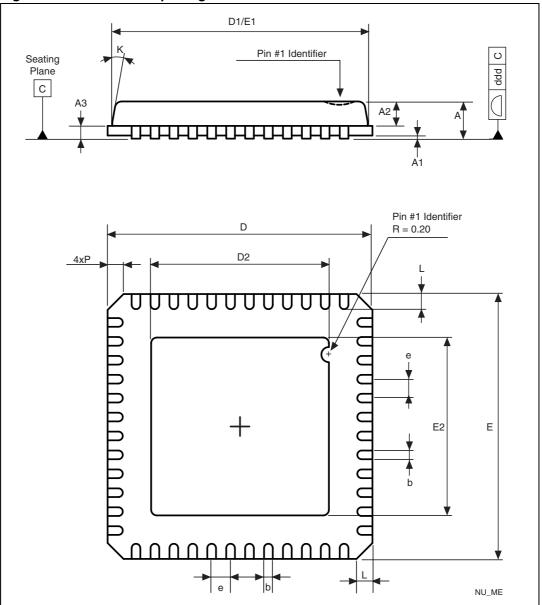

| 30       |         | ige mechanical data                                                                                                                                                                                                                                       |     |

| Appendix | A At    | ttributes and constants                                                                                                                                                                                                                                   | 221 |

| Appendix | B De    | efault register settings                                                                                                                                                                                                                                  | 224 |

| Revision | history | y                                                                                                                                                                                                                                                         | 234 |

## 1 Summary description

The TN100 transceiver IC is designed to build robust, short distance wireless networks operating in the 2.45 GHz ISM band with extremely low power consumption over a wide range of operating temperatures.

The TN100 supports 7-frequency channels with 3 non-overlapping channels. This provides support for multiple physically independent networks and improved coexistence performance with existing 2.4 GHz wireless technologies. Data rates are selectable between 31.25 kbps and 2 Mbps. Due to the chip's unique chirp pulse, adjustment of the antenna is not critical. This significantly simplifies the system's installation and maintenance ("pick-and-place").

The TN100 transceiver includes a sophisticated MAC controller with CSMA/CA and TDMA support as well as forward error correction (FEC) and 128-bit hardware encryption. It also provides scrambling, automatic address matching, and packet retransmission, thus minimizing the requirements for microcontroller and software.

Through its high-speed standard SPI interface, the TN100 can be interfaced with a wide range of external microcontrollers. It includes a 4-Kbit frame buffer which allows even very slow microcontrollers to work with the transceiver. This means that several receive and transmit frames can be stored simultaneously in the buffers. This solution eliminates the problems of different peak data rates between air and microcontroller interfaces.

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. ECOPACK<sup>®</sup> packages are lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

### **Target applications**

Target applications for the TN100 include:

- Asset tracking

- Enabling 2D/3D real-time location systems

- Security

- Industrial monitoring and control

- Medical applications

### **Development environment**

- Simple API access to chip registers

- Easy-to-use evaluation boards for testing the TN100 in any environment

- Ready-to-customize development boards for quick application development

57

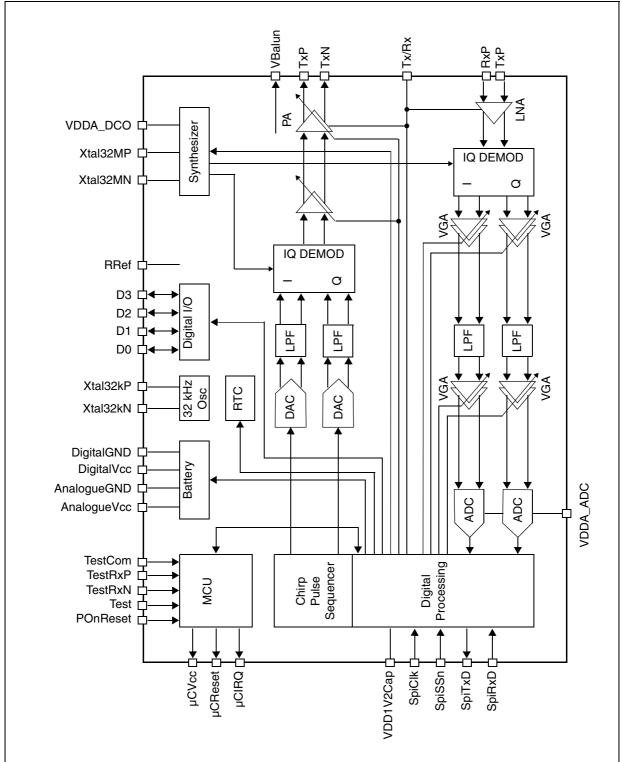

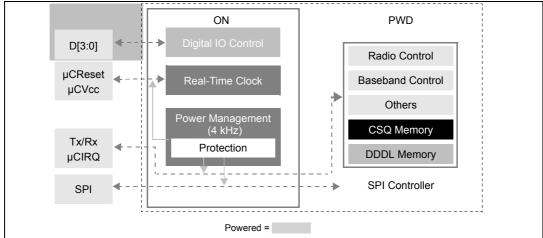

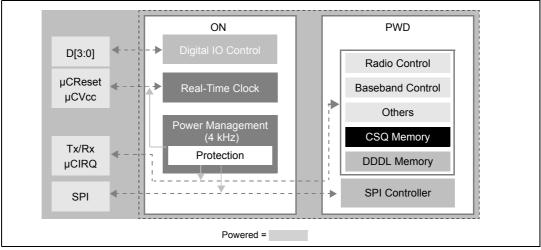

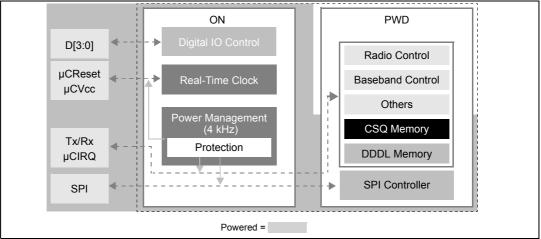

## 2 TN100 block diagram

## 3 Key features

The TN100 transceiver incorporates robust wireless communication capabilities including:

- Built-in precise ranging capabilities

- Channelization using FDMA for improved coexistence

- Different symbol durations and symbol rates

- Standard set of default register values set into chip

- Digital Dispersive Delay Line (DDDL) incorporated in the chip

- Programmable pull resistors

## 3.1 Built-in ranging capability

The TN100 transceiver provides a built-in ranging capability. The chip can be enabled to provide Round Trip of Flight (RToF) information using a special Data / Ack packet transmission. Because the processing time for generating a hardware acknowledgment is known and the time of transmission a data packet is known, these two values can be used to calculate a ranging distance between the two TN100 stations.

## 3.2 Channelization using FDMA for improved coexistence

Channelization is the subdividing of the available frequency band (in this case, the 83 MHz ISM band) into many narrow frequency bands, which for the TN100 transceiver is 22 MHz channels. This increases coexistence with devices sharing the same ISM band. The TN100 transceiver channelizes the 2.4 GHz ISM band into multiple 22 MHz frequency channels using Frequency Division Multiple Access (FDMA). With register settings, the chip can be set to 80 MHz or 22 MHz signal bandwidth. The chip is set by default to use FDMA on startup and can be programmed to use one of multiple 22 MHz channels in the ISM band.

## 3.3 Incorporated digital dispersive delay-line (DDDL)

The TN100 transceiver incorporates a Digital Dispersive Delay Line (DDDL), which in previous chips was an external component. Reference values for I and Q can be stored in Baseband RAM. These values are used to detect incoming signals generated by another transceiver chip. The detectable signals can be one of the following:

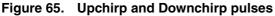

- An Upchirp (linear frequency modulation, where frequency increases in time)

- A Downchirp (linear frequency modulation, where frequency decreases in time)

- An OffChirp, which is the absence of a chirp

Note: For more details, see Section 20: Chirp modulation on page 89.

## 3.4 Selectable symbol durations and symbol rates

The TN100 transceiver provides selectable symbol durations and symbol rates.

- Symbol durations include: 0.5 µs, 1 µs, 2 µs, and 4 µs

- Symbol rates include: 2 Mbps, 1 Mbps, 0.5 Mbps and 0.25 Mbps

*Note: See Section 26.2.61: 0x48 – Symbol duration, symbol rate, and modulation system on page 169.*

## 4 Architecture

The TN100 is a extremely low power, highly integrated mixed signal chip incorporating both an analog and a digital part in one silicon die. This section provides a brief overview of the digital and analog parts of the chip.

## 4.1 Analog part - TX and RX

For transmission, the analog part of the chip converts data obtained from the digital part into chirp pulses and sends packets over the air using an RF link. For reception, it detects received chirp pulses into a form that can be used by the digital part.

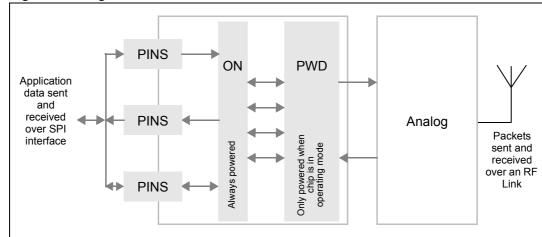

## 4.2 Digital part - programming interface

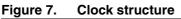

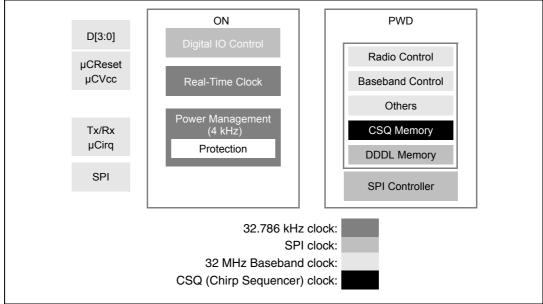

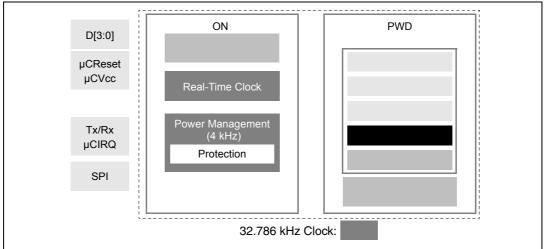

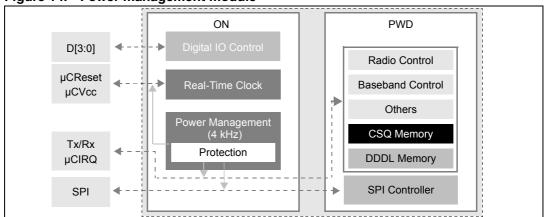

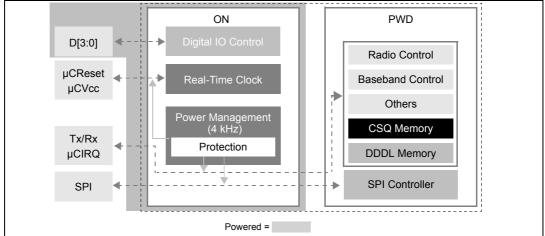

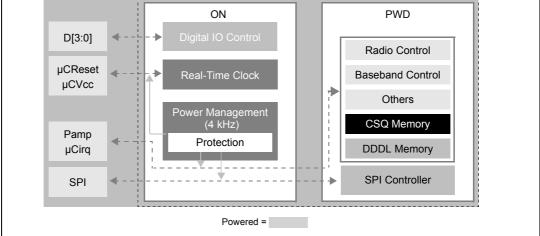

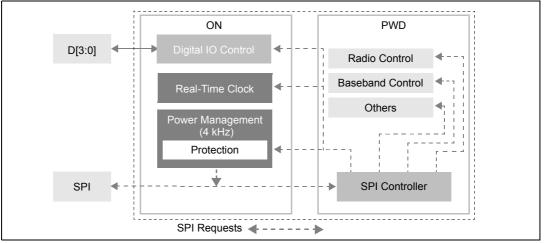

The digital part of the chip provides an SPI interface for reading and writing to chip registers. Application data is written to chip buffers in the digital part, which is then provided to the analog part of the chip for transmission over the air. Data received from the analog part is provided to an application via buffers in the digital part. To achieve maximum power savings, the digital part of the TN100 transceiver is divided into two sections called an *ON* section (that is, always powered) and a *PWD* section (that is, powered during operating mode).

### 4.2.1 Digital part – ON Section

The ON section, which is always powered, contains the minimum number of required controls that are used to maintain the chip settings. It also is connected to the digital I/O pins as these pins are used for power management.

### 4.2.2 Digital part – PWD section

The PWD section, which is powered up only during operating mode, contains the remaining controls that are used when the chip is required for data transmission and reception.

### 4.3 Signal flow

Figure 2 illustrates the signal flow within the chip.

### Figure 2. Signal flow in the TN100 transceiver

### 4.4 Commonly used set of register default values

The chip has been set with a number of default values that would be required for most standard applications to reduce the time required for chip initialization.

## 4.5 **Programmable pull-resistors**

The TN100 transceiver uses programmable pull-resistors to lower the cost of the bill of materials. The following pads can now be set as either pull-up or pull-down:

- SpiClk (pin 15)

- SpiSsn (pin 16)

- SpiTxd (pin 17)

- SpiRxd (pin 18)

- POnReset (pin 30)

- TxRx (pin 9)

- µCIRQ (pin 27)

- µCReset (pin 28)

- Digital IO pads (pins 19 to 22)

Note: A full listing of register default values is provided in Appendix B: Default register settings on page 224.

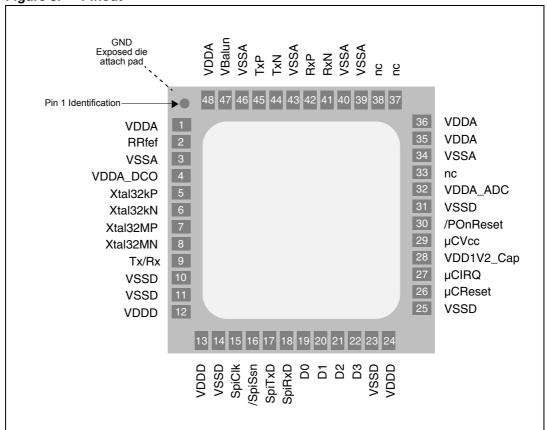

## 5 Pin description

This section provides a brief overview of the location and function of each pin.

#### Table 1.Pin descriptions

| Pin | Signal   | Direction      | Direction Description                                                       |  |  |

|-----|----------|----------------|-----------------------------------------------------------------------------|--|--|

| 1   | VDDA     | Supply         | Power supply for analog parts                                               |  |  |

| 2   | RRef     | Analog IO      | Pin for external reference resistor                                         |  |  |

| 3   | VSSA     | Supply         | Power supply for analog parts                                               |  |  |

| 4   | VDDA_DCO | Supply         | Power supply for DCO                                                        |  |  |

| 5   | Xtal32kP | Analog IO      | Crystal 32768 Hz, input from external 32768 Hz frequency reference          |  |  |

| 6   | Xtal32kN | Analog IO      | Crystal 32768 Hz                                                            |  |  |

| 7   | Xtal32MP | Analog IO      | 32.0 MHz crystal oscillator, input from external 32 MHz frequency reference |  |  |

| 8   | Xtal32MN | Analog IO      | 32.0 MHz crystal oscillator                                                 |  |  |

| 9   | Tx/Rx    | Digital output | Output signal to distinguish between transmit and receive                   |  |  |

| 10  | VSSD     | Supply         | Power supply for digital parts                                              |  |  |

| 11  | VSSD     | Supply         | Power supply for digital parts                                              |  |  |

| Table 1 | . Pin descriptions (continued) |                |                                                                                                                                               |  |  |  |  |

|---------|--------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin     | Signal                         | Direction      | Description                                                                                                                                   |  |  |  |  |

| 12      | VDDD                           | Supply         | Power supply for digital parts                                                                                                                |  |  |  |  |

| 13      | VDDD                           | Supply         | Power supply for digital parts                                                                                                                |  |  |  |  |

| 14      | VSSD                           | Supply         | Power supply for digital parts                                                                                                                |  |  |  |  |

| 15      | SpiClk                         | Digital input  | SPI clock                                                                                                                                     |  |  |  |  |

| 16      | SpiSSn                         | Digital input  | SPI slave selected                                                                                                                            |  |  |  |  |

| 17      | SpiTxD                         | Digital output | SPI transmit data (MISO)                                                                                                                      |  |  |  |  |

| 18      | SpiRxD                         | Digital Input  | SPI receive data (MOSI)                                                                                                                       |  |  |  |  |

| 19      | D0                             | Digital IO     | Digital input or output line 0                                                                                                                |  |  |  |  |

| 20      | D1                             | Digital IO     | Digital input or output line 1                                                                                                                |  |  |  |  |

| 21      | D2                             | Digital IO     | Digital input or output line 2                                                                                                                |  |  |  |  |

| 22      | D3                             | Digital IO     | Digital input or output line 3                                                                                                                |  |  |  |  |

| 23      | VSSD                           | Supply         | Power supply for digital parts                                                                                                                |  |  |  |  |

| 24      | VDDD                           | Supply         | Power supply for digital parts                                                                                                                |  |  |  |  |

| 25      | Test                           | Digital IO     | Pin for digital tests                                                                                                                         |  |  |  |  |

| 26      | µCReset                        | Digital output | Reset for external microprocessor                                                                                                             |  |  |  |  |

| 27      | μCIRQ                          | Digital output | Interrupt request to external microprocessor                                                                                                  |  |  |  |  |

| 28      | VDD1V2_CAP                     | Supply         | 1.2 V digital power supply decoupling.                                                                                                        |  |  |  |  |

| 29      | μCVCC                          | Supply         | Switchable power supply for external microcontroller                                                                                          |  |  |  |  |

| 30      | POnReset                       | Digital input  | Power on reset line                                                                                                                           |  |  |  |  |

| 31      | VSSD                           | Supply         | Power supply for digital parts                                                                                                                |  |  |  |  |

| 32      | VDDA_ADC                       | Supply         | Power supply for analog parts (Rx ADC)                                                                                                        |  |  |  |  |

| 33      | TestCom                        | LF signal      | Test pin for analogue signals                                                                                                                 |  |  |  |  |

| 34      | VSSA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 35      | VDDA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 36      | VDDA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 37      | TestRxP                        | LF Signal      | Test pin for RX signals                                                                                                                       |  |  |  |  |

| 38      | TestRxN                        | LF Signal      | Test pin for RX signals inverted                                                                                                              |  |  |  |  |

| 39      | VSSA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 40      | VSSA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 41      | RxN                            | RF input       | Differential receiver input (inverted)                                                                                                        |  |  |  |  |

| 42      | RxP                            | RF input       | Differential receiver input                                                                                                                   |  |  |  |  |

| 43      | VSSA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 44      | TxN                            | RF output      | Differential transmitter output (inverted)                                                                                                    |  |  |  |  |

| 45      | TxP                            | RF output      | Differential transmitter output                                                                                                               |  |  |  |  |

| 46      | VSSA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

| 47      | VBalun                         | Supply         | Power supply for external balun (DC for TxP/TxN; needs to be blocked with an external capacitor in the 27pF to 47pF range close to the balun) |  |  |  |  |

| 48      | VDDA                           | Supply         | Power supply for analog parts                                                                                                                 |  |  |  |  |

Table 1. Pin descriptions (continued)

## 5.1 Input and/or output pins

Table 2 describes the digital pins and analog pins of the TN100 transceiver.

| Table 2.  | Digital input | pins         |                                                                                                                                                                                                                                                |

|-----------|---------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin       | Pin no.       | Direction    | Description                                                                                                                                                                                                                                    |

| Xtal32kP  | 5             | Input        | Analog pin. 32.768 kHz crystal oscillator pin 1 or input<br>for an external 32.768 kHz clock generator. Used to<br>connect crystal or active frequency reference.                                                                              |

| Xtal32kN  | 6             | Output       | Analog pin. 32.768 kHz crystal oscillator pin 2.                                                                                                                                                                                               |

| Xtal32MP  | 7             | Input        | Analog pin. 32 MHz crystal oscillator pin 1 or input for<br>an external 32 MHz clock generator. Used to connect<br>crystal or active frequency reference.                                                                                      |

| Xtal32MN  | 8             | Output       | Analog pin. 32 MHz kHz crystal oscillator pin 2.                                                                                                                                                                                               |

| /POnReset | 30            | Input        | Power on reset signal.                                                                                                                                                                                                                         |

| SpiClk    | 15            | Input        | The SPI Clock is generated by the microcontroller<br>(master) and synchronizes data movement in and out of<br>the device through the pins SpiRxD and SpiTxD.                                                                                   |

| /SpiSSn   | 16            | Input        | SPI Slave Select (low active) is externally asserted<br>before the microcontroller (master) can exchange data<br>with the TN100 transceiver. Must be low before data<br>transactions and must stay low for the duration of the<br>transaction. |

| SpiRxD    | 18            | Input        | SPI Receive Data (MOSI).                                                                                                                                                                                                                       |

| SpiTxD    | 17            | Output       | SPI Transmit Data (MISO).                                                                                                                                                                                                                      |

| Tx/Rx     | 9             | Output       | Distinguishes between the TX and RX phase. Can also<br>be used to provide an external power amplifier control.<br>Active Low during TX, otherwise High.                                                                                        |

| µCReset   | 26            | Output       | Reset for external microprocessor.                                                                                                                                                                                                             |

| μCIRQ     | 27            | Output       | Interrupt request to external microprocessor.                                                                                                                                                                                                  |

| D0        | 19            | Input/Output | Digital Input or Output (programmable, see configuration bits below), line 0.                                                                                                                                                                  |

| D1        | 20            | Input/Output | Digital Input or Output (programmable, see configuration bits below), line 1.                                                                                                                                                                  |

| D2        | 21            | Input/Output | Digital Input or Output (programmable, see configuration bits below), line 2                                                                                                                                                                   |

| D3        | 22            | Input/Output | Digital Input or Output (programmable, see<br>configuration bits below), line 3. Note that a 32.768 kHz<br>clock operates on this pin after reset/power up.                                                                                    |

| μCVcc     | 29            | Output       | Analog pin. Power supply for external microprocessor.                                                                                                                                                                                          |

| Table 2. | Digital input pins |  |

|----------|--------------------|--|

|          | Bigitai inpat pino |  |

## 5.2 Configuring the digital I/O pins – D0 to D3 (pins 19 to 22)

Each digital I/O pin can be configured as either an input or an output pin. Signal levels or an alarm occurrence can be reported at a digital I/O pin that has been set as input. *Table 3* lists the fields are used for configuring digital I/O pins.

| Field                  | Offset | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DioDirection           | 0x04   | WO  | Controls the direction of Digital I/O port. Set it as either an input or an output pin.                                                                                                                                                                                                                                                                                                                   |

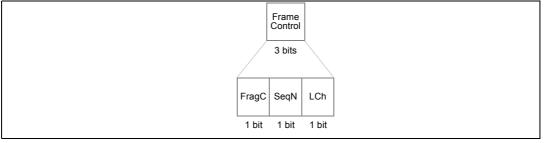

| DioOutValueAlarmEnable | 0x04   | WO  | When a Digital I/O port is configured as input,<br>this bit selects to be reported either the signal<br>level at the port or the occurrence of an<br>alarm.                                                                                                                                                                                                                                               |