# TACT2150 512 × 8 CACHE ADDRESS COMPARATOR

D2993 JANUARY 1987-REVISED SEPTEMBER 1987

| <ul> <li>Address to MATCH Valid Time<br/>TACT2150-20 20 ns max</li> </ul> | DW, JD, OR NT PACKAGE<br>(TOP VIEW) |

|---------------------------------------------------------------------------|-------------------------------------|

| TACT2150-30 30 ns max                                                     | RESET 1 U24 VCC                     |

| <ul> <li>300-Mil 24-Pin Ceramic Side-Brazed or</li> </ul>                 | A5 2 23 A1                          |

| Plastic Dual-In-Line or Small Outline                                     | A4 🔲 3 22 🗍 A0                      |

| Packages                                                                  | A3 🛛 4 21 🗍 A8                      |

| • 53 mA Typical Supply Current                                            | A2 🔲 5 20 🖸 A7                      |

|                                                                           | D3 <b>[</b> ]6 19 [] A6             |

| <ul> <li>On-Chip Parity Generation and Checking</li> </ul>                | DO <b>□</b> 7 18 <b>□</b> D5        |

| Parity Error Output/Force Parity Error Input                              | D1 <b>[]</b> 8 17 [] D4             |

| , ,                                                                       | <u>D2</u> <b>□</b> 9 16 □ D7        |

| On-Chip Address/Data Comparator                                           | <u>W</u> ☐10 15 ☐ D6                |

| Asynchronous, Single-Cycle Reset                                          | PE ☐11 14☐ MATCH<br>GND ☐12 13☐ S   |

| Easily Expandable                                                         | GND [_12 13]_] S                    |

# description

**Fully Static**

Fully TTL Compatible

Reliable Advanced CMOS Technology

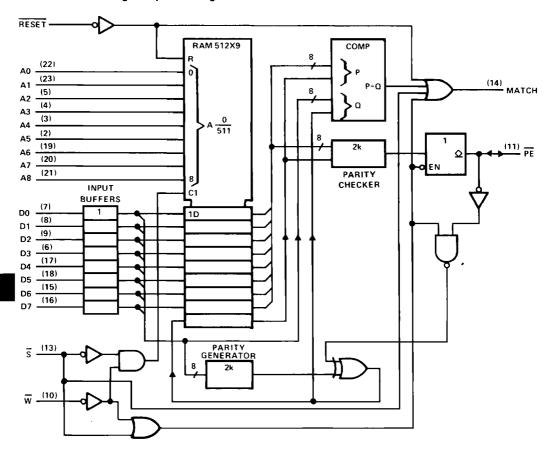

This 8-bit-slice cache address comparator consists of a high-speed 512 × 9 static RAM array, parity generator, parity checker, and 9-bit high-speed comparator. It is fabricated using Advanced CMOS technology for high-speed, low-power interface with bipolar TTL circuits. The cache address comparator is easily cascadable for wider tag addresses or deeper tag memories. Significant reductions in cache memory component count, board area, and power dissipation can be achieved with this device.

When  $\overline{S}$  is low and  $\overline{W}$  is high, the cache address comparator compares the contents of the memory location addressed by A0-A8 with the data on D0-D7 plus generated parity. An equality is indicated by the high level on the MATCH output. A low-level output from  $\overline{PE}$  signifies a parity error in the internal RAM data.  $\overline{PE}$  is an N-channel open-drain output for easy OR-tying. During a write cycle ( $\overline{S}$  and  $\overline{W}$  low), data on D0-D7 plus generated even parity are written in the 9-bit memory location addressed by A0-A8. Also during write, a parity error may be forced by holding  $\overline{PE}$  low.

A reset input is provided for initialization. When  $\overline{\text{RESET}}$  is taken low, all 512  $\times$  9 RAM locations are cleared to zero (with valid parity) and the MATCH output is forced high. If an input data word of zero is compared to any memory location that has not been written into since reset, MATCH will be high indicating that input data, plus generated parity, is equal to the reset memory location.  $\overline{\text{PE}}$  will be high for every addressed memory location after reset indicating no parity error in the RAM data. By tying a single data input pin high, this bit will function as a valid bit and a match will not occur unless data has been written into the addressed memory location. When cascading in the width direction, only one bit needs to be tied high regardless of the address width.

The TACT2150 operates from a single 5 V supply and is offered in a 24-pin 300-mil ceramic side-brazed or plastic dual-in-line packages and plastic "Small Outline" packages. The device is fully TTL compatible and is characterized for operation from 0 °C to 70 °C.

### functional block diagram (positive logic)

#### MATCH OUTPUT DESCRIPTION

$$\begin{split} \text{MATCH} = \ V_{OH} \quad & \text{if:} \quad [\text{AO-A8}] = \text{DO-D7} + \text{parity.} \\ \text{or:} \quad & \overline{\text{RESET}} = V_{IL}, \\ \text{or:} \quad & \overline{\text{S}} = V_{IH}, \\ \text{or:} \quad & \overline{\text{W}} = V_{IL} \\ \end{split}$$

$$\text{MATCH} = \ V_{OL} \quad & \text{if:} \quad [\text{AO-A8}] \neq \text{DO-D7} + \text{parity,} \\ \text{with} \quad & \overline{\text{RESET}} = V_{IH}, \\ \overline{\text{S}} = \ V_{IL}, \text{ and } \overline{\text{W}} = V_{IH} \end{split}$$

#### **FUNCTION TABLE**

| OUTPUT |    | FUNCTION        |

|--------|----|-----------------|

| MATCH  | PE | DESCRIPTION     |

| L      | L  | Parity Error    |

| L      | н  | Not Equal       |

| н      | L  | Undefined Error |

| н      | Н  | Equal           |

#### PIN FUNCTIONAL DESCRIPTION

| PIN   |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME  | NÓ. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| AO    | 22  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A1    | 23  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A2    | 5   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A3    | 4   | Address from the Address Addre |  |  |  |  |

| A4    | 3   | Address inputs. Address 1 of 512-by-9-bit random-access memory locations. Must be stable for the duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| A5    | 2   | the write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| A6    | 19  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Α7    | 20  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A8    | 21  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D0    | 7   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D1    | 8   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D2    | 9   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D3    | 6   | Data inputs. Compared with memory location addressed by AO-A8 when $\overline{W}$ is at $V_{IH}$ and $\overline{S}$ is at $V_{IL}$ . Provide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| D4    | 17  | imput data to RAM when Wis at V <sub>IL</sub> and Sis at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D5    | 18  | · <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| D6    | 15  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D7    | 16  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| GND   | 12  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| MATCH | 14  | When MATCH output is at VOH during a compare cycle, D0 through D7 plus parity equal the contents of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|       |     | 9-bit memory location addressed by A0 through A8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PE    | 11  | Parity error input/output. During write cycles, PE can force a parity error into the 9-bit location specified by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|       |     | A0 through A8 when PE is at V <sub>IL</sub> . For compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|       |     | PE is an open-drain output so an external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| RESET | 1   | RESET input. Asynchronously clears entire RAM array and forces MATCH high when RESET is at VII and W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|       |     | is at V <sub>IH</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ই     | 13  | Chip select input. Enables device when \$\overline{S}\$ is at \$V_{IL}\$. Deselects device and forces MATCH high when \$\overline{S}\$ is at \$V_{IH}\$.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Vcc   | 24  | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| ₩     | 10  | Write control input, Writes D0 through D7 and generated parity into RAM and forces MATCH high when $\overline{W}$ is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|       |     | at V <sub>IL</sub> and $\overline{S}$ is at V <sub>IL</sub> . Places selected device in compare mode if $\overline{W}$ is at V <sub>IH</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

# application

Due to the high-performance switching characteristics of the TACT2150, it is necessary that the address inputs not be allowed to float. Proper termination techniques should be employed. It is recommended that the RC time constant associated with the address inputs (63.2% of rise time on AO-A8) not exceed 60 ns.

### absolute maximum ratings over operating free-air temperature range (unless otherwise specified)

| Supply voltage range, VCC (see Note 1)   |

|------------------------------------------|

| Input voltage range, any input           |

| Continuous power dissipation             |

| Operating free-air temperature range     |

| Storage temperature range65 °C to 150 °C |

NOTE 1: All voltage values are with respect to GND.

#### recommended operating conditions

|     |                                 | PARAMETER |  | MIN  | NOM | MAX                  | UNIT |

|-----|---------------------------------|-----------|--|------|-----|----------------------|------|

| Vcc | Supply voltage                  |           |  | 4.5  | 5   | 5.5                  | V    |

| VIH | High-level input voltage        |           |  | 2    | ,   | / <sub>CC</sub> +0.5 | V    |

| VIL | Low-level input voltage (See No | ote 21    |  | -0.5 |     | 0.8                  | V    |

| Voн | High-level output voltage       | PE        |  |      |     | 5.5                  | ٧    |

| ЮН  | High-level output current       | MATCH     |  |      | •   | -8                   | mA   |

| la. | Law lavel cutout aureast        | MATCH     |  |      |     | 8                    | mA   |

| lor | Low-level output current        | PE        |  |      |     | 16                   | mA   |

| TA  | Operating free-air temperature  |           |  | 0    |     | 70                   | °C   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                        |                                        | TEST CONDITIONS                                    |     | TACT2150-20      |       |     | TACT2150-30      |       |       |

|----------------------------------|----------------------------------------|----------------------------------------------------|-----|------------------|-------|-----|------------------|-------|-------|

|                                  |                                        |                                                    |     | TYP <sup>†</sup> | MAX   | MIN | TYP <sup>†</sup> | MAX   | UNIT  |

| MATCH high found output unlesses | IOH = -8 mA, VCC = 4.5 V               | 2.4                                                |     |                  | 2.4   |     |                  | v     |       |

| VOH(M)                           | VOH(M) MATCH high-level output voltage | $I_{OH} = -20  \mu A, V_{CC} = 4.5  V$             | 3.5 |                  |       | 3.5 |                  |       | i ' I |

| VOL(M)                           | MATCH low-level output voltage         | $I_{OL} = 8 \text{ mA},  V_{CC} = 4.5 \text{ V}$   |     |                  | 0.4   |     |                  | 0.4   | V     |

| VOL(PE)                          | PE low-level output voltage            | $I_{OL} = 16 \text{ mA},  V_{CC} = 4.5 \text{ V},$ |     |                  | 0.4   |     |                  | 0.4   | V     |

| lį                               | Input current                          | $V_1 = 0 \ V \ to \ 5.5 \ V$                       |     |                  | 10    |     |                  | 10    | μА    |

| los                              | Short-circuit MATCH output current     | $V_0 = GND$ , $V_{CC} = 5.5 V$                     |     |                  | - 150 |     |                  | - 150 | mA    |

| lcc1                             | Supply current (operative)             | RESET = VIH                                        |     | 53               | 95    |     | 53               | 95    | mA    |

| ICC2                             | Supply current (reset)                 | RESET = VL                                         |     | 2.75             | 6     |     | 2.75             | 6     | mA    |

| Ci                               | Input capacitance                      | f = 1 MHz                                          |     |                  | 5     |     |                  | 5     | рF    |

| Co                               | Output capacitance                     | f = 1 MHz                                          | L.  |                  | 6     |     |                  | 6     | pF    |

<sup>&</sup>lt;sup>†</sup>All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_{A} = 25 \text{ °C}$ .

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature

| PARAMETER             | TACT2                                                 | TACT2150-20 |     | TACT2150-30 |      |      |

|-----------------------|-------------------------------------------------------|-------------|-----|-------------|------|------|

| FANAMEICN             |                                                       | MIN         | MAX | MIN         | MAX  | UNIT |

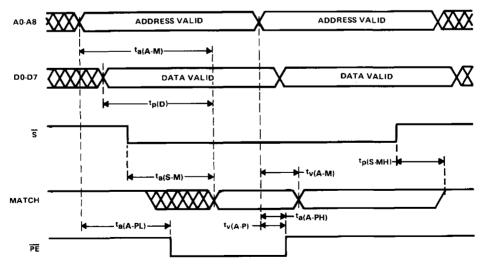

| ta(A-M)               | Access time from address to MATCH                     |             | 20  |             | . 30 | ns   |

| ta(A-PL)              | Access time from address to PE low                    |             | 22  |             | 30   | ns   |

| ta(A-PH)              | Access time from address to PE high                   |             | 30  |             | 35   | ns   |

| ta(S-M)               | Access time from \$\overline{S}\$ to MATCH            |             | 10  |             | 15   | ns   |

| tp(D)                 | Propagation time, data inputs to MATCH                |             | 15  |             | 20   | ns   |

| t <sub>p(R-MH)</sub>  | Propagation time, RESET low to MATCH high             |             | 10  |             | 15   | пŝ   |

| tp(S-MH)              | Propagation time, \$\overline{S}\$ high to MATCH high |             | 10  |             | 12   | ns   |

| tp(W-MH)              | Propagation time, W low to MATCH high                 |             | 10  |             | 12   | ns   |

| t <sub>p</sub> (W-PH) | Propagation time, W low to PE high                    |             | 15  |             | 20   | ns   |

| t <sub>v(A-M)</sub>   | MATCH valid time after change of address              | 3           |     | 3           |      | ns   |

| t <sub>V</sub> (A-P)  | PE valid time after change of address                 | 5           | -   | 5           |      | ns   |

# timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                     | PARAMETER                                        | TACT2 | TACT2150-20 |     | TACT2150-30 |      |

|---------------------|--------------------------------------------------|-------|-------------|-----|-------------|------|

|                     | PANAMETER                                        |       | MAX         | MIN | MAX         | UNIT |

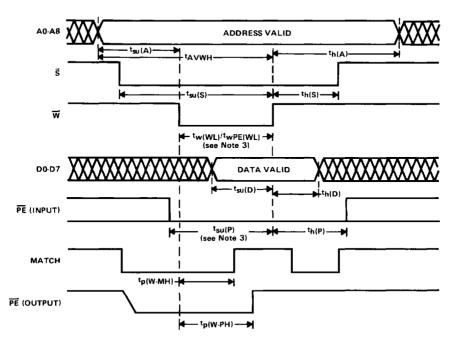

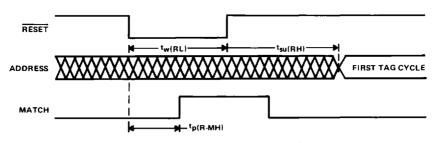

| tw(RL)              | Pulse duration, RESET low                        | 35    |             | 40  |             | ns   |

| tw(WL)              | Pulse duration, W low, without writing PE        | 20    |             | 25  |             | ns   |

| twPE(WL)            | Pulse duration, W low, writing PE (see Note 3)   | 20    |             | 25  |             | ns   |

| t <sub>su(A)</sub>  | Address setup time before ₩ low                  | 0     |             | 0   |             | ns   |

| t <sub>su(D)</sub>  | Data setup time before W high                    | 20    |             | 25  |             | ns   |

| t <sub>su(P)</sub>  | PE setup time before W high (see Note 3)         | 20    |             | 25  |             | ns   |

| t <sub>su(S)</sub>  | Chip select setup time before W high             | 20    |             | 25  |             | ns   |

| t <sub>su(RH)</sub> | RESET inactive setup time before first tag cycle | 0     |             | 0   |             | ns   |

| th(A)               | Address hold time after W high                   | 0     |             | 0   |             | ns   |

| th(D)               | Data hold time after W high                      | 0     |             | 0   |             | ns   |

| th(P)               | PE hold time after W high                        | 0     |             | 0   |             | ns   |

| th(S)               | Chip select hold time after W high               | 0     |             | 0   |             | ns   |

| tAVWH               | Address valid to write enable high               | 20    |             | 25  |             | ns   |

NOTE 3: Parameters twPE(WL) and tsu(P) apply only during the write cycle time when writing a parity error, tcPE(W).

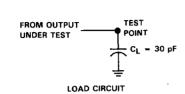

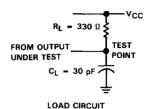

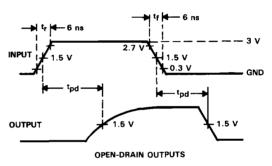

FIGURE 1. TOTEM-POLE OUTPUTS

FIGURE 2. OPEN-DRAIN OUTPUTS

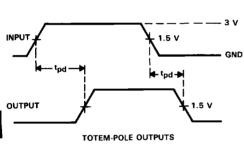

FIGURE 3. TIMING REFERENCE LEVELS

FIGURE 4. COMPARE CYCLE TIMING

#### PARAMETER MEASUREMENT INFORMATION

NOTE 3: Parameters  $t_{WPE(WL)}$  and  $t_{Su(P)}$  apply only during the write cycle time when writing a parity error,  $t_{CPE(Wl-VL)}$

#### FIGURE 5. WRITE CYCLE TIMING

FIGURE 6. RESET CYCLE TIMING