#### **FEATURES**

- 40 MHz operation

- Easy Interface to Motorola and Intel CPUs

- · 68040/68EC030 burst mode operation

- 1486 burst mode operation

- · Page, static column and nibble mode accesses

- Interleaved and non-interleaved accesses

- · Synchronous and asynchronous operation

- · Direct drive for 256K, 1Mbit and 4Mbit DRAMs

- Page switch detection logic

- Built in precision delay line

- Four Independent RAS and CAS outputs

- · Programmable wait state generation logic

- · Single or burst refresh

- · Error scrubbing during refresh

- · CMOS technology for low power consumption

- · TTL compatible inputs

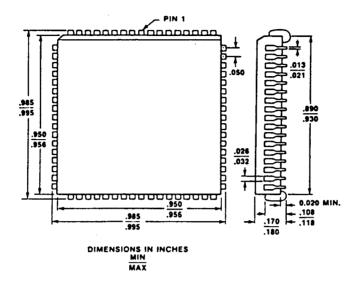

- 68-pin PLCC package

#### PRODUCT OVERVIEW

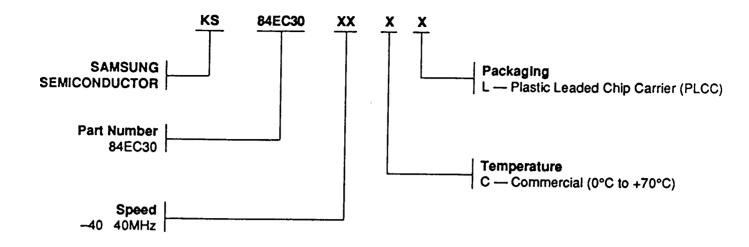

The Samsung KS84EC30 is a high performance DRAM controller designed for high speed DRAM arrays up to 4Mbytes in size. It simplifies the interface between the microprocessor and DRAM array, while also significantly reducing the required design time.

The KS84EC30 is an enhanced version of its KS84C31 counterpart. Like the KS84C31, this user programmable device is an economical and flexible design solution. The 26-bit programmable Mode Register allows the selection of various options and features.

The MC68EC030™, MC68040™ and i486™ microprocessors are supported by special programming modes specifically tailored to their bus operations.

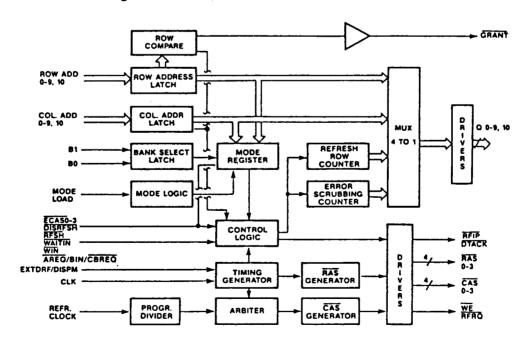

Figure 1 shows a block diagram of the KS84EC30.

Figure 1. KS84EC30 Block Diagram

MC68EC030, MC68040 are registered trademarks of Motorola, Inc.

<sup>1486</sup> is a registered trademark of Intel, Inc.

#### INTRODUCTION

The KS84EC30 is a dynamic RAM controller (hereafter referred to as DRC) which is built upon the proven KS84C31 architecture with enhancements that improve memory access time. The DRC contains all of the advanced features of the KS84C31 including the capabilities of address latches, refresh counter, refresh clock, address multiplexor, precision delay line, and refresh/access arbitration logic.

Improvements in the  $\overline{RAS}$ ,  $\overline{CAS}$  and address drivers reduce propagation delays by up to 42% over the KS84C31. A programmable system interface allows any manufacturer's CPU to be easily interfaced to DRAM arrays up to 4Mbytes in size.

The incorporation of on-chip page detection logic enables the DRC to support random accesses within a page for use with page and static column mode DRAMs. A 2-bit wrap around column counter may be used during burst accesses. On-chip RAS timeout circuitry enables the DRC to maintain an active RAS signal while EPROM or I/O is referenced, greatly improving system performance in embedded control applications and during data transfers between memory and I/O.

The MC68EC030, MC68040 and i486 burst cache fill accesses are supported. The special 68030 programming mode supports a burst memory access which doubles the 68EC030's cache hit ratio when compared against memory controllers that inhibit bursting.

The DRC must be programmed after power up before the DRAM array is referenced. The DRC is programmed through the address bus.

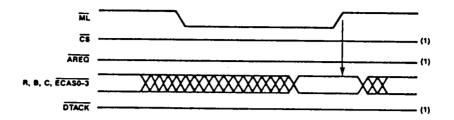

There are two methods of programming the chip. The first method, Mode Load , is performed by first asserting the mode load ( $\overline{\text{ML}}$ ) signal and presenting the programming selection on the row, column, bank and  $\overline{\text{ECAS}}$  inputs. The programming selection is loaded into the Mode Register when  $\overline{\text{ML}}$  is negated.

The second method, Fake Access, is performed by first asserting  $\overline{\text{ML}}$ , then performing a chip selected access. The programming value present on the address bus when  $\overline{\text{AREQ}}$  is asserted is loaded into the Mode Register. The DRC then asserts the appropriate control signals to terminate the chip selected access.

The DRC supports two access modes, synchronous (Access Mode 0) and asynchronous (Access Mode 1). To access the DRAM in Mode 0, the address latch enable (ALE) signal is asserted. RAS will be asserted on the next rising clock edge. To access the DRAM in Mode 1, the address strobe (ADS) signal is asserted causing RAS to be asserted immediately.

The KS84EC30 DRC offers four refreshing control modes:

- 1) internal automatic refreshing

- 2) internal automatic burst refreshing

- 3) externally controlled/burst refreshing

- 4) refresh request/acknowledge refreshing

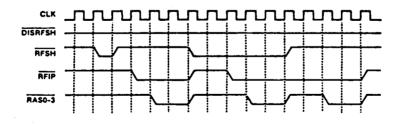

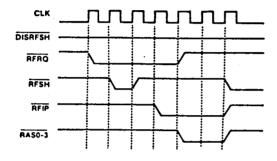

When using internal automatic refreshing, the DRC's refresh request clock generates internal refresh requests. The DRC arbitrates between refresh requests and accesses. If an access is not currently in progress, the DRC will assert the refresh in progress signal (RFIP). The refresh will start on the next rising clock edge. If an access had been in progress, the refresh would be delayed until the access is terminated.

Internal automatic burst refreshing is available when Page Mode is programmed. After the refresh request clock has generated the fifth internal refresh request, the DRC will arbitrate between the refresh request and any accesses in progress. The DRC will assert  $\overline{\text{RFIP}}$  and perform a five refresh burst.

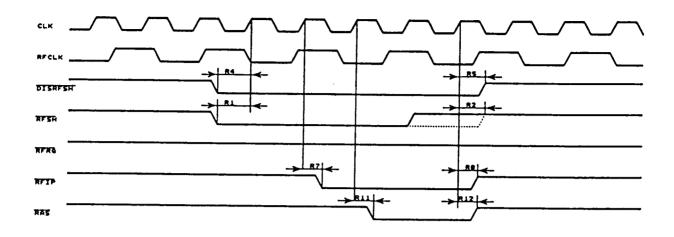

To use externally controlled burst/refreshing, the internally requested refreshes are disabled by asserting the disable refresh (DISFRSH) signal. A refresh can now be requested externally by asserting the refresh (RFSH) signal. The DRC will arbitrate between accesses and external refresh requests, assert RFIP and perform the refresh.

When refresh request/acknowledge refreshing is used, the DRC broadcasts the internal refresh request by asserting the refresh request (RFRQ) signal. External circuitry can determine when to enable the refresh by asserting RFSH. When RFSH is asserted, the DRC will perform an externally controlled/burst refresh.

The DRC supports two types of refreshing

- 1) RAS Only

- 2) RAS Only with Error Scrubbing

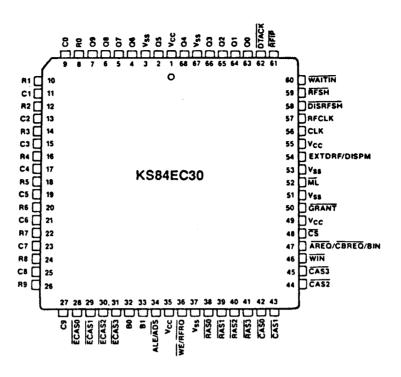

Figure 2. Pin Configuration of the KS84EC30 DRAM Controller

In a RAS only refresh, all the RAS outputs will be asserted and negated at once. Error scrubbing is the same as RAS only refresh except that a CAS and column address will be asserted during refresh, allowing the system to run the data through an error detection/correction chip and write it back to memory if an error has occured.

The DRC provides wait state support through its DTACK and GRANT output signals. Both signals may be used during Modes 0 and 1. DTACK is asserted by the on-chip wait state logic after a pre-programmed number of clock cycles to terminate the access. GRANT is asserted by the DRC to inform external circuitry that the DRC has begun an access. DTACK can be dynamically delayed by asserting the WAITIN input.

When a page miss is detected, the DRC will insert wait states during the access and precharge the memory.

The DRC has address latches, used to latch the row, column, and bank address inputs. The latches may also be used in fall through mode, even when the DRC is programmed for page mode operation. (The page address is latched in a separate page register).

The RAS and CAS drivers can be configured to drive a 1, 2, 3 or 4 bank memory array up to 36 bits in width (32 data, 4 parity). The CAS enable (ECAS) signals can then be used to selectively enable the CAS drivers for byte writing without requiring external logic. The DRC contains internal logic that ensures that the CAS outputs will not be asserted in case of a page miss, thus preventing spurious data writes to an incorrect page.

When configuring the DRC for more than one bank, memory interleaving can be used. The DRC can perform 2 or 4 way interleaving to eliminate wait states due to RAS prechage time.

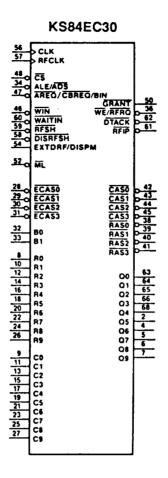

The KS84EC30, as shown in Figure 2, is available in a 68 pin PLCC and supports 256K, 1M and 4Mbit (1M · 4) DRAMs. The logic symbol is shown in Figure 3.

Figure 3. Logic Symbol

Table 1 shows detailed pin allocations for the KS84EC30.

Table 1. KS84EC30 Pin Allocations

| Pin<br>No. | Signal<br>Abbrev. | Signal Name                             |

|------------|-------------------|-----------------------------------------|

| 1          | V <sub>CC</sub>   | V <sub>CC</sub>                         |

| 2          | Q5                | Multiplexed Address 5                   |

| 3          | V <sub>SS</sub>   | V <sub>SS</sub>                         |

| 4          | Q6                | Multiplexed Address 6                   |

| 5          | Q7                | Multiplexed Address 7                   |

| 6          | Q8                | Multiplexed Address 8                   |

| 7          | Q9                | Multiplexed Address 9                   |

| 8          | R0                | Row Address 0                           |

| 9          | C0                | Column Address 0                        |

| 10         | R1                | Row Address 1                           |

| 11         | C1                | Column Address 1                        |

| 12         | R2                | Row Address 2                           |

| 13         | C2                | Column Address 2                        |

| 14         | R3                | Row Address 3                           |

| 15         | C3                | Column Address 3                        |

| 16         | R4                | Row Address 4                           |

| 17         | C4                | Column Address 4                        |

| 18         | R5                | Row Address 5                           |

| 19         | C5                | Column Address 5                        |

| 20         | R6                | Row Address 6                           |

| 21         | C6                | Column Address 6                        |

| 22         | R7                | Row Address 7                           |

| 23         | C7                | Column Address 7                        |

| 24         | R8                | Row Address 8                           |

| 25         | C8 -              | Column Address 8                        |

| 26         | R9                | Row Address 9                           |

| 27_        | C9                | Column Address 9                        |

| 28         | ECAS0             | Enable CAS0                             |

| 29         | ECAS1             | Enable CAS1                             |

| 30         | ECAS2             | Enable CAS2                             |

| 31         | ECAS3             | Enable CAS3                             |

| 32         | B0                | Bank Select 0                           |

| 33         | B1                | Bank Select 1                           |

| 34         | ALE/ADS           | Address Latch Enable/<br>Address Strobe |

| Pin<br>No. | Signal<br>Abbrev. | Signal Name                  |

|------------|-------------------|------------------------------|

| 35         | V <sub>CC</sub>   | V <sub>CC</sub>              |

| 36         | RFRQ/WE           | Refresh Request/Write Enable |

| 37         | V <sub>SS</sub>   | V <sub>SS</sub>              |

| 38         | RAS0              | Row Address Strobe 0         |

| 39         | RAS1              | Row Address Strobe 1         |

| 40         | RAS2              | Row Address Strobe 2         |

| 41         | RAS3              | Row Address Strobe 3         |

| 42         | CAS0              | Column Address Strobe 0      |

| 43         | CAS1              | Column Address Strobe 1      |

| 44         | CAS2              | Column Address Strobe 2      |

| 45         | CAS3              | Column Address Strobe 3      |

| 46         | WIN               | Write Enable Input           |

| 47         | AREQ              | Access Request               |

|            | CBREQ             | Cache Burst Request          |

|            | BIN               | Burst Inhibit                |

| 48         | CS                | Chip Select                  |

| 49         | Vcc               | V <sub>CC</sub>              |

| 50         | GRANT             | Access Grant                 |

| 51         | V <sub>SS</sub>   | V <sub>SS</sub>              |

| 52         | ML                | Mode Load                    |

| 53         | V <sub>SS</sub>   | V <sub>SS</sub>              |

| 54         | EXTORF            | Extend Refresh               |

|            | DISPM             | Disable Page Mode            |

| 55         | V <sub>CC</sub>   | V <sub>CC</sub>              |

| 56         | CLK               | Clock                        |

| 57         | RFCLK             | Refresh Clock                |

| 58         | DISRFSH           | Disable Internal Refresh     |

| 59         | RFSH              | External Refresh Request     |

| 60         | WAITIN            | Add Wait State               |

| 61         | RFIP              | Refresh in Progress          |

| 62         | DTACK             | Data Transfer Acknowledge    |

| 63         | Q0                | Multiplexed Address 0        |

| 64         | Q1                | Multiplexed Address 1        |

| 65         | Ω2                | Multiplexed Address 2        |

| 66         | Q3                | Multiplexed Address 3        |

| 67         | V <sub>SS</sub>   | V <sub>SS</sub>              |

| 68         | Q4                | Multiplexed Address 4        |

Table 2. Interface Signal Descriptions

| Symbol             | Туре | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Access Signals     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ADS (ALE)          | ı    | Address Strobe (Address Latch Enable): This input latches row, column and bank addresses, and initiates the DRAM access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |      | ADS (ALE) must be invoked for every non-burst access. ADS (ALE) need only be invoked for the opening cycle of a burst access when used with microprocessors that only assert ADS (ALE) during the opening cycle.                                                                                                                                                                                                                                                                                                                                                                              |

|                    |      | In Access Mode 0, this input functions as Address Latch Enable (ALE). In Access Mode 1, this input functions as Address Strobe (ADS).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CS                 | l    | Chip Select: The $\overline{CS}$ input must be active to enable a DRAM access. $\overline{CS}$ must enable every non-burst access. $\overline{CS}$ need only be invoked for the opening cycle of a burst access when used with microprocessors that only assert $\overline{ADS}$ (ALE) during the opening access.                                                                                                                                                                                                                                                                             |

| AREQ (CBREQ) (BIN) | ı    | Access Request (Cache Burst Request) (Burst Inhibit): This input terminates an access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    |      | AREQ: In Single Access Mode, this input functions as Access Request. It brings RAS and CAS high to terminate the access. In Page Access Mode, AREQ only brings CAS high.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |      | CBREQ: In 68030 Burst Mode, this signal functions as Cache Burst Request. CBREQ is sampled on the rising edge of CLK that negates DTACK. Directly compatible with the MC68EC030's CBREQ signal, it controls the termination of the DRC's burst access. It brings RAS and CAS high to terminate the burst. When combined with Page Mode, only CAS is brought high.                                                                                                                                                                                                                             |

|                    |      | BIN: When programmed for 68040 Burst Mode, this signal functions as Burst Inhibit. Burst Inhibit is sampled on the rising edge of CLK that negates DTACK. BIN prevents the DRC from bursting if the CPU aborts the burst or is performing a single access. It brings RAS and CAS high to terminate the burst. When combined with Page Mode, only CAS is brought high.                                                                                                                                                                                                                         |

| DTACK              | 0    | Data Transfer Acknowledge: This output is asserted to terminate the CPU access. In Single Access Mode and Page Mode, it is negated when the access is terminated by AREQ. In both burst modes, DTACK is negated on the first rising clock edge after it has been asserted.                                                                                                                                                                                                                                                                                                                    |

| WAITIN             |      | Walt State Insert: This input is used to dynamically add wait states during a bus cycle. If R6=0 during programming, WAITIN is used to add one wait state during the access. WAITIN is sampled once during the access, when DTACK is to be asserted by the DRC. DTACK will remain negated for one more rising CLK edge if DTACK is rising edge triggered or one more falling CLK edge if DTACK is falling edge triggered. WAITIN will not be sampled again, until the next access.                                                                                                            |

| •                  |      | If R6=1 during programming, WAITIN may be used to defer DTACK indefinitely. WAITIN is sampled at the access start. If WAITIN is inactive, the DRC will assert DTACK after the programmed number of CLK edges. If WAITIN was active, the DTACK CLK edge count is deferred. WAITIN will be continually sampled on the rising edge of CLK if DTACK is rising edge triggered or on the falling edge of CLK if DTACK is falling edge triggered. Once WAITIN is negated, the DRC will assert DTACK after the programmed number of CLK edges and will not sample WAITIN again until the next access. |

Table 2. Interface Signal Descriptions (Continued)

| Symbol                | Туре                       | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Access Signals (Conti | Access Signals (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GRANT                 | 0                          | Access Grant: This output is asserted only when RAS is asserted for a DRAM access. It is asserted at the beginning of an access to indicate that the access has begun. If an access is deferred due to a refresh cycle, page miss, or to satisfy RAS precharge time, GRANT will not be asserted until the access has begun. GRANT will remain asserted until the access RAS is negated.                                                                               |  |  |  |

| Address, R/W and Pro  | gramm                      | ing Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| C0-9                  | 1                          | Column Address Inputs: These address bits are connected to the CPU's address bus. When the DRC is programmed for use with page mode or static column DRAMs, they should be connected to the low order address bits.                                                                                                                                                                                                                                                   |  |  |  |

| R0-9                  | J                          | Row Address Inputs: Theses address bits are connected to the CPU's address bus. When the DRC is programmed for use with page or static column mode DRAMs, they should be connected to the higher order address bits.                                                                                                                                                                                                                                                  |  |  |  |

| B0, B1                | ı                          | Bank Select: These inputs select the memory bank to be addressed. Up to four banks are supported by the DRC.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| ECASO-3               | ı                          | Enable CAS0-3: These inputs are used to enable or disable individual CAS outputs when accessing bytes, words or doublewords. They can also be used to delay the falling edge of CAS.                                                                                                                                                                                                                                                                                  |  |  |  |

| WIN                   | l                          | Write Enable Input: This input controls the Write Enable (WE) output. If programmed to do so, it also delays the falling edge of CAS by one rising CLK edge during page hits and one CLK period during burst accesses. It does not delay the falling edge of CAS in Single Access Mode or the opening cycle of a burst access that results in a page miss. When the leading edge of CAS is delayed by WIN, one wait state is automatically added to the access cycle. |  |  |  |

|                       |                            | WIN is sampled when a burst or page hit access starts in all operating modes and also on the rising edge of CLK that negates DTACK when the DRC is bursting.                                                                                                                                                                                                                                                                                                          |  |  |  |

| ML                    | ı                          | <b>Mode Load</b> : This input strobes the row, column, bank and ECASO-3 inputs into the Mode Register.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DRAM Control Signals  | 3                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

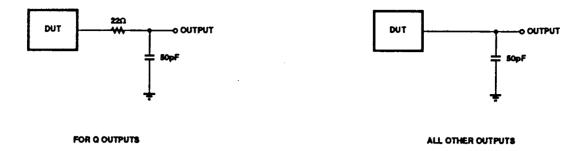

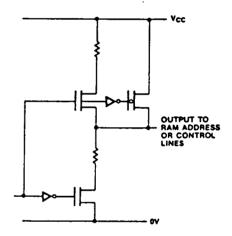

| Q0-9                  | 0                          | Address Outputs: These outputs are the multiplexed address bits (R0-9, C0-9). They access the memory for read, write and refresh operations. The output loading is rated at 50 pF. 22 ohm series damping resistors are suggested for the Q outputs.                                                                                                                                                                                                                   |  |  |  |

| RAS0-3                | 0                          | Row Address Strobe: These output signals are used to strobe the row address into the DRAM.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CAS0-3                | 0                          | Column Address Strobe: These output signals are used to strobe the column address into the DRAM.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| WE (RFRQ)             | 0                          | Write Enable (Refresh Request): After power up and when the DRC is programmed for interleaved operation, this output functions as Refresh Request. When the DRC is not programmed for interleaved operation, this output may be programmed as Write Enable or Refresh Request.                                                                                                                                                                                        |  |  |  |

|                       |                            | When programmed as WE, this output is controlled by the WIN input. The output loading is rated at 50 pF. When programmed as RFRQ, the DRC asserts this output whenever a refresh request has been generated by the internal refresh interval timer. RFRQ is negated when the refresh begins.                                                                                                                                                                          |  |  |  |

Table 2. Interface Signal Descriptions (Continued)

| Symbol               | Туре | Descriptions                                                                                                                                                                                                                                                                                                      |

|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Refresh Control Sign | nals |                                                                                                                                                                                                                                                                                                                   |

| EXTORF (DISPM)       | ı    | Extend Refresh (Disable Page Mode): When the DRC is programmed to support error scrubbing, this pin is time multiplexed.                                                                                                                                                                                          |

|                      |      | During refresh, this input extends the refresh cycle to allow a read-modify-write cycle to be performed in a system with error scrubbing. During accesses, this pin is used to terminate RAS when the DRC is programmed for Page Mode.                                                                            |

|                      |      | When the DRC is not programmed to support error scrubbing, this pin only functions as Disable Page Mode and does not affect refresh cycles.                                                                                                                                                                       |

| DISRFSH              | 1    | Disable Internal Refresh: This input prevents the DRC from performing internally requested refreshes. This signal could be asserted to prevent the DRC from performing refreshes during DMA transfers, while the CPU is executing time critical code or if refreshes are going to be controlled externally.       |

| RFIP                 | 0    | Refresh In Progress: This output indicates that a refresh cycle is in progress. RFIP is asserted one clock cycle prior to the start of a refresh cycle.                                                                                                                                                           |

| RFSH                 | l    | External Refresh: Refresh requests can be generated externally by asserting this input when DISRFSH is low.                                                                                                                                                                                                       |

| Clock Inputs         |      |                                                                                                                                                                                                                                                                                                                   |

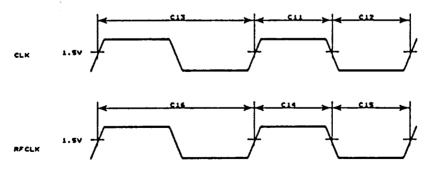

| CLK                  | ı    | Sytem Clock: This input should be connected to the system bus clock. It is used for access arbitration and timing.                                                                                                                                                                                                |

| BFCLK                | 1    | Refresh Clock: This input determines the interval between internally requested refreshes. RFCLK must be synchronous to CLK, but need not be the same frequency as CLK. It is divided internally, according to the value in the Mode Register, so that refresh requests are generated at 15 μs or 13 μs intervals. |

#### **ACCESS START AND TERMINATION MODES**

The KS84EC30 supports both synchronous and asynchronous access modes. The user selects the mode best suited to the microprocessor by programming bit B1 of the Mode Register.

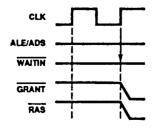

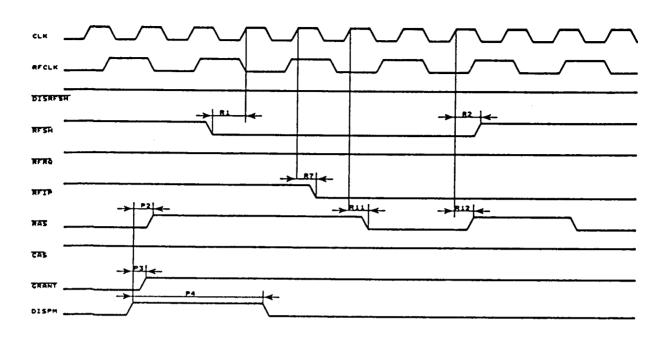

## Mode 0 — Synchronous Access Start and Termination

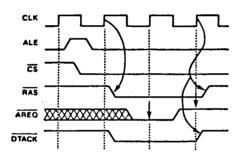

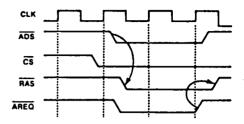

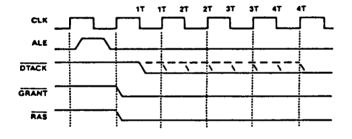

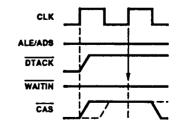

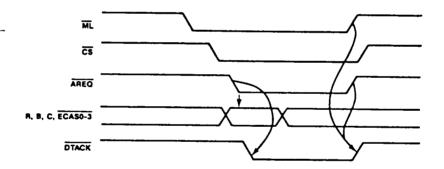

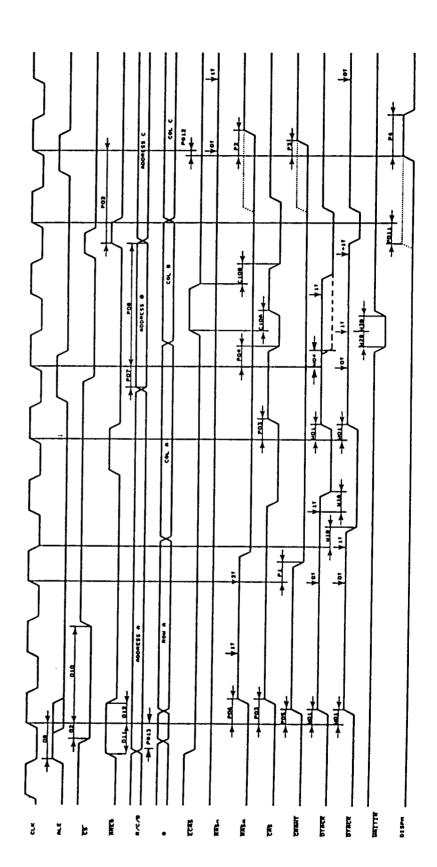

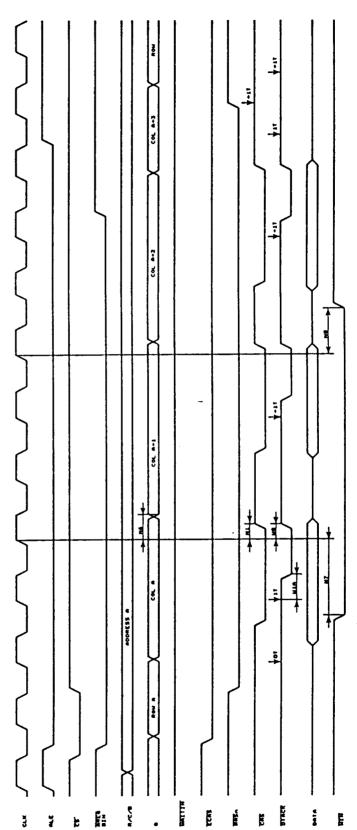

Mode 0 is selected when B1 = 0 during programming. To initiate a Mode 0 access, ALE is pulsed high and a valid  $\overline{CS}$  signal is asserted before the input clock's (CLK) rising edge. The access will start on the rising edge of CLK as shown in Figure 4, provided that the ALE and  $\overline{CS}$  setup times were observed, the  $\overline{RAS}$  precharge time was met and a refresh was not currently in progress. If the  $\overline{RAS}$  precharge time was not met from the previous access or a refresh was in progress, the DRC will wait until these events have taken place before asserting  $\overline{RAS}$  on the rising edge of CLK.

The DRC will begin sampling AREQ on the rising edge of CLK after DTACK is asserted. The access will continue until AREQ is negated.

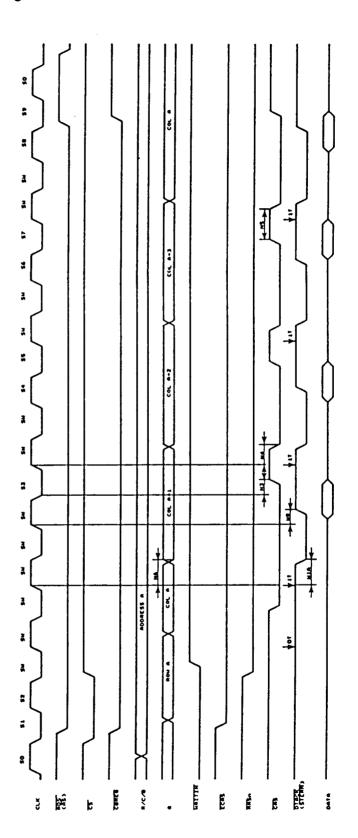

Figure 4. Synchronous Access Start and Termination

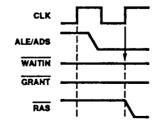

# Mode 1 — Asynchronous Access Start and Termination

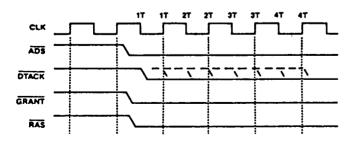

Mode 1 is selected when B1 = 1 during programming. To initiate a Mode 1 access,  $\overline{CS}$  is asserted, followed by  $\overline{ADS}$ . The access will start when  $\overline{ADS}$  is asserted as shown in Figure 5, provided that the  $\overline{RAS}$  precharge time was met and a refresh was not currently in progress. If the  $\overline{RAS}$  precharge time was not met from the previous access or a refresh was in progress, the DRC will wait until these events have taken place before asserting  $\overline{RAS}$  on the rising edge of CLK. The access will be terminated when  $\overline{AREQ}$  is negated.

Figure 5. Asynchronous Access Start and Termination

#### **OPERATING MODES**

The KS84EC30 may be programmed to operate in several different modes, depending on the CPU characteristics and type of DRAM used. The Single Access Mode is recommended for use in slower speed systems in which there is no advantage to be gained from a CAS only access and where the RAS precharge time is hidden between back to back accesses. For higher performance systems, Page Mode operation is provided and may be used with page or static column DRAMs. Two versions of burst mode operation, 68030 Burst Mode and 68040 Burst Mode are provided to support CPUs that are capable of performing burst accesses. Both burst modes may be used with nibble, page or static column DRAMs.

Interleaved Access Mode can provide a performance advantage when used in systems that support address pipelining. The user selects the operating mode best suited to the system's requirements by programming bits C4, C5, C6 and ECAS1-3 in the Mode Load Register.

#### Single Access Mode

Single Access Mode is selected when ECAS1, ECAS2, ECAS3 = 0,0,0 during programming. The access is initiated by two signals, ADS(ALE) and CS, and is terminated by one signal, AREQ. Both RAS and DTACK are negated when the access is terminated.

The user has the option of negating  $\overline{CAS}$  when the access is terminated or up to one clock period later. If  $\overline{ECASO}$  = 0 during programming,  $\overline{CAS}$  will be negated with  $\overline{RAS}$  and  $\overline{DTACK}$ . If  $\overline{ECASO}$  = 1 during programming,  $\overline{CAS}$  will remain asserted until the next rising CLK edge or the rising edge of  $\overline{ECAS}$ , whichever occurs first. This allows the DRAM to continue to drive the data bus while  $\overline{RAS}$  is precharging. See Figure 6.

Figure 6. Single Access Mode with Synchronous Access Start and Extended CAS

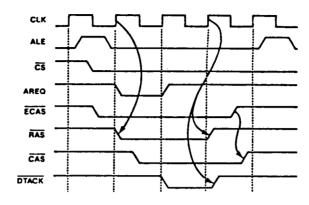

#### Page Mode Access

Page Mode is selected when ECAS1, ECAS2, ECAS3 = 0,1,0 during programming. Page Mode allows the CPU to access random columns within a page without having to pay the penalties associated with RAS access and precharge time. Both page and static column mode DRAMs may be used. It is very similar in operation to the Single Access Mode, with only two notable exceptions:

- 1) Only CAS and DTACK are negated when AREQ terminates the access.

- 2) The DRC maintains RAS low even when the CPU is not accessing DRAM.

On-chip page detection logic detects page hits and misses. The DRC's on-chip wait state logic delays the assertion of DTACK in case of a page miss to allow for RAS precharge and RAS access time. An external signal, GRANT, is asserted to indicate to external circuitry when the access has begun.

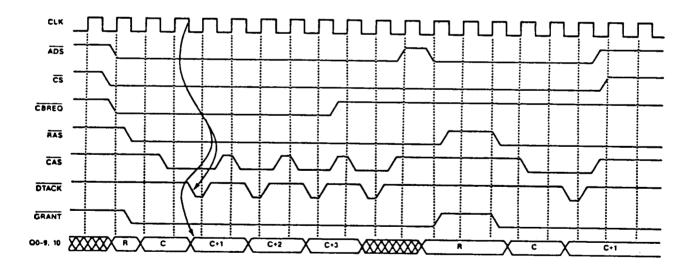

Several Page Mode accesses are shown in Figure 7. Access A occurred after a refresh cycle. The access was not delayed due to RAS precharge since the CPU initiated the access after the RAS was already precharged. Access B is a page hit. Access C is a page miss. Access D is an access to a memory location other than DRAM.

Figure 7. Page Mode Accesses

When programmed for Page Mode operation ( $\overline{ECAS2}$  = 1), the DRC maintains  $\overline{RAS}$  and  $\overline{GRANT}$  low for 5 internal refresh requests (75  $\mu$ s). After the 5th internal refresh request, both signals will be negated when  $\overline{AREQ}$  terminates the access. The DRC will then perform a 5 refresh burst.

Certain applications may require that, at certain times, the DRAM is precharged prior to an access start. Since it is impossible to ensure that a given access will result in a page hit, and if the penalty of a page miss is intolerable, DISPM may be used to negate RAS when an access is completed.

If DISPM is asserted when there is no access or refresh in progress, RAS is negated immediately. If DISPM is asserted during an access, AREQ will negate both RAS and CAS when the access is completed. The DRC will continue to function as though it were programmed for Single Access Mode operation as long as DISPM is asserted. After DISPM is negated, all pending refreshes (up to 5) will be performed in a burst refresh.

When the DRC is not programmed to support error scrubbing, DISPM has no effect on  $\overline{RAS}$  during refreshes. When the DRC is programmed to support error scrubbing, DISPM is time multiplexed with EXTDRF. EXTDRF will cause the refresh  $\overline{RAS}$  to be extended when it is sampled active on the rising edge of CLK that was programmed to negate  $\overline{RAS}$ .

#### **Burst Mode Accesses**

In order to support high performance CPUs that can perform up to 4 memory accesses in a single burst, the MC68EC030 is capable of performing 4 accesses when provided with the starting address of the burst. The DRC supports two forms of burst mode operation. When programmed for 68040 Burst Mode, CAS is asserted on the falling edge of CLK and is negated on the rising edge of CLK. This mode should be used when the data is to be sampled on the rising edge of CLK such as with the MC68040 and i486 CPUs. To accommodate CPU's that sample data on the falling edge of CLK, such as the MC68EC030, 68030 Burst Mode should be used. In 68030 Burst Mode, CAS is asserted on the rising edge of CLK and is negated on the falling edge of CLK.

The user has the choice of using nibble, page or static column DRAMs in both burst modes. An on-chip address counter may be used while bursting, if desired. The 2-bit address counter wraps around to support CPU's that wrap around when filling their cache lines. The user can

choose when to increment the address counter depending on whether page or static column DRAMs are used. The DRC's burst access can be terminated early if the CPU is performing a single access or aborts the burst.

Either burst mode may be combined with Page Mode operation to reduce the number of clock cycles required for the opening access of the burst by programming ECAS2 = 1. When programmed in combination with Page Mode, CAS will be negated, but RAS will remain asserted after the last access of the burst.

If DISPM is asserted during an access, both  $\overline{RAS}$  and  $\overline{CAS}$  are negated when the access is completed. The DRC will continue to function as though it were not programmed for Page Mode ( $\overline{ECAS2}$  = 0) as long as DISPM is asserted. After DISPM is negated, all pending refreshes (up to 5) will be performed in a burst refresh.

The on-chip address counter is enabled when the address latches are programmed to latch the address on the falling edge of  $\overline{ADS}(ALE)$ . If the latches are transparent, the counter is disabled. When the latches are transparent, external circuitry may be used to provide a new column address to the DRC.

If the on-chip address counter is used, the user needs to select when the counter is incremented. If static column DRAMs are used, R6=0 should be programmed. If page mode DRAMs are used, R6=1 may be programmed. When R6=0, the column address will be incremented when  $\overline{CAS}$  is negated. When R6=1, the column address is incremented before the access is completed, on the CLK edge that asserts  $\overline{DTACK}$ .

The CAS strobe is negated when the DRAM access is completed, even when static column DRAMs are used. This insures that data is not strobed into the incorrect page if a page miss occurs during a write access.

Since the CAS propagtion delay and precharge time is matched to the DRC's column address increment propagation delay, there is no performance penalty associated with bringing CAS high.

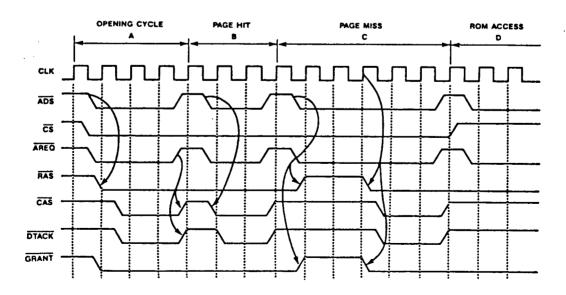

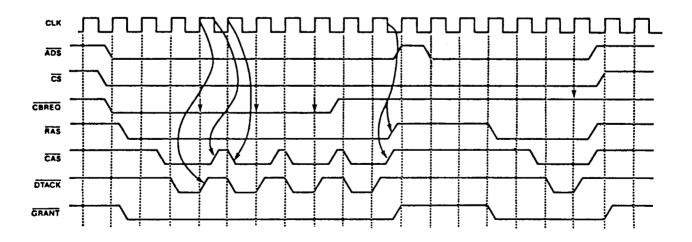

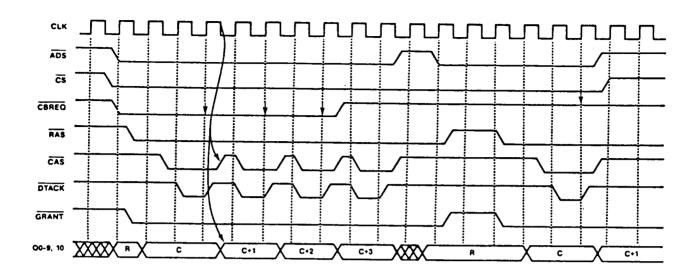

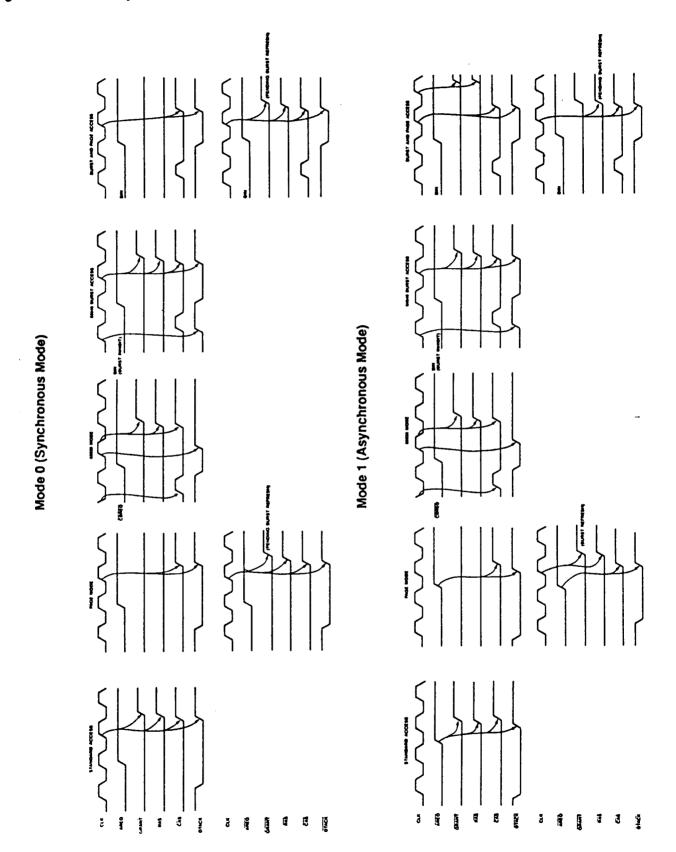

#### 68040 Burst Access Mode

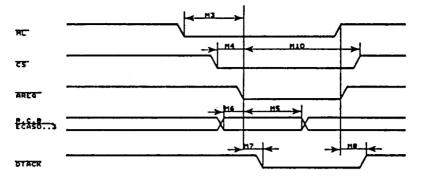

68040 Burst Mode operation is selected when  $\overline{\text{ECAS1}}$ ,  $\overline{\text{ECAS3}}$  = 0,1 during programming.

When programmed for 68040 Burst Mode, CAS is always negated by the same rising CLK edge that negates DTACK. CAS is always asserted on the next falling CLK edge unless the DRC has completed the burst or if the burst was aborted.

The DRC's burst can be aborted by asserting the DRC's Burst Inhibit (BIN) input. BIN is sampled on the rising edge of CLK that negates CAS and DTACK, and if asserted, the burst is aborted. Once aborted, the next access must be initiated with ADS(ALE) and CS.

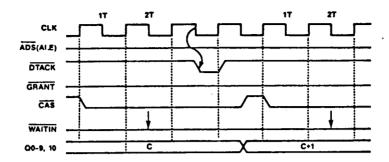

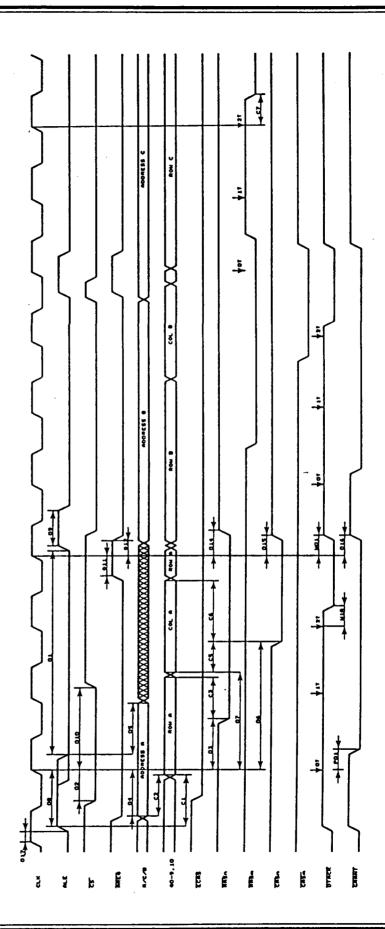

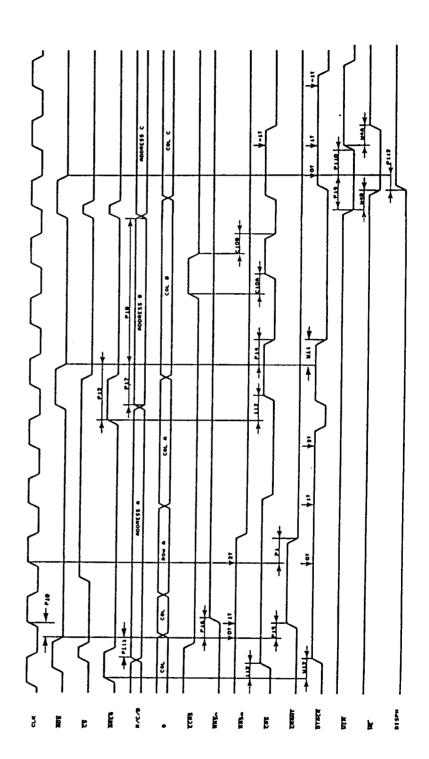

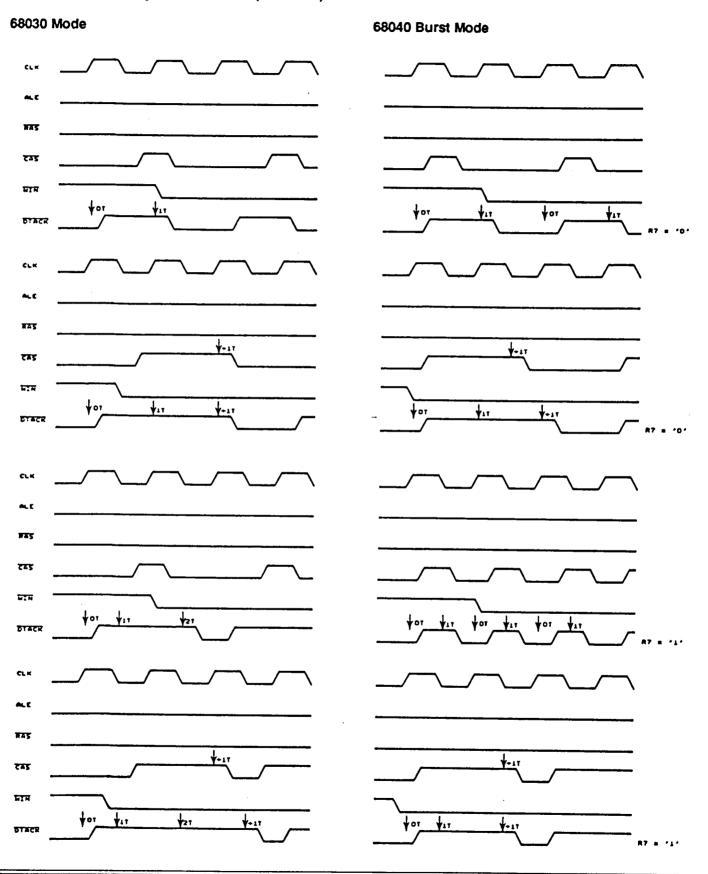

Two 68040 Burst Mode accesses are shown in Figure 8. During the first access, the DRC is allowed to complete

the burst normally. The second access was deferred due to  $\overline{RAS}$  precharge. The burst was aborted during the second access by asserting BIN.

Figures 9 and 10 show the same accesses when 68040 Burst Mode is combined with Page Mode. In the case of Figures 9 and 10, the RAS precharge is due to a page miss.

Figure 8. 68040 Burst Mode Access (ECAS2 = 0 Programmed)

Figure 9. Burst Mode Access with Page Mode (ECAS2 = 1, R6 = 0 Programmed)

Figure 10. Burst Mode Access with Page Mode (ECAS2 = 1, R6 = 1 Programmed)

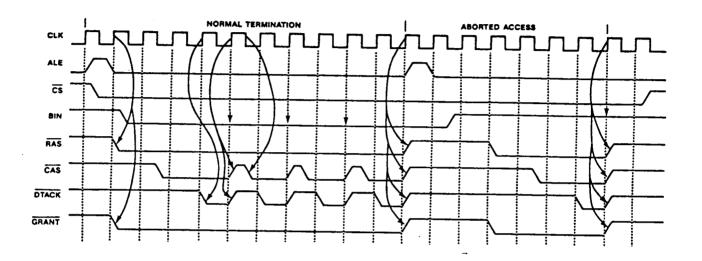

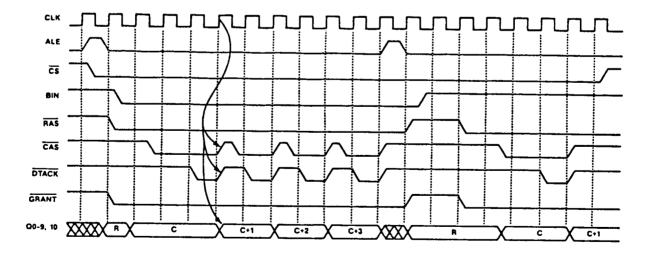

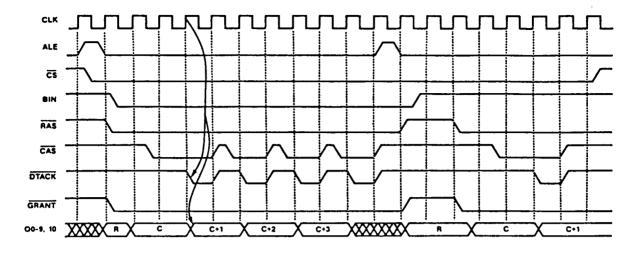

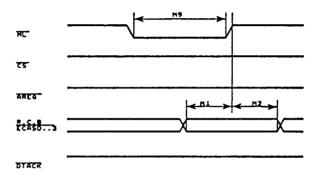

#### 68030 Burst Access Mode

The MC68EC030's synchronous burst cache fill operation is supported by programming the DRC for 68030 Burst Mode operation. 68030 Burst Mode operation is very similar to 68040 Burst Mode operation, with only two notable exceptions:

- 1) CAS is asserted on the rising edge of CLK and negated on the falling edge.

- 2) The handshake input CBREQ is provided and is sampled on the rising edge of CLK that negates DTACK.

The DRC's DTACK output drives the MC68EC030's STERM and CBACK inputs.

68030 Burst Mode operation is selected when  $\overline{\text{ECAS1}}$ ,  $\overline{\text{ECAS3}} = 1.0$  during programming.

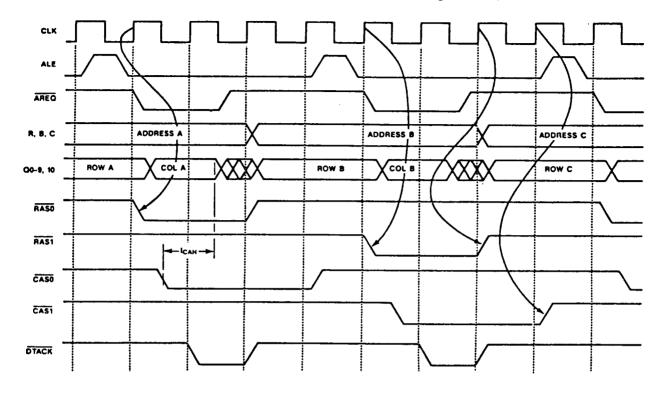

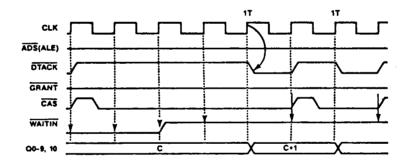

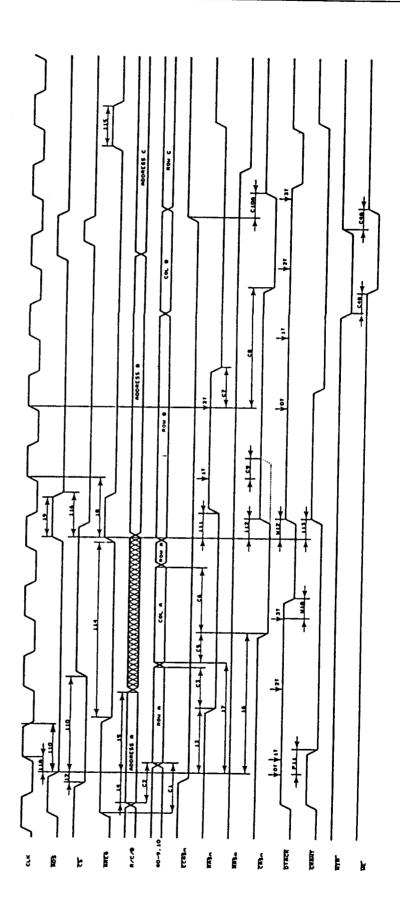

Two 68030 Burst Mode accesses are shown in Figure 11. During the first access, the DRC is allowed to complete the burst normally. The second access was deferred due to RAS precharge. The burst was aborted during the second access by negating CBREQ.

Figures 12 and 13 show the same accesses when 68030 Burst Mode is combined Page Mode. In the case of Figures 12 and 13, the RAS precharge is due to a page miss.

Figure 11. 68030 Burst Mode Access (ECAS2 = 0 Programmed)

Figure 12. 68030 Burst Mode with Page Mode ( $\overline{ECAS2} = 1$ , R6 = 0 Programmed)

Figure 13. 68030 Burst Mode with Page Mode (ECAS2 = 1, R6 = 1 Programmed)

#### Interleaved Access Modes

The KS84EC30 supports 2 or 4-way interleaved accesses between memory banks. By interleaving accesses, performance degradation due to RAS access and precharge time is minimized.

Interleaved Access Mode may be used in systems that support address pipelining. When interleaving accesses, the DRC supplies the next row address after the column address hold time is satisfied for the current access. If the next access is to a different bank of memory than the current access. RAS will be asserted for the next access by ALE(ADS).

Interleaved Access Mode is selected by programming the RAS and CAS configuration bits C4, C5 and C6. These bits enable the DRC to initiate an access to one bank with ALE(ADS) while maintaining an access to another bank with AREQ. The GRANT output should not be used in this mode.

The ECASn bits should be programmed for Single Access Mode for proper interleaved operation. R8 = 0 should be programmed so that the DRAM controller will drive the new row address onto the bus after the column address hold time for the current access is satisfied.

Interleaved Access Mode should not be used in conjunction with page or burst mode operation. However, the RAS precharge time is hidden in these modes if consecutive accesses hit different banks. Only one CLK of precharge will be incurred when switching banks. The programmed number of precharge clock cycles will be observed if consecutive access hit the same memory bank.

#### **Wait State Support**

Wait states are required when a relatively slow DRAM is operating with a fast CPU. Wait states allow the CPU's bus cycle to be extended by one or more CPU clock periods. The KS84EC30 will insert wait states during the CPU's DRAM bus access in order to:

- insert the desired number of wait states during the access.

- delay the access until the refresh in progress is complete, or

- c) delay the access to guarantee RAS precharge time.

The DRC generates two output signals to support the insertion of wait states. GRANT is asserted to inform external logic that the DRC has begun an access. DTACK is asserted to terminate the access. An input signal, WAITIN, is provided to allow the user to add wait states dynamically during the access.

GRANT mimics the operation of RAS during an access. Like RAS, it is asserted synchronous to CLK in Mode 0 and asynchronous to CLK in Mode 1 and remains active until RAS is negated. In case of a page miss, both GRANT and RAS will remain negated for at least 1T so that GRANT may be sampled by external circuitry to determine if a page miss has occured. GRANT is deasserted during refresh operations.

When programmed for Page Mode operation, GRANT will remain asserted for two rising edges of CLK after ADS is asserted while the DRC is arbitrating between the access and the 5th internal refresh request (See Automatic Internal Burst Refreshing).

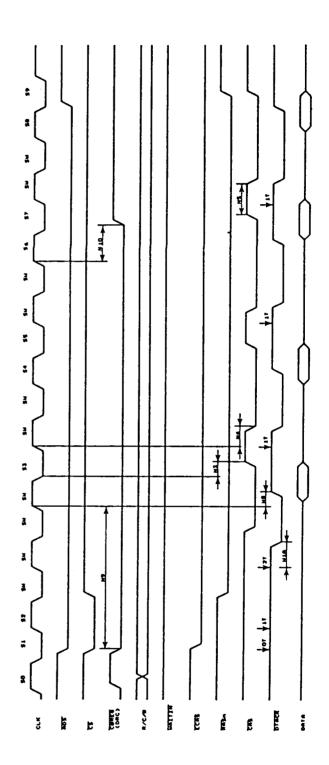

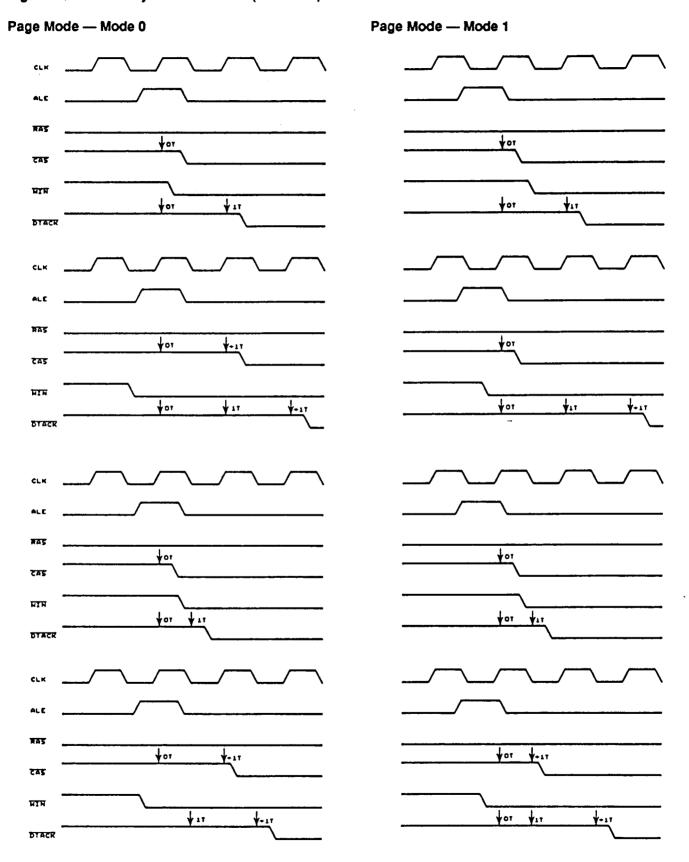

DTACK may be programmed (via R7) to be asserted on the rising or falling CLK edge. The number of CLK edges that DTACK is delayed, is programmable. DTACK is controlled by programming bits R2 and R3 for any access during which RAS is initially asserted (i.e. single accesses, page misses, etc). Programming bits R4 and R5 control DTACK during page hits and while bursting.

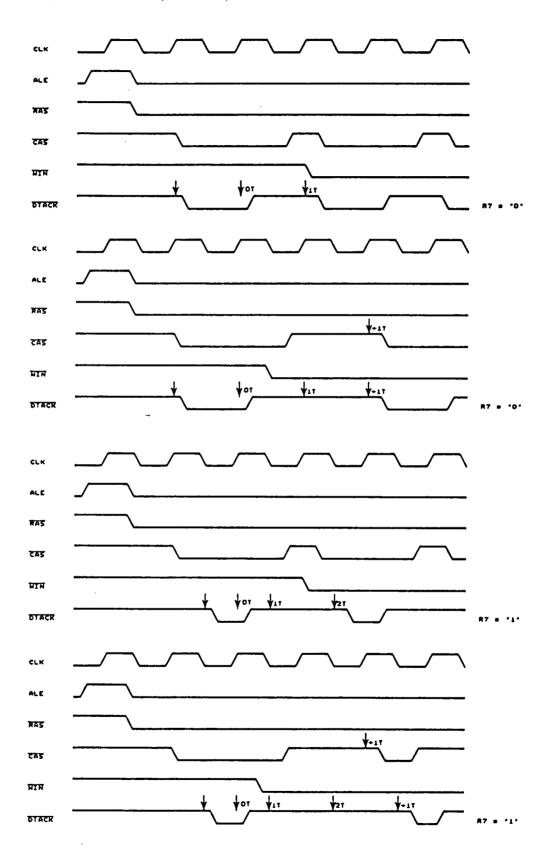

Figures 15 and 16 show how DTACK behaves in Mode 0 and 1 accesses during which RAS is initially asserted. Figures 17 and 18 shows how DTACK behaves during page hits.

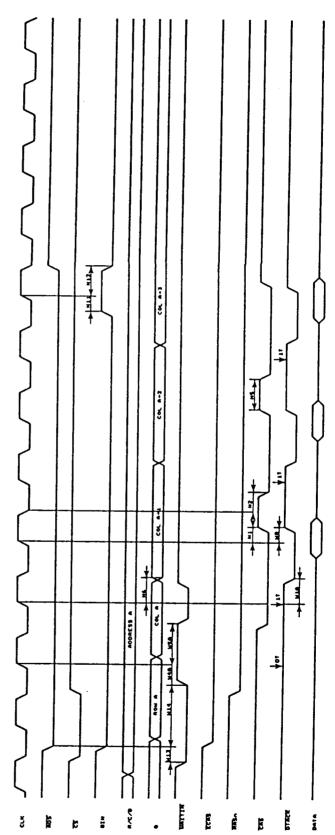

Figure 14. 2-Way Interleaved Access Mode Operation (ECASO = 1 Programmed)

DTACK

CAS

Figure 15. DTACK During Mode 0 Accesses, RAS Initially Asserted

OT 17 17 27 27 37 37 CLX

Figure 17. DTACK During Mode 0 Page Hits

Figure 16. DTACK During Mode 1 Accesses, RAS Initially Asserted

Figure 18. DTACK During Mode 1 Page Hits

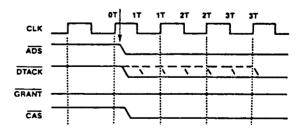

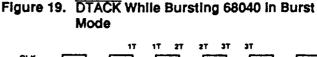

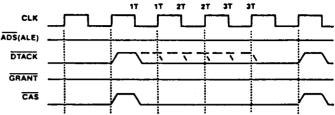

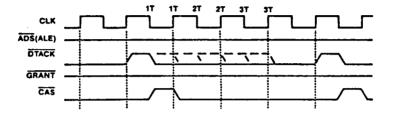

When used in 68040 Burst Mode or 68030 Burst Mode, the DRC should not be programmed for 0T operation for page hits and subsequent burst cycles. This will not impact memory performance, since the opening cycle of a burst access would be expected to have at least one wait state. Regardless of when DTACK is asserted, it is always negated on the next rising CLK edge in both burst modes, as shown in Figures 19 and 20.

Figure 20. DTACK While Bursting in 68030 Burst Mode

Any access may be extended on the fly by asserting the WAITIN input. If R6 = 0 during programming, WAITIN is used to add one wait state during the access as shown in Figure 21. WAITIN is sampled once during the access, when DTACK is to be asserted by the DRC. DTACK will remain negated for one more rising CLK edge if DTACK is rising edge triggered or one more falling CLK edge if DTACK is falling edge trigered. WAITIN will not be sampled again, until the next access.

If R6 = 1 during programming, WAITIN may be used to defer DTACK indefinitely as shown in Figure 22. WAITIN is first sampled on:

- The falling edge of ADS (Mode 1)

- The first rising edge of CLK after ALE is pulsed high (Mode 0)

- The CLK edge that negates DTACK while bursting

If the access start is deferred due to RAS precharge, page hit writes or burst writes WAITIN is sampled again on:

- The rising edge of CLK that asserts RAS during a deferred access

- The rising edge of CLK that asserts CAS if CAS is delayed during page hit writes (C9 = 1 programmed)

- The next rising CLK edge after the CLK edge that negates DTACK during burst writes (C9 = 1 programmed)

The status of WAITIN when it was last sampled takes precedence for that access.

If WAITIN is inactive, the DRC will assert DTACK after the programmed number of CLK edges. If WAITIN was active, the DTACK CLK edge count is deferred. WAITIN will be continually sampled on the rising edge of CLK if DTACK is rising edge triggered or on the falling edge of CLK if DTACK is falling edge triggered. Once WAITIN is negated, the DRC will assert DTACK after the programmed number of CLK edges and will not sample WAITIN again until the next access.

Programming bit R6 also determines when the column address is incremented in both burst modes. If R6 = 0 during programming, the column address is incremented when CAS is negated. If R6 = 1 during programming, the column address is incremented when DTACK is asserted.

Figure 21 shows a 68030 Burst Mode burst cycle. The DRC has been programmed to assert DTACK on the second falling CLK edge after CAS is asserted. DTACK was held negated for 1 extra CLK period due to WAITIN. Since R6 = 0, the column address is incremented when CAS is negated.

Figure 21. WAITIN, R6 = 0 Programmed

Figure 22 shows two 68040 Burst Mode burst cycles. The DRC has been programmed to assert DTACK on the first rising CLK edge after CAS is asserted. In the first cycle, WAITIN was sampled active on the clock edge that negated DTACK. DTACK is rising edge triggered, so WAITIN is continually sampled on rising CLK edges until it is negated. Since the DRC was programmed to assert DTACK one rising CLK edge after CAS was asserted, DTACK is asserted one rising CLK edge after WAITIN is

negated. Since WAITIN is negated during the second burst cycle, DTACK is asserted on the first rising CLK edge after CAS is asserted.

Since R6 = 1, the column address is incremented when DTACK is asserted.

Figures 23 through 25 show when WAITIN is sampled during deferred accesses, page hit writes, and burst writes, respectively.

Figure 22. WAITIN, R6 = 1 Programmed

Figure 23. WAITIN, R6 = 1

During Programming,

Deferred Access Start

Figure 24. WAITIN, R6 = 1

During Programming,

Delay CAS During

Page Hit Writes

Figure 25. WAITIN, R6 = 1

During Programming,

Delay CAS During

Burst Writes

#### REFRESH OPERATIONS

The DRC supports four refresh control mode options:

- 1) internal automatic refreshing

- 2) internal automatic burst refreshing

- 3) externally controlled/burst refreshing

- 4) refresh request/acknowledge burst refreshing

With each of the control modes above, RAS only refresh, or error scrubbing with RAS only refresh may be performed.

Three inputs, extend refresh (EXTDRF), refresh (RFSH) and disable refresh (DISRFSH), along with two outputs, refresh in progress (RFIP) and refresh request (RFRQ) are associated with refreshing.

DISRFSH and RFSH are used in the externally controlled/burst refresh mode and the refresh request/acknowledge mode. External circuitry asserts DISRFSH to inhibit internally requested refreshes and requests refreshes by asserting RFSH.

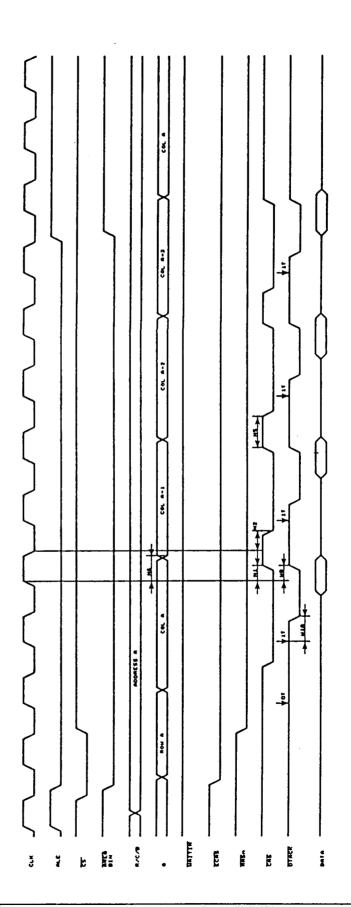

Figure 26. RAS Low and Precharge Time

RFRQ is used in the refresh request/acknowledge mode. The DRC asserts RFRQ to request a refresh cycle but will not perform the refresh until external circuitry acknowledges the request by asserting RFSH as long as DISRFSH is asserted.

RFIP is used in all refresh modes. The DRC asserts RFIP to indicate to external circuitry that a refresh is in progress.

EXTDRF is used when the DRC is programmed for error scrubbing. External circuitry asserts EXTDRF to extend the refresh cycle.

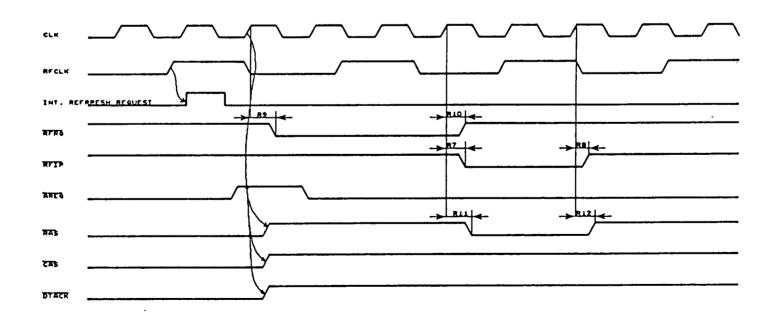

The internal refresh row counter will be incremented automatically, regardless of the refresh control mode used. The refresh address counter will be incremented once all of the refresh RASs have been negated. The refresh counter may be reset by asserting RFSH while DISRFSH is high.

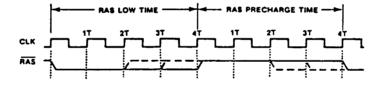

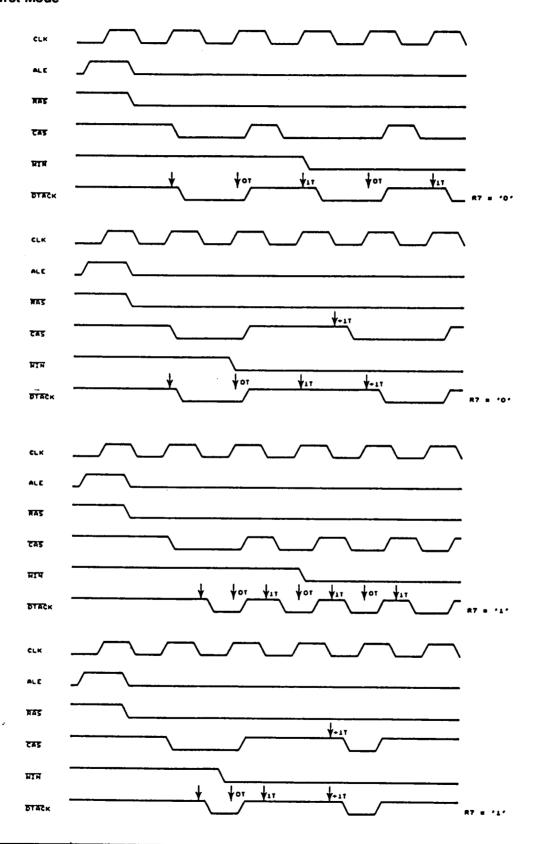

In every combination of refresh control mode and type, the DRC will assert the refresh RASs for a programmed number of CLK periods. CLK edges for RAS low time during refresh and RAS precharge time are counted as shown in Figure 26.

#### REFRESH CONTROL MODES

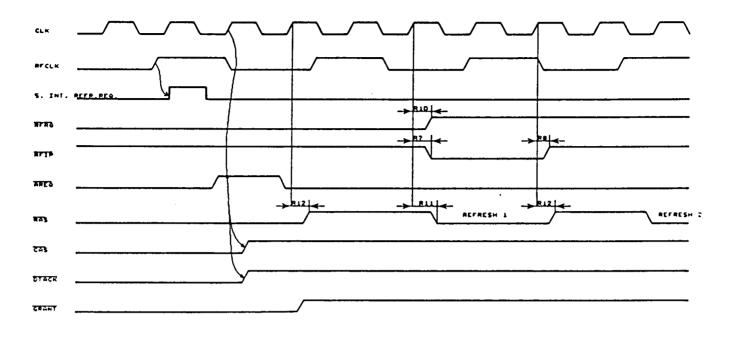

#### **Automatic Internal Refresh**

The DRC has an internal refresh clock to generate internal refresh requests. An internal refresh request is generated every period of the refresh clock. RFRQ is pulsed once every period of the refresh clock. The refresh clock period is programmed according to the value of address bits C0-C3. The internal refresh request will generate an automatic internal refresh as long as a DRAM access is not currently in progress and the RAS precharge time has been met. If a DRAM access is in progress when the refresh timer requests a refresh, the on-chip arbitration logic will allow the access to finish before the refresh is initiated. The next DRAM access is deferred until the refresh cycle is complete.

The refresh period for most DRAMs is 15  $\mu$ s. This means that a 1 Mbit DRAM has to be refreshed every 8 ms, during which time, 512 rows must be accessed. This requires a 9-bit row address refresh counter. The KS84EC30 has a 10-bit counter and the KS84C32, an 11-bit counter. The extra bits are used for error scrubbing over the entire address range.

Automatic internal refresh is possible in Single Access, Interleaved Access and both burst modes. When the DRC is operated in Page Mode or either burst mode with Page Mode, an enhanced version of automatic internal refreshing is available as shown in the next section.

DISRESH must be negated to enable automatic internal refreshes.

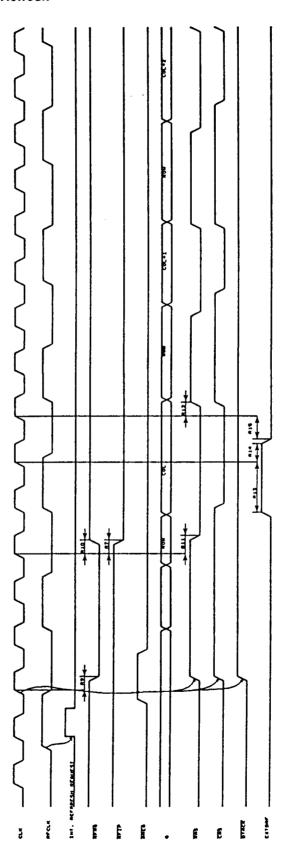

#### **Automatic Internal Burst Refreshing**

The  $\overline{RAS}$  pulse width,  $t_{RASP}$  and  $t_{RASC}$ , of most page and static column DRAMs is limited to 100  $\mu s$ . The DRC takes advantage of this characteristic by supporting automatic internal burst refreshing. When operating in automatic internal burst refresh control mode, the DRC will perform a 5-refresh burst after the 5th internal refresh request (approximately every 75  $\mu s$ ) instead of performing a refresh after every internal request, as in the automatic internal refresh control mode.

DISRFSH must be negated to enable automatic internal burst refreshes. However, if DISRFSH is asserted for any reason, all pending refreshes (up to 5) will be performed when DISRFSH is again negated. While DISRFSH is asserted, no internal refresh requests will accumulate.

#### **Externally Controlled/Burst Refresh**

When using externally controlled/burst refresh, internally generated refresh requests are ignored. Instead, external circuitry is used to pulse the refresh (RFSH) signal low to generate a refresh request. The refresh cycle will take place on the next positive edge of CLK. If a DRAM access is in progress or the RAS precharge time has not been satisfied, the refresh will be delayed. This means that the access RAS must be negated with DISPM if ECAS2 = 1 is programmed in order to precharge RAS before the refresh can take place. If RFSH is asserted when the refresh RAS is negated, RFIP will remain asserted and another refresh cycle will be performed after RAS has been precharged.

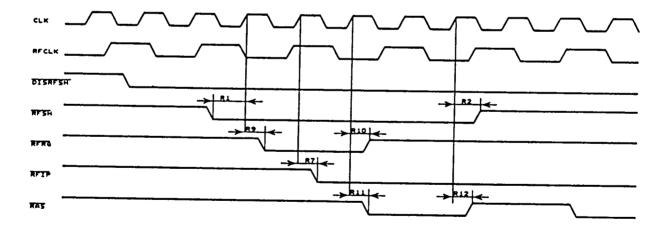

Figure 27 shows how DISRFSH and RFSH are used to control single and burst refreshes. The DRC is performing a RAS only refresh under external control and has been programmed to assert the refresh RAS for 2T and to precharge RAS for 2T.

Figure 27. Externally Controlled/Burst Refresh

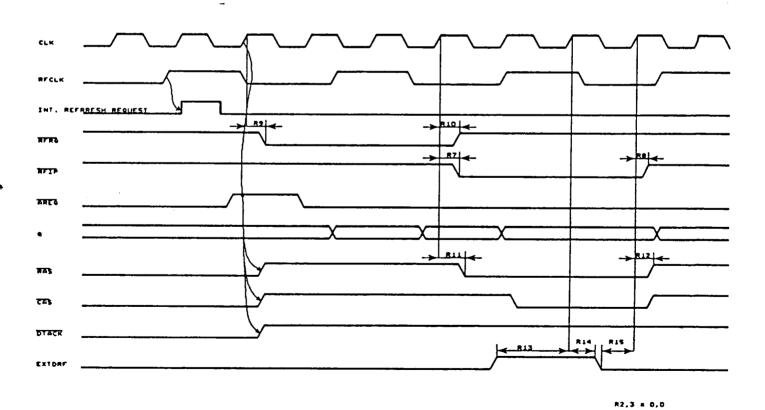

#### Refresh Request/Acknowledge Burst Refreshing

In this refresh control mode, internally generated refresh requests are ignored by the DRC. Instead, external circuitry monitors the the DRC's RFRQ output and generates a refresh request at the appropriate time by pulsing RFSH. The refresh is then performed as shown in Figure 28.

Figure 28. Refresh Request/Acknowledge Refresh

#### **REFRESH TYPES**

The DRC supports two types of refreshing:

- 1) RAS only

- 2) RAS only with Error Scrubbing

Each refreshing type may be controlled by any refresh control mode. The DRC asserts all RASs at the same time when performing RAS only refreshing as shown in Figure 27.

RAS and CAS are asserted during refresh when Error Scrubbing refresh is programmed as shown in Figure 48. The ECAS inputs do not enable or disable CAS during the refresh. The EDAC circuit should control the DRAMs' output enable lines to avoid bus contention if the DRAM has common I/O.

#### RESET

The KS84EC30 on-chip power-up reset logic generates a reset pulse:

- At power up

- If V<sub>CC</sub> falls well below 3V and reaches V<sub>CC</sub> min.

When the chip is reset, the Mode Register (with the exception of bit C6, which is set) and all internal counters are reset. All of the output signals are inactive; RAS0-3, CAS0-3, DTACK, RFIP, WE, RFRQ and GRANT are high while Q0-9 are low.

After power-up, the DRC is operable after 200 µs and the Mode Register can be programmed if the programmable version of the chip is being used.

The Mode Load signal ( $\overline{\text{ML}}$ ) can be used to reset the chip at any time after power-up. When  $\overline{\text{ML}}$  is driven low, all internal counters are reset and the Mode Register is enabled to receive the mode bit inputs.

The internal refresh interval counter may be reset at any time by asserting RFSH while DISRFSH is high.

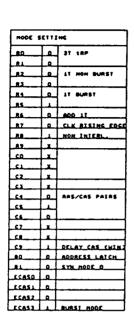

#### PROGRAMMING THE KS84EC30

The KS84EC30 has a Mode Register that is programmed by the user. The Mode Register controls the internal operating modes of the DRC.

The DRC is programmed via the system's address bus, not the data bus. The Mode Register receives inputs from the CPU on address lines R0-9 and C0-9, the bank select lines B0 and B1, and the  $\overline{CAS}$  enable lines  $\overline{ECAS0-3}$ . The Mode Register is enabled by the falling edge of  $\overline{ML}$ . The inputs are then strobed in on the rising edge of  $\overline{ML}$  as show in Figure 29.

Alternatively, the Mode Register may be programmed by initiating a "fake" access as shown in Figure 30. When programmed in this fashion, ML and CS are asserted, followed by AREQ. The programming inputs are strobed into the Moad Load Register on the falling edge of AREQ. DTACK is asserted on the falling edge of AREQ to terminate the bus access and is negated by the rising edge of ML or AREQ (whichever occurs first).

Figure 29. Mode Load Only Programming

Figure 30. Fake Access Programming

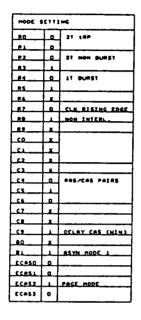

#### Table 3. Programming the Mode Register

#### **OPERATING MODES**

ECASI-3

These bits program the DRCs operating mode. The user has the choice of Single Access Mode, Interleaved Access Mode, Page Access Mode, 68040 Burst Access Mode with or without Page Mode or 68030 Burst Access Mode with or without Page Mode. Interleaved Access Mode is selected by the RAS and CAS configuration bits C4, C5, and C6.

| ECAS1 | ECAS2 | ECAS3 | Operating Mode                         |  |

|-------|-------|-------|----------------------------------------|--|

| 0     | 0     | 0     | Single Access Mode                     |  |

| 0     | 1     | 0     | Page Access Mode                       |  |

| 0     | 0     | 1     | 68040 Burst Access Mode                |  |

| 0     | 1     | 1     | 68040 Burst Access Mode with Page Mode |  |

| 1     | 0     | 0     | 68030 Burst Access Mode                |  |

| 1     | 1     | 0     | 68030 Burst Access Mode with Page Mode |  |

#### ADDRESS LATCH/AUTOMATIC COLUMN INCREMENT WHILE BURSTING

Bo

B0 allows the user to specify whether the on-chip latches should latch the address inputs on the falling edge of ADS(ALE) or whether they should remain transparent. If ECAS2 = 1 during programming the row address is always latched by the on-chip page detect logic regardless of how B0 is programmed.

The user also specifies whether the DRC automatically increments the column address while bursting or if external circuitry is required to change the column address. If B0 = 0 during programming, then the column address is automatically incremented while bursting. If B0 = 1, the address latches will remain transparent, disabling the automatic column increment.

| Bo | •                           | Automatic Column Increment |

|----|-----------------------------|----------------------------|

| 0  | Address Bits Latched        | Enabled                    |

| 1  | Address Latches Transparent | Disabled                   |

#### **ACCESS START AND TERMINATION MODES**

**B**1

B1 allows the user to specify either synchronous or asynchronous access start and termination modes.

A synchronous (Mode 0) access is controlled by the system clock. The access is initiated on the first rising CLK edge after ALE goes high.  $\overline{AREQ}$  is sampled on rising CLK edges and terminates the access when it is negated.

An asynchronous (Mode1) access is initiated immediately by the falling edge of  $\overline{ADS}$  and is immediately terminated by the rising edge of  $\overline{AREQ}$ .

| B1 |        |

|----|--------|

| 0  | Mode 0 |

| 1  | Mode 1 |

#### Table 3. Programming the Mode Register (Continued)

### RAS LOW AND RAS PRECHARGE TIME

R0, R1

These bits control the time that RAS is low during refresh operations and also determine the RAS precharge time. The time interval shown (T) is equivalent to one rising CLK edge. The user should take into account RAS rise and fall time when programming these bits.

| RO | R1 | RAS Low Time | RAS Precharge Time |

|----|----|--------------|--------------------|

| 0  | 0  | 2T           | 2T                 |

| 0  | 1  | 2T           | 3T                 |

| 1  | 0  | 3T           | 3T                 |

| 1  | 1  | 4T           | 4T                 |

#### DTACK GENERATION FOR ACCESSES THAT INITIALLY ASSERT RAS

R2, R3

These bits control DTACK generation for any access during which RAS is initiated. R2 and R3 determine the number of CLK edges that DTACK remains negated under the following conditions:

- All accesses when the DRC is programmed for Single or Interleaved Access Modes

- · During page misses and deferred accesses when the DRC is programmed for Page Mode

- During the opening cycle of a burst access when the DRC is programmed for 68040 Burst or 68030 Burst Access Modes or if a page miss occurs during the opening access when they are combined with Page Mode.

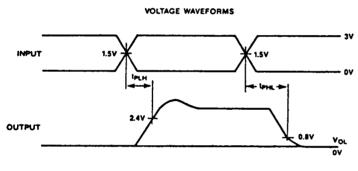

The time interval shown (T) refers to one rising or falling CLK edge. Bit R7 determines whether DTACK is asserted on rising or falling CLK edges.

| R2 | R3 | DTACK Low From Access Start |

|----|----|-----------------------------|

| 0  | 0  | 1T                          |

| 0  | 1  | 2Т                          |

| 1  | 0  | 3Т                          |

| 1  | 1  | 4T                          |

#### DTACK GENERATION FOR PAGE HITS AND BURST ACCESSES

R4, R5

These bits control DTACK generation for any access during which only CAS is initiated. R4 and R5 determine the number of CLK edges that DTACK remains negated under the following conditions:

- During page hits when the DRC is programmed for Page Mode

- During the opening cycle of a burst access that results in a page hit when the DRC is programmed for 68040

Burst or 68030 Burst Access Modes and Page Mode is used.

- While Bursting

The time interval shown (T) refers to one rising or falling CLK edge. Bit R7 determines whether DTACK is asserted on rising or falling CLK edges.

| R4 | R5 | DTACK Low From Access Start |

|----|----|-----------------------------|

| 0  | 0  | от                          |

| 0  | 1  | 1T                          |

| 1  | 0  | 2T                          |

| 1  | 1  | эт                          |

Table 3. Programming the Mode Register (Continued).

#### PROGRAMMING WAITIN FOR WAIT STATE INSERTION AND COLUMN INCREMENT R6 controls the functionality of WAITIN in all operating modes. It also determines when the column address will R6 be incremented when the DRC is operated in 68040 Burst and 68030 Burst Modes. Column Address Increment R6 **WAITIN** Functionality Increment when CAS is negated Add 1 wait state if active. 0 Increment when DTACK is asserted 1 Continually add wait states. PROGRAMMING DTACK FOR RISING OR FALLING CLK EDGES This bit controls whether DTACK is asserted (and WAITIN is sampled) on rising or falling CLK edges. R7 R7 DTACK 0 Rising Edge Triggered Falling Edge Triggered 1 INTERLEAVING R8 determines whether the Q outputs are driven in interleaved or non-interleaved mode. R8 In interleaved mode, the row addresses are multiplexed to the DRAM controller address outputs, after the column addresses have been held for a sufficient time (25ns minimum) after CAS has gone low. in non-interleaved mode, the column addresses are held on the DRAM controller address outputs until CAS goes R8 0 Interleaved mode Non-interleaved mode **RESERVED BIT** This bit should be programmed = 0. If programmed = 1, Error Scrubbing is not supported. R9 RFCLK DIVISOR These bits allow the user to select the divisor for the refresh clock (RFCLK) input, from which the internal refresh C0, C1, C2 clock is generated. Select the divisor such that the internal refresh clock frequency is approximately 2 MHz. CO C2 Divisor C<sub>1</sub> 0 0 0 10 ٥ 0 1 6 ٥ 1 0 8 4 ٥ 1 1 0 0 9 1 1 0 1 5 1 1 0 7 3 1 1 1

### Table 3. Programming the Mode Register (Continued)

#### INTERNAL REFRESH CLOCK DIVISOR

СЗ

C3 allows the user to divide the internal refresh clock to achieve the desired interval between internally generated refresh requests.

| ඍ | Divisor | Refresh interval if internal Refresh Clock Frequency is 2 MHz |

|---|---------|---------------------------------------------------------------|

| 0 | 30      | 15 μs                                                         |

| 1 | 26      | 13 µs                                                         |

#### RAS AND CAS CONFIGURATIONS

C4, C5, C6

These bits control the RAS and CAS configurations. There are 4 RAS and 4 CAS outputs. They can always be grouped such that each RAS and CAS will drive one fourth of the memory array, regardless of whether the array is arranged in 1, 2 or 4 banks. The setting of these bits also determines whether error scrubbing and Interleaved Access Mode are selected.

| C4 | C5  | C6                                   | RAS and Configuration Modes                                                                                                                                            |    |            |                     | Error<br>Scrubbing | Interleaved<br>Access Mode |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|----|-----|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|---------------------|--------------------|----------------------------|--|--|--|--|--|--|--|--------------------------------|---|---|---------------------|--|--|

| 0  | 0   | 0                                    | RASO-3 are brought low during an access. CASO-3 are all selected during an access but only those enabled by the corresponding ECAS can go low. B0 and B1 are not used. |    |            |                     | Yes                | No                         |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

| 0  |     |                                      | RAS pairs are selected by B1. B1 B0                                                                                                                                    |    |            |                     | No                 | No                         |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      | CASO-3 are all selected during an access but only those enabled                                                                                                        | 0  | X          | RASO, 1             |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      | by the corresponding ECAS can go low.                                                                                                                                  | 1  | X          | RAS2, 3             |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

| 0  | 1   | 0                                    | RAS, CAS pairs are selected by                                                                                                                                         |    | ВО         |                     | Yes                | Yes                        |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      | B0 and B1. A selected CAS will go low only if enabled by its                                                                                                           | 0  | 0          | RASO, CASO          |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      | corresponding ECAS.                                                                                                                                                    | ٥  | 1          | RAS1, CAS1          |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      | 1                                                                                                                                                                      | 0  | RAS2, CAS2 |                     |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      | 1                                                                                                                                                                      | 1  | RAS3, CAS3 |                     |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

| 0  | . 1 | 1                                    | RAS is selected by B0 and B1. CASO-3 are all selected during                                                                                                           | B1 | Bo         |                     | No                 | No                         |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     | an access but only those enabled     | 0                                                                                                                                                                      | 0  | PASO       |                     |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     | by the corresonding ECAS can go low. | 0                                                                                                                                                                      | 1  | RAST       |                     |                    |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     | WW.                                  | 1                                                                                                                                                                      | 0  | PAS2       |                     | 1                  |                            |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

|    |     |                                      |                                                                                                                                                                        | 1  | 1          | RAS3                |                    | :                          |  |  |  |  |  |  |  |                                |   |   |                     |  |  |

| 1  | 0   | 0                                    | RAS, CAS pairs are selected by<br>B1. A selected CAS will go low                                                                                                       | B1 | BO         |                     | Yes                | Yes                        |  |  |  |  |  |  |  |                                |   |   |                     |  |  |