# Bt68561A

# Distinguishing **Multiprotocol Features**

- Full Duplex Synchronous/ Asynchronous Receiver and Transmitter

- Implements IBM Binary **Synchronous Communications** (BSC) in Two Coding Formats: **ASCII and EBCDIC**

- Supports Other Synchronous **Character-Oriented Protocols** (COP), such as 6-Bit BSC, X3.28k, ISO IS1745, and ECMA-16

- Asynchronous and Isochronous Modes

- Modem Handshake Interface

- High-Speed Serial Data Rate (DC to 4 MHz)

- · Internal Oscillator and Baud Rate Generator (BRG) with Programmable Data Rate

- Crystal- or TTL-Level Clock Input and Buffered Clock Output (8 MHz)

- Direct Interface to 68008/68000 Asynchronous Bus

- Eight-Character Receiver and Transmitter Buffer Registers

- Maskable Interrupt Conditions For Receiver, Transmitter, and Serial Interface

- 22 Directly Addressable Registers for Flexible Option Selection, Complete Status Reporting, and Data Transfer

- Three Separate Programmable Interrupt Vector Numbers for Receiver, Transmitter, and Serial Interface

- Programmable Microprocessor Bus Data Transfer; Polled, Interrupt, and Two-Channel **DMA Transfer Compatible with** MC68440/MC68450

- Clock Control Register for Receiver Clock Divisor and Receiver and Transmitter Clock Routing

- Selectable Full/Half-Duplex, Autoecho and Local Loop-Back Modes

- Selectable Parity (Enable, Odd, and Even) and CRC (Control Field Enable, CRC-16, CCITT V.41, and VRC/LRC)

# **Applications**

· Support of Synchronous Bit Oriented Protocols (BOP), such as SDLC, HDLC, and X.25.

# **Communications Controllers** (MPCCs)

# **Product Description**

The Bt68560A, Bt68561A Multi-Protocol Communications Controller interfaces a single serial communications channel to a 68008/68000 microcomputerbased system using either asynchronous or synchronous protocol. High-speed bit rate, formatting, low-overhead automatic programming, 8-character buffering, twochannel DMA interface, and three separate interrupt vector numbers optimize MPCC performance to take full advantage of the 68008/68000 processing capabilities and asynchronous bus structure.

In synchronous operation, the MPCC supports Bit-Oriented Protocols (BOP), such as SDLC/HDLC; and Character-Oriented Protocols (COP), such as IBM Bisync (BSC), in either ASCII or EBCDIC coding. Formatting, synchronizing, validation, and error detection are performed automatically in accordance with protocol requirements and selected options. Asynchronous (ASYNC) and Isochronous (ISOC) modes are also supported. In addition, modem interface handshake signals are available for general use.

# **Product Description** (continued)

Control, status, and data are transferred between the MPCC and the microcomputer bus via 22 directly addressable registers and a DMA interface. Two First-In First-Out (FIFO) registers, addressable through separate receiver and transmitter data registers, each buffer up to eight characters at a time to allow more MPU processing time to service data received or to be transmitted and to maximize bus throughput, especially during DMA operation. The two-channel Direct Memory Access (DMA) interface operates with the MC68440/MC68450 DMA controllers. Three prioritized interrupt vector numbers separately support receiver, transmitter, and modem interface operation.

An on-chip oscillator drives the internal Baud Rate Generator (BRG) and an external clock output with an 8 MHz input crystal or clock frequency. The BRG, in conjunction with two selectable prescalers and a 16-bit programmable divisor, provides a data bit rate of DC to 4 MHz.

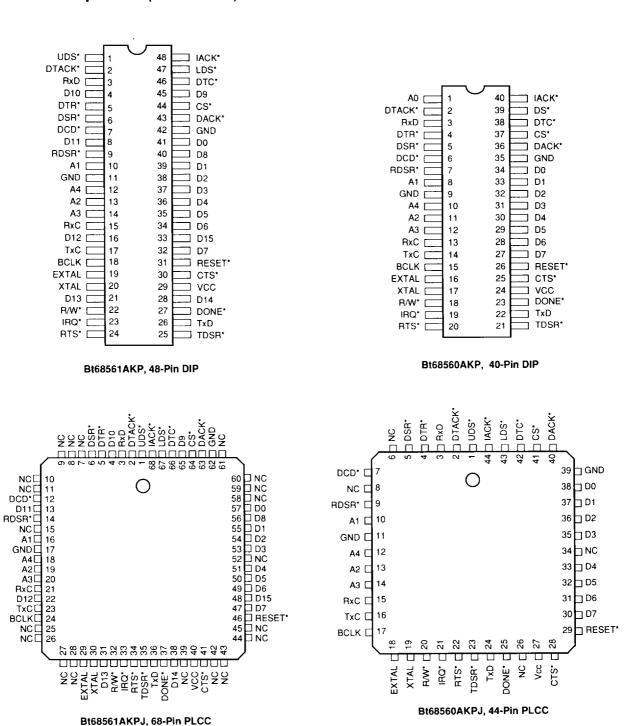

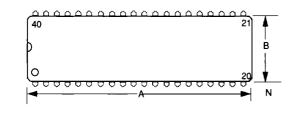

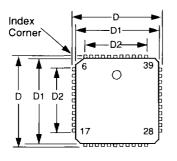

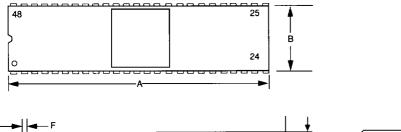

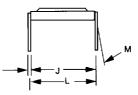

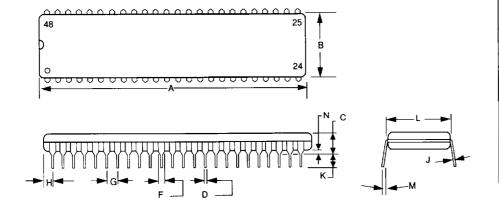

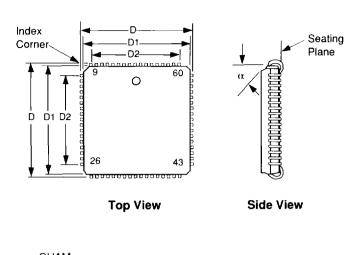

The 48-pin Bt68561A supports word-length operation when connected to the 68000 16-bit asynchronous bus, as well as byte-length (8-bit) operation when connected to the 68008 8-bit bus. The 40-pin Bt68560A supports byte-length operation on the 68008 bus (see Figure 1).

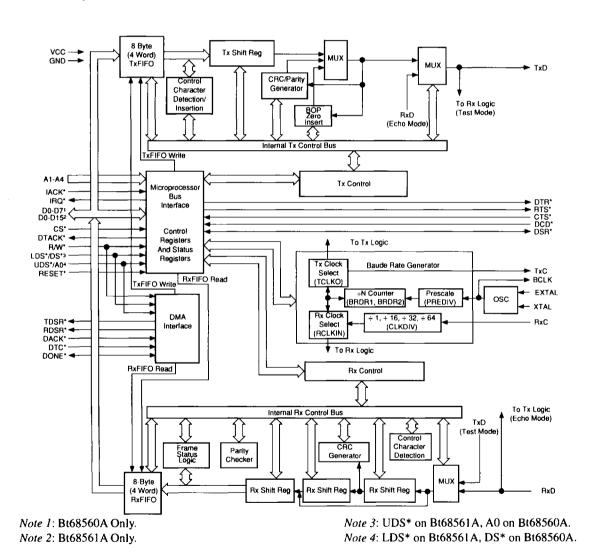

Figure 1. MPCC Functional Block Diagram.

# **Pin Descriptions**

Throughout this document, signals are presented with the terms active and inactive or asserted and negated regardless of whether the signal is active in the high-voltage state or low-voltage state. (The active state of each logic pin is described below.) Active low signals are denoted by an asterisk. For example, R/W\* indicates write is active low and read is active high.

*Note:* The Bt68561A interface is described for word-mode operation only, and the Bt68560A interface is described for byte-mode operation only.

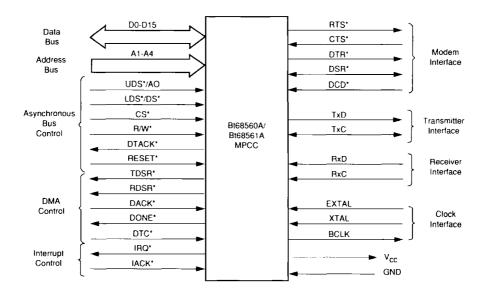

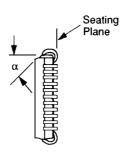

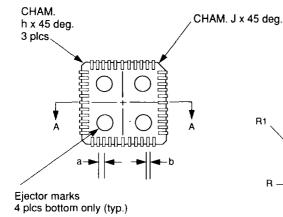

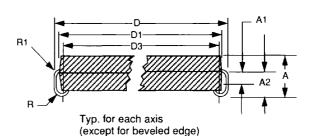

The MPCC input and output signals, and the pin configuration are shown in Figures 2 and 3.

**A1-A4—Address Lines.** A1 through A4 are active high inputs used in conjunction with the CS\* input to access the internal registers. The address map for these registers is shown in Table 1

**D0-D15—Data Lines.** The bidirectional data lines transfer data between the MPCC and the MPU, memory, or other peripheral device. D0 through D15 are used when connected to the 16-bit 68000 bus and operating in the MPCC word mode. D0 through D7 are used when connected to the 16-bit 68000 bus or the 8-bit 68008 bus and operating in the MPCC-byte mode. The data bus is three-stated when CS\* is inactive. (See exceptions in DMA mode.)

**CS\*—Chip Select.** CS\* low selects the MPCC for programmed transfers with the host. The MPCC is deselected when the CS\* input is inactive in non-DMA mode. CS\* must be decoded from the address bus and gated with address strobe (AS\*).

**R/W\*—Read/Write.** R/W\* controls the direction of data flow through the bidirectional data bus by indicating that the current bus cycle is a read (high) or write (low) cycle.

DTACK\*—Data Transfer Acknowledge. DTACK\* is an active low output that signals the completion of the bus cycle. During read or interrupt-acknowledge cycles, DTACK\* is asserted by the MPCC after data have been provided on the data bus; during write cycles it is asserted after data have been accepted at the data bus. DTACK\* is driven high after assertion prior to being three-stated. A holding resistor is required to maintain DTACK\* high between bus cycles.

**DS\*—Data Strobe (Bt68560A).** During a write (R/W\* low), the DS\* positive transition latches data on data bus lines D0 through D7 into the MPCC. During a read (R/W\* high), DS\* low enables data from the MPCC to data bus lines D0 through D7.

LDS\*—Lower Data Strobe (Bt68561A). During a write (R/W\* low), the positive transition latches data on the data bus lines D0 through D7 (and on D8 through D15 if UDS\* is low) into the MPCC. During a read (R/W\* high), LDS\* low enables data from the MPCC to D0 through D7 (and to D8 through D15 if UDS\* is low).

**A0—Address Line A0 (Bt68560A).** When interfacing to an 8-bit data bus system such as the 68008, address line A0 is used to access an internal register. A0 = 0 defines an even register, and A0 = 1 defines an odd register (see Table 2).

*UDS\**—*Upper Data Strobe (Bt68561A).* When interfacing to a 16-bit data bus system such as the 68000, a low on control bus signal UDS\* enables access to the upper data byte on D8–D15. A high on UDS\* disables access to D8–D15. Data are latched and enabled in conjunction with LDS\*.

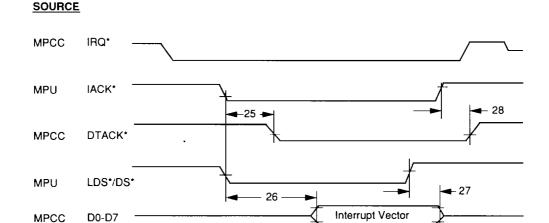

**IRQ\*—Interrupt Request.** The active low IRQ\* output requests interrupt service by the MPU. IRQ\* is driven high after assertion prior to being three-stated.

**IACK\*—Interrupt Acknowledge.** The active low IACK\* input indicates that the current bus cycle is an interrupt acknowledge cycle. When IACK\* is asserted the MPCC places an interrupt vector on the lower byte (D0 through D7) of the data bus.

**TDSR\*—Transmitter Data Service Request.**When Transmitter DMA mode is active, the low TDSR\* output requests DMA service.

**RDSR\*—Receiver Data Service Request.**When receiver DMA mode is active, the low RDSR\* output requests DMA service.

**DACK\*—DMA Acknowledge.** The DACK\* low input indicates that the data bus has been acquired by the DMAC and that the requested bus cycle is beginning.

DTC\*—Data Transfer Complete. On a 68000 bus, the DTC\* low input indicates that a DMA data transfer was completed with no bus conflicts. DTC\* in response to an RDSR\* indicates that the data have been successfully stored in memory. DTC\* in response to a TDSR\* indicates that the data are present on the data bus for strobing into the MPCC. If not used, this input should be connected to ground.

**DONE\*—Done.** DONE\* is a bidirectional active low signal. The DONE\* signal is asserted by the DMAC when the DMA transfer count is exhausted and there are no more data to be transferred, or asserted by the MPCC when the status byte following the last character of a frame (block) is being transferred in response to an

# Pin Descriptions (continued)

Figure 2. Input/Output Signals.

RDSR\*. The DONE\* signal asserted by the DMAC in response to a TDSR\* will be stored to track with the data byte (lower byte for word transfer) through the TxFIFO.

**RESET\***—**Reset.** RESET\* is an active low, high-impedance input that initializes all MPCC functions. RESET\* must be asserted for at least 500 ns to initialize the MPCC.

**DTR\***—**Data Terminal Ready.** The DTR\* active low output is general purpose in nature and is controlled by the DTRLVL bit in the Serial Interface Control Register (SICR).

**RTS\*—Request to Send.** The RTS\* active low output is general purpose in nature and is controlled by the RTSLVL bit in the SICR.

CTS\*—Clear to Send. The CTS\* active low input positive transition and level are reported in the CTST and CTSLVL bits in the Serial Interface Status Register (SISR), respectively.

**DSR\***—**Data Set Ready.** The DSR\* active low input negative transition and level are reported in the DSRT and DSRLVL bits in the SISR, respectively. DSR\* is also an output for RSYN.

**DCD\***—**Data Carrier Detect.** The DCD\* active low input positive transition and level are reported in the DCDT and DCDLVL bits in the SISR, respectively.

**TxD—Transmitted Data.** The MPCC transmits

serial data on the TxD output. The TxD output changes on the negative going edge of TxC.

**RxD—Received Data.** The MPCC receives serial data on the RxD input. The RxD input is shifted into the receiver with the negative-going edge of RxC.

**TxC—Transmitter Clock.** TxC can be programmed to be an input or an output. When TxC is selected to be an input, the transmitter clock must be provided externally. When TxC is programmed to be an output, a clock is generated by the MPCC's internal band rate generator.

**RxC—Receiver Clock.** RxC provides the MPCC receiver with received data timing information.

#### EXTAL - Crystal/External Clock Input,

XTAL—Crystal Return. EXTAL and XTAL connect a 20 kHz to 8.064 MHz parallel resonant external crystal to the MPCC internal oscillator (see Clock Oscillator in the Circuit Description Section). The pin EXTAL may also be used as a TTL level input to supply DC to 8 MHz reference timing from an external clock source. XTAL must be tied to ground when applying an external clock to the EXTAL input.

**BCLK—Buffered Clock.** BCLK is the internal oscillator buffered output available to other MPCC devices, eliminating the need for additional crystals.

**VCC—Power.**  $5 \lor \pm 5\%$ .

**GND—Ground.** Ground  $(V_{SS})$ .

# Pin Descriptions (continued)

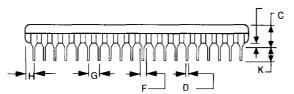

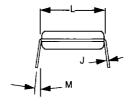

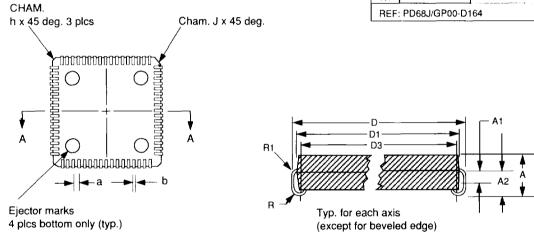

Figure 3. Pin Configurations.

# **MPCC** Registers

Twenty-two registers control and monitor the MPCC operation. The registers and their addresses are identified in Tables 1 and 2. When the Bt68561A is operated in the word mode, two registers are read or written at a time starting at an even boundary. When the Bt68560A is operated in the byte mode, each register is explicitly addressed based on A0.

Table 3 summarizes the MPCC register bit assignments and their accesses. A read from an unassigned location results in a read from a null register. A null register returns all ones for data and results in a normal bus cycle. Unused bits of a defined register are read as zeros unless otherwise noted.

| Regis                                            | ster(s)                                              |     |                | Ad        | dres | s Lir | ıes |

|--------------------------------------------------|------------------------------------------------------|-----|----------------|-----------|------|-------|-----|

| 15 — (Odd Registers) — 8                         | 7 — (Even Registers) — 0                             | R/W | Addr<br>(Hex.) | <b>A4</b> | А3   | A2    | A1  |

| Receiver Control Register (RCR)                  | Receiver Status Register (RSR)                       | R/W | 00             | 0         | 0    | 0     | 0   |

| Receiver Data Register (RDR)—16 bits (Note 1)    |                                                      | R   | 02             | 0         | 0    | 0     | 1   |

| Receiver Interrupt Enable Register (RIER)        | Receiver Interrupt Vector Number Register (RIVNR)    | R/W | ()4            | 0         | 0    | 1     | 0   |

|                                                  |                                                      |     |                |           |      |       |     |

| Transmitter Control Register (TCR)               | Transmitter Status Register (TSR)                    | R/W | 08             | 0         | 1    | 0     | 0   |

| Transmitter Data Register (TDR)—16 bits (Note 2) |                                                      | W   | 0 <b>A</b>     | 0         | 1    | 0     | 1   |

| Transmitter Interrupt Enable Register (TIER)     | Transmitter Interrupt Vector Number Register (TIVNR) | R/W | 0C             | 0         | 1    | 1     | 0   |

| Serial Interface Control Register (SICR)         | Serial Interface Status Register (SISR)              | R/W | 10             | 1         | 0    | 0     | 0   |

| Reserved (Note 3)                                | Reserved (Note 3)                                    | R/W | 12             | 1         | 0    | 0     | 1   |

| Serial Interrupt Enable Register (SIER)          | Serial Interrupt Vector Number Register (SIVNR)      | R/W | 14             | 1         | 0    | 1     | 0   |

|                                                  |                                                      |     |                |           |      |       |     |

| Protocol Select Register 2 (PSR2)                | Protocol Select Register (PSR1)                      | R/W | 18             | 1         | 1    | 0     | 0   |

| Address Register 2 (AR2)                         | Address Register 1 (AR1)                             | R/W | 1 <b>A</b>     | 1         | 1    | 0     | 1   |

| Baud Rate Divider Register 2 (BRDR2)             | Baud Rate Divider Register 1 (BRDR1)                 | R/W | 1C             | 1         | 1    | 1     | 0   |

| Error Control Register (ECR)                     | Clock Control Register (CCR)                         | R/W | 1E             | 1         | 1    | 1     | 1   |

- Note 1: Accessible register of the 4-word RxFIFO. The data are not initialized, however RES\* resets the RxFIFO pointer to the start of the first word.

- Note 2: Accessible register of the 4-word TxFIFO. The data are not initialized, however RES\* resets the TxFIFO pointer to the start of the first word.

- Note 3: Reserved Registers may contain random bit values.

Table 1. Bt68561A Accessible Registers (Word Mode).

# MPCC Registers (continued)

| Register(s)                                          |             |     |                | 1  | Addr | ess | Line      | s  |

|------------------------------------------------------|-------------|-----|----------------|----|------|-----|-----------|----|

| 7                                                    | 0           | R/W | Addr<br>(Hex.) | Α4 | А3   | A2  | <b>A1</b> | AO |

| Receiver Status Register (RSR)                       |             | R/W | 00             | 0  | 0    | 0   | 0         | 0  |

| Receiver Control Register (RCR)                      |             | R/W | 01             | 0  | 0    | 0   | 0         | 1  |

| Receiver Data Register (RDR) —8 bits (Note 1)        |             | R   | 02             | 0  | ()   | 0   | 1         | 0  |

| Reserved (Note 2)                                    | <del></del> |     | 03             | 0  | 0    | ()  | 1         | 1  |

| Receiver Interrupt Vector Number Register (RIVNR)    |             | R/W | 04             | 0  | 0    | 1   | 0         | 0  |

| Receiver Interrupt Enable Register (RIER)            | 147         | R/W | 05             | 0  | 0    | 1   | 0         | 1  |

| Transmitter Status Register (TSR)                    |             | R/W | 08             | 0  | 1    | 0   | 0         | 0  |

| Transmitter Control Register (TCR)                   |             | R/W | 09             | 0  | 1    | 0   | 0         | 1  |

| Transmitter Data Register (TDR) (Note 3)—8 bits      |             | w   | 0A             | 0  | 1    | 0   | 1         | 0  |

| Reserved (Note 2)                                    |             |     | OB             | 0  | 1    | 0   | 1         | 1  |

| Transmitter Interrupt Vector Number Register (TIVNR) |             | R/W | 0C             | 0  | 1    | 1   | 0         | 0  |

| Transmitter Interrupt Enable Register (TIER)         |             | R/W | 0D             | 0  | 1    | 1   | 0         | 1  |

| Scrial Interface Status Register (SISR)              |             | R/W | 10             | 1  | 0    | 0   | 0         | 0  |

| Serial Interface Control Register (SICR)             |             | R/W | 11             | 1  | 0    | 0   | 0         | 1  |

| Reserved (Note 2)                                    |             |     | 12             | 1  | 0    | 0   | ı         | 0  |

| Reserved (Note 2)                                    |             |     | 13             | 1  | 0    | 0   | 1         | l  |

| Serial Interrupt Vector Number Register (SIVNR)      |             | R/W | 14             | 1  | 0    | 1   | 0         | 0  |

| Serial Interrupt Enable Register (SIER)              |             | R/W | 15             | 1  | 0    | 1   | 0         | 1  |

| Protocol Select Register 1 (PSR1)                    |             | R/W | 18             | 1  | 1    | 0   | 0         | 0  |

| Protocol Select Register 2 (PSR2)                    |             | R/W | 19             | 1  | 1    | 0   | 0         | 1  |

| Address Register I (ARI)                             |             | R/W | 1A             | 1  | l    | 0   | 1         | 0  |

| Address Register 2 (AR2)                             |             | R/W | 1B             | 1  | l    | 0   | 1         | 1  |

| Baud Rate Divider Register I (BRDRI)                 |             | R/W | 1C             | 1  | 1    | 1   | 0         | 0  |

| Baud Rate Divider Register 2 (BRDR2)                 |             | R/W | 1D             | 1  | 1    | 1   | 0         | 1  |

| Clock Control Register (CCR)                         |             | R/W | 1E             | 1  | 1    | 1   | 1         | 0  |

| Error Control Register (ECR)                         |             | R/W | 1F             | 1  | 1    | 1   | 1         | 1  |

- Note 1: Accessible register of the 8-byte RxFIFO. The data are not initialized, however RES\* resets the RxFIFO pointer to the start of the first byte.

- Note 2: Reserved registers may contain random bit values.

- Note 3: Accessible register of the 8-byte TxFIFO. The data are not initialized, however RES\* resets the TxFIFO pointer to the start of the first byte.

Table 2. Bt68560A Accessible Registers (Byte Mode)

# **MPCC Registers** (continued)

| R/W    |            |           |                         | Bit No                      | umber       |                   |             |            | Reset                                   |                                                         |

|--------|------------|-----------|-------------------------|-----------------------------|-------------|-------------------|-------------|------------|-----------------------------------------|---------------------------------------------------------|

| Access | 7          | 6         | 5                       | 4                           | 3           | 2                 | 1           | 0          | (Note 1)<br>Value                       |                                                         |

| R/W    | RDA        | EOF       | 0                       | C/PERR                      | FRERR       | ROVRN             | RA/B        | RIDLE      | 00                                      | Receiver Status Register (RSR)                          |

| R/W    | 0          | RDSREN    | DONEEN                  | RSYNEN                      | STRSYN      | 0                 | RABTEN      | RRES       | 01                                      | Receiver Control Register (RCR)                         |

| R      | ·          | _         | RECEI                   | VER DATA                    | (RxFIFO) (  | (Note 2)          |             |            |                                         | Receiver Data Register (RDR)                            |

| R/W    |            | REC       | EIVER IN                | TERRUPT V                   | ECTOR N     | UMBER (R          | IVN)        |            | 0F                                      | Receiver Interrupt Vector Number<br>Register (RIVNR)    |

| R/W    | RDA<br>IE  | EOF<br>IE | 0                       | C/PERR<br>IE                | FRERR<br>IE | ROVRN<br>IE       | RA/B<br>IE  | 0          | 00                                      | Receiver Interrupt Enable Register (RIER)               |

|        |            |           |                         |                             |             |                   |             |            |                                         |                                                         |

| R/W    | TDRA       | TFC       | 0                       | 0                           | 0           | TUNRN             | TFERR       | 0          | 80                                      | Transmitter Status Register (TSR)                       |

| R/W    | TEN        | TDSREN    | TICS                    | THW                         | TLAST       | TSYN              | TABT        | TRES       | 01                                      | Transmitter Control Register (TCR)                      |

| W      |            |           | TRANSM                  | HTTER DA                    | TA (TxFIFC  | )) (Note 2)       |             |            |                                         | Transmitter Data Register (TDR)                         |

| R/W    |            | TRAN      | SMITTER I               | NTERRUP                     | T VECTOR    | NUMBER            | (TIVN)      |            | 0F                                      | Transmitter Interrupt Vector<br>Number Register (TIVNR) |

| R/W    | TDRA<br>IE | TFC<br>IE | 0                       | 0                           | 0           | TUNRN<br>IE       | TFERR<br>IE | 0          | 00                                      | Transmitter Interrupt Enable<br>Register (TIER)         |

| R/W    | CTST       | DSRT      | DCDT                    | CTSLVL                      | DSRLVL      | DCDLVL            | 0           | 0          | 00                                      | Serial Interface Status Register (SISR)                 |

| R/W    | RTSLVL     | DTRLVL    | 0                       | 0                           | 0           | ЕСНО              | TEST        | 0          | 00                                      | Serial Interface Control Register (SICR)                |

|        |            |           | F                       | RANDOM F                    | BIT VALUE   | S                 |             |            |                                         | (reserved)                                              |

|        |            |           | F                       | RANDOM E                    | BIT VALUE   | S                 |             |            |                                         | (reserved)                                              |

| R/W    |            | SE        | RIAL INTE               | ERRUPT VECTOR NUMBER (SIVN) |             |                   |             |            | 0F                                      | Serial Interrupt Vector Number<br>Register (SIVNR)      |

| R/W    | CTS<br>IE  | DSR<br>IE | DCD<br>IE               | 0                           | 0           | 0                 | 0           | 0          | 00                                      | Scrial Interrupt Enable Register (SIER)                 |

| R/W    | 0          | 0         | 0                       | 0                           | IPARS       | ADRO              | CTLEX       | ADDEX      | 00                                      | Protocol Select Register 1 (PSR1)                       |

| R/W    | WD/        | STOP B    | IT SEL                  | CHAR L                      | EN SEL      | PRO               | TOCOL SE    | EL         | 00                                      | D. A. LO. L. D. L. CARODAN                              |

| IX/ VV | BYT        | SB2       | SBI                     | CL2                         | CL1         | PS3               | PS2         | PS1        | 00                                      | Protocol Select Register 2 (PSR?)                       |

| R/W    |            | В         | OP ADDRE                | ESS/BSC &                   | COP PAD/I   | PARS SYN          | 1           |            | 00                                      | Address Register 1 (AR1)                                |

| R/W    |            | В         | OP ADDRE                | ESS/BSC &                   | COP SYN/I   | PARS SYN          | 2           |            | 00                                      | Address Register 2 (AR2)                                |

| R/W    | BAU        |           | UD RATE I               | DIVIDER (L                  | SH)         |                   |             | 01         | Baud Rate Divider Register 1<br>(BRDR1) |                                                         |

| R/W    | ВА         |           | BAUD RATE DIVIDER (MSH) |                             |             | ATE DIVIDER (MSH) |             | 00         | Baud Rate Divider Register 2<br>(BRDR2) |                                                         |

| R/W    | 0          | 0         | 0                       | PSCDIV                      | TCLKO       | RCLKIN            | CLK<br>CK2  | DIV<br>CK1 | 00                                      | Clock Control Register (CCR)                            |

| R/W    | PAREN      | ODDPAR    | 0                       | 0                           | CFCRC       | CRCPRE            | CRC<br>CR2  | SEL<br>CR1 | 04                                      | Error Control Register (ECR)                            |

*Note 1*: RESET = register contents upon power-up or RESET\*.

Note 2: 16 bits for Bt68561A (word mode); 8 bits for Bt68560A (byte mode).

Table 3. MPCC Register Bit Assignments.

## **Clock Oscillator**

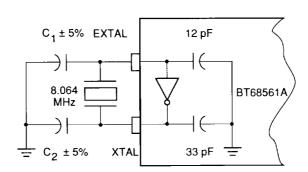

An on-chip oscillator is designed for a parallel resonant crystal connected between EXTAL and XTAL pins. The equivalent oscillator circuit is shown in Figure 4.

A parallel resonant crystal is specified by its load capacitance and series resonant resistance. For proper oscillator operation, the load capacitance ( $C_L$ ), series resistance ( $R_s$ ), and the crystal resonant frequency (F) must meet the following two relationships:

$$C_1 = 2 C_L - 12 pF$$

$C_2 = 2 C_L - 33 pF$

$$R_s/R_{smax} = \frac{2 \times 10^6}{(FC_L)^2}$$

where: F is in MHz; C and C<sub>L</sub> are in pF; R is in ohms.

To select a parallel resonant crystal for the oscillator, first select the load capacitance from a crystal manufacturer's catalog. Next, calculate  $R_{smax}$  based on F and  $C_L$ . The selected crystal must have an  $R_s$  less than the  $R_{smax}. \label{eq:Rsmax}$

For example, if  $C_L = 20 \text{ pF}$  for an 8.064 MHz parallel resonant crystal, then

$$C_1 = 40 - 12 = 28 \text{ pF}$$

(Use standard value of 27 pF.)

$C_2 = 40 - 33 = 7 \text{ pF}$  (Use standard value of 6.8 pF.)

Note:  $C_X$  = total shunt capacitance, including that caused by board layout.

The series resistance of the crystal must be less than

$$R_{smax} = \frac{2 \times 10^6}{(8.064 \times 20)^2} = 77 ohms$$

Figure 4. Clock Oscillator.

# **Internal Registers**

### Receiver Registers

#### Receiver Status Register (RSR)

| 7   | 6   | 5 | 4      | 3     | 2     | 1    | 0     |

|-----|-----|---|--------|-------|-------|------|-------|

| RDA | EOF | 0 | C/PERR | FRERR | ROVRN | RA/B | RIDLE |

Address = 00 Reset Value = \$00

The Receiver Status Register (RSR) contains the status of the receiver, including error conditions. Status bits are cleared by writing a 1 into respective positions, by writing a 1 into the RCR RRES bit, or by RESET\*. If an EOF, C/PERR, or FRERR is set in the RSR, the data reflecting the error (the next byte or word in the RxFIFO) must be read prior to resetting the corresponding status bit in the RSR. The IRQ\* output is asserted if any of the conditions reported by the status bits occur and the corresponding interrupt enable bit in the RIER is set.

The RSR format is the same as the frame status format (see below), except as noted.

### RSR 7 RDA—Receiver Data Available (RSR Only)

- (0)—The RxFIFO is empty (i.e., no received data are available).

- (1)—RDA bit is set and an interrupt issued (if enabled) when the RxFIFO has 1 to 8 bytes, or 1 to 4 words, of data in it.

RDA Reset—RDA cannot be cleared or reset in software. It is initialized to 0 upon hardware reset and remains 0 if no data have been received. It is set to a 1 and an interrupt is issued when a data byte/word is loaded to the RxFIFO with the negative edge of RxC coincident with the first bit of the next byte transmitted. It is automatically reset to 0 when the last byte/word is read from the RxFIFO by the host through the receiver data register.

#### RSR 6 EOF—End Of Frame (BOP and BSC)

- (0)—No end of frame has been detected.

- (1)—The closing flag (BOP) or pad (BSC) has been detected. EOF is loaded in the RxFIFO along with the FSB with which it is associated. The EOF is loaded into the RSR and the interrupt issued, if enabled, (when the RxFIFO read pointer is positioned at the FSB) with the trailing edge of the LDS\*.

EOF Reset—The byte/word containing the FSB must be read from the RxFIFO before resetting the EOF bit. Then EOF may be reset by writing a 1 to RSR6.

## RSR 5 RHW—Receive Half Word (Frame Status only [see Frame Status (RSR) in this section])

- (0)—The last word of the frame contains data on the upper half (D8–D15) and frame status on the lower half (D0–D7) of the data bus.

- (1)—The lower half of the data bus (D0-D7) contains the frame status, but the upper half (D8-D15) is blank or invalid.

#### RSR 4 C/PERR—CRC/Parity Error

- (0)—No CRC or parity error detected

- (1)—CRC error detected (BOP, BSC) or parity error detected (ASYNC, ISOC, and COP). The C/PERR bit is loaded into the RxFIFO with the negative-going RxC edge and with the byte or word with which it is associated. For ASYNC, ISOCH, or COP protocols, this is with the byte/word containing a parity error. For BOP or BSC, the C\PERR bit is loaded to RxFIFO (after the CRC check) with the FSB. C/PERR is loaded into the RSR and the interrupt is issued (when the read pointer is positioned at the FSB) with the trailing edge of LDS\*.

C/PERR Reset—The byte/word containing the FSB must be read from the RxFIFO before resetting the C/PERR bit. Then it may be reset by writing a 1 to RSR4.

#### RSR 3 FRERR—Frame Error

- (0)—No frame error detected

- (1)—FRERR is set for receiver overrun, flag detected off boundary (BOP), or frame error (ASYNC, ISOCH). For receiver overrun, the FRERR bit is set in the RxFIFO with the last byte when the overrun is detected.

For BOP, a minimum message size is an opening flag, one address byte, and one control byte. If the closing flag is detected before the control byte is sent, a short frame is indicated and a frame error results. For address extension, multi-address bytes may be received before the control byte is expected. The FRERR bit is latched in RxFIFO with the negative-going edge of RxC with the last address byte received upon detection of the flag off boundary. FRERR is loaded into the RSR and the interrupt is issued when the read pointer is positioned at the FSB with the trailing edge of LDS\*.

In ASYNC or ISOCH, an FRERR bit set indicates that the stop bit was detected off boundary (too early or too late for the number of bits expected by the setting of PSR2-3 and PSR2-4) or it was not the correct width (as expected by the setting of PSR2-6 and PSR2-5).

FRERR Reset—The byte/word containing the FSB must be read from the RxFIFO before the C/PERR bit is reset. The C/PERR bit may then be reset by writing a 1 to RSR3.

### RSR 2 ROVRN—Receiver Overrun

- (0)—No receiver overrun detected

- (1)—Receiver overrun detected. Data are loaded into the RxFIFO on byte boundaries with the negative-going edge of RxC coincident with the first bit of the subsequent data being received. When the eighth byte, or fourth word, of data has been written into RxFIFO without any data being read out, the RxFIFO is full and the incremented write pointer catches up with the read pointer. The next attempt to write data to RxFIFO causes ROVRN bit to be loaded to the RSR and the interrupt to be issued (if enabled). The data in the RxFIFO are not affected, but new received data are lost.

ROVRN Reset—The ROVRN bit is not self-clearing when data are read from the RxFIFO, but it may be reset by writing a 1 to RSR2.

#### RSR 1 RA/B—Receiver Abort/Break

- (0)—Normal operation

- (1)—(BOP). When an ABORT (seven 1s) is detected after the opening flag, the RA/B bit is set in the RSR and an interrupt is issued (if enabled). This bit is latched with the negative edge of RxC after the seventh 1 bit is detected.

*Note*: Because the previous byte can end in zero to five 1 bits, the abort could be recognized in the next byte as early as two to seven 1 bits.

(BSC) When ENQ is detected in a block of text data, the RA/B bit is set in the RSR and the interrupt is issued (if enabled) with the next negative edge of the RxC clock.

RA/B Reset—The RA/B bit is reset by writing a 1 to RSR1.

### RSR 0 RIDLE—Receiver-Idle (BOP Only)

- (0)—Receiver is not idle

- (1)—Fifteen or more 1s are detected. The RIDLE bit is set in RSR with the negative edge of the next RxC after 15 consecutive 1s have been detected.

RIDLE Reset—The RIDLE is reset by writing a 1 to RSR0.

Note: The RIDLE bit will set again in 15 clock cycles if RxD is still in the idle condition.

#### Receiver Control Register (RCR)

| 7 | 6      | 5      | 4      | 3      | 2 | 1     | 0    |

|---|--------|--------|--------|--------|---|-------|------|

| _ | RDSREN | DONEEN | RSYNEN | STRSYN | 0 | RABEN | RRES |

Address = 01 Reset value = \$01

The RCR selects receiver control options.

#### RCR 7 Not used

### RCR 6 RDSREN—Receiver Data Service Request Enable

- (0)—Disable receiver DMA mode

- (1)—Enable receiver DMA mode

### RCR 5 DONEEN—DONE\* Output Enable

- (0)—Disable DONE\* output

- (1)—Enable DONE\* output (when the receiver is in the DMA mode, i.e., RDSREN = 1)

### RCR 4 RSYNEN—RSYN Output Enable

Selects the DSR signal input or the RSYN SYNC signal output on the DSR\* pin.

- (0)—Input data-set-ready on DSR\*

- (1)—Output RSYN on DSR\*

# RCR 3 STRSYN—Strip SYN Character. (COP only)

- (0)—Do not strip SYN character

- (1)—Strip SYN character

*Note:* In non-IPARS mode, SYN character is the contents of AR2. In IPARS mode, SYN character is the content of register pair AR1, AR2.

#### RCR 2 Must be zero.

### RCR 1 RABTEN—Receiver Abort Enable. (BOP Only)

- (0)—Do not abort frame upon error detection.

- (1)—Abort frame upon RxFIFO overrun (ROVRN bit = 1 in the RSR) or CFCRC error detection (C/PERR bit = 1 in the RSR). If either error occurs, the MPCC ignores the remainder of the current frame and searches for the beginning of the next frame. (EOF is set upon abort.)

### RCR 0 RRES—Receiver Reset Command

- (0)—Enable normal receiver operation

- (1)—Reset receiver. Resets the receiver section, including the RxFIFO and the RSR (but not the RCR). RRES is set by RESET\* or by writing a 1 into this bit, and must be cleared by writing a 0 into this bit. RRES requires clearing after RESET\*.

### Receiver Data Register (RDR)

#### Bt68561 (Word Mode)

| 15  | 14 | 13 | 12     | 11 | 10 | 9 | 8   | 7   | 6 | 5      | 4 | 3 | 2   | 1 | 0 |

|-----|----|----|--------|----|----|---|-----|-----|---|--------|---|---|-----|---|---|

| MSB |    |    | Byte 1 |    |    |   | LSB | MSB |   | Byte 0 |   |   | LSB |   |   |

Address = 02

#### Bt68560 (Byte Mode)

| 7   | 6 | 5 | 4      | 3 | 2 | 1 | 0   |

|-----|---|---|--------|---|---|---|-----|

| MSB |   |   | Byte 0 | _ |   |   | LSB |

Address = 02

The receiver has an 8-byte (or 4-word) First In First Out (FIFO) register file (RxFIFO) where received data are stored before being transferred to the bus. The received data are transferred out of the RxFIFO via the receiver data register in 8-bit bytes or 16-bit words depending on the WD/BYT bit setting in PSR2. When the RxFIFO has a data byte/word ready to be transferred, the RDA status bit in the RSR is set to 1.

#### Frame Status (RDR)

| 7 | 6   | 5   | 4      | 3     | 2     | 1    | 0 |

|---|-----|-----|--------|-------|-------|------|---|

| 0 | EOF | RHW | C/PERR | FRERR | ROVRN | RA/B | 0 |

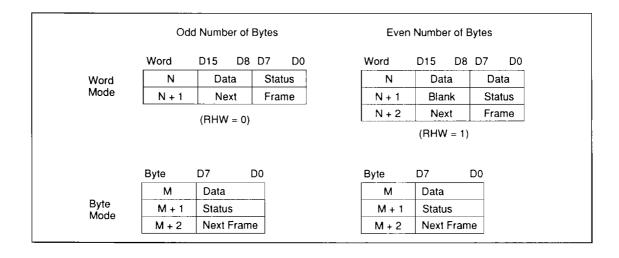

For the BSC and BOP protocols that have defined message blocks or frames, a frame status byte will be loaded into the RxFIFO following the last data byte of each block. The frame status byte contains all the status contained within the RSR with the exception of RDA and RIDLE. But, in addition to the RSR contents, the frame status byte has an RHW status in bit 5, which indicates either an even or an odd boundary (applicable to word mode only).

If the MPCC is in word mode and the last data byte was on an even byte boundary (i.e., there was an even number of bytes in the message), a blank byte will be loaded into the RxFIFO prior to loading the frame status byte in order to force the frame status byte and the next frame to be on an even boundary. When RHW = 0, the last word of the frame contains data on the upper half and status on the lower half of the data bus. If RHW = 1, the lower half of the bus contains status but the upper half is a blank or invalid byte.

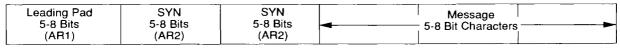

In the byte mode, the status byte will always immediately follow the last data byte of the block/frame (see Figure 5). The EOF status in the RSR is then set when the byte/word containing the frame status is the next byte/word to be read from the RxFIFO.

In the receiver DMA mode, when the EOF status in the RSR is set, DONE is asserted to the DMAC. Thus the last byte accessed by the DMAC is always a status byte, which the processor may read to check the validity of entire frame.

#### Receiver Interrupt Vector Number Register (RIVNR)

| 7                                       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------|---|---|---|---|---|---|---|--|--|

| Receiver Interrupt Vector Number (RIVN) |   |   |   |   |   |   |   |  |  |

Address = 04 Reset Value = \$0F

If a receiver interrupt condition occurs (as reported by status bits in the RSR that correspond to interrupt enable bits in the RIER) and the corresponding bit is set in the RIER, IRQ\* output is asserted to request MPU receiver interrupt service. When the IACK\* input is asserted from the bus, the Receiver Interrupt Vector Number (RIVN) from the Receiver Interrupt Vector Number Register (RIVNR) is placed on the data bus.

Figure 5. BSC/BOP Block/Frame Status Location.

### Receiver Interrupt Enable Register (RIER)

| 7         | 6         | 5 | 4            | 3           | 2           | 1          | 0 |

|-----------|-----------|---|--------------|-------------|-------------|------------|---|

| RDA<br>IE | EOF<br>IE | 0 | C/PERR<br>IE | FRERR<br>IE | ROVRN<br>IE | RA/B<br>IE | 0 |

Address = 05

Reset value = \$00

The Receiver Interrupt Enable Register (RIER) contains interrupt enable bits for the Receiver Status Register (RSR). When enabled, the IRQ\* output is asserted when the corresponding condition is detected and reported in the RSR.

- RIER 7 RDA IE—Receiver Data Available Interrupt Enable

- (0)—Disable RDA interrupt

- (1)—Enable RDA interrupt

- RIER 6 EOF IE—End of Frame Interrupt Enable

- (0)—Disable EOF interrupt

- (1)—Enable EOF interrupt

- RIER 5 Not used.

- RIER 4 C/PERR IE—CRC/Parity Error Interrupt Enable

- (0)—Disable C/PERR interrupt

- (1)—Enable C/PERR interrupt

- RIER 3 FRERR IE—Frame Error Interrupt Enable

- (0)—Disable FRERR interrupt

- (1)—Enable FRERR interrupt

- RIER 2 ROVRN IE—Receiver Overrun Interrupt Enable.

- (0)—Disable ROVRN interrupt

- (1)—Enable ROVRN interrupt

- RIER 1 RA/B IE—Receiver Abort/Break Interrupt Enable

- (0)—Disable RA/B interrupt

- (1)—Enable RA/B interrupt

- RIER 0 Not used

## Transmitter Registers

### **Transmitter Status Register (TSR)**

| 7    | 6   | 5 | 4 | 3 | 2     | 1     | 0 |

|------|-----|---|---|---|-------|-------|---|

| TDRA | TFC | 0 | 0 | 0 | TUNRN | TFERR | 0 |

Address = 08 Reset value = \$80

The Transmitter Status Register (TSR) contains the transmitter status, including error conditions. The transmitter status bits are cleared by writing a 1 into their respective positions, by writing a 1 into the TCR TRES bit, or by RESET\*. The IRQ\* output is asserted if any of the conditions reported by the status bits occur, and the corresponding interrupt enable bit in the transmitter interrupt enable register is set.

### TSR 7 TDRA—Transmitter Data Register Available

- (0)—The TxFIFO is full.

- (1)—The TxFIFO is available to be loaded through the Transmitter Data Register (TDR) (1–8 bytes or 1–4 words).

TDRA Reset—The TDR Available cannot be reset by the host in normal operation. It initializes to a 1 upon hardware or software reset of the MPCC. TDRA is not dependent on the serial clock.

### TSR 6 TFC—Transmitted Frame Complete (BOP, BSC, and COP Only)

- (0)—(All) Frame not complete

- (1)—(BOP) Closing flag or ABORT has been transmitted. The TFC bit is set, and the interrupt is issued (if enabled) with the negative edge of TxC coincident with the end of the last bit of the flag. When TABT set in TCR1, an ABORT is transmitted immediately, but TFC is not issued until after the closing flag or until after 8 bits of the MARK idle condition when the TxFIFO has been flushed of all current data bytes.

- (BSC) Trailing pad has been transmitted. TFC bit set is set and/or interrupt is issued with the negative edge of TxC coincident with the end of the last bit of the trailing pad.

- (COP) Last byte has been transmitted (TLAST set in TCR3). TFC bit set and/or interrupt is issued with the negative edge of the TxC coincident with the end of the last bit of the last byte.

TFC Reset—One full cycle of the serial clock (TxC) must elapse before the TFC bit can be reset by writing a 1 to TSR6.

#### TSR 5-3 Not used

### TSR 2 TUNRN—Transmitter Underrun (BOP, BSC, and COP Only)

- (0)—No TxFIFO underrun has occurred.

- (1)—An empty TxFIFO was accessed for data.

(BOP) Underrun is treated as an ABORT in that eight consecutive 1s are transmitted followed by the idle condition of MARK or FLAG.

(BSC and COP) Underrun causes SYN characters to be transmitted until new data are available in the TxFIFO. This is a repeated string of AR1, AR2 in the IPARS option of COP mode; otherwise this is a repeated string of AR2 pairs.

The TUNRN bit is set in TSR2, and the interrupt is issued with the positive edge of the TxC coincident with the eighth bit of data prior to the ABORT in BOP, or to SYN in BSC or COP.

TUNRN Reset—One full cycle of the serial clock (TxC) must elapse before the TUNRN bit can be reset by writing a 1 to TSR2.

#### TSR 1 TFERR—Transmit Frame Error (BOP Only)

- (0)—No frame error has occurred.

- (1)—A short frame condition exists in that no control field is transmitted. (Transmit Last Character [TLAST] was issued early with an address byte.) TFERR bit is set, and the interrupt is issued with the positive edge of TxC coincident with the end of the last bit of the byte causing the error

TFERR Reset—One full cycle of the serial clock (TxC) must elapse before TFERR bit can be reset by writing a 1 to TSR1.

#### **Transmitter Control Register (TCR)**

| 7   | 6      | 5    | 4   | 3     | 2    | 1    | 0    |

|-----|--------|------|-----|-------|------|------|------|

| TEN | TDSREN | TICS | THW | TLAST | TSYN | TABT | TRES |

Address = 09

Reset value = \$01

The Transmitter Control Register (TCR) selects transmitter control function.

#### TCR 7 TEN—Transmitter Enable

- (0)—Disable transmitter. TxD output is idled. The TxFIFO may be loaded while the transmitter is disabled.

- (1)—Enable transmitter

#### TCR 6 TDSREN—Transmitter Data Service Request Enable

- (0)—Disable transmitter DMA mode

- (1)—Enable transmitter DMA mode

#### TCR 5 TICS—Transmitter Idle Character Select

Selects the idle character to be transmitted when the transmitter is in an active idle mode (transmitter enabled or disabled).

(0)—Mark idle. TxD output is held high, except in IPARS mode. In this mode the idle character is the inverted contents of AR1.

```

For AR1(0) = 0; Idle code = 111 111

For AR1(0) = 1; Idle code = 000\ 000

```

(1)—Content of AR2 (BSC and COP, except in IPARS subject of COP mode). In IPARS mode, contents of AR1 and AR2. BREAK condition (ASYNC and ISOC), or FLAG character (BOP).

#### TCR 4 THW—Transmit Half Word

(Bt68561, word mode only). This bit is used when the frame or block ends on an odd boundary in conjunction with the TLAST bit and indicates that the last word in the TxFIFO contains valid data in the upper byte only. This bit must always be 0 in byte mode (Bt68560).

- (0)—Transmit full word (16 bits) from the TxFIFO.

- (1)—Transmit upper byte (8 bits) from the TxFIFO.

#### TCR 3 TLAST—Transmit Last Character (BOP, BSC, and COP Only)

- (0)—The next character is not the last character in a frame or block.

- (1)—The next character to be written into the TDR is the last character of the message. The TLAST bit automatically returns to a 0 when the associated word/byte is written to the TxFIFO. If the transmitter DMA mode is enabled, TLAST is set to a 1 by DONE\* from the DMA Controller. In this case the character written into the TDR in the current cycle is the last character.

#### TCR 2 TSYN—Transmit SYN (BSC and COP Only)

- (0)—Do not transmit SYN characters.

- (1)—Transmit SYN characters. Causes a pair of SYN characters to be transmitted (AR1 and AR2 in IPARS; AR2and AR2, otherwise) immediately following the current character. If BSC transparent mode is active, a DLE SYN sequence is transmitted. The TSYN bit automatically returns to a 0 when the SYN character is loaded into the transmitter shift register.

#### TCR 1 TABT—Transmit ABORT (BOP Only)

- (0)—Enable normal transmitter operation.

- (1)—Causes an abort by sending eight consecutive 1s. A data word/byte must be loaded into the TxFIFO after setting this bit in order to complete the command. The TABT bit clears automatically when the subsequent data word/byte is loaded into the TxFIFO.

#### TCR 0 TRES—Transmitter Reset Command

- (0)—Enable normal transmitter operation.

- (1)—Reset transmitter. Clears the transmitter section, including the TxFIFO and the TSR (but not the TCR). The TxD output is hold in "Mark" condition (TxD output is held high). TRES is set by RESET\* or by writing a 1 into this bit and is cleared by writing a 0 into this bit. TRES requires clearing after RESET\*.

### Transmit Data Register (TDR)

Bt68561 (Word Mode)

| 15  | 14 | 13 | 12 | 11     | 10 | 9 | 8   | 7   | 6 | 5 | 4       | 3 | 2 | 1 | 0   |

|-----|----|----|----|--------|----|---|-----|-----|---|---|---------|---|---|---|-----|

| MSB | _  |    |    | Byte 1 |    |   | LSB | MSB |   |   | Byte () |   |   |   | LSB |

Address = 0A

Bt68560 (Byte Mode)

| 7   | 6 | 5 | 4      | 3 | 2 | 1 | 0   |

|-----|---|---|--------|---|---|---|-----|

| MSB |   |   | Byte 0 |   |   |   | LSB |

Address = 0A

The transmitter has an 8-byte (or 4-word) FIFO register file (TxFIFO). Data to be transmitted are transferred from the bus into the TxFIFO via the Transmit Data Register (TDR) in 8-bit bytes or 16-bit words, depending on the WD/BYT bit setting in PSR2. The TDRA status bit in the TSR is set to 1 when the TxFIFO is ready to accept another data word/byte.

### **Transmitter Interrupt Vector Number Register (TIVNR)**

| 7 | 6 | 5 | 4                  | 3                | 2 | 1 | 0 |

|---|---|---|--------------------|------------------|---|---|---|

|   |   |   | nitter Interrupt \ | Vector Number (* | , |   |   |

Address = 0C

Reset value = \$0F

If a transmitter interrupt condition occurs (as reported by status bits in the TSR that correspond to interrupt enable bits in the TIER) and the corresponding bit in the TIER is set, the IRQ\* output is asserted to request MPU transmitter interrupt service when the IACK\* input is asserted from the bus, the transmitter interrupt vector number (TIVN) from the Transmitter Interrupt Vector Number Register (TIVNR) is placed on the data bus.

#### Transmitter Interrupt Enable Register (TIER)

| 7          | 6         | 5 | 4 | 3 | 2           | 1           | 0 |

|------------|-----------|---|---|---|-------------|-------------|---|

| TDRA<br>IE | TFC<br>IE | 0 | 0 | 0 | TUNRN<br>IE | TFERR<br>IE | _ |

Address = 0D

Reset value = \$00

The Transmitter Interrupt Enable Register (TIER) contains interrupt enable bits for the transmitter status register. When enabled, the IRQ\* output is asserted when the corresponding condition is detected and reported in the TSR.

#### TIER 7 TDRA IE—Transmitter Data Register (TDR) Available Interrupt Enable

(0)—Disable TDRA interrupt

(1)—Enable TDRA interrupt

### TIER 6 TFC IE—Transmit Frame Complete (TFC) Interrupt Enable

(0)—Disable TFC interrupt

(1)—Enable TFC interrupt

#### TIER 5-3 Not used.

#### TIER 2 TUNRN IE—Transmitter Underrun (TUNRN) Interrupt Enable

(0)—Disable TUNRN interrupt

(1)—Enable TUNRN interrupt

## TIER 1 TFERR IE—Transmit Frame Error (TFERR) Interrupt Enable

(0)—Disable TFERR interrupt

(1)—Enable TFERR interrupt

TIER 0 Not used

### Serial Interface Registers

#### Serial Interface Status Register (SISR)

| 7    | 6    | 5    | 4      | 3      | 2      | 1 | 0 |

|------|------|------|--------|--------|--------|---|---|

| CTST | DSRT | DCDT | CTSLVL | DSRLVL | DCDLVL | 0 | 0 |

Address = 10 Reset value = \$00

The Serial Interface Status Register (SISR) contains the serial interface status information. The transition status bits (CTST, DSRT, and DCDT) are cleared by writing a 1 into their respective position or by RESET\*. The level status bits (CTSLVL, DSRLVL, and DCDLVL) reflect the state of their respective inputs and cannot be cleared internally. The IRQ\* output is asserted if any of the conditions reported by the transition status bits occur and the corresponding interrupt enable bit in the SIER is set.

#### SISR 7 CTST—Clear to Send Transition Status

- (0)—The input on CTS\* has not transitioned positive.

- (1)—The input of CTS\* has transitioned positive from active to inactive. To detect this transition, RTS\* must be active (low) and the transmitter must be enabled (TRES in TCR0 = 0). The CTST bit is set in SISR7 and an interrupt is issued (if enabled) with the negative edge of TxC.

CTST Reset—A negative transition of the serial clock (TxC) must occur after the CTS\* input goes high before the CTST bit can be reset by writing a 1 to SISR7.

#### SISR 6 DSRT—Data Set Ready Transition Status

- (0)—The input on DSR\* has not transitioned negative.

- (1)—The input on DSR\* has transitioned negative from inactive to active. The DSRT bit is set in SISR7, and an interrupt is issued (if enabled) with the negative edge of RxC. The receiver must be enabled (RRES in RCR0 = 0).

DSRT Reset—A negative transition of the serial clock (RxC) must occur after the DSR\* input goes high before the DSRT bit can be reset by writing a 1 to SISR6.

#### SISR 5 DCDT—Data Carrier Detect Transition Status

- (0)—The input on DCD\* has not transitioned positive.

- (1)—The input on DCD\* has transitioned positive from active to inactive. The DCDT bit is set in SISR5, and an interrupt is issued (if enabled) with the negative edge of RxC. The receiver must be enabled (RRES in RCR0 = 0).

DCDT Reset—A negative transition of the serial clock (RxC) must occur after the DCD\* input goes high before the DCDT bit can be reset by writing a 1 to SISR5.

#### SISR 4 CTSLVL—Clear to Send Level

- (0)—The input on CTS\* is negated (high, inactive).

- (1)—The input on CTS\* is asserted (low, active).

CRSLVL Reset—The CTSLVL bit is SISR4 follows the state of the input to CTS\* and cannot be reset internally.

#### SISR 3 DSRLVL—Data Set Ready Level

- (0)—The input on DSR\* is negated (high, inactive).

- (1)—The input on DSR\* is asserted (low, active).

DSRLVL Reset—The DSRLVL bit in SISR3 follows the state of the input to DSR\* and cannot be reset internally.

#### SISR 2 DCDLVL—Data Carrier Detect Level

- (0)—The input on DCD\* is negated (high, inactive).

- (1)—The input on DCD\* is asserted (low, active).

DCDLVL Reset—The DCDLVL bit in SISR2 follows the state of the input to DCD\* and cannot be reset internally.

#### SISR 1-0 Not used

### **Serial Interface Control Register (SICR)**

| 7      | 6      | 5 | 4 | 3 | 2    | 1    | 0 |

|--------|--------|---|---|---|------|------|---|

| RTSLVL | DTRLVL | 0 | 0 | 0 | ECHO | TEST | 0 |

Address = 11

Reset value = \$00

The Serial Interface Control Register (SICR) controls various serial interface signals and test functions.

### SICR 7 RTSLVL—Request to Send Level

- (0)—Negate RTS\* output (high)

- (1)—Assert RTS\* output (low)

Note: In BOP, BSC, or COP, when the RTSLVL bit is cleared in the middle of data transmission, the RTS\* output remains asserted until the end of the current frame or block has been transmitted. In ASYNC or ISOC, the RTS\* output is negated when the TxFIFO is empty. If the transmitter is idling when the RTSLVL bit is reset, the RTS\* output is negated within two bit times.

#### SICR 6 DTRLVL—Data Terminal Ready Level

- (0)—Negate DTR\* output (high)

- (1)—Assert DTR\* output (low)

- **SICR** 5–3 **Not used.** These bits are initialized to 0 by RESET\* and must not be set to 1.

#### SICR 2 ECHO—Echo Mode Enable

- (0)—Disable echo mode (enable normal operation)

- (1)—Enable echo mode. Received data (RxD) is routed back through the transmitter to TxD. The contents of the TxFIFO are undisturbed. This mode may be used for remote test purposes.

#### SICR 1 TEST—Self-test Enable

- (0)—Disable self-test (Enable normal operation)

- (1)—Enable self-test. The transmitted data (TxD) and clock (TxC) are routed back through to the receiver through RxD and RxC, respectively (DCD\* and CTS\* are ignored). This loopback self-test may be used for all protocols. RxC is external, and CCR bits 2 and 3 must be a 1.

### SICR 0 Must be zero

## Serial Interrupt Vector Number Register (SIVNR)

| 7 | 6 | 5   | 4                 | 3               | 2   | 1 | 0 |

|---|---|-----|-------------------|-----------------|-----|---|---|

|   |   | Ser | ial Interrupt Vec | tor Number (SIV | /N) |   |   |

Address = 14 Reset value = \$0F

If a serial interface interrupt condition occurs (as reported by status bits in the SISR that correspond to interrupt enable bits in the SIER) and the corresponding bit in the SIER is set, the IRQ\* output is asserted to request MPU serial interface interrupt service. When the IACK\* input is asserted from the bus, the Serial Interrupt Vector Number (SIVN) from the Serial Interrupt Vector Number Register (SIVNR) is placed on the data bus.

### Serial Interrupt Enable Register (SIER)

| 7   | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|-----|-----|-----|---|---|---|---|---|

| CTS | DSR | DCD | 0 | 0 | 0 | 0 | 0 |

| IE  | ΙE  | IE  |   |   |   |   |   |

Address = 15 Reset value = \$00

The Serial Interrupt Enable Register (SIER) contains interrupt enable bits for the serial interface status register. When an interrupt enable bit is set, the IRQ\* output is asserted when the corresponding condition occurs as reported in the SISR.

### SIER 7 CTS IE—Clear to Send (CTS) Interrupt Enable

- (0)—Disable CTS interrupt

- (1)—Enable CTS interrupt

#### SIER 6 DSR IE—Data Set Ready (DSR) Interrupt Enable

- (0)—Disable DSR interrupt

- (1)—Enable DSR interrupt

### SIER 5 DCD IE—Data Carrier Detect (DCD) Interrupt Enable

- (0)—Disable DCD interrupt

- (1)—Enable DCD interrupt

#### SIER 4-0 Not used

## Global Registers

The global registers contain command information applying to different modes of operation and protocols. After changing global register data, the TRES in the TCR and RRES in the RCR should be set and then cleared prior to performing normal mode processing.

#### Protocol Select Register 1 (PSR1)

| 7 | 6 | 5 | 4 | 3     | 2    | 1     | 0     |

|---|---|---|---|-------|------|-------|-------|

| 0 | 0 | 0 | 0 | IPARS | ADR0 | CTLEX | ADDEX |

Address = 18

Reset value = \$00

Protocol select register 1 (PSR1) selects BOP protocol related options.

#### PSR1 7-4 Not used

### PSR1 3 IPARS—IPARS Option (COP Only)

- (0)—Normal COP operation

- (1)—Enable IPARS mode. See, also, RCR3 (STRSYN), TSR2 (TUNRN), TCR5 (TICS), and TCR2 (TSYN).

## PSR1 2 ADR0—Zero Address Option (BOP Only) (New Feature)

- (0)—Normal BOP operation

- (1)—Allow NULL (all "0") addresses

### PSR1 1 CTLEX—Control Field Extend (BOP Only) (New Feature)

- (0)—Select 8-bit control field

- (1)—Select 16-bit control field

### PSR1 0 ADDEX—Address Extend (BOP Only)

- (0)—Disable address extension. All 8-bits of the address byte are used for addressing.

- (1)—Enable address extension. When bit 0 in the address byte is a 0 the address field is extended by 1 byte. An exception to the address field extension occurs when the first address byte is all zeros (null address).

### **Protocol Select Register 2 (PSR2)**

| 7      | 6      | 5       | 4      | 3       | 2   | 1            | 0   |

|--------|--------|---------|--------|---------|-----|--------------|-----|

| WD/BYT | STOP E | BIT SEL | CHAR L | LEN SEL | F   | PROTOCOL SEI |     |

|        | SB2    | SB1     | CL2    | CLI     | PS3 | PS2          | PS1 |

Address = 19

Reset value = \$00

Protocol Select Register 2 (PSR2) selects protocols, character size, the number of stop bits, and word/byte mode.

#### PSR2 7 WD/BYT—Data Bus Word/Byte Mode

- (0)—Select byte mode. Selects the number of data bits to be transferred from the RxFIFO and the registers to the data bus, and to be transferred from the data bus to the TxFIFO and the registers. The MPCC is initialized by RESET\* to the byte mode.

- (1)—Select word mode. For operation with the 16-bit bus, select the word mode by sending \$80 on D7-D0 to address \$19 prior to transferring subsequent data between the MPCC and the data bus.

### PSR2 6-5 STOP BIT SEL—Number of Stop Bits Select

Selects the number of stop bits transmitted at the end of the data bits in ASYNC and ISOC modes.

| 6   | 5   | No. of S | top Bits |

|-----|-----|----------|----------|

| SB2 | SB1 | ASYNC    | ISOC     |

| 0   | 0   | 1        | 1        |

| 0   | 1   | 1-1/2    | 2        |

| 1   | 0   | 2        | 2        |

#### PSR2 4-3 CHAR LEN SEL—Character Length Select

Selects the character length, except in BOP and BSC, where the character length is always eight bits. Parity is not included in the character length.

| 4   | 3   | Character Length |

|-----|-----|------------------|

| CL2 | CL1 | Character Length |

| 0   | 0   | 5 bits           |

| 0   | 1   | 6 bits           |

| 1   | 0   | 7 bits           |

| 1   | 1   | 8 bits           |

#### PSR2 2-0 Protocol Sel-Protocol Select

Selects protocol and defines the protocol dependent control bits.

| 2   | 1   | 0   | Protocol        |

|-----|-----|-----|-----------------|

| PS3 | PS2 | PS1 | Fiolocol        |

| 0   | 0   | 0   | BOP (Primary)   |

| 0   | 0   | 1   | BOP (Secondary) |

| 0   | 1   | 0   | Reserved        |

| 0   | 1   | 1   | COP             |

| 1   | 0   | 0   | BSC EBCDIC      |

| 1   | 0   | 1   | BSC ASCII       |

| 1   | 1   | 0   | ASYNC           |

| 1   | 1   | 1   | ISOC            |

# Address Register 1 (AR1) Address

| 7 | 6                                                  | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----------------------------------------------------|---|---|---|---|---|---|

|   | BOP ADDRESS/BSC & COP PAD/IPARS SYN 1(New Feature) |   |   |   |   |   |   |

Address = 1A Reset value = \$00

### Address Register 2 (AR2)

| 7 | 6 | 5     | 4            | 3             | 2        | 1 | 0 |

|---|---|-------|--------------|---------------|----------|---|---|

|   |   | BSC & | COP SYN/IPAR | RS SYN 2 (New | Feature) |   |   |

Address = 1B Reset value = \$00

The protocol selected in PSR2 (BOP, BSC, and COP only) determines the function of the two 8-bit address registers (AR1 and AR2). As a secondary station in BOP, the contents of AR1 are used for address matching. In BSC and COP, AR1 and AR2 contain programmable leading PAD and programmable SYN characters, respectively.

### Address Register (AR) Contents

| Protocol Selected         | AR1         | AR2   |

|---------------------------|-------------|-------|

| BOP (Primary)             | X           | X     |

| BOP (Secondary)           | Address     | x     |

| BSC EBCDIC                | Leading PAD | SYN   |

| BSC ASCII                 | Leading PAD | SYN   |

| COP                       | Leading PAD | SYN   |

| COP (IPARS mode) (Note 1) | SYN 1       | SYN 2 |

| X = Not used              | •           | •     |

#### **Baud Rate Divider Register 1 (BRDR1)**

| 7 | 6 | 5 | 4           | 3             | 2 | 1 | 0 |

|---|---|---|-------------|---------------|---|---|---|

|   |   |   | BAUD RATE D | DIVIDER (LSH) |   |   |   |

Address = 1C

Reset value = \$01

### **Baud Rate Divider Register 2 (BRDR2)**

| 7 | 6 | 5 | 4           | 3            | 2 | 1 | 0 |

|---|---|---|-------------|--------------|---|---|---|

|   |   |   | BAUD RATE D | IVIDER (MSH) |   |   |   |

Address = 1D

Reset value = \$00

The two 8-bit Baud Rate Divider Registers (BRDR1 and BRDR2) hold the divisor of the baud rate divider circuit. BRDR1 contains the Least Significant Half (LSH), and BRDR2 contains the Most Significant Half (MSH). With an 8.064 MHz EXTAL input, standard bit rates can be selected with the combination of prescaler divider (in the CCR) and baud rate divider values shown in Table 4. For isochronous or synchronous protocols, the baud rate divider value must be multiplied by two for the same prescaler divider value.

The Baud Rate Divider (BRD) value can be computed for other crystal frequency, prescaler divider, and desired baud rate values as follows:

$$BRD = \frac{Crystal\ Frequency}{Prescaler\ Divider\ \bullet\ Baud\ Rate\ \bullet\ K}$$

where K = 1 for isochronous or synchronous

K = 2 for asynchronous

|            | Pres             | caler             |                  |                | Baud R         | ate Divider      | •                           |                |  |

|------------|------------------|-------------------|------------------|----------------|----------------|------------------|-----------------------------|----------------|--|

| Desired    | Divi             | ider              | A:               | synchrono      | us             | Isochror         | Isochronous and Synchronous |                |  |

| Baud Rate  |                  |                   |                  | Hexadeci       | mal Value      |                  | Hexade                      | cimal Value    |  |

| (Bit Rate) | Decimal<br>Value | PSCDIV<br>(0 - 1) | Decimal<br>Value | BRDR2<br>(MSH) | BRDR1<br>(LSH) | Decimal<br>Value | BRDR2<br>(MSH)              | BRDR1<br>(LSH) |  |

| 50         | 3                | 1                 | 26,880           | 69             | 00             | 53,760           | D2                          | 00             |  |

| 75         | 2                | 0                 | 26,880           | 69             | 00             | 53,760           | D2                          | 00             |  |

| 110        | 3                | 1                 | 12,218           | 2F             | BA             | 24,436           | 5F                          | 74             |  |

| 135        | 2                | 0                 | 14,933           | 3A             | 55             | 29,866           | 74                          | AA             |  |

| 150        | 3                | 1                 | 8,960            | 23             | 00             | 17,920           | 46                          | 00             |  |

| 300        | 2                | 0                 | 6,720            | 1A             | 40             | 13,440           | 34                          | 80             |  |

| 1200       | 3                | 1                 | 1,120            | 04             | 60             | 2,240            | 08                          | C0             |  |

| 1800       | 2                | 0                 | 1,120            | 04             | 60             | 2,240            | 08                          | C0             |  |

| 2400       | 2                | 0                 | 840              | 03             | 48             | 1,680            | 06                          | 90             |  |

| 3600       | 2                | 0                 | 560              | 02             | 30             | 1,120            | 04                          | 60             |  |

| 4800       | 3                | 1                 | 280              | 01             | 18             | 560              | 02                          | 30             |  |

| 7200       | 2                | 0                 | 280              | 01             | 18             | 560              | 02                          | 30             |  |

| 9600       | 3                | 1                 | 140              | 00             | 8C             | 280              | 01                          | 18             |  |

| 19200      | 3                | 1                 | 70               | 00             | 46             | 140              | 00                          | 8C             |  |

| 38400      | 3                | 1                 | 35               | 00             | 23             | 70               | 00                          | 46             |  |

Table 4. Standard Baud Selection (8.064 MHz Crystal).

## **Clock Control Register (CCR)**

| 7 | 6 | 5 | 4      | 3     | 2      | 1   | 0   |

|---|---|---|--------|-------|--------|-----|-----|

| 0 | 0 | 0 | PSCDIV | TCLKO | RCLKIN | CLK | DIV |

|   |   |   |        |       |        | CK2 | CK1 |

Address = 1E Reset value = \$00

The CCR selects various clock options.

#### CCR 7-5 Not used

#### CCR 4 PSCDIV—Prescaler Divider

The prescaler divider network reduces the external/oscillator frequency to a value for use by the internal baud rate generator.

(0)—Divide by 2

(1)—Divide by 3

#### CCR 3 TCLKO—Transmitter Clock Output Select

(0)—Select TxC to be an input

(1)—Select TxC to be an output (1X clock)

### CCR 2 RCLKIN—Receiver Clock Internal Select (ASYNC Only)

(0)—Select external RxC

(1)—Select internal RxC

### CCR 1-0 CLK DIV--External Receiver Clock Divider

Selects the divider of the external RxC to determine the receiver data rate.

| CK2 | CK1 | Divider         |

|-----|-----|-----------------|

| 0   | 0   | 1 (ISOC)        |

| 0   | 1   | 16 (ASYNC only) |

| 1   | 0   | 32 (ASYNC only) |

| 1   | 1   | 64 (ASYNC only) |

## CCR 1-0 CLK DIV—External Receiver Clock Divider

Selects the divider of the external RxC to determine the receiver data rate.

| CK2 | CK1 | Divider         |

|-----|-----|-----------------|

| 0   | 0   | 1 (ISOC)        |

| 0   | 1   | 16 (ASYNC only) |

| 1   | 0   | 32 (ASYNC only) |

| 1   | 1   | 64 (ASYNC only) |

## **Error Control Register (ECR)**

| 7     | 6      | 5 | 4 | 3     | 2      | 1   | 0   |

|-------|--------|---|---|-------|--------|-----|-----|

| PAREN | ODDPAR | _ |   | CFCRC | CRCPRE | CRC | SEL |

|       |        |   |   |       |        | CR2 | CR1 |

Address = 1F

Reset value = \$04

# Input/Output Functions

#### MPU Interface

Transfer of data between the MPCC and the system bus involves the following signals:

|                              | Bt68561A      | Bt68560A |

|------------------------------|---------------|----------|

| Address Lines                | A1-A4         | A0–A4    |

| Data Lines                   | D0-D15        | D0-D7    |

| Read/Write                   | R/W*          | R/W*     |

| Data Transfer<br>Acknowledge | DTACK*        | DTACK*   |

| Chip Select                  | CS*           | CS*      |

| Data Strobes                 | UDS* and LDS* | DS*      |

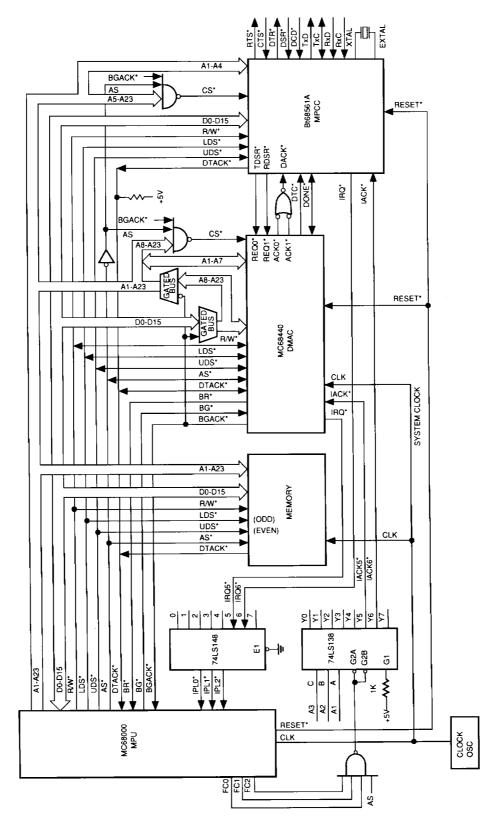

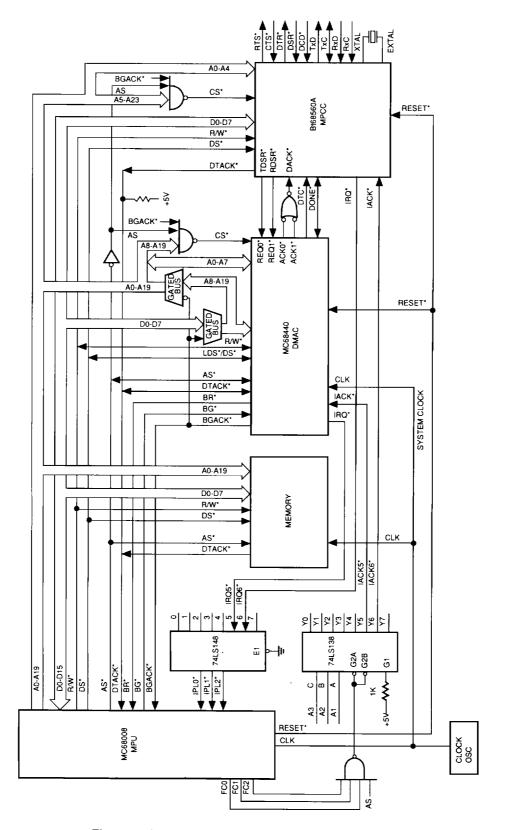

Figure 6 and Figure 7 show typical interface connections.

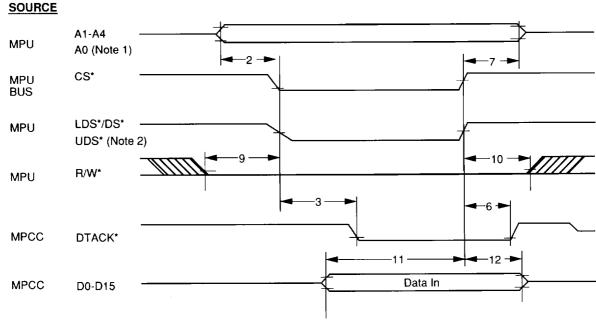

#### **Read/Write Operation**

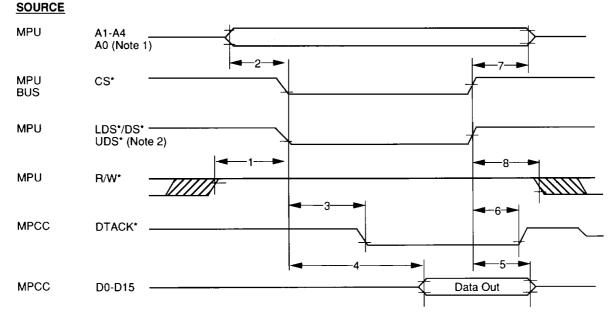

The R/W\* input controls the direction of data flow on the data bus. Chip Select (CS\*) enables the MPCC for access to the internal registers and other operations. When CS\* is asserted, the data I/O buffer acts as an output driver during a read operation and as an input buffer during a write operation. CS\* must be decoded from the address bus and gated with Address Strobe (AS\*).

When the Bt68561A is connected to the 16-bit bus for operation in the word mode (WD/BYT = 1 in the PSR2), address lines A1 through A4 select the internal register(s). The 8-bit control/status registers are accessed two at a time, and the 16-bit data registers are accessed on even address boundaries. When the MPCC is selected (CS\* low) during a read (R/W\* high), 16 bits of register data are placed on the data bus when the data strobes LDS\* and UDS\* are asserted. LDS\* strobes the eight data bits from the even-numbered registers to the lower data bus lines (D0-D7), and UDS\* strobes the eight data bits from the odd-numbered registers to the upper data bus lines (D8-D15). The MPCC

asserts Data Transfer Acknowledge (DTACK\*) prior to placing data on the data bus. Conversely, when the MPCC is selected (CS\* low) during a write (R/W\* low), LDS\* and UDS\* strobe data from the D0–D7 and D8–D15 data bus lines into the addressed even- and odd-numbered registers, respectively, and the MPCC asserts DTACK\*. DTACK\* is negated when CS\* is negated, as illustrated in Figures 8 and 9).

When the Bt68560A is connected to the 8-bit bus for operation in the byte mode (WD/BYT = 0 in the PSR2), address lines A0 through A4 select one internal 8-bit register. When the MPCC is selected (CS\* low) during a read (R/W\* high), eight bits of register data are placed on data bus lines D0 through D7 when the data strobe DS\* is asserted. When the MPCC is selected (CS\* low) for a write (R/W\* low), DS\* strobes data from the D0-D7 data lines into the selected register.

#### DMA Interface

The MPCC is capable of providing DMA data transfers at up to 2 Mbytes per second when used with the MC68440 or MC68450 DMAC in the single address mode. Based on 4 Mb/s serial data rate and 5 bits per character, the maximum DMA required transfer rate is 800 Kbytes per second.

The MPCC has separate DMA enable bits for the transmitter and receiver, each of which requires a DMA channel. Both the transmitter and receiver data are implicitly addressed (TDR or RDR); therefore, addressing the data register is not required before data may be transferred. The MPCC and the DMAC communicate with each other by way of a two-signal request/acknowledge handshake. Since the MPCC has only one acknowledge input, DACK\*, for its two DMA request lines, an external OR function must be provided to combine the two DMA acknowledge signals. The MPCC uses the R/W\* input to distinguish between the Transmitter Data Service Request (TDSR\*) acknowledge and the Receiver Data Service Request (RDSR\*) acknowledge.

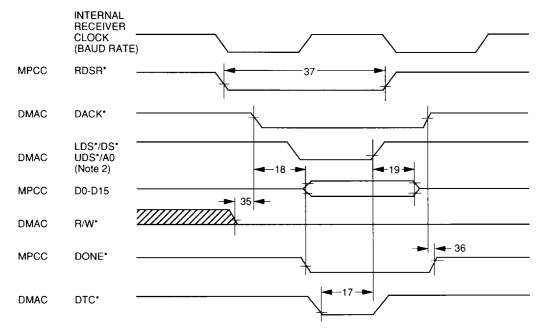

#### **Receiver DMA Mode**

The receiver DMA mode is enabled when the RDSREN bit in the Receiver Control Register (RCR) is set to 1. When data are available in the RxFIFO, RDSR\* is asserted for one receiver clock period (BOP and BSC) to initiate the MPCC to memory DMA transfer. For asynchronous operation, RDSR\* is asserted for two to

Figure 6. Typical Interface to 68000-Based System.

Figure 7. Typical Interface to 68008-Based System.

- Note 1: Byte mode when connected to A0 ON 68008 bus.

- Note 2: Word mode when connected to UDS\* on 68000 bus.

- Note 3: Timing measurements are referenced to and from a low voltage of 0.8 V and a high voltage of 2.0 V, unless otherwise noted.

Figure 8. MPCC Read Cycle Timing.

- Note 1: Byte mode when connected to A0 ON 68008 bus.

- Note 2: Word mode when connected to UDS\* on 68000 bus.

- Note 3: Timing measurements are referenced to and from a low voltage of 0.8 V and a high voltage of 2.0 V, unless otherwise noted.

Figure 9. MPCC Write Cycle Timing.

three periods of the system clock, depending on the prescale factor. The next RDSR\* cycle may be initiated as soon as the current RDSR\* cycle is completed (i.e., a full sequence of DACK\*, DS\*, and DTC\*).

In response to RDSR\* assertion, the DMAC sets the R/W\* line to write, and asserts the memory address, address strobe, and DMA acknowledge. The MPCC outputs data from the RxFIFO to the data bus, and the DMAC asserts the data strobes. The memory latches the data and asserts DTACK\* to complete the data transfer. The DMAC asserts DTC\* to indicate to the MPCC that data transfer is complete. Timing relationships for the DMA mode are illustrated in Figure 10.

RDSR\* is inhibited when either RDSREN is reset to zero or RRES is set to 1 (both in the RCR), or when RESET\* is asserted.

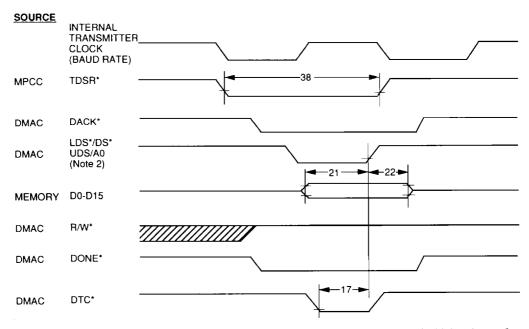

#### **Transmitter DMA Mode**

The transmitter DMA mode is enabled when the TDSREN bit in the TCR is set to 1. When the TxFIFO is available, (TDSR\* is asserted for one transmitter clock period to initiate the memory to MPCC DMA transfer. For asynchronous operation, TDSR\* is asserted for a period of one half the transmitter baud rate. The next TDSR\* cycle may be initiated as soon as the current TDSR\* cycle is completed.

In the transmitter DMA mode, the TxFIFO is implicitly addressed. That is, when the transfer is from memory to the TxFIFO, only the memory is addressed. In response to TDSR\* assertion, the DMAC sets the R/W\* line to read, and asserts the memory address, address and data strobes, and DMA acknowledge. The memory places data on the data bus and asserts DTACK\*. Data are valid at this time and will remain valid until the data strobes are negated. The DMAC asserts DTC\* to indicate to the MPCC that data are available. The MPCC loads the data into the TxFIFO on the negation (rising edge) of DS\*, and the transfer is complete. When a TxFIFO underrun occurs, the TUNRN bit is set in TSR2, the interrupt is issued, and the ABORT sequence is entered (eight consecutive 1s are transmitted). The next word/byte in TxFIFO clears the ABORT bit, and the idle mode is entered. When a transmission is aborted, it is expected that the interrupt will allow the host system to decide the next course of action probably to reset the DMAC and retransmit the message. A timing diagram for the transmitter DMA mode is illustrated in Figure 11.

TDSR\* is inhibited when either TDSREN is reset to zero or RRES is set to 1 (both in the TCR), or when RESET\* is asserted.

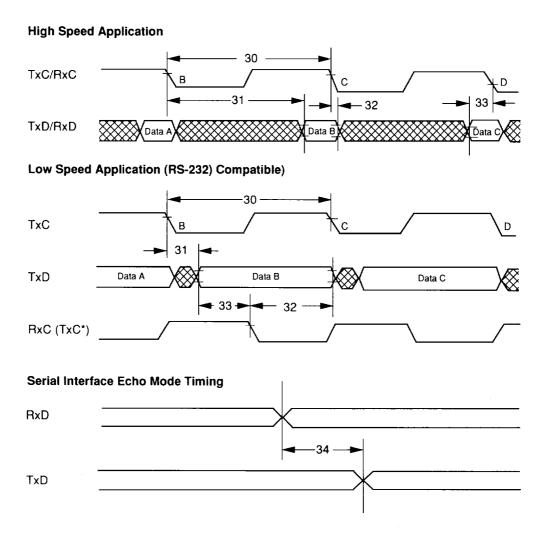

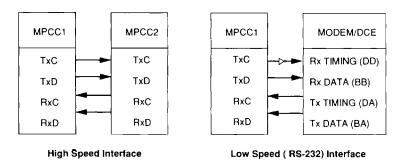

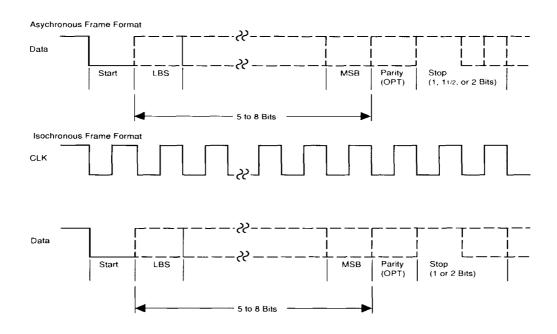

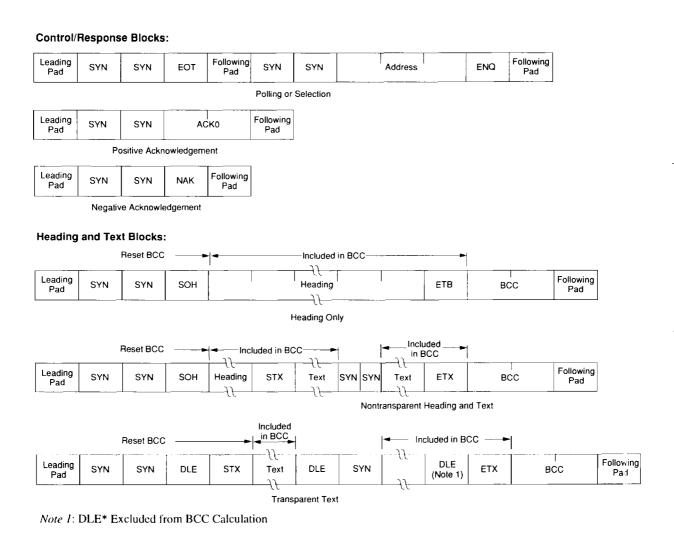

#### **DONE\* Signal**