**CS-283**

# FLOPPY DISK WRITE CONTROL/HEAD DRIVER

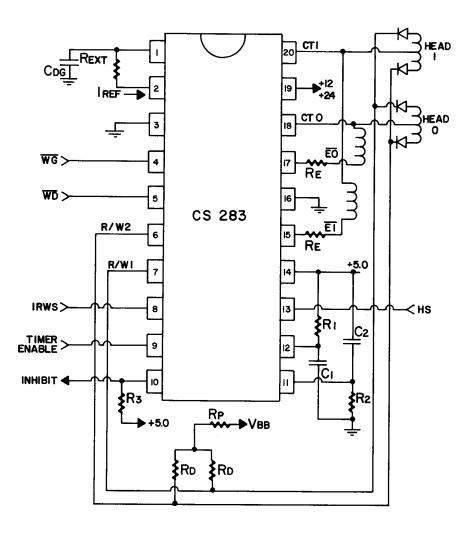

The CS 283 is a monolithic integrated WRITE CONTROLLER/HEAD DRIVER designed to provide the entire interface between the write data and head control signals and the heads (write and erase) for either TUNNEL or STRADDLE erase floppy disk systems.

Provisions are made for selecting a range of accurately controlled write currents and for head selection during both read and write operation. Additionally, provisions are included for externally adjusting degauss period, inner/outer track compensation, and the delay from write gate to erase turn on and turn off.

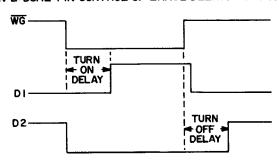

ERASE DELAYS are controlled by driving the delay inputs D1 and D2 with standard TTL open collector logic (microprocessor compatible) or by using the external RC mode in which case the delay is one RC (K factor = 1.0). By grounding pin 9, the erase delays may be controlled by driving D2 only.

In addition, an INHIBIT output is provided which indicates that the heads are active whether during write, degauss, or erase.

- Head Selection—Current Steering Through Write Head and Erase Coil in Write Mode.

- Adjustable On-Chip Delay of Erase Timing—Stable K Factor.

- Delay Pins Logic Compatible for Direct Micro-processor Compatibility.

- Optional Single Pin Control of Erase Delays.

- Inhibit Output Provided to Disable Read or Step During Head Active Time.

- Provides High Impedance (Read Data Enable) During Read Mode.

- Head Current (Write) Guaranteed Using Trimmed Internal Resistor (3.0 mA using R<sub>ext</sub>=10kΩ).

- IRW Select Input Provides for Inner/Outer Track Compensation.

- Degauss Period Externally Adjustable.

- Specified With ±10% Logic Supply and Head Supply (V<sub>BB</sub>) from 10.8V to 26.4V.

- Power Up Inhibit Function On Both V<sub>BB</sub> And V<sub>CC</sub> Power Supplies.

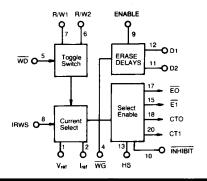

#### **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (Note 1) $(T_A = 25^{\circ}C)$

| RATING                         | SYMBOL           | VALUE       | UNIT |

|--------------------------------|------------------|-------------|------|

| Power Supply Voltage (Pin 14)  | V <sub>cc</sub>  | 7.0         | Vdc  |

| Power Supply Voltage (Pin 19)  | V <sub>BB</sub>  | 30          | Vdc  |

| Input Voltage (Pins 4, 5, 8)   | V,               | 5.75        | Vdc  |

| Storage Temperature            | T <sub>stq</sub> | -55 to +150 | °C   |

| Operating Junction Temperature | T,               | 150         | °C   |

Note 1 "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

#### RECOMMENDED OPERATING CONDITIONS

| RATING                              | SYMBOL          | VALUE          | UNIT |

|-------------------------------------|-----------------|----------------|------|

| Power Supply Voltage (Pin 14)       | V <sub>cc</sub> | +4.5 to +5.5   | Vdc  |

| Power Supply Voltage (Pin 19)       | V <sub>BB</sub> | +10.8 to +26.4 | Vdc  |

| Operating Ambient Temperature Range | TA              | 0 to +70       | °C   |

**ELECTRICAL CHARACTERISTICS**  $(T_A = 0 \text{ to} + 70^{\circ}\text{C}, V_{CC} = 4.5 \text{ to} 5.5 \text{ V}, V_{BB} = 10.8 \text{ to} 26.4 \text{ V unless otherwise noted.}$  Typicals given for  $V_{CC} = 5.0 \text{ V}, V_{BB} = 12 \text{ V and } T_A = 25^{\circ}\text{C}$  unless otherwise noted.)

| CHARACTERISTICS                                                                                                                                                                                                               | PINS                                | SYMBOL            | MIN.                  | TYP.                             | MAX.                                             | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-----------------------|----------------------------------|--------------------------------------------------|------|

| DIGITAL INPUT VOLTAGES                                                                                                                                                                                                        |                                     |                   | •                     |                                  | <del>*************************************</del> |      |

| Power Supply Current—V <sub>cc</sub><br>V <sub>BB</sub>                                                                                                                                                                       |                                     | I <sub>cc</sub>   |                       | 22<br>15                         | 60<br>30                                         | mA   |

| High Level Input Voltage $(V_{CC} = 4.5 \text{ V})$                                                                                                                                                                           | 4, 8, 13                            | V <sub>IH</sub>   | 2.0                   | _                                | _                                                | ٧    |

| Low Level Input Voltage $(V_{CC} = 5.5 \text{ V})$                                                                                                                                                                            | 4, 8, 13                            | V <sub>IL</sub>   | _                     | -                                | 0.8                                              | ٧    |

| Input Clamp Voltage $(I_{IK} = -12 \text{ mA})$                                                                                                                                                                               | 4, 5, 8, 13                         | V <sub>IK</sub>   | _                     | 0.87                             | -1.5                                             | ٧    |

| Positive Threshold $(V_{CC} = 5.0)$                                                                                                                                                                                           | 5                                   | V <sub>T(+)</sub> | 1.5                   | 1.75                             | 2.0                                              | ٧    |

| Negative Threshold $(V_{cc} = 5.0)$                                                                                                                                                                                           | 5                                   | V <sub>T(-)</sub> | 0.7                   | 0.98                             | 1.3                                              | ٧    |

| Hysteresis ( $V_{T(+)} - V_{T(-)}$<br>$T_A = 0^{\circ}C$ to + $70^{\circ}C$<br>$T_A = 25^{\circ}C$                                                                                                                            |                                     | $V_{HTS}$         | 0.2<br>0.4            | <br>0.76                         | _                                                | v    |

| DIGITAL INPUT CURRENTS                                                                                                                                                                                                        |                                     |                   |                       | •                                |                                                  |      |

| High Level Input Current $(V_{CC} = 5.5 \text{ V}, V_{BB} = 26.4 \text{ V}, V_{I} = 2.4 \text{ V})$                                                                                                                           | 4, 5, 8, 13                         | I <sub>tH</sub>   |                       | 0.1                              | 40                                               | μА   |

| Low Level Input Current $ \begin{array}{ll} \text{($V_{CC}=5.5$ V, $V_{BB}=26.4$ V, $T_{A}=25^{\circ}$C unless} \\ \text{noted below)} \\ V_{BB}=12 \ V \\ V_{BB}=24 \ V \\ V_{CC}=5.0 \ V \\ V_{CC}=5.0 \ V \\ \end{array} $ | 4, 5, 8, 13<br>4<br>4<br>5<br>8, 13 | l <sub>it</sub>   | _<br>_<br>_<br>_<br>_ | <br>0.36<br>0.76<br>0.46<br>0.39 | -1.6<br><br>                                     | mA   |

| DIGITAL OUTPUT LEVEL (INHIBIT)                                                                                                                                                                                                |                                     |                   |                       |                                  |                                                  |      |

| High Level Output Current $(V_{OH} = 7.0V, V_{CC} = 4.5V)$                                                                                                                                                                    | 10                                  | I <sub>OH</sub>   | _                     | <u> </u>                         | 100                                              | μΑ   |

| Low Level Output Voltage $(I_{OL} = 4.0 \text{mA}, V_{CC} = 4.5 \text{V})$                                                                                                                                                    | 10                                  | V <sub>oL</sub>   | _                     | _                                | 0.5                                              | V    |

**ELECTRICAL CHARACTERISTICS** (continued) ( $T_A=0$  to +70°C.  $V_{CC}=4.5$  to 5.5 V,  $V_{BB}=10.8$  to 26.4 V unless otherwise noted. Typicals given for  $V_{CC}=5.0$  V,  $V_{BB}=12$  V and  $T_A=25$ °C unless otherwise noted.)

| loted. Typicals given for $V_{cc}$ =5.0 V, $V_{BB}$ =12 V and T <sub>A</sub> CHARACTERISTICS       | PINS   | SYMBOL                         | MIN                  | TYP                  | MAX          | UNIT |

|----------------------------------------------------------------------------------------------------|--------|--------------------------------|----------------------|----------------------|--------------|------|

| CENTER-TAP and ERASE OUTPUTS                                                                       |        |                                |                      |                      |              |      |

| Output High Voltage                                                                                | 1      | Ī                              |                      |                      |              |      |

| $(I_{OH} = -100 \text{ mA}, V_{CC} = 4.5 \text{ V})$<br>$V_{BB} = 10.8 \text{ to } 26.4 \text{ V}$ | 18, 20 | V <sub>oн</sub>                | V <sub>вв</sub> -1.5 | V <sub>вв</sub> -1.0 |              | V    |

| Output Low Voltage                                                                                 |        |                                |                      |                      |              | l    |

| $(I_{OL} = 1.0 \text{ mA})$<br>$V_{BB} = 12 \text{V}$                                              | 18, 20 | V <sub>oL</sub>                |                      | 70                   | 150          | m∨   |

| $V_{BB} = 24 \text{ V}$                                                                            | 10, 20 | ¥ 0L                           | _                    | 70                   | 150          | ,    |

| Output High Leakage<br>(V <sub>OH</sub> =24 V, V <sub>CC</sub> =4.5V, V <sub>BB</sub> =24 V)       | 15, 17 | I <sub>OH</sub>                |                      | 0.01                 | 100          | μΑ   |

| Output Low Voltage                                                                                 |        |                                |                      |                      |              | }    |

| $(I_{OL} = 90 \text{ mA}, V_{CC} = 4.5 \text{ V})$<br>$V_{BB} = 12 \text{V}$                       | 15, 17 | Vol                            | _                    | 0.27                 | 0.60         | V    |

| V <sub>88</sub> =24 V                                                                              |        | :                              | -                    | 0.27                 | 0.60         | _    |

| CURRENT SOURCE                                                                                     |        |                                |                      |                      | _            |      |

| Reference Voltage                                                                                  | 1      | $V_{ref}$                      | _                    | 5.7                  | _            | ٧    |

| Degauss Voltage<br>(Voltage Pin 1-Voltage Pin 2)                                                   | 1      | V <sub>DEG</sub>               | _                    | 1.0                  | -            | V    |

| Bias Voltage                                                                                       | 2      | V <sub>F</sub>                 | _                    | 0.7                  | _            | V    |

| Write Current Off Leakage (V <sub>OH</sub> =35 V)                                                  | 6, 7   | I <sub>OH</sub>                | _                    | 0.03                 | 15           | μΑ   |

| Saturation Voltage                                                                                 | 6, 7   | V <sub>sat</sub>               | _                    | 0.85                 | 2.7          | V    |

| (V <sub>BB</sub> =12 V)                                                                            |        | Sat                            |                      |                      |              | ļ    |

| Current Sink Compliance (For $V_{6,7}$ =4.0 V to 24 V, $V_{\overline{WG}}$ =0.8 V)                 | 6, 7   | △I <b>RW2</b> ,1               | _                    | 15                   | 40           | μΑ   |

| Average Value Write Current                                                                        |        |                                |                      |                      |              |      |

| $(\frac{(I_{Pin 6} + I_{Pin}7)}{2}$ for $V_{BB} = 10.8$ to 26.4 V)                                 |        |                                |                      |                      |              |      |

| $@I_{R} = I_{Low}, R = 10k$                                                                        |        |                                | 0.04                 |                      | 0.00         |      |

| $T_A = 25$ °C'<br>$T_A = 0$ to +70°C                                                               | 6, 7   |                                | 2.91<br>2.84         | 3.0                  | 3.09<br>3.16 |      |

| $@l_{R,w} = l_{LOW} R = 5.0 k$                                                                     | ", '   | I <sub>R/W(L)</sub>            |                      |                      |              | mA   |

| $T_A = 25$ °C'<br>$T_A = 0$ to +70°C                                                               |        |                                | 5.64<br>5.51         | 5.89                 | 6.14<br>6.28 |      |

|                                                                                                    |        |                                | 5.51                 | _                    | 0.20         |      |

| T <sub>A</sub> =25-C                                                                               |        | $\Delta \overline{I_{R/W(H)}}$ | 30.3                 | 33.3                 | 35.5         | %    |

| T <sub>A</sub> =0 to +70°C                                                                         |        | R/W(H)                         | 29.3                 | 33.3                 | 36.6         |      |

| Difference in Write Current (IPIN 6-IPIN 7)                                                        |        |                                |                      |                      |              |      |

| $@I_{BW} = I_{LOW}$ , $V_{BB} = 10.8 \text{ V to } 26.4 \text{ V}$                                 |        |                                |                      |                      |              |      |

| R=10 k<br>T <sub>a</sub> =25°C                                                                     | 6.7    |                                |                      | 0.003                | 0.015        |      |

| $T_A=0$ to $+70^{\circ}$ C                                                                         | ".,    | 1 <sub>n/w</sub> △             | _                    | J.003                | 0.013        | mA   |

| R=5.0 k                                                                                            |        |                                |                      |                      | 0.030        | 1    |

| $T_A = 25^{\circ}C$<br>$T_A = 0 \text{ to } +70^{\circ}C$                                          |        |                                | _                    | _                    | 0.030        | l    |

| ERASE DELAY ACCURACY                                                                               |        |                                |                      |                      |              |      |

| T = KRC                                                                                            | 11,12  | К                              | 0.91                 | 11                   | 1.09         |      |

| POWER UP INHIBIT                                                                                   |        |                                |                      |                      |              |      |

| (Voltage Below Which R/W1, R/W2, EO, E1 Are Inhibited.)                                            |        |                                |                      |                      | ****         |      |

| V <sub>cc</sub> Power Up Inhibit                                                                   |        |                                |                      |                      |              |      |

| $V_{BB} = OV To 26.4V$                                                                             | 14     | V <sub>cc</sub> /PUI           | 3.2                  | 3.9                  | 4.4          | V    |

| V <sub>BB</sub> Power Up Inhibit                                                                   | 19     | V <sub>BB</sub> /PUI           | 8                    | 9                    | 10           | l V  |

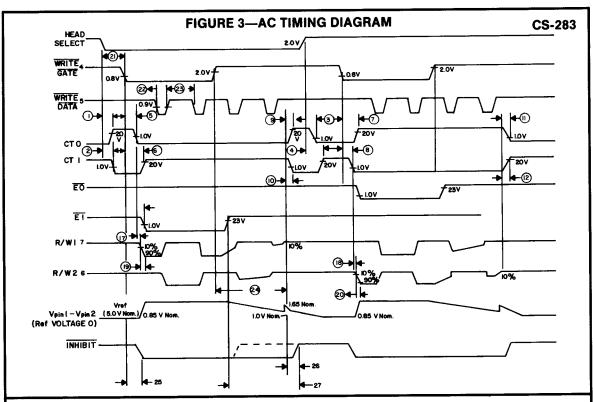

#### **AC SWITCHING CHARACTERISTICS**

$(V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}, V_{BB} = 24 \text{V}, IRWS = 0.4 \text{V}, and I_{BW} = 3.0 \text{ mA} unless otherwise noted—refer to Figure 3.)}$

| CHARACTERISTICS (NOTE 2)                                                                                                                                                                | fin (NOTE 3) | MIN | TYP  | MAX | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|------|-----|------|

| Delay from Head Select going low through 0.8 V to CTO going high through 20 V.                                                                                                          | HS, Pin 13   | _   | 1.6  | 4.0 | μS   |

| Delay from Head Select going low though 0.8 V to CT1 going low through 1.0 V.                                                                                                           | HS, Pin 13   | _   | 2.1  | 4.0 | μS   |

| 3 Delay from Head Select going high through 2.4 V to CTO going low through 1.0 V.                                                                                                       | HS, Pin 13   | _   | 1.7  | 4.0 | μS   |

| 4 Delay from Head Select going high through 2.4 V to CT1 going high through 20 V.                                                                                                       | HS, Pin 13   | _   | 1.4  | 4.0 | μS   |

| Delay from WG going low through 0.8 V to CTO going low through 1.0 V.                                                                                                                   | WG, Pin 4    | _   | 1.3  | 4.0 | μS   |

| Delay from WG going low through 0.8 V to CT1 going high through 20 V.                                                                                                                   | WG. Pin 4    | _   | 0.8  | 4.0 | μS   |

| Delay from WG going low through 0.8 V to CTO going high through 20 V.                                                                                                                   | WG. Pin 4    | _   | 0.75 | 4.0 | μS   |

| B Delay from WG going low through 0.8 V to CT1 going low through 1.0 V.                                                                                                                 | WG, Pin 4    | _   | 1.2  | 4.0 | μS   |

| After WG goes high, delay from R/W1 turning off<br>through 10% to CTO going high through 20 V.                                                                                          | WG, Pin 4    | 20  | 750  | _   | ns   |

| 10 After WG goes high, delay from R/W1 turning off through 10% to CT1 going low through 1.0 V.                                                                                          | WG, Pin 4    | 20  | 1200 | _   | ns   |

| 11 After WG goes high, delay from R/W2 turning off through 10% to CTO going low through 1.0 V.                                                                                          | WG, Pin 4    | 20  | 1200 | _   | ns   |

| 12 After WG goes high, delay from R/W2 turning off through 10% to CT1 going high through 20 V.                                                                                          | WG. Pin 4    | 20  | 600  | _   | ns   |

| 17 After WG goes low, delay from CTO going low through 1.0 V to R/W1 turning on through 10%.                                                                                            | WG, Pin 4    | 20  | 750  | _   | ns   |

| 18 After WG goes low, delay from CT1 going low through 1.0 V to R/W2 turning on through 10%.                                                                                            | WG, Pin 4    | 20  | 750  | _   | ns   |

| 19 After WG goes low, fall time (10% to 90%) of R/W1.                                                                                                                                   | WG, Pin 4    |     | 5.0  | 200 | ns   |

| 20 After WG goes low, fall time (10% to 90%) of R/W2.                                                                                                                                   | WG, Pin 4    | _   | 5.0  | 200 | ns   |

| 21 Setup time, Head Select going low before WG going low.                                                                                                                               | WG, Pin 4    | 4.0 | _    |     | μS   |

| 22 Write Data low Hold Time.                                                                                                                                                            | WD, Pin 5    | 200 |      | _   | ns   |

| 23 Write Data high Hold Time.                                                                                                                                                           | WD, Pin 5    | 500 |      |     | ns   |

| 24 Delay from WG going high through 2.0 V to R/W1 turning off through 10% of on value.                                                                                                  | WG, Pin 4    |     | 3.9  |     | μs   |

| 25 Delay from WG going low thru 0.8V<br>to Inhibit going low thru 0.5V (Note 5)                                                                                                         | WG, Pin 4    |     | 0.08 | 4.0 | μs   |

| 26 After WG goes high, delay from R/W1 turning off thru 10% to Inhibit going high thru 1.5V (10K pull-up on Inhibit, Note 5)                                                            | WG, Pin 4    | 20  | 750  |     | ns   |

| 27 After WG goes high, delay from E1 going high thru 23V to Inhibit going high thru 1.5V (10K pull-up on Inhibit, Note 5)  Note 2:—Test numbers refer to encircled numbers in Figure 3. | WG           | 20  | 750  |     | ns   |

Note 2:—Test numbers refer to encircled numbers in Figure 3.

Note 3:—AC test waveforms applied to the designated pins, see chart below.

Note 5:-26, or 27, whichever produces the longer delay, will control Inhibit.

| PIN        | fin     | AMPLITUDE    | DUTY CYCLE |

|------------|---------|--------------|------------|

| HS, Pin 13 | 50 KHz  | 0.4 to 2.4 V | 50%        |

| WG, Pin 4  | 50 KHz  | 0.4 to 2.4 V | 50%        |

| WD, Pin 5  | 1.0 MHz | 0.2 to 2.4 V | 50%        |

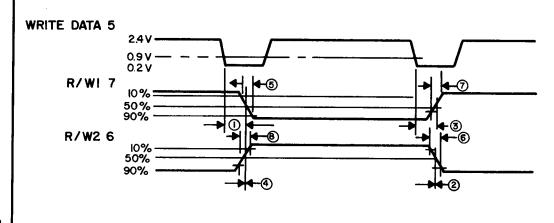

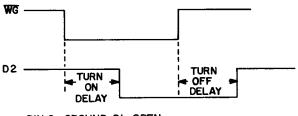

# AC SWITCHING CHARACTERISTICS (continued)

(V<sub>CC</sub>=5.0 V, T<sub>A</sub>=25°C, V<sub>BB</sub>=24 V, WG=0.4V unless otherwise noted---refer to Figure 2.)

| CHARACTERISTICS (NOTE 4)                                                                                            | MIN          | TYP | MAX | UNIT |

|---------------------------------------------------------------------------------------------------------------------|--------------|-----|-----|------|

| Delay from Write Data going low through 0.9 V to R/W1 turning on through 50%                                        | <del>-</del> | 85  | _   | ns   |

| Delay skew difference of R/W1 turning off and R/W2 turning on through 50% after Write Data going low through 0.9 V. | _            | 1.0 | ±40 | ns   |

| Delay from Write Data going low through 0.9 V to R/W1 turning off through 50%                                       | _            | 80  | _   | ns   |

| Delay skew, difference of R/W1 turning on and R/W2 turning off 50% after Write Data going low through 0.9 V.        | _            | 1.0 | ±40 | ns   |

| 5. Rise time, 10% to 90%, of R/W1                                                                                   | _            | 1.7 | 200 | ns   |

| 6. Rise time, 10% to 90%, of R/W2                                                                                   | _            | 1.7 | 200 | ns   |

| 7. Fall time, 90% to 10%, of R/W1                                                                                   |              | 12  | 200 | ns   |

| 8. Fall time, 90% to 10%, of R/W2                                                                                   | _            | 12  | 200 | ns_  |

Note 4: Test numbers refer to encircled numbers in Figure 2  $f_{\rm in}{=}\,1.0MHz.~50\%$  Duty Circle and Amplitude of 0.2 V to 2.4 V

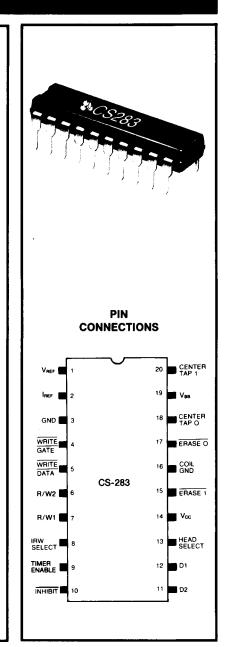

#### PIN DESCRIPTION TABLE

| NAME                                 | SYMBOL                               | PIN | DESCRIPTION                                                                                                                                                                                                                  |

|--------------------------------------|--------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Head Select                          | HS                                   | 13  | Head Select input selects between the head I/O pins center-tap, erase, and read write. A HIGH selects Head 0 and a LOW selects Head 1.                                                                                       |

| Write Gate                           | WG                                   | 4   | Write Gate input selects the mode of operation. HIGH selects the read mode, while LOW selects the Write Control mode and forces the write current.                                                                           |

| Write Data                           | WD                                   | 5   | Write Data input controls the turn on/off of the write current. The internal divide-by-two flip-flop toggles on the negative going edge of this input to direct the current alternately to the two halves of the head coils. |

| IRW Select                           | IRWS                                 | 8   | IRW Select input selects the amount of write current to be used. When LOW, the current equals the value according to the external resistor. When HIGH, the current equals the low current +33%.                              |

| V <sub>ref</sub><br>I <sub>ref</sub> | V <sub>ref</sub><br>I <sub>ref</sub> | 2   | A resistor between these pins sets the write current, on chip trimming reliably produces 3 mA of current for a 10 k resistor. A capacitor from V <sub>ref</sub> to Gnd will adjust the Degauss period.                       |

| Center-tap O                         | сто                                  | 18  | Center-tap O output is connected to the center tap of Head O. It will be pulled to Gnd or V <sub>BB</sub> (+12 or +24) depending on mode and head selection.                                                                 |

| Erase O                              | EO                                   | 17  | Erase O will be LOW for writing on Head O, and floating for other conditions.                                                                                                                                                |

| Center-tap 1                         | CT1                                  | 20  | Center-tap 1 output is connected to the center tap of Head 1. It will be pulled to Gnd or V <sub>BB</sub> (+12 or +24) depending on mode and head selection.                                                                 |

| Erase 1                              | E1                                   | 15  | Erase 1 will be LOW for writing on Head 1, and floating for other conditions.                                                                                                                                                |

| R/W2                                 | R/W2                                 | 6   | R/W2 input is one of the differential inputs that sinks current during writing, being the opposite phase of R/W1. It will be connected to one side of the heads.                                                             |

| R/W1                                 | R/W1                                 | 7   | R/W1 input is one of the differential inputs that sinks current during writing, being the opposite phase of R/W2. It will be connected to one side of the heads.                                                             |

|                                      | Vcc                                  | 14  | +5 V Power                                                                                                                                                                                                                   |

|                                      | V <sub>BB</sub>                      | 19  | +12 V or +24 V Power                                                                                                                                                                                                         |

|                                      | Gnd                                  | 16  | Coil grounds                                                                                                                                                                                                                 |

|                                      | Gnd                                  | 3   | Reference and logic ground.                                                                                                                                                                                                  |

| DELAY 1                              | D1                                   | 12  | Erase turn on delay adjust (RC or Logic).                                                                                                                                                                                    |

| DELAY 2                              | D2                                   | 11  | Erase turn of delay adjust (RC or Logic).                                                                                                                                                                                    |

| INHIBIT                              | INHIBIT                              | 10  | Active low open collector output provided to indicate heads are active in the write, Degauss or erase mode. (Used for step or read Inhibit.)                                                                                 |

| TIMER<br>ENABLE                      | ENABLE                               | 9   | When left open, the erase delays are controlled by D1 and D2. When this pin is gounded, the erase delays are controlled by D2 only. (Microprocessor compatible)                                                              |

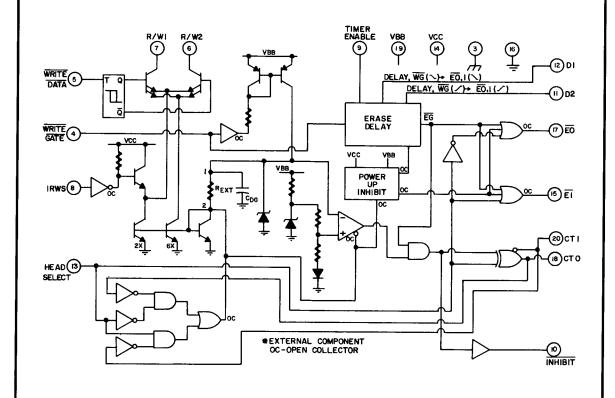

FIGURE 1—LOGIC DIAGRAM

# FIGURE 2—R W1 AND R W2 RELATIONSHIP

# FIGURE 4—DIGITAL CONTROL OF ERASE DELAYS

OPTION I: SINGLE PIN CONTROL OF ERASE DELAYS VIA MICROPROCESSOR

PIN 9 = GROUND, DI = OPEN

OPTION 2: DUAL PIN CONTROL OF ERASE DELAYS VIA MICROPROCESSOR

# FIGURE 5—TYPICAL APPLICATION

2000 South County Trail, East Greenwich, Rhode Island 02818 Tel: (401)885-3600 Telex WUI 6817157 Our Sales Representative in Your Area is: