## Sync separation circuit for video applications

## **TDA4820T**

### **FEATURES**

- Fully integrated, few external components

- Positive video input signal, capacitively coupled

- Operates with non-standard video input signals

- Black level clamping

- Generation of composite sync slicing level at 50% of peak sync voltage

- Vertical sync separator with double slope integrator

- Delay time of the vertical output pulse is determined by an external resistor

- Vertical sync generation with a slicing level at 40% of peak sync voltage

- Output stage for composite sync

- Output stage for vertical sync

#### **GENERAL DESCRIPTION**

The TDA4820T is a monolithic integrated circuit including a horizontal and a vertical sync separator, offering composite sync and vertical sync extracted from the video signal.

### QUICK REFERENCE DATA

| SYMBOL                 | PARAMETER                                                                | CONDITIONS              | MIN. | TYP. | MAX. | UNIT |

|------------------------|--------------------------------------------------------------------------|-------------------------|------|------|------|------|

| V <sub>P</sub>         | supply voltage<br>range (pin 1)                                          |                         | 10.8 | 12   | 13.2 | ٧    |

| l <sub>P</sub>         | supply current<br>(pin 1)                                                |                         | -    | 8    | 12   | mA   |

| V <sub>2(p-p)</sub>    | input voltage<br>amplitude<br>(peak-to-peak value)                       |                         | 0.2  | 1    | 3    | ٧    |

| V <sub>sync(p-p)</sub> | sync pulse input<br>voltage amplitude<br>(pin 2)<br>(peak-to-peak value) |                         | 50   | 300  | 500  | mV   |

| V <sub>o</sub>         | maximum vertical sync output voltage (pin 6)                             | l <sub>6</sub> = -1 mA  | 10.0 | -    | -    | V    |

| V <sub>o</sub>         | maximum composite<br>sync output voltage<br>(pin 7)                      | I <sub>7</sub> = -3 mA  | 10.0 | -    | _    | V    |

| V <sub>o</sub>         | minimum output<br>voltage<br>(pins 6 and 7)                              | l <sub>6,7</sub> = 1 mA | -    | -    | 0.6  | ٧    |

| Tamb                   | operating ambient temperature range                                      |                         | 0    | -    | + 70 | °C   |

## ORDERING AND PACKAGE INFORMATION

| EXTENDED    | PACKAGE |              |          |             |  |

|-------------|---------|--------------|----------|-------------|--|

| TYPE NUMBER | PINS    | PIN POSITION | MATERIAL | CODE        |  |

| TDA4820T    | 8       | mini-pack    | plastic  | SO8; SOT96A |  |

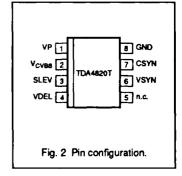

## PINNING

| SYMBOL            | PIN | DESCRIPTION                     |

|-------------------|-----|---------------------------------|

| V <sub>P</sub>    | 1   | supply voltage                  |

| V <sub>CVBS</sub> | 2   | video input signal              |

| SLEV              | 3   | slicing level                   |

| VDEL              | 4   | vertical integration delay time |

| n.c.              | 5   | not connected                   |

| VSYN              | 6   | vertical sync output signal     |

| CSYN              | 7   | composite sync output signal    |

| GND               | 8   | ground                          |

## PIN CONFIGURATION

## Sync separation circuit for video applications

#### **FUNCTIONAL DESCRIPTION**

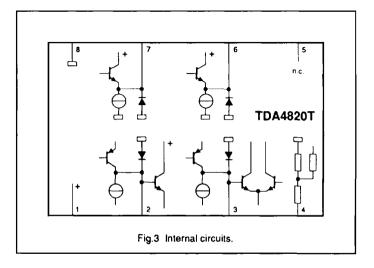

The complete circuit consists of the following functional blocks as shown in Fig. 1:

- Video amplifier and black level clamping

- 50% peak sync voltage

- Composite sync slicing

- Vertical slicing and double slope integrator

- Vertical sync output

- Composite sync output

# Video amplifier and black level clamping (pin 2)

The sync separation circuit TDA4820T is designed for positive video input signals.

The video signal (supplied via capacitor C2 at pin 2) is amplified by approximately 15 in the input amplifier. The black level clamping voltage (approximately 2 V) is stored by capacitor C2.

## 50% peak sync voltage (pin 3)

From the black level and the peak sync voltage, the 50% value of the peak sync voltage is generated and stored by capacitor C3 at pin 3. A slicing level control circuit ensures a constant 50% value, as long as the sync pulse amplitude at pin 2 is between 50 mV and 500 mV, independent of the amplitude of the picture content.

### Composite sync slicing

A comparator in the composite sync slicing stage compares the amplified video signal with the DC voltage derived from 50% peak sync voltage. This generates the composite sync output signal.

## Vertical slicing and double slope integrator

Vertical slicing compares the composite sync signal with a DC level equal to 40 % of the peak sync

voltage, similar to the composite sync slicing.

With signal interference (reflections or noise) the reduced vertical slicing level ensures more energy for the vertical pulse integration. The slope is double-integrated to eliminate the influence of signal interference.

The vertical integration delay time t<sub>dV</sub> can be set from typically 45 µs (pin 4 open) to typically 18 µs (pin 4 grounded). Between these maximum

and minimum values,  $t_{dV}$  can be set by a resistor R1 from pin 4 to ground. For optimum sync behaviour with input line sync pulses only, R1 has to be  $\geq 3.3~\text{k}\Omega$ . In this case  $t_{dV}$  is typically  $\geq 23~\mu\text{s}$ .

# Vertical sync output Composite sync output

Both output stages are emitter followers with bias currents of 2 mA.

### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL           | PARAMETER                           | MIN. | MAX.  | UNIT |

|------------------|-------------------------------------|------|-------|------|

| V <sub>P</sub>   | supply voltage (pin 1)              | 0    | 13.2  | V    |

| Vi               | input voltage (pin 2)               | -0.5 | 6     | v    |

| l <sub>o</sub>   | output current (pin 6 and pin 7)    | 3    | -10   | mA   |

| T <sub>stg</sub> | storage temperature range           | -25  | + 150 | ဇ    |

| Tamb             | operating ambient temperature range | 0    | + 70  | °C   |

| Tj               | maximum junction temperature        | -    | 150   | ℃    |

| P <sub>tot</sub> | total power dissipation             | -    | 500   | mW   |

CHARACTERISTICS

All voltages measured to GND (pin 8);  $V_P = 12 \text{ V}$ ;  $T_{amb} = 25 \,^{\circ}\text{C}$ ; unless otherwise specified.

| SYMBOL                  | PARAMETER                                            | CONDITIONS                                                                                   | MIN. | TYP. | MAX.     | UNIT        |

|-------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|----------|-------------|

| V <sub>P</sub>          | supply voltage range (pin 1)                         |                                                                                              | 10.8 | 12.0 | 13.2     | V           |

| lp                      | supply current (pin 1)                               |                                                                                              | 4    | 8    | 12       | mA          |

| Video amp               | lifler                                               |                                                                                              |      |      |          | <del></del> |

| V <sub>2(p-p)</sub>     | input amplitude<br>(peak-to-peak value)              | positive video signal<br>AC coupled                                                          | 0.2  | 1    | 3        | ٧           |

| V <sub>sync (p-p)</sub> | sync pulse amplitude (pin 2)<br>(peak-to-peak value) | composite sync slicing level 50% for $0.2 \text{ V} \le \text{V}_{2(p-p)} \le 1.5 \text{ V}$ | 50   | 300  | 500      | m∨          |

| Z <sub>s</sub>          | source impedance                                     |                                                                                              | -    | -    | 200      | Ω           |

| Black level             | l clamping                                           |                                                                                              |      |      |          |             |

| l <sub>2</sub>          | discharge current of C2                              | during video content                                                                         | -    | 5    | _        | μА          |

|                         | charge currents of C2                                | sync below slicing level                                                                     | -    | -40  | _        | μА          |

|                         |                                                      | sync above slicing level                                                                     | _    | -25  | -        | μА          |

|                         |                                                      | during black level                                                                           | -    | -20  | -        | μА          |

| 50% peak                | sync voltage                                         |                                                                                              |      |      |          |             |

| l <sub>3</sub>          | discharge current of C3                              | during video content                                                                         | _    | 16   | -        | μА          |

|                         | maximum charge current of C3                         |                                                                                              | -    | -345 | _        | μА          |

|                         | reduced charge current of C3                         | during vertical sync                                                                         |      | -255 | _        | μА          |

|                         | charge current of C3                                 | during sync pulse                                                                            |      | -160 | _        | μА          |

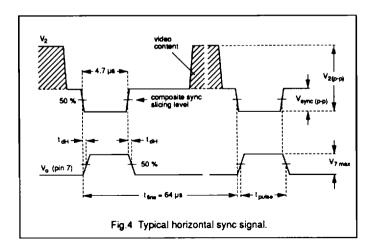

| Composite               | sync slicing (see Fig.4)                             |                                                                                              |      |      | <u> </u> |             |

|                         | composite sync slicing level                         | $0.2 \text{ V} \le \text{V}_{2(p \cdot p)} \le 1.5 \text{ V}$                                | -    | 50   | -        | %           |

| чн                      | horizontal delay time (pin 7)                        | maximum load at pin 7:<br>$C_L \le 5$ pF; $R_L \ge 100$ kΩ                                   | -    | 250  | 500      | ns          |

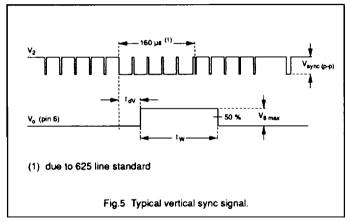

| Vertical sy             | nc separation (see Fig.5)                            |                                                                                              |      |      |          |             |

|                         | slicing level for vertical sync                      | 0.2 V ≤ V <sub>2(p-p)</sub> ≤ 1.5 V                                                          | -    | 40   | -        | %           |

| t₀v                     | vertical leading edge delay times                    | pin 4 open                                                                                   | 30   | 45   | 60       | μs          |

|                         | (pin 6)                                              | pin 4 grounded                                                                               | 11   | 18   | 25       | μs          |

| Vertical an             | d composite sync outputs                             | <u> </u>                                                                                     |      |      |          |             |

| V <sub>o</sub>          | maximum vertical sync<br>output voltage (pin 6)      | I <sub>6</sub> = -1 mA                                                                       | 10.0 | 10.5 | 11.5     | ٧           |

| V <sub>o</sub>          | maximum composite sync output voltage (pin 7)        | I <sub>7</sub> = -3 mA                                                                       | 10.0 | 10.5 | 11.5     | V           |

| V <sub>o</sub>          | minimum output voltages (pins 6 and 7)               | l <sub>6,7</sub> = 1 mA                                                                      | 0.1  | 0.3  | 0.6      | ٧           |

| tw                      | vertical sync pulse width                            | pin 4 open; standard<br>signal of 625 lines                                                  | -    | 180  | -        | μs          |