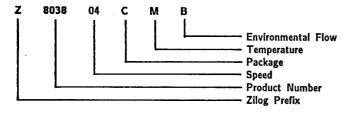

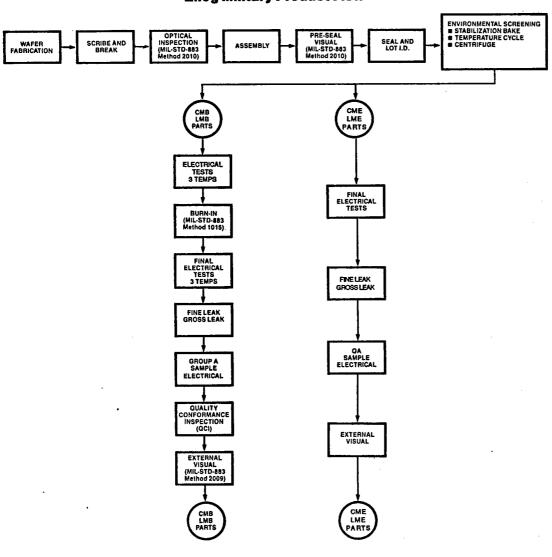

### Z8038/Z8538 Military FIO FIFO Input/ Output Interface Unit

### Features

- 128-byte FIFO buffer provides asynchronous bidirectional CPU/CPU or CPU/peripheral interface, expandable to any width in byte increments by use of multiple FIOs.

- Interlocked 2-Wire or 3-Wire Handshake logic port mode; Z-BUS® or non-Z-BUS interface.

- Pattern-recognition logic stops DMA transfers and/or interrupts CPU; preset byte count can initiate variable-length DMA transfers.

- Seven sources of vectored/nonvectored interrupt which include pattern-match, byte count, empty or full buffer status; a dedicated "mailbox" register with interrupt capability provides CPU/CPU communication.

- REQUEST/WAIT lines control high-speed data transfers.

- All functions are software controlled via directly addressable read/write registers.

### General Description

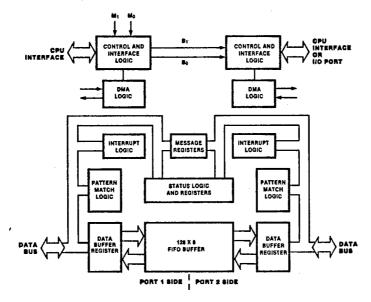

The Z8038/Z8538 FIO provides an asynchronous 128-byte FIFO buffer between two CPUs or between a CPU and a peripheral device. This buffer interface expands to a 16-bit or wider data path and expands in depth to add as many Z8060 FIFOs (and an additional FIO) as are needed.

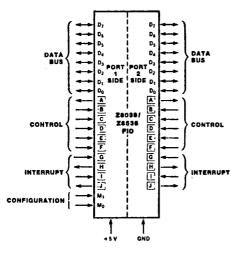

The FIO manages data transfers by assuming Z-BUS, non-Z-BUS microprocessor (a generalized microprocessor interface), Interlocked 2-Wire

Handshake, and 3-Wire Handshake operating modes. These modes interface dissimilar CPUs or CPUs and peripherals running under differing speeds or protocols, allowing asynchronous data transactions and improving I/O overhead by as much as two orders of magnitude. Figures 1 and 2 show how the signals controlling these operating modes are mapped to the FIO pins.

Figure 1. Pin Functions

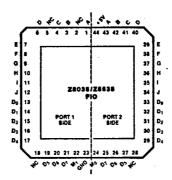

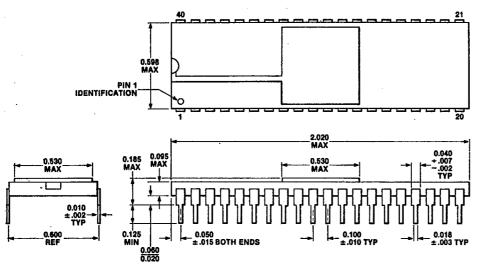

Figure 2a. 40-pin Dual-In-Line Package (DIP), Pin Assignments

General Description (Continued) The FIO supports the Z-BUS interrupt protocols, generating seven sources of interrupts upon any of the following events: a write to a message register, change in data direction, pattern match, status match, over/underflow error, buffer full and buffer empty status. Each interrupt source can be enabled or disabled, and can also place an interrupt vector on the port address/data lines.

The data transfer logic of the FIO has been

specially designed to work with DMA (Direct Memory Access) devices for high-speed transfers. It provides for data transfers to or from memory each machine cycle, while the DMA device generates memory address and control signals. The FIO also supports the variably sized block length, improving system throughput when multiple variable length messages are transferred amongst several sources.

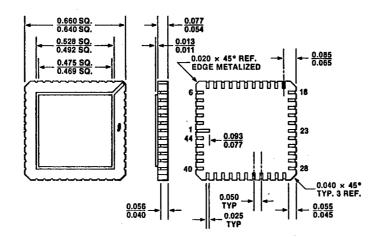

Figure 2b. 44-pin Chip Carrier, Pin Assignments

Figure 3. FIO Block Diagram

### Functional Description

Operating Modes. Ports 1 and 2 operate in any of twelve combinations of operating modes, listed in Table 2. Port 1 functions in either the Z-BUS or non-Z-BUS microprocessor modes, while Port 2 functions in Z-BUS, non-Z-BUS, Interlocked 2-Wire Handshake, and 3-Wire Handshake modes. Table 1 describes the signals and their corresponding pins in each of these modes.

The pin diagrams of the FIO are identical, except for two pins on the Port 1 side, which select that port's operating mode. Port 2's operating mode is programmed by two bits in Port 1's Control register 0. Table 2 describes the combinations of operating modes; Table 3 describes the control signals mapped to pins A-J in the five possible operating modes.

| Signal<br>Pins | Z-BUS<br>Low Byte | Z-BUS<br>High Byte        | Non-Z-BUS   | Interlocked<br>HS Port* | 3-Wire<br>HS Port* |

|----------------|-------------------|---------------------------|-------------|-------------------------|--------------------|

| A              | REQ/WT            | REQ/WT                    | REQ/WT      | RFD/DAV                 | RFD/DAV            |

| 13             | DMASTB            | DMASTB                    | DACK        | ACKIN                   | DAV/DAC            |

| C              | DS                | DS                        | RD          | FULL                    | DAC/RFD            |

| D              | R∕₩               | R/₩                       | <b>WR</b> ⊦ | EMPTY                   | EMPTY              |

| E              | CS                | <del>CS</del>             | CE          | CLEAR                   | CLEAR              |

| F              | ĀS                | AS                        | C/D         | DATĂ DIR                | DATA DÌR           |

| G              | INTACK            | A <sub>0</sub>            | INTACK      | INO                     | IN <sub>0</sub>    |

| H              | IEO               | $\mathbf{A}_{\mathbf{l}}$ | IEO         | OUT1                    | OUT                |

| 1              | IEI               | A <sub>2</sub>            | IEI         | ŌĒ                      | ÕĒ                 |

| 1              | ĪNT               | A <sub>3</sub>            | INT         | OUT3                    | OUT3               |

<sup>\*2</sup> side only.

Table 1. Pin Assignments

| Mode | $M_1$ | Mo | <b>B</b> 1 | B <sub>0</sub> | Port 1          | Port 2           |

|------|-------|----|------------|----------------|-----------------|------------------|

| 0    | 0     | 0  | 0          | 0              | Z-BUS Low Byte  | Z-BUS Low Byte   |

| 1    | 0 -   | 0  | 0          | 1              | Z-BUS Low Byte  | Non-Z-BUS        |

| 2    | 0     | 0  | 1          | 0              | Z-BUS Low Byte  | 3-Wire Handshake |

| 3    | 0     | 0  | 1          | 1              | Z-BUS Low Byte  | 2-Wire Handshake |

| 4    | 0     | 1  | 0          | 0              | Z-BUS High Byte | Z-BUS High Byte  |

| 5    | 0     | 1  | 0          | 1              | Z-BUS High Byte | Non-Z-BUS        |

| 6    | 0     | 1  | 1          | 0              | Z-BUS High Byte | 3-Wire Handshake |

| 7    | 0     | 1  | 1          | 1              | Z-BUS High Byte | 2-Wire Handshake |

| 8    | 1     | 0  | 0          | 0              | Non-Z-BUS       | Z-BUS Low Byte   |

| 9    | 1     | 0  | 0          | 1.             | Non-Z-BUS       | Non-Z-BUS        |

| 10   | 1     | 0  | 1          | 0              | Non-Z-BUS       | 3-Wire Handshake |

| 11   | 1     | 0  | 1          | 1              | Non-Z-BUS       | 2-Wire Handshake |

Table 2. Operating Modes

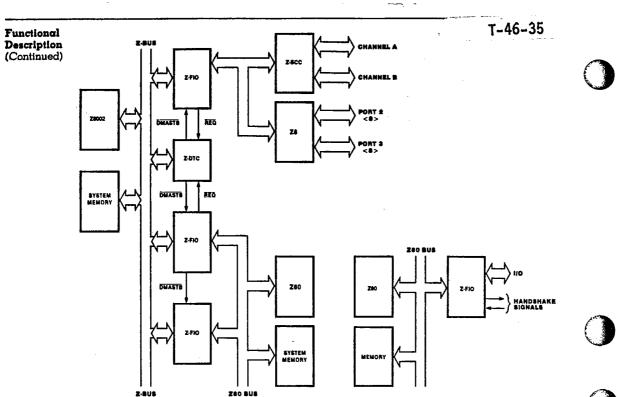

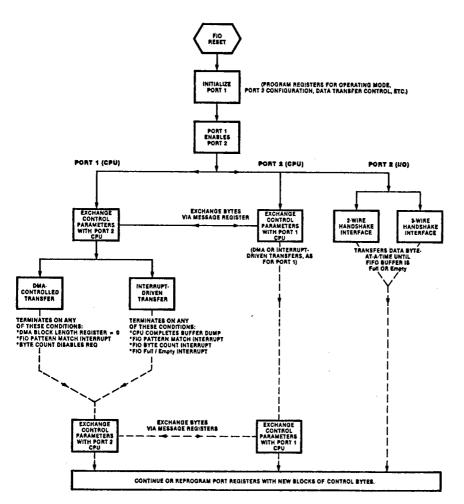

Figure 4. CPU to CPU Configuration

Figure 5. CPU to 1/O Configuration

|                              |                                                    |                                |             |                    | T-46-35                                                                                                                               |

|------------------------------|----------------------------------------------------|--------------------------------|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Pins Common<br>To Both Sides | Pin<br>Signals                                     | Pin<br>Names                   |             | in<br>nbers        | Signal<br>Description                                                                                                                 |

|                              | M <sub>0</sub>                                     | Mo                             |             | 21                 | M1 and M0 program Port 1                                                                                                              |

|                              | M <sub>l</sub><br>+5 Vdc                           | M <sub>l</sub><br>+5 Vdc       |             | 19<br>10           | side CPU interface                                                                                                                    |

|                              | GND                                                | GND                            |             | 40<br>20           | DC power ground                                                                                                                       |

| <del></del>                  |                                                    |                                | ·····       |                    | DC power ground                                                                                                                       |

| Z-BUS<br>Low Byte<br>Mode    | Pin<br>Signals                                     | Pin<br>Names                   |             | umbers<br>ort<br>2 | Signal<br>Description                                                                                                                 |

| Z8038                        | AD <sub>0</sub> -AD <sub>7</sub><br>(Address/Data) | D <sub>0</sub> -D <sub>7</sub> | 11-18       | 29-22              | Multiplexed bidirectional address/data lines, Z-BUS compatible.                                                                       |

|                              | REQ/WAIT<br>(Request/Wait)                         | A                              | 1           | 39                 | Output, active Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfers. |

|                              | DMASTB<br>(Direct Memory<br>Access Strobe)         | В                              | 2           | 38                 | Input, active Low. Strobes DMA data to and from the FIFO buffer.                                                                      |

|                              | DS<br>(Data Strobe)                                | С                              | 3           | 37                 | Input, active Low. Provides timing for data transfer to or from FIO.                                                                  |

|                              | R/W<br>(Read/Write)                                | D                              | 4           | 36                 | Input; active High signals CPU read from FIO; active Low signals CPU write to FIO.                                                    |

|                              | CS<br>(Chip Select)                                | E                              | 5           | 35                 | Input, active $L_{\underline{ow}}$ . Enables FiO. Latched on the rising edge of $\overline{AS}$ .                                     |

|                              | AS<br>(Address Strobe)                             | F                              | 6           | 34                 | Input, active Low. Addresses, CS and INTACK sampled while AS Low.                                                                     |

|                              | INTACK<br>(Interrupt<br>Acknowledge)               | G                              | 7           | 33                 | Input, active Low. Acknowledges an interrupt.<br>Latched on the rising edge of AS.                                                    |

|                              | IEO<br>(Interrupt<br>Enable Out)                   | н                              | 8           | 32                 | Output, active High. Sends interrupt enable to lower priority device IEI pin.                                                         |

|                              | IEI<br>(Interrupt<br>Enable In)                    | I                              | 9           | 31                 | Input, active High. Receives interrupt enable from higher priority device IEO signal.                                                 |

| ·                            | INT<br>(Interrupt)                                 | J                              | 10          | 30                 | Output, open drain, active Low. Signals FIO interrupt request to CPU.                                                                 |

| -BUS                         |                                                    |                                | Pin Nu      | mbers              |                                                                                                                                       |

| iigh Byte<br>Vode            | Pin<br>Signals                                     | Pin<br>Names                   | Port<br>1 2 |                    | Signal<br>Description                                                                                                                 |

| 28038                        | AD <sub>0</sub> -AD <sub>7</sub><br>(Address/Data) | D <sub>0</sub> -D <sub>7</sub> | 11-18       | 29-22              | Multiplexed bidirectional address/data lines, Z-BUS compatible.                                                                       |

|                              | REQ/WAIT<br>(Request/Wait)                         | A                              | 1           | 39                 | Output, active Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfers. |

|                              | DMASTB<br>(Direct Memory<br>Access Strobe)         | В                              | 2           | 38                 | Input, active Low. Strobes DMA data to and from the FIFO buffer.                                                                      |

|                              | DS<br>(Data Strobe)                                | С                              | 3           | 37                 | Input, active Low. Provides timing for transfer of data to or from FIO.                                                               |

|                              | R/W<br>(Read/Write)                                | D                              | 4           | 36                 | Input, active High. Signals CPU read from FIO; active Low signals CPU write to FIO.                                                   |

|                              | CS<br>(Chip Select)                                | E                              | 5           | 35                 | Input, active $L_{\underline{ow}}$ . Enables FIO. Latched on the rising edge of $\overline{AS}$ .                                     |

|                              | AS<br>(Address Strobe)                             | F                              | 6           | 34                 | Input, active Low. Addresses, CS and INTACK are sampled while AS is Low.                                                              |

|                              | A <sub>0</sub><br>(Address Bit 0)                  | G<br>                          | 7           | 33                 | Input, active High. With $A_1$ , $A_2$ , and $A_3$ , addresses FIO internal registers.                                                |

|                              | A <sub>1</sub><br>(Address Bit 1)                  | H                              | 8           | 32                 | Input, active High. With A <sub>0</sub> , A <sub>2</sub> , and A <sub>3</sub> , addresses FIO internal registers.                     |

|                              | A <sub>2</sub><br>(Address Bit 2)                  | I                              | 9           | 31                 | Input, active High. With A <sub>0</sub> , A <sub>1</sub> , and A <sub>3</sub> , addresses FIO internal registers.                     |

| _                            | A <sub>3</sub><br>(Address Bit 3)                  | J                              | 10          | 30                 | Input, active High. With $A_0$ , $A_1$ , and $A_2$ , addresses FIO internal registers.                                                |

Table 3. Signal/Pin Descriptions

### 9984043 0013711 6 📰 17E D

35

| Non-Z-BUS               | Di-                                           | Pin                            | Pin Nu<br>Po  |              | •                                   | T-46-3                                                                                                                                                                                            |

|-------------------------|-----------------------------------------------|--------------------------------|---------------|--------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode                    | Pin<br>Signals                                | Names                          | 1             | " 4          |                                     | Description                                                                                                                                                                                       |

| <b>Z</b> 8538           | D <sub>0</sub> -D <sub>7</sub><br>(Data)      | D <sub>0</sub> -D <sub>7</sub> | 11-18         | 29-22        |                                     | Bidirectional data bus.                                                                                                                                                                           |

|                         | REQ/WT<br>(Request/Wait)                      | A                              | 1             | 39           |                                     | Output, active Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfer.                                                              |

|                         | DACK<br>(DMA Acknowledge)                     | В                              | 2             | 38           |                                     | Input, active Low, DMA acknowledge.                                                                                                                                                               |

|                         | RD<br>(Read)                                  | С                              | 3             | 37           |                                     | Input, active Low. Signals CPU read from FIO.                                                                                                                                                     |

|                         | WR<br>(Write)                                 | D                              | 4             | · <b>3</b> 6 |                                     | Input, active Low. Signals CPU write to FIO.                                                                                                                                                      |

|                         | CE<br>(Chip Select)                           | E                              | 5             | <b>3</b> 5   |                                     | Input, active Low. Used to select FIO,                                                                                                                                                            |

|                         | C/D<br>(Control/Data)                         | F                              | 6             | 34           |                                     | Input, active High. Identifies control byte on D <sub>0</sub> -D <sub>7</sub> ; active Low identifies data byte on D <sub>0</sub> -D <sub>7</sub> .                                               |

|                         | ÏNTACK<br>(Interrupt<br>Acknowledge)          | G                              | 7             | <b>3</b> 3   |                                     | Input, active Low. Acknowledges an interrupt.                                                                                                                                                     |

|                         | IEO<br>(Interrupt<br>Enable Out)              | Н                              | 8             | 32           |                                     | Output, active High. Sends interrupt enable to lower priority device IEI pin.                                                                                                                     |

|                         | IEI<br>(Interrupt<br>Enable In)               | 1                              | 9             | 31           |                                     | Input, active High. Receives interrupt enable from higher priority device IEO signal.                                                                                                             |

|                         | INT<br>(Interrupt)                            | 1                              | 10            | 30           |                                     | Output, open drain, active Low. Signals FIO interrupt to CPU.                                                                                                                                     |

| Port 2-I/O<br>Port Mode | Pin<br>Signals                                | Pin<br>Names                   | Pin<br>Number | ,            | Mode                                | Signal<br>Description                                                                                                                                                                             |

|                         | D <sub>0</sub> -D <sub>7</sub><br>(Date)      | D <sub>0</sub> -D <sub>7</sub> | 29-22         | ·            | 2-Wire HS*<br>3-Wire HS             | Bidirectional data bus.                                                                                                                                                                           |

|                         | RFD/DAV<br>(Ready for Data/Data<br>Available) | Ā                              | 39            |              | 2-Wire HS<br>3-Wire HS              | Output, RFD active High. Signals peripherals that FIG is ready to receive data. DAV active Low signals that FIO is ready to send data to peripherals.                                             |

|                         | ACKIN<br>(Acknowledge Input)                  | В                              | 38            |              | 2-Wire HS                           | Input, active Low. Signals FIO that output data is received by peripherals or that input data is valid.                                                                                           |

|                         | DAV/DAC<br>(Data Available/Data<br>Accepted)  | В                              | 38            |              | 3-Wire HS                           | Input; DAV (active Low) signals that data is valid on bus. DAC (active High) signals that output data is accepted by peripherals.                                                                 |

|                         | FULL                                          | С                              | 37            |              | 2-Wire HS                           | Output, open drain, active High. Signals that FIO buffer is full.                                                                                                                                 |

|                         | DAC/RFD<br>(Data Accepted/Read<br>for Data)   | C                              | 37            |              | 3-Wire HS                           | Direction controlled by internal programming. Both active High. DAC (an output) signals that FIO has received data from peripheral; RFD (an input) signals that the listeners are ready for data. |

|                         | EMPTY                                         | D                              | 36            |              | 2-Wire HS<br>3-Wire HS              | Output, open drain, active High. Signals that FIFO buffer is empty.                                                                                                                               |

|                         | CLEAR                                         | E                              | 35            |              | 2-Wire HS<br>3-Wire HS              | Programmable input or output, active Low. Clears all data from FIFO buffer.                                                                                                                       |

|                         |                                               |                                |               |              | 2-Wire HS                           | Programmable input or output. Active High signals                                                                                                                                                 |

|                         | DATA DIR<br>(Data Direction)                  | F                              | 34            |              | 3-Wire HS                           | data input to Port 2; Low signals data output from Port 2.                                                                                                                                        |

|                         |                                               | F<br>G                         | 34            |              | 2-Wire HS<br>3-Wire HS              |                                                                                                                                                                                                   |

|                         | (Data Direction)                              |                                |               |              | 2-Wire HS                           | Port 2.                                                                                                                                                                                           |

|                         | (Data Direction) IN <sub>0</sub>              | G                              | 33            |              | 2-Wire HS<br>3-Wire HS<br>2-Wire HS | Port 2.  Input line to D <sub>0</sub> of Control Register 3.                                                                                                                                      |

\*Handshake

OUT<sub>3</sub>

Table 3. Signal/Pin Descriptions (Continued)

Output line from  $D_3$  of Control register 3.

2-Wire HS 3-Wire HS

30

Reset

The FIO can be reset under either hardware or software control by one of the following methods:

- By forcing both  $\overline{AS}$  and  $\overline{DS}$  Low simultaneously in Z-BUS mode (normally illegal).

- By forcing RD and WR Low simultaneously in non-Z-BUS mode.

- By writing a 1 to the Reset bit in Control register 0 for software reset.

In the Reset state, all control bits are cleared to 0. Only after clearing the Reset bit (by

writing a 0 to it) can the other command bits be programmed. This action is true for both sides of the FIO when programmed as a CPU interface.

For proper system control, when Port 1 is reset, Port 2 is also reset. In addition, all Port 2's outputs are floating and all inputs are ignored. To initiate the data transfer, Port 2 must be enabled by Port 1. The Port 2 CPU can determine when it is enabled by reading Control register 0, which reads "floating" data bus if not enabled and "01H" if enabled.

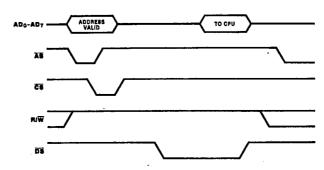

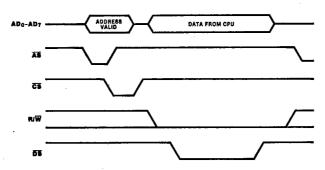

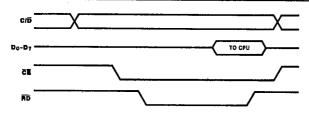

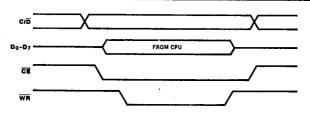

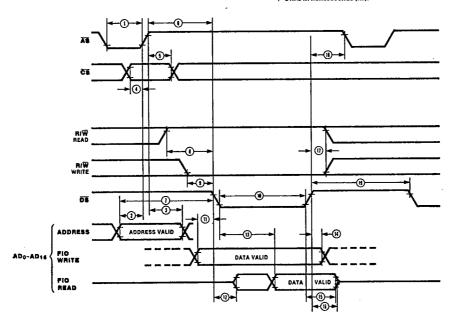

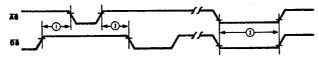

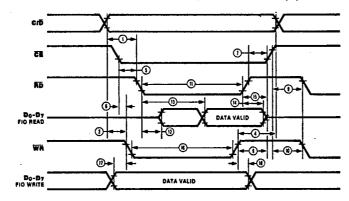

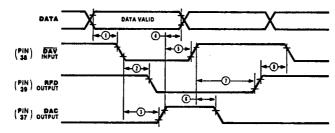

CPU Interfaces The FIO is designed to work with both Z-BUS- and non-Z-BUS-type CPUs on both Port 1 and Port 2. The Z-BUS configuration interfaces CPUs with time-multiplexed address and data information on the same pins. The Z8001°, Z8002°, and Z8° are examples of this type of CPU. The  $\overline{\rm AS}$  (Address Strobe) pin is used to latch the address and chip select information sent out by the CPU. The R/W (Read/Write) pin and the  $\overline{\rm DS}$  (Data Strobe) pin are used for timing reads and writes from the CPU to

the FIO (Figures 6 and 7).

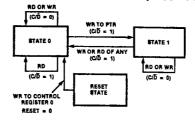

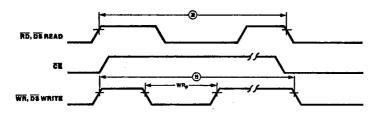

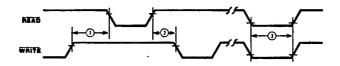

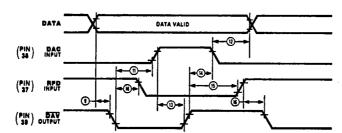

The non-Z-BUS configuration is used for CPUs where the address and data buses are separate. Examples of this type of CPU are the Z80° and the Intel 8080. The  $\overline{\text{RD}}$  (Read) and  $\overline{\text{WR}}$  (Write) pins are used to time reads and writes from the CPU to the FIO (Figures 9 and 10). The  $\overline{\text{C/D}}$  (Control/Data) pin is used to directly access the FIFO buffer ( $\overline{\text{C/D}}$  = 0) and to access the other

Figure 6. Z-BUS Read Cycle Timing

Figure 7. Z-BUS Write Cycle Timing

CPU Interfaces (Continued) registers ( $C/\overline{D}=1$ ). Read and write to all registers except the FIFO buffer I are two-step operations, described as follows (Figure 8). First, write the address ( $C/\overline{D}=1$ ) of the register to be accessed into the Pointer Register (State 0); second, read or write ( $C/\overline{D}=1$ ) to the register pointed at previously (State 1). Continuous status monitoring can be performed in State 1 by continuous Control Read operations ( $C/\overline{D}=1$ ).

The FIFO buffer can also be accessed by this two-step operation.

Figure 8. Register Access in Non-Z-BUS Mode

Figure 9. Non-Z-BUS Read Cycle Timing

Figure 10. Non-Z-BUS Write Cycle Timing

WAIT Operation

When data is output by the CPU, the REQ/WT (WAIT) pin is active (Low) only when the FIFO buffer is full, the chip is selected, and the FIFO buffer is addressed. WAIT goes inactive when the FIFO buffer is not full.

$\frac{\text{When }}{\text{REQ/WT}} \text{ pin becomes active (Low) only when the FIFO buffer is empty, the chip is selected, and the FIFO buffer is addressed. WAIT goes inactive when the FIFO buffer is not empty.}$

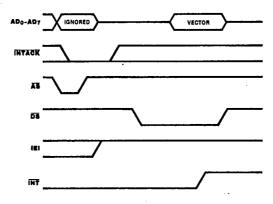

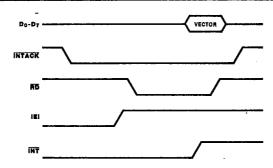

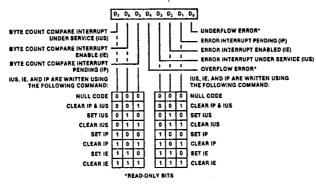

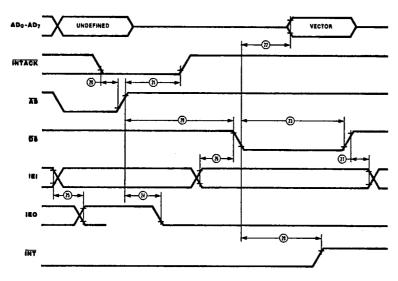

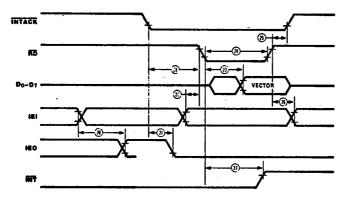

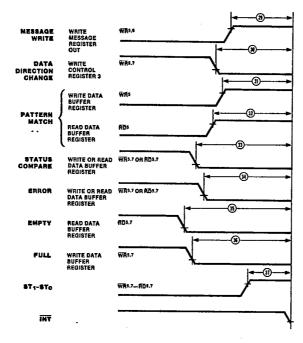

Interrupt Operation The FIO supports Zilog's prioritized daisy chain interrupt protocol for both Z-BUS and non-Z-BUS operating modes (for more details refer to the Zilog Z-BUS Summary).

Each side of the FIO has seven sources of interrupt. The priorities of these devices are fixed in the following order (highest to lowest): Mailbox Message, Change in Data Direction, Pattern Match, Status Match, Overflow/

Underflow Error, Buffer Full, and Buffer Empty. Each interrupt source has three bits that control how it generates the interrupt. These bits are Interrupt Pending (IP), Interrupt Enable (IE), and Interrupt Under Service (IUS).

In addition, each side of the FIO has an interrupt vector and four bits controlling the FIO interrupt logic. These bits are Vector

Interrupt Operation (Continued) Includes Status (VIS), Master Interrupt Enable (MIE), Disable Lower Chain (DLC), and No Vector (NV).

T-46-35

A typical Interrupt Acknowledge cycle for Z-BUS operation is shown in Figure 11 and for non-Z-BUS operation in Figure 12. The only difference is that in Z-BUS mode, INTACK is latched by AS, and in non-Z-BUS mode INTACK is not latched.

When MIE = 1, reading the vector always includes status, independent of the state of the VIS bit. In this way, when VIS = 0, all information can be obtained with one additional read, thus conserving vector space. When MIE = 0, reading the vector register returns the unmodified base vector so that it can be verified.

In non-Z-BUS mode, the IPs do not get set while in State 1. Therefore, to minimize interrupt latency, the FIO should be left in State 0. In Z-BUS mode IPs are set by an AS following the event.

Figure 11. Z-BUS Interrupt Acknowledge Cycle

Figure 12. Non-Z-BUS Interrupt Acknowledge Cycle

**CPU** to **CPU** Operation

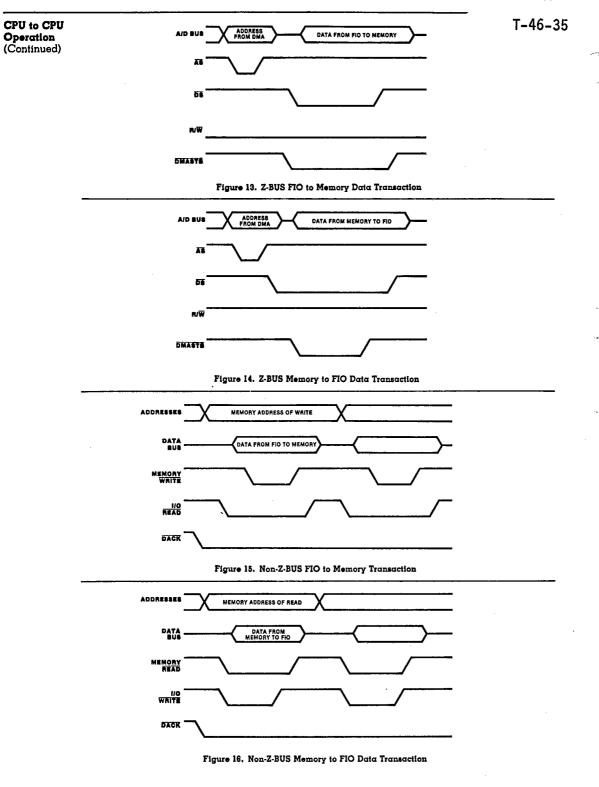

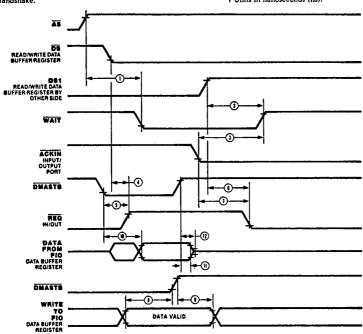

DMA Operation. The FIO is particularly well suited to work with a DMA in both Z-BUS and non-Z-BUS modes. A data transfer between the FIO and system memory can take place during every machine cycle on both sides of the FIO simultaneously.

In Z-BUS mode, the DMASTB pin (DMA Strobe) is used to read or write into the FIFO buffer. The R/W (Read/Write) and DS (Data Strobe) signals are ignored by the FIO;

however, the CS (Chip Select) signal is not ignored and therefore must be kept invalid. Figures 13 and 14 show typical timing.

In Non-Z-BUS mode, the DACK pin (DMA Acknowledge) is used to tell the FIO that its DMA request is granted. After DACK goes Low, every read or write to the FIO goes into the FIFO buffer. Figures 15 and 16 show typical timing.

**CPU** to **CPU** Operation (Continued)

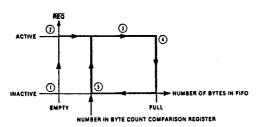

The FIO provides a special mode to enhance its DMA transfer capability, When data is written into the FIFO buffer, the REQ/WT (REQUEST) pin is active (Low) until the FIFO buffer is full. It then goes inactive and stays inactive until the number of bytes in the FIFO buffer is equal to the value programmed into the Byte Count Comparison register. Then the REQUEST signal goes active and the sequence starts over again (Figure 17).

- NOTES:

1. FIFO empty.

2. REQUEST enabled, FIO requests DMA transfer.

3. DMA transfers data into the FIO.

4. FIFO full, REQUEST inactive.

5. The FIFO empties from the opposite port until the number of bytes in the FIFO buffer is the same as the number programmed in the Byte Count Comparison register.

Figure 17. Byte Count Control: Write to FIO

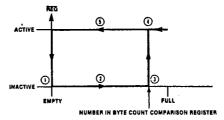

When data is read from the FIO, the REQ/WT pin (REQUEST) is inactive until the number of bytes in the FIFO buffer is equal to the value programmed in the Byte Count Comparison register. The REQUEST signal then goes active and stays active until the FIFO buffer is empty. When empty, REQUEST goes inactive and the sequence starts over again (Figure 18).

### NOTES:

- NOTES:

1. FIFO empty.

2. CPU/DMA fills FIFO buller from the opposite port.

3. Number of bytes in FIFO buller is the same as the number of bytes programmed in the Byte Count Comparison register.

4. REQUEST goes active.

5. DMA transfers data out of FIFO until it is empty.

Figure 18. Byte Count Control: Read from FIO

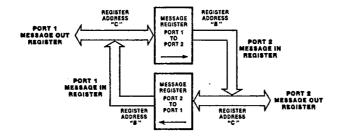

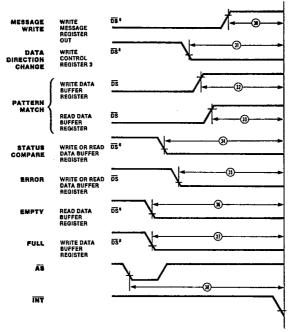

Message Registers. Two CPUs can communicate through a dedicated "mailbox" register without involving the 128 × 8 bit FIFO buffer (Figure 19). This mailbox approach is useful for transferring control parameters between the interfacing devices on either side of the FIO without using the FIFO buffer. For example, when Port 1's CPU writes to the Message Out register, Port 2's message IP is set. If interrupts are enabled, Port 2's CPU is

interrupted. Port 2's message IP status is readable from the Port 1 side. When Port 2's CPU reads the data from its Message In register, the Port 2 IP is cleared. Thus, Port 1's CPU can read when the message has been read and can now send another message or follow whatever protocol that is set up between the two CPU's. The same transfer can also be made from Port 2's CPU to Port 1's CPU.

NOTE: Usable only for CPU/CPU interface.

Figure 19. Message Register Operation

CPU to CPU

Operation

(Continued)

CLEAR (Empty) FIFO Operation. The CLEAR FIFO bit (active Low) clears the FIFO buffer of data. Writing a 0 to this bit empties the FIFO buffer, inactivates the REQUEST line, and disables the handshake (if programmed). The CLEAR bit does not affect any control or data register. To remove the CLEAR state, write a 1 to the CLEAR bit.

In CPU/CPU mode, under program control, only one of the ports can empty the FIFO by writing to its Control Register 3, bit 6. The Port 1 CPU must program bit 7 in Control Register 3 to determine which port controls the CLEAR FIFO operation (0 = Port 1 control; 1 = Port 2 control).

Direction of Data Transfer Operation. The

T-46-35

Data Direction bit controls the direction of data transfer in the FIFO buffer. The Data Direction bit is defined as 0 = output from CPU and 1 = input to CPU. This bit reads correctly when read by either port's CPU. For example, if Port 1's CPU reads a 0 (CPU output) in its Data Direction bit, then Port 2's CPU reads a 1 (input to CPU) in its Data Direction bit.

In CPU/CPU mode, under program control, only one of the ports can control the direction of data transfer. The Port 1 CPU must program bit 5 in Control Register 3 to determine which port controls the data direction (0 = Port 1 control; 1 = Port 2 control). Figure 20 shows FIO data transfer options.

Figure 20. FIO Data Transfer Options

CPU to I/O

Operation

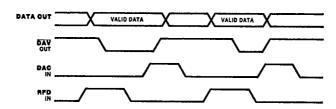

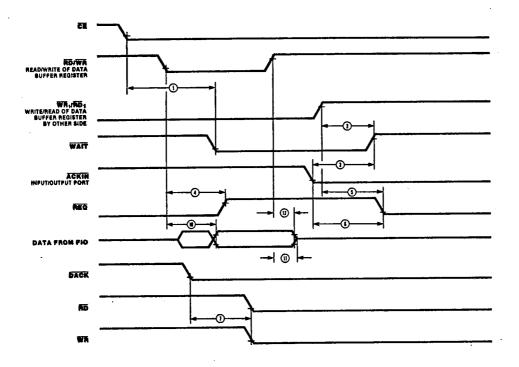

When Port 2 is programmed in the Interlocked 2-Wire Handshake mode or the 3-Wire Handshake mode, and Port A is programmed in Z-BUS or non-Z-BUS Microprocessor mode, the FIO interfaces a CPU and a peripheral device. In the Interlocked 2-Wire Handshake mode, RFD/DAV and ACKIN strobe data to and from Port 2. In the 3-Wire Handshake mode, RFD/DAV, DAV/DAC, and DAC/RFD signals control data flow.

17E D

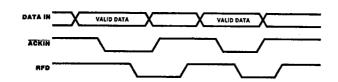

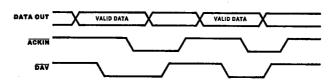

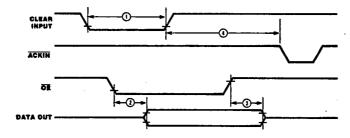

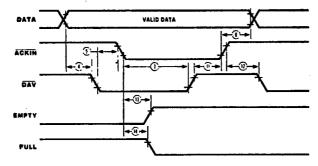

Interlocked 2-Wire Handshake. In the Interlocked Handshake, the action of the FIO must be acknowledged by the other half of the handshake before the next action can take place. In output mode, Port 2 does not indicate that new data is available until the external device indicates it is ready for the data. Similarly, in input mode, Port 2 does not indicate that it is ready for new data until the data source indicates that the previous byte of the data is no longer available, thereby acknowledging Port 2's acceptance of the last byte. This allows the FIO to directly interface to a Z8's port, a CIO's port, a UPC's port, another FIO port, or another FIFO Z8060, with no external logic (Figures 21 and 22).

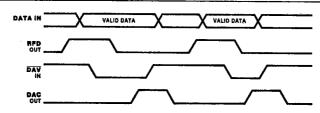

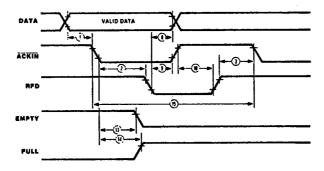

3-Wire Handshake. The 3-Wire Handshake is designed for applications in which one output port is communicating with many input ports simultaneously. It is essentially the same as the Interlocked Handshake, except that two signals are used to indicate that an input port is ready for new data or that it has accepted the present data. In the 3-Wire Handshake, the rising edge of the RFD status line indicates that the port is ready for data, and the rising edge of the DAC status line indicates that the data has been accepted. With 3-Wire Handshake, the lines of many input ports can be bussed together with open-drain drivers and the out-

put port knows when all of the ports are ready and have accepted the data. This handshake is the same handshake used in the IEEE-488 Instruments. Since the port's direction can be changed under software control, bidirectional IEEE-488-type transfers can be performed. Figures 23 and 24 show the timings associated with 3-Wire Handshake communications.

CLEAR FIFO Operation. In CPU-to-I/O operation, the CLEAR FIFO operation can be performed by the CPU side (Port 1) under software control as previously explained. The CLEAR FIFO operation can also be performed under hardware control by defining the CLEAR pin of Port 2 as an input (Control Register 3, bit 7 = 1).

For cascading purposes, the  $\overline{\text{CLEAR}}$  pin can also be defined as an output (Control Register 3, bit 7 = 0), which reflects the current state of the  $\overline{\text{CLEAR}}$  FIFO bit. It can then empty other FIOs or initialize other devices in the system.

Data Direction Control. In CPU-to-I/O mode, the direction of data transfer can be controlled by the CPU side (Port 1) under software control as previously explained. The data direction can also be determined by hardware control by defining the Data Direction pin of Port 2 as an input (Control Register 3, bit 5 = 1).

For cascading purposes, the Data Direction pin can also be defined as an output (Control Register 3, bit 5 = 0) pin which reflects the current state of the Data Direction bit. It can then be used to control the direction of data transfer for other FIOs or for external logic.

On the Port 2 side, when data direction is 0, Port 2 is in Output Handshake mode. When data direction is 1, Port 2 is in Input Handshake mode.

Figure 21. Interlocked Handshake Timing (Input) Port 2 Side Only

Figure 22. Interlocked Handshake Timing (Output) Port 2 Side Only

Figure 23. Input (Acceptor) Timing IEEE-488 HS Port: Port 2 Side Only

Figure 24. Output (Source) Timing IEEE-488 HS Port: Port 2 Side Only

Programming

The programming of the FIO is greatly simplified by the efficient grouping of the various operation modes in the control registers. Since all of the control registers are read/write, the need for maintaining their image in system memory is eliminated. Also, the read/write feature of the registers aids in system debugging.

Each side of the FIO has 16 registers. All 16 registers are used by the Port 1 side; Control register 2 is not used on the Port 2 side. All registers are addressable OH through FH.

In the Z-BUS Low Byte mode, the FIO allows two methods for register addressing under control of the Right Justify Address (RJA) bit in Control register 0. When RIA = 0, address bus bits 1-4 are used for register addressing and bits 0, 5, 6, and 7 are ignored (Table 4). When RJA = 1, bits 0-3 are used for the register addresses, and bits 4-7 are ignored.

Control Registers. These four registers specify FIO operation. The Port 2 side control

registers operate only if the Port 2 device is a CPU. The Port 2 CPU can control interface operations, including data direction, only when enabled by the setting of bit 0 in the Port 1 side of Control Register 2. A 1 in bit 1 of the same register enables the handshake logic.

Interrupt Status Registers. These four registers control and monitor the priority interrupt functions for the FIO.

Interrupt Vector Register. This register stores the interrupt service routine address. This vector is placed on  $D_0\text{-}D_7$  when IUS is set by the Interrupt Acknowledge signal from the CPU. When bit 4 (Vector Includes Status) is set in Control Register 0, the reason for the interrupt is encoded within the vector address in bits 1, 2, and 3. If bit 5 is set in Control register 0, no vector is output by the FIO during an Interrupt Acknowledge cycle. However, IUS is set as usual.

| Non Z-BUS                         | D <sub>7</sub> -D <sub>4</sub> D <sub>3</sub>                        |                                    | $D_2$                              | $D_1$                              | $D_0$                              |                 |

|-----------------------------------|----------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------|

| Z-BUS High                        |                                                                      | A <sub>3</sub>                     | A <sub>2</sub>                     | A <sub>1</sub>                     | X <sub>0</sub>                     |                 |

| Z-BUS Low RJA=0                   | AD <sub>7</sub> -AD <sub>5</sub><br>AD <sub>7</sub> -AD <sub>4</sub> | AD <sub>4</sub><br>AD <sub>3</sub> | AD <sub>3</sub><br>AD <sub>2</sub> | AD <sub>2</sub><br>AD <sub>1</sub> | AD <sub>1</sub><br>AD <sub>0</sub> | AD <sub>0</sub> |

| Description                       |                                                                      | •                                  |                                    |                                    |                                    |                 |

| Control Register 0                | x                                                                    | 0                                  | 0                                  | 0                                  | 0                                  | x               |

| Control Register 1                | x                                                                    | 0                                  | 0                                  | 0                                  | 1                                  | x               |

| Interrupt Status Register 0       | x                                                                    | 0                                  | 0                                  | 1                                  | 0                                  | x               |

| Interrupt Status Register 1       | x                                                                    | 0                                  | 0                                  | 1                                  | 1                                  | x               |

| Interrupt Status Register 2       | ×                                                                    | 0                                  | 1                                  | 0                                  | 0                                  | x               |

| Interrupt Status Register 3       | x                                                                    | 0                                  | 1                                  | 0                                  | 1                                  | x               |

| Interrupt Vector Register         | x                                                                    | 0                                  | 1                                  | 1                                  | 0                                  | x               |

| Byte Count Register               | x                                                                    | 0                                  | 1                                  | 1                                  | 1                                  | x               |

| Byte Count Comparison<br>Register | ×                                                                    | 1                                  | 0                                  | 0                                  | 0                                  | x               |

| Control Register 2*               | x                                                                    | 1                                  | 0                                  | 0                                  | 1                                  | x               |

| Control Register 3                | x                                                                    | 1                                  | 0                                  | 1                                  | 0                                  | ×               |

| Message Out Register              | x                                                                    | 1                                  | 0                                  | 1                                  | 1                                  | x               |

| Message In Register               | x                                                                    | 1                                  | 1                                  | 0                                  | 0                                  | x               |

| Pattern Match Register            | x                                                                    | 1                                  | 1                                  | 0                                  | 1.                                 | ×               |

| Pattern Mask Register             | x                                                                    | 1                                  | 1                                  | 1                                  | 0                                  | x               |

| Data Buffer Register              | x                                                                    | 1                                  | 1                                  | 1                                  | 1                                  | x               |

Table 4. FIO Register Address Summary

x = Don't Care

\*Register is only on Port 1 side

(Continued)

ZILOG INC

Programming Byte Count Compare Register. This register contains a value compared with the byte count in the Byte Count register. If the Byte Count Compare interrupt is enabled, an interrupt will occur upon compare.

> Message Out Register. Either CPU can place a message in its Message Out register. If the opposite side Message register interrupt is enabled, the receiving side CPU will receive an interrupt request, advising that a message is present in its Message In register. Bit 5 in Control Register 1 on the initiating side is set when a message is written. It is cleared when the message is read by the receiving CPU.

Message In Register. This register receives a message placed in the Message Out register by the opposite side CPU.

Pattern Match Register. This register contains a bit pattern matched against the byte in the

Data Buffer register. When these patterns match, a Pattern Match interrupt will be generated, if previously enabled.

Pattern Mask Register. The Pattern Mask register may be programmed with a bit pattern mask that limits comparable bits in the Pattern Match register to non-masked bits (1 = mask).

Data Buffer Register. This register contains the data to be read from or written to the FIFO buffer.

Byte Count Register. This is a read-only register, containing the byte count for the FIFO buffer. The byte count is derived by subtracting the number of bytes read from the buffer from the number of bytes written into the buffer. The count is "frozen" for an accurate reading by setting bit 6 (Freeze Status register) in Control Register 1. This bit is cleared when the Byte Count register read is completed.

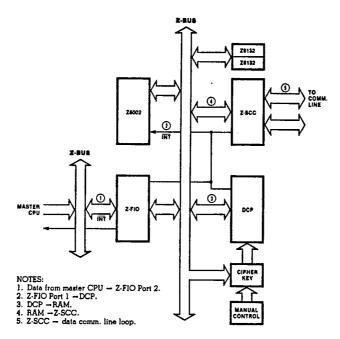

Figure 25. Typical Application: Node Controller

READ-ONLY BITS

Registers

Figure 28. Control Registers

### Interrupt Status Register 0 Address: 0010 (Read/Write) D, D, D, D, D, D, D, D, NOT USED (MUST BE PROGRAMMED 0) MESSAGE INTERRUPT PENDING (IP) MESSAGE INTERRUPT ENABLE (IE) - MESSAGE INTERRUPT UNDER SERVICE (IUS) IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: 0 0 0 NULL CODE 0 0 1 CLEAR IP & IUS 0 1 0 SET IUS 0 1 1 CLEAR IUS 1 0 0 SET IP 1 0 1 CLEAR IP 1 1 0 SET IE 1 1 1 CLEAR IE

Figure 27. Interrupt Status Registers

### Interrupt Status Register I Address: 0011

Address: 0011 (Read/Write)

### D, D4 D, D4 D, D, D, D4 DATA DIRECTION CHANGE INTERRUPT UNDER SERVICE (IUS) 1 = PATTERN MATCH FLAG\* PATTERN MATCH INTERRUPT PENDING (IP) DATA DIRECTION CHANGE INTERRUPT ENABLE (IE) DATA DIRECTION CHANGE INTERRUPT PENDING (IP) PATTERN MATCH INTERRUPT ENABLED (IE) PATTERN MATCH INTERRUPT UNDER SERVICE (IUS) HUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: NOT USED (MUST BE PROGRAMMED 6) IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: NULL CODE 0 0 0 CLEAR IP & IUS 0 0 1 SET IUS 0 1 0 CLEAR IUS 0 1 1 SET IP 1 0 0 1 0 1 CLEAR IP SET IE CLEAR IE 1 1 1 1 1 1 CLEAR IE READ-ONLY BITS

### Interrupt Status Register 2

Address: 0100 (Read/Write)

### Interrupt Status Register 3

Address: 0101 (Read/Write)

|                                                                                                                              | Ď. | ъ.       | D.   | Ď. | D.  | D.  | ۵. | Do                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------|----|----------|------|----|-----|-----|----|-------------------------------------------------------------------------------------------------------------|

|                                                                                                                              | _  |          |      |    |     |     | ÷  | <u>ت</u>                                                                                                    |

| FULL INTERRUPT UNDER SERVICE (IUS) FULL INTERRUPT ENABLE (IE) FULL INTERRUPT PENDING (IP) (IUS. IE. AND IP ARE WRITTEN USING | ÷  | <u> </u> |      |    |     |     |    | UFFER EMPTY  EMPTY INTERRUPT PENDING (IP)  EMPTY INTERRUPT ENABLE (IE)  EMPTY INTERRUPT UNDER SERVICE (IUS) |

| THE FOLLOWING COMMAND:                                                                                                       | Į  | 1        | Т    | 1. | ī   | 1   | 1  |                                                                                                             |

| NULL CODE<br>CLEAR IP & IUS                                                                                                  | Ġ  | 0        | ٥    |    | Ī   | Ī   | Ī  | IUS, IE, AND IP ARE WRITTEN USING<br>THE FOLLOWING COMMAND:                                                 |

| SET IUS                                                                                                                      | 1  | 1        | 0    | l  | r   | 1   | 6  | NULL CODE                                                                                                   |

| CLEAR IUS                                                                                                                    | 0  | 1        | 1    |    | 0   | 0   | 1  | CLEAR IP & IUS                                                                                              |

| SET IP                                                                                                                       | ī  | 0        | 0    |    | 0   | 1   | •  | SET IUS                                                                                                     |

| CLEAR IP                                                                                                                     | 1  | 0        | 1    |    | 0   | 1   | 1  | CLEAR IUS                                                                                                   |

| SET IE                                                                                                                       | 1  | T        | 0    |    | 1   | ۰   | ٥  | SET IP                                                                                                      |

| CLEAR IE                                                                                                                     | 1  | 1        | 1    | ĺ  | 1   | ٥   | 1  | CLEAR IP                                                                                                    |

|                                                                                                                              |    |          |      |    | 1   | -   | ٥  | SET IE                                                                                                      |

|                                                                                                                              |    |          |      |    | ⊡   | -   | -  | CLEAR IE                                                                                                    |

|                                                                                                                              |    | •R       | EAD- | ON | LYB | IT5 |    |                                                                                                             |

Figure 27. Interrupt Status Registers (Continued)

Registers

(Continued)

Figure 34. Message Out Register

Figure 35. Message In Register

### **ABSOLUTE MAXIMUM RATINGS**

Guaranteed by characterization/design.

| Voltages on all pins with respect  |                |

|------------------------------------|----------------|

| to GND                             | 0.3V to +7V    |

| Operating Case Temperature         |                |

| Storage Temperature Range          | 65°C to +150°C |

| Absolute Maximum Power Dissination |                |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

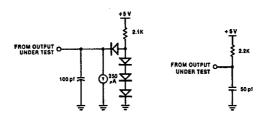

### STANDARD TEST CONDITIONS

The DC Characteristics and Capacitance sections listed below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin.

Military Operating Temperature Range (T<sub>C</sub>) -55°C to +125°C

Standard Military Test Condition +4.5V ≤ V<sub>CC</sub> ≤ +5.5V

All AC parameters assume a load capacitance of 50 pf. Add 15 ns delay for each 50 pf increase in load up to a maximum of 200 pf for the data bus. AC timing measurements are referenced to 1.5 volts (except for clock, which is referenced to the 20% and 80% points).

Standard Test Load

**Open-Drain Test Load**

| DC                   | Symbol            | Parameter                                   | Min              | Max                   | Unit | Condition                        |

|----------------------|-------------------|---------------------------------------------|------------------|-----------------------|------|----------------------------------|

| Charac-<br>teristics | $v_{IH}$          | Input High Voltage                          | 2,4 <sup>8</sup> | V <sub>CC</sub> +0.3° | V    |                                  |

|                      | $v_{iL}$          | Input Low Voltage                           | -0.3°            | 0.8                   | v    |                                  |

|                      | $\mathbf{v}_{OH}$ | Output High Voltage                         | 2.4 <sup>a</sup> |                       | v    | $I_{OH} = -250 \mu\text{A}$      |

|                      | v <sub>ol</sub>   | Output Low Voltage                          |                  | 0.4ª                  | V    | $I_{OL} = +2.0 \text{ mA}$       |

|                      |                   |                                             |                  | 0.5 <sup>b</sup>      | v    | $I_{OL} = +3.2 \text{ mA}$       |

|                      | $I_{IL}$          | Input Leakage                               | -10.0ª           | + 10.0ª               | μΑ   | $0.4 \leq V_{\rm IN} \leq +2.4V$ |

|                      | IOL               | Output Leakage                              | - 10.0ª          | + 10.0ª               | μĀ   | $0.4 \le V_{OUT} \le +2.4V$      |

|                      | I <sub>LM</sub>   | Mode Pins Input Leakage<br>(Pins 19 and 21) | -100b            | + 10.0ª               | μΑ   | $0 < V_{IN} < V_{CC}$            |

|                      | I <sub>CC</sub>   | V <sub>CC</sub> Supply Current              |                  | 350*                  | mÅ   |                                  |

V<sub>CC</sub> = 5 V ± 10% unless otherwise specified, over specified temperature range.

| Capacitance | Symbol          | Parameter                 | Min | Max             | Unit | Condition |

|-------------|-----------------|---------------------------|-----|-----------------|------|-----------|

|             | C <sub>IN</sub> | Input Capacitance         |     | 10 <sup>b</sup> | pf   |           |

|             | COUT            | Output Capacitance        |     | 15 <sup>b</sup> | pí   |           |

|             | C <sup>no</sup> | Bidirectional Capacitance |     | 20 <sup>b</sup> | pf   |           |

|             | Unmeasured pin  | s returned to ground.     |     |                 |      | ,         |

| Inputs      | ir              | Any Input Rise Time       |     | 100 b           | ns   |           |

| -           | Ħ               | Any Input Fall Time       |     | 100b            | ns   |           |

Note: a. Tested

- b. Guaranteed

- c. Guaranteed by characterization/design

- d. Not tested or guaranteed or spec'ed

| AC ( | Characteristics |                                                                                    | 41                           | 4Hz             | ė s              | (Hz             |             |

|------|-----------------|------------------------------------------------------------------------------------|------------------------------|-----------------|------------------|-----------------|-------------|

| No.  | Symbol          | Parameter                                                                          | Min                          | Max             | Min              | Max             | Notes*†     |

| 1    | Twas            | AS Low Width                                                                       | 70ª                          |                 | 50 <sup>4</sup>  |                 | 1           |

| . 2  | TsA(AS)         | Address to AS 1 Setup Time                                                         | 30ª                          |                 | 10ª              |                 | 1           |

| 3    | ThA(AS)         | Address to AS t Hold Time                                                          | 50ª                          |                 | 30ª              |                 | 1           |

| 4    | TsCSO(AS)       | CS to AS † Setup Time                                                              | 0ª                           |                 | 0*               |                 | 1           |

| 5-   | - ThCSO(AS) -   | — CS to AS † Hold Time —                                                           | 60ª-                         |                 | 40 <sup>a</sup>  |                 | <u> </u>    |

| 6    | TdAS(DS)        | AS t to DS   Delay                                                                 | 60 <sub>р</sub>              |                 | 40 <sup>b</sup>  |                 | 1           |

| 7    | TsA(DS)         | Address to $\overline{DS}$   (with $\overline{AS}$   to $\overline{DS}$   = 60 ns) | 120 <sup>b</sup>             |                 | 100 <sup>b</sup> |                 |             |

| 8    | TsRWR(DS)       | $R/\overline{W}$ (Read) to $\overline{DS}$   Setup Time                            | 100 <sup>b</sup>             |                 | 80 <sup>b</sup>  |                 |             |

| 9    | TsRWW(DS)       | R/W (Write) to DS   Setup Time                                                     | $0_p$                        |                 | 0 <sub>p</sub>   |                 |             |

| 10 - | - TwDS          | DS Low Width                                                                       | <del></del> 390 <sup>ь</sup> |                 | 250 <sup>b</sup> |                 |             |

| 11   | TsDW(DSi)       | Write Data to DS ↓ Setup Time                                                      | 30ª                          |                 | 20ª              |                 |             |

| 12   | TdDS(DRV)       | DS (Read) I to Address Data Bus Driven                                             | 0р                           |                 | 0р               |                 |             |

| 13   | TdDSf(DR)       | DS I to Read Data Valid Delay                                                      |                              | 250 ª           |                  | 180ª            |             |

| 14   | ThDW(DS)        | Write Data to DS ! Hold Time                                                       | 30 <sub>p</sub>              |                 | 20 <sup>b</sup>  |                 |             |

| 15-  | - TdDSr(DR)     | - DS 1 to Read Data Not Valid Delay                                                | 0 <sub>p</sub> -             |                 | 0 <sub>p</sub>   | <del>-</del>    | <del></del> |

| 16   | TdDS(DRz)       | DS 1 to Read Data Float Delay                                                      |                              | 70 <sup>b</sup> |                  | 45 <sup>b</sup> | 2           |

| 17   | ThRW(DS)        | R/W to DS 1 Hold Time                                                              | 55 <sup>b</sup>              |                 | 40 <sup>b</sup>  |                 |             |

| 18   | TdDS(AS)        | DS 1 to AS I Delay                                                                 | 50 <sup>b</sup>              |                 | 25 <sup>b</sup>  |                 |             |

| 19   | Tro             | Valid Access Recovery Time                                                         | 1000 <sup>b</sup>            |                 | 650 <sup>b</sup> |                 | 3           |

### NOTES:

- 1. Parameter does not apply to Interrupt Acknowledge transactions.

2. Float delay is measured to the time when the output has changed 0.5V from steady state with minimum ac load and maximum de load.

- 3. This is the delay from DS of one FIO access to DS of another FIO access (either read or write).

All timing references assume 2.0V for a logic "1" and 0.8V for a logic "0". All timings are preliminary and subject to change.

† Units in nanoseconds (ns).

# Parameter Test Status a. Tested b. Guaranteed

- Guaranteed by Design/Characterization

Not Tested or Guaranteed or Spec'd

Figure 36. Z-BUS CPU Interface Timing

### **AC** Characteristics

| ••  |             |                                             |                  | MHz              | 61               | av . 44          |               |

|-----|-------------|---------------------------------------------|------------------|------------------|------------------|------------------|---------------|

| No. | Symbol      | Parameter                                   | Min              | Max              | Min              | Max              | Notes*†       |

| 20  | TsIA(AS)    | INTACK to AS 1 Setup Time                   | 0р               |                  | 0ь               |                  |               |

| 21  | ThIA(AS)    | INTACK to AS t Hold Time                    | 250ª             |                  | 250ª             |                  |               |

| 22  | TsDSA(DR)   | DS (Acknowledge) I to Read Data Valid Delay |                  | 250 <sup>b</sup> |                  | 180 <sup>b</sup> |               |

| 23  | TwDSA       | DS (Acknowledge) Low Width                  | 390р             |                  | 250 <sup>b</sup> |                  |               |

| 24- | —Tdas(Ieo)— | AS 1 to IEO 1 Delay (INTACK Cycle)          | <del></del>      | —350ª            |                  | 250 <sup>a</sup> | <del></del> 4 |

| 25  | TdIEI(IEO)  | IEI to IEO Delay                            |                  | 150ª             |                  | 100ª             | 4             |

| 26  | TslEI(DSA)  | IEI to DS (Acknowledge)   Setup Time        | 100 <sup>b</sup> |                  | 70 <sup>b</sup>  |                  |               |

| 27  | Thiei(DSA)  | IEI to DS (Acknowledge) ! Hold Time         | 50 <sup>b</sup>  |                  | 30 <sup>b</sup>  |                  | 4             |

| 28  | TdDS(INT)   | DS (INTACK Cycle) to INT Delay              |                  | 900ª             |                  | 800 <sup>a</sup> |               |

| 29  | TdDCST      | Interrupt Daisy Chain Settle Time           |                  | đ                |                  | d                | 4             |

and TdIEI(IEO) for each peripheral, separating them in the chain.

\* Timings are preliminary and subject to change.

† Units in nanoseconds (ns).

Figure 37. Z-BUS CPU Interrupt Acknowledge Timing

- Parameter Test Status

a. Tested

b. Guaranteed

c. Guaranteed by Design/Characterization

d. Not Tested or Guaranteed or Spec'd

NOTES:

4. The parameters for the devices in any particular daisy chain must meet the following constraint: The delay from AS to DS must be greater than the sum of TARS(IEO) for the highest priority peripheral, TsIEI(DSA) for the lowest priority peripheral

| AC C | haracteristics |                                         |            |              |            |                      | T-46-35 |

|------|----------------|-----------------------------------------|------------|--------------|------------|----------------------|---------|

| No.  | Symbol         | Parameter                               | 4 M<br>Min | Hz<br>Max    | 6 I<br>Min | MHz<br>Max           | Notes*† |

| 30   | TdMW(INT)      | Message Write to INT Delay              |            | 1°           |            | lc                   | 5       |

| 31   | TdDC(INT)      | Data Direction Change to INT Delay      |            | 1°           |            | 1¢                   | 6       |

| 32   | TdPMW(INT)     | Pattern Match to INT Delay (Write Case) |            | 1°           |            | lc                   |         |

| 33   | TdPMR(INT)     | Pattern Match (Read Case) to INT Delay  |            | lc           |            | lc                   |         |

| 34   | -TdSC(INT)-    | Status Compare to INT Delay             |            | – 1 <u>°</u> |            | — 1 <mark>c</mark> — | 6       |

| 35   | Tder(INT)      | Error to INT Delay                      |            | 1°           |            | 1°                   |         |

| 36   | TdEM(INT)      | Empty to INT Delay                      |            | 1°           |            | Jc                   | 6       |

| 37   | TdFL(INT)      | Full to INT Delay                       |            | 1°           |            | 1°                   | 6       |

| 38   | TdAS(INT)      | AS to INT Delay                         |            | d            |            | d                    |         |

NOTES:

5. Write is from the other side of FIO.

6. Write can be from either side, depending on programming of FIO.

Timings are preliminary and subject to change.

Units equal to AS Cycles + ns.

Figure 38. Z-BUS Interrupt Timing

**Parameter Test Status**

- a. Tested

- b. Guaranteed

- c. Guaranteed by Design/Characterization d. Not Tested or Guaranteed or Spec'd

| ٦ | Γ | Δ | 6 |   | 3 | ı |

|---|---|---|---|---|---|---|

|   | - | 4 | 0 | - | 3 | i |

| AC. | Characteristics  |                             |                 |                  |                    | 1-40              | ,-33    |  |

|-----|------------------|-----------------------------|-----------------|------------------|--------------------|-------------------|---------|--|

|     | J110100141121102 |                             | 41              | MHz              | 6 3                | 1Hz               |         |  |

| No. | Symbol           | Parameter                   | Min             | Max              | Min                | Max               | Notes*† |  |

| 1   | TdDS(WAIT)       | AS 1 to WAIT   Delay        |                 | 190ª             |                    | 160               |         |  |

| 2   | TdDSi(WAIT)      | DSI 1 to WAIT 1 Delay       |                 | 1000b            |                    | 1000þ             |         |  |

| 3   | TdACK(WAIT)      | ACKIN I to WAIT   Delay     |                 | 1000p            |                    | 1000p             | 1       |  |

| 4-  | -TdDS(REQ)       | - DS I to REQ 1 Delay       | ·-··            | 350 <u></u>      |                    | — 300, —          |         |  |

| 5   | TdDMA(REQ)       | DMASTB I to REQ 1 Delay     |                 | 350 b            |                    | 300 b             |         |  |

| 6   | TdDS1(REQ)       | DSI 1 to REQ   Delay        |                 | 1000             |                    | 1000 <sup>a</sup> |         |  |

| 7   | TdACK(REQ)       | ACKIN I to REQ I Delay      | 6               | 1000p            |                    | 1000b             |         |  |

| 8-  | - TdSU(DMA)      | - Data Setup Time to DMASTB | 200 b           |                  | 150 <mark>b</mark> |                   |         |  |

| 9   | TdH(DMA)         | Data Hold Time to DMASTB    | 30 <sub>p</sub> |                  | 20 <sup>b</sup>    |                   |         |  |

| 10  | TdDMA(DR)        | DMASTB I to Valid Data      |                 | 150 <sup>b</sup> | _                  | 100p              |         |  |

| 11  | TdDMA(DRH)       | DMASTB I to Data Not Valid  | 0р              |                  | Ор                 |                   |         |  |

| 12  | TdDMA(DR2)       | DMASTB 1 to Data Bus Float  |                 | 70 b             |                    | 45 b              |         |  |

|     |                  |                             |                 |                  |                    | ····              |         |  |

Timings are preliminary and subject to change.

Units in nanoseconds (ns).

Figure 39. Z-BUS Request/Wait Timing

| AC           | Characteristics                       |                                                                                                                         |                                                        | ИНz | 61                                                     | ИНz |         |

|--------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|--------------------------------------------------------|-----|---------|

| No.          | Symbol                                | Parameter                                                                                                               | Min                                                    | Max | Min                                                    | Max | Notes*† |

| 1<br>2.<br>3 | TdDSQ(AS)<br>TdASQ(DS)<br>Tw(AS + DS) | Delay from DS 1 to AS 1 for No Reset Delay for AS 1 to DS 1 for No Reset Minimum Width of AS and DS Both Low for Reset. | 40 <sup>b</sup><br>50 <sup>b</sup><br>500 <sup>b</sup> |     | 20 <sup>b</sup><br>30 <sup>b</sup><br>350 <sup>b</sup> |     | 1       |

Timings are preliminary and subject to change.

Units in nanoseconds (ns).

Figure 40. Z-BUS Reset Timing

NOTES:

1. The delay is from DAV for 3-Wire Input Handshake. The delay is from DAC for 3-Wire Handshake.

NOTES:

1. Internal circuitry allows for the reset provided by the Z8 (DS held Low while AS pulses) to be sufficient.

| AC C |               | •                                 |                  | 1-                 | .40-55          |             |

|------|---------------|-----------------------------------|------------------|--------------------|-----------------|-------------|

| No.  | Symbol        | Parameter                         | 4 M<br>Min       | iHz 6 h<br>Max Min | (Hz<br>Max      | Notes*†     |

| 1    | TsA(RD)       | Address Setup to RD ↓             | 80ª              | 80ª                |                 | 1           |

| 2    | TsA(WR)       | Address Setup to WR               | 80ª              | 80 <sup>a</sup>    |                 |             |

| 3    | ThA(RD)       | Address Hold Time to RD 1         | √ 0p             | 0 <sub>p</sub>     |                 | 1           |

| 4 -  | -ThA(WR)      |                                   | 0 <sub>p</sub>   | 0 <sub>p</sub>     |                 |             |

| 5    | TsCEI(RD)     | CE Low Setup Time to RD           | О <sub>р</sub>   | Op                 |                 | 1           |

| 6    | TsCEI(WR)     | CE Low Setup Time to WR           | Op               | 0 <sub>p</sub>     |                 |             |

| 7    | ThCEI(RD)     | CE Low Hold Time to RD            | О.р.             | 0р                 |                 | 1           |

| 8-   | -ThCEI(WR) -  | — CE Low Hold Time to WR          | 0 <u>b</u>       | 0 <u>b</u>         |                 | <del></del> |

| 9    | TsCEh(RD)     | CE High Setup Time to RD          | 100 <sup>b</sup> | 70 <sup>b</sup>    |                 | 1           |

| 10   | TsCEh(WR)     | CE High Setup Time to WR          | 100 <sup>b</sup> | 70 <sup>b</sup>    |                 |             |

| 11   | TwRD1         | RD Low Width                      | 390p             | 250 <sup>b</sup>   |                 |             |

| 12-  | - TdRD(DRA) - |                                   | 0 <mark>b</mark> | 0 <sub>p</sub>     |                 |             |

| 13   | TdRDi(DR)     | RD I to Valid Data Delay          |                  | 250 <sup>a</sup>   | 180ª            |             |

| 14   | TdRDr(DR)     | RD 1 to Read Data Not Valid Delay | 0 <sub>p</sub>   | Op                 |                 |             |

| 15   | TdRD(DRz)     | RD 1 to Data Bus Float            |                  | 70 <sup>b</sup>    | 45 <sup>b</sup> | 2           |

| 16 - | -TwWR1        | WR Low Width                      | 390 <sup>b</sup> | 250 <sup>b</sup>   |                 |             |

| 17   | TsDW(WR)      | Data Setup Time to WR             | 0 <b>p</b>       | 0 <sub>p</sub>     |                 |             |

| 18   | ThDW(WR)      | Data Hold Time to WR              | 30 <sub>p</sub>  | 20 <sup>b</sup>    |                 |             |

| 19   | Trc(WR)       | Write Valid Access Recovery Time  | 1000 b           | 650 <sup>b</sup>   |                 |             |

| 20   | Trc(RD)       | Read Valid Access Recovery Time   | 1000 + WRD       | 650 + WRp          |                 | 3           |

- 1. Parameter does not apply to Interrupt Acknowledge transactions.

2. Float delay is measured to the time the output has changed 0.5V from steady state with minimum ac load and maximum dc load.

- 3. Recovery time equal to Trc(WR) + write pulse width of the opposite side.

- \* Timings are preliminary and subject to change.

† Units in nanoseconds (ns).

Figure 41. Non-Z-BUS CPU Interface Timing

Figure 42. Z-BUS/Non-Z-BUS Recovery Time

| AC ( | Chara | cteris | lics |

|------|-------|--------|------|

|------|-------|--------|------|

| AC CH | GLGCIOLIBIICE |                                        | 41               | MHz              |                  | #**              |        |

|-------|---------------|----------------------------------------|------------------|------------------|------------------|------------------|--------|