# Low Power 10-bit 3 Gsps Digital to Analog Datasheet DS1090

## **MAIN FEATURES**

- 10-bit Resolution

- 3 GSps Guaranteed Conversion Rate

- 6 GHz Analog Output Bandwidth

- 60 ps Full Scale Rise Time

- 4:1 or 2:1 integrated Parallel MUX (Selectable)

- Selectable Output Modes for Performance Optimization:

Return to Zero, Non Return to Zero, Narrow Return to Zero, RF

- Low Latency Time: 3.5 Clock Cycles

- 1.4 Watt Power Dissipation in MUX 4:1 Mode

- Functions

- Selectable MUX Ratio 4:1 (Full Speed), 2:1 (Half Speed)

- Triple Majority Voting

- User-friendly Functions:

- Gain Adjustment

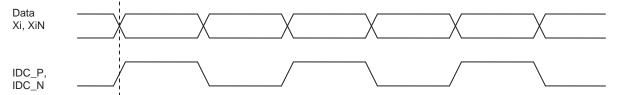

- Input Data Check Bit (FPGA Timing Check)

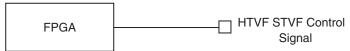

- Setup Time and Hold Time Violation Flags (STVF, HTVF)

- Clock Phase Shift Select for Synchronization with DSP (PSS[2:0])

- Output Clock Division Selection (Possibility to Change the Division Ratio of the DSP Clock)

- Input Under Clocking Mode

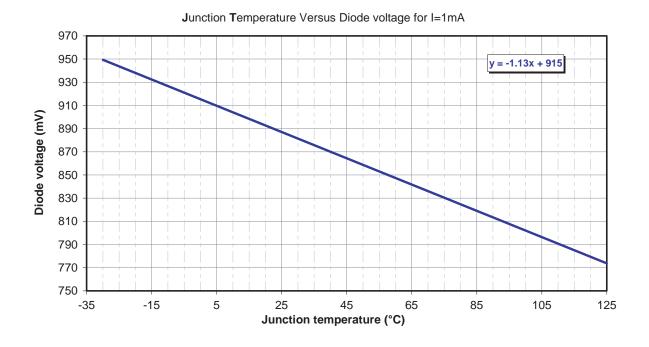

- Diode for Die junction Temperature Monitoring

- LVDS Differential Data input and DSP Clock Output

- Analog Output Swing:  $1V_{pp}$  Differential ( $100\Omega$  Differential Impedance)

- External Reset for Synchronization of Multiple MuxDACs

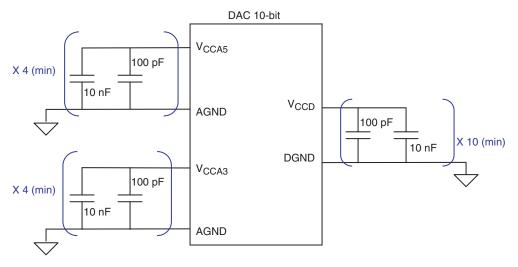

- Power Supplies: 3.3 V (Digital), 3.3V & 5.0V (Analog)

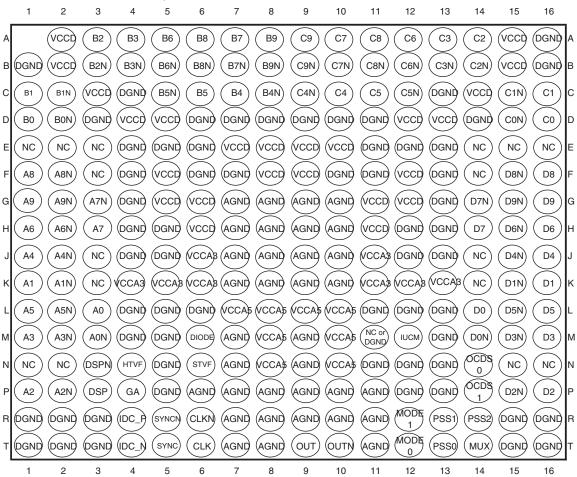

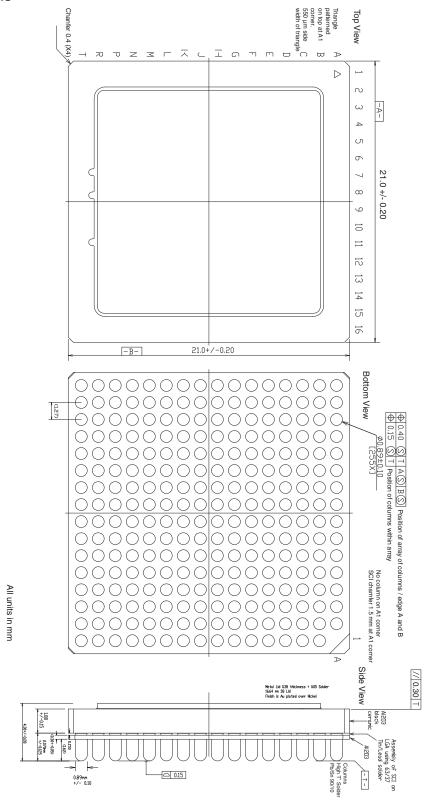

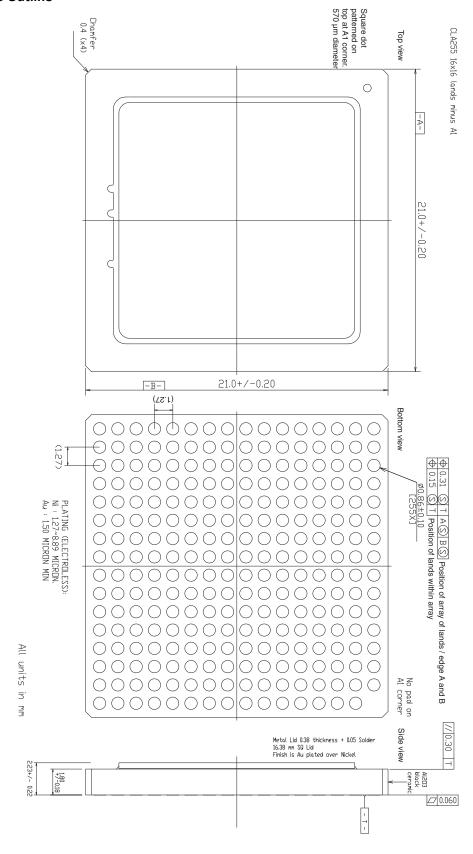

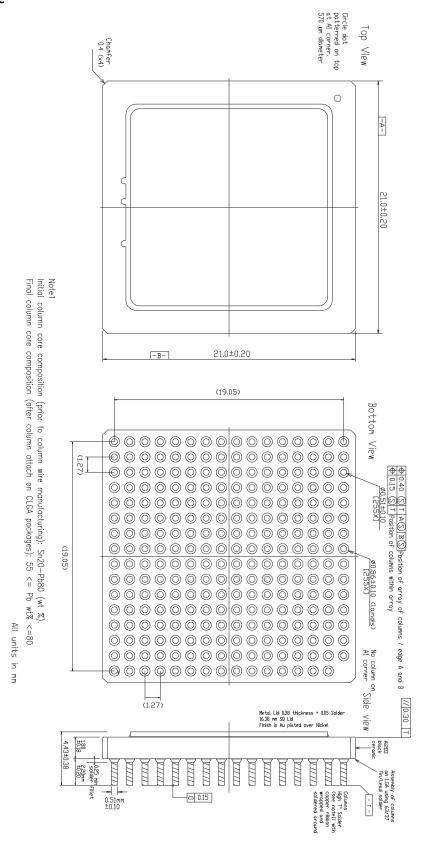

- LGA255, CCGA255, Ci-CGA255 Package (21 × 21 mm Body Size, 1.27 mm Pitch)

# **PERFORMANCES**

Broadband: NPR at -14 dB Loading Factor

| • | 1st Nyquist (NRTZ):        | NPR = 46.0 dB | 9.2 Bit |

|---|----------------------------|---------------|---------|

|   | Equivalent at Fs = 3 GSps  |               |         |

| • | 2nd Nyquist (NRTZ or RTZ): | NPR = 40.0 dB | 8.2 Bit |

|   | Equivalent at Fs = 3 GSps  |               |         |

| • | 3rd Nyquist (RF):          | NPR = 38.0 dB | 7.8 Bit |

|   | Equivalent at Fs = 3 GSps  |               |         |

|   |                            |               |         |

Single Tone: (see Section 5. "Functional Description" on page 16)

- Performances Characterized for Fout from 100 MHz to 4500 MHz and from 2 GSps to 3.2 GSps.

- Performance Industrially Screened Over 3 Nyquist Zones at 3 GSps for Selected Fout.

Step Response

• Full Scale Rise /Fall Time < 60 ps

#### **APPLICATIONS**

- Direct Digital Synthesis for Broadband Applications (L-S and Lower C Band)

- Automatic Test Equipment (ATE)

- Arbitrary Waveform Generators

- Satellite up-conversion Sub-systems

- Radar Waveform Signal Synthesis

- DOCSIS V3.0 Systems

Whilst Teledyne e2v Semiconductors SAS has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. Teledyne e2v Semiconductors SAS accepts no liability beyond the set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of the devices in accordance with information contained herein.

Teledyne e2v Semiconductors SAS, avenue de Rochepleine 38120 Saint-Egrève, France

Contact Teledyne e2v by e-mail: hotline-bdc@teledyne-e2v.com or visit www.teledyne-e2v.com for global sales and operations centres

1090E-BDC-01/18

Holding Company: Teledyne e2v Semiconductors SAS

Telephone: +33 (0)4 76 58 30 00

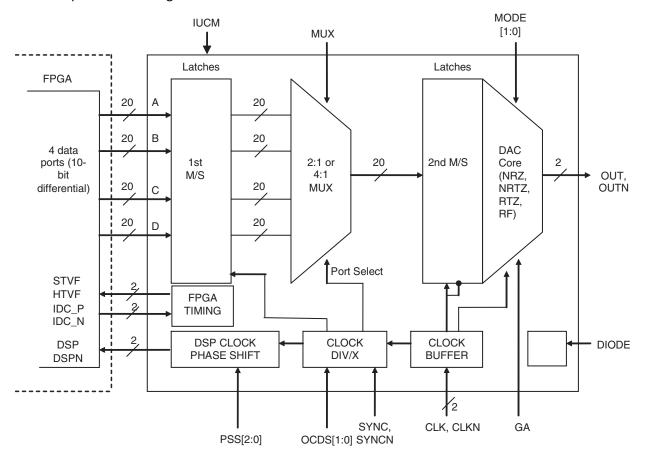

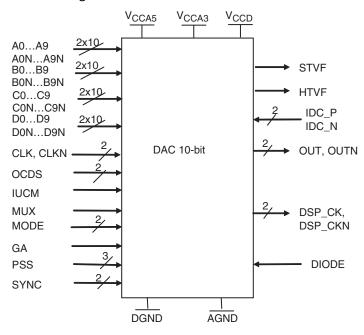

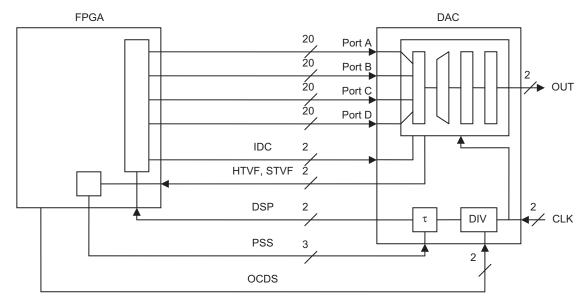

#### 1. BLOCK DIAGRAM

Figure 1-1. Simplified Block Diagram

# 2. DESCRIPTION

The EV10DS130A/B is a 10-bit 3 GSps DAC with an integrated 4:1 or 2:1 multiplexer, allowing easy interface with standard LVDS FPGAs thanks to user friendly features as OCDS, PSS.

It embeds different output modes (RTZ, NRZ, narrow RTZ, RF) that allows performance optimizations depending on the working Nyquist zone.

The Noise Power Ratio (NPR) performance, over more than 900 MHz instantaneous bandwidth, and the high linearity (SFDR, IMD) over full 1<sup>st</sup> Nyquist zone at 3 GSps (NRZ feature), make this product well suited for high-end applications such as arbitrary waveform generators and broadband DDS systems.

## 3. ELECTRICAL CHARACTERISTICS

# 3.1 Absolute Maximum Ratings

Table 3-1. Absolute Maximum Ratings

| Parameter                                                                                                                     | Symbol                                     | Value                           | Unit                      |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------|---------------------------|

| Positive Analog supply voltage                                                                                                | V <sub>CCA5</sub>                          | 6.0                             | V                         |

| Positive Analog supply voltage                                                                                                | V <sub>CCA3</sub>                          | 4.0                             | V                         |

| Positive Digital supply voltage                                                                                               | V <sub>CCD</sub>                           | 4.0                             | V                         |

| Digital inputs (on each single-ended input) and IDC , SYNC, signal Port P = A, B, C, D $V_{\rm IL} \\ V_{\rm IH}$             | [POP9], [PON P9N] IDC_P, IDC_N SYNC, SYNCN | GND-0.3<br>V <sub>CCA3</sub>    | V<br>V                    |

| Digital Input maximum Differential mode swing                                                                                 | 311(6) 311(6)(                             | 2.0                             | $V_{pp}$                  |

| Master clock input (on each single-ended input)  V <sub>IL</sub> V <sub>IH</sub> Master Clock Maximum Differential mode swing | CLK, CLKN                                  | 1.5<br>3.5<br>2.5               | V<br>V<br>V <sub>pp</sub> |

| Control functions inputs $ {\bf V_{IL}} \\ {\bf V_{IH}} $                                                                     | MUX,<br>MODE[01],<br>PSS[02],<br>OCDS[01]  | -0.4V<br>V <sub>CCD</sub> + 0.4 | V<br>V                    |

| Gain Adjustment function                                                                                                      | GA                                         | -0.3V, V <sub>CCA3</sub> + 0.3  | V                         |

| Maximum Junction Temperature                                                                                                  | Tj                                         | 170                             | °C                        |

| Storage Temperature                                                                                                           | Tstg                                       | -65 to 150                      | °C                        |

| Electrostatic discharge immunity ESD Classification                                                                           | ESD HBM                                    | 1000<br>Class 1B                | V                         |

Notes: 1. Absolute maximum ratings are limiting values (referenced to GND = 0V), to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability.

- 2. All integrated circuits have to be handled with appropriate care to avoid damages due to ESD. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

- 3. Maximum ratings enable active inputs with DAC powered off.

- 4. Maximum ratings enable floating inputs with DAC powered on.

- 5. DSP clock and STVF, HTVF output buffers must not be shorted to ground nor positive power supply.

#### 3.2 Recommended Conditions of Use

Table 3-2. Recommended Conditions of Use

| Parameter                                                                                                                                       | Symbol                                              | Comments                           | Recommended Value      | Unit                       | Note      |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------|------------------------|----------------------------|-----------|

| Positive analog supply voltage                                                                                                                  | V <sub>CCA5</sub>                                   |                                    | 5.0                    | ٧                          | (2)(4)    |

| Positive analog supply voltage                                                                                                                  | V <sub>CCA3</sub>                                   |                                    | 3.3                    | V                          | (1)(2)(4) |

| Positive digital supply voltage                                                                                                                 | V <sub>CCD</sub>                                    |                                    | 3.3                    | V                          | (2)(4)    |

| Digital inputs (on each single-ended input) and IDC , SYNC, signal Port P = A, B, C, D  V <sub>IL</sub> V <sub>IH</sub> Differential mode swing | [P0P9],<br>[P0N P9N]<br>IDC_P, IDC_N<br>SYNC, SYNCN |                                    | 1.075<br>1.425<br>700  | V<br>V<br>mV <sub>pp</sub> | (3)       |

| Master clock input power level (Differential mode)                                                                                              | P <sub>CLK</sub>                                    |                                    | 3                      | dBm                        | (3)       |

| Control functions inputs                                                                                                                        | IUCM, MUX,<br>OCDS, PSS,<br>MODE, PSS               | V <sub>IL</sub><br>V <sub>IH</sub> | 0<br>V <sub>CCD</sub>  | V<br>V                     |           |

| Gain Adjustment function                                                                                                                        | GA                                                  | Range                              | 0<br>V <sub>CCA3</sub> | V                          |           |

| Operating Temperature Range                                                                                                                     | Tc = Tcase<br>Tj = T junction                       | Military "M" & space grade         | −55°C < Tc, Tj < 125°C | °C                         |           |

Notes: 1. For low temperature it is recommended to operate at maximum analog supplies (V<sub>CCA3</sub>) level.

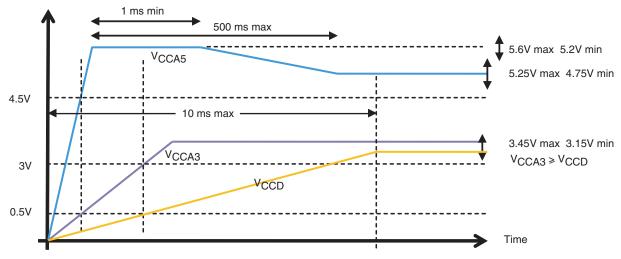

- The rise time of any power supplies (V<sub>CCD</sub>, V<sub>CCA5</sub>, V<sub>CCA3</sub>) shall be <10ms.</li>

For EV10DS130A, in order to obtain the guaranteed performances and functionality, the following rules shall be followed when powering the devices (See Section 7.9 "Power Up Sequencing" on page 42)

For EV10DS130B, no specific power up sequence nor power supplies relationships are required.

- 3. Analog output is in differential. Single-ended operation is not recommended. Guaranted performance is only in differential configuration.

- 4. No power-down sequencing is required.

# 3.3 Electrical Characteristics

Values in the tables below are based on our conditions of measurement and valid over temperature range respectively for M, and Space quality level and for typical power supplies ( $V_{CCA5} = 5.0V$ ,  $V_{CCA3} = 3.3V$ ,  $V_{CCD} = 3.3V$ ), typical swing, unless specified and in MUX4:1 mode.

Table 3-3.Electrical Characteristics

| Parameter                                                          | Symbol                                                     | Min                  | Тур              | Max                  | Unit                 | Note   | Test<br>Level <sup>(2)</sup> |

|--------------------------------------------------------------------|------------------------------------------------------------|----------------------|------------------|----------------------|----------------------|--------|------------------------------|

| RESOLUTION                                                         |                                                            |                      | 10               | -                    | bit                  |        | 1,6                          |

| POWER REQUIREMENTS                                                 | •                                                          |                      |                  |                      |                      | •      |                              |

| Power Supply voltage                                               |                                                            |                      |                  |                      |                      |        |                              |

| - Analog<br>- Analog<br>- Digital                                  | V <sub>CCA5</sub><br>V <sub>CCA3</sub><br>V <sub>CCD</sub> | 4.75<br>3.15<br>3.15 | 5<br>3.3<br>3.3  | 5.25<br>3.45<br>3.45 | V<br>V               | (7)(8) | 1,6                          |

| Power Supply current (4:1 MUX)                                     |                                                            |                      |                  |                      |                      |        |                              |

| - Analog<br>- Analog<br>- Digital                                  | I <sub>CCA5</sub><br>I <sub>CCA3</sub><br>I <sub>CCD</sub> |                      | 84<br>106<br>187 | 92<br>125<br>213     | mA<br>mA<br>mA       |        | 1,6                          |

| Power Supply current (2:1 MUX)                                     |                                                            |                      |                  |                      |                      |        |                              |

| - Analog<br>- Analog<br>- Digital                                  | I <sub>CCA5</sub><br>I <sub>CCA3</sub><br>I <sub>CCD</sub> |                      | 84<br>106<br>160 | 92<br>125<br>185     | mA<br>mA<br>mA       |        | 1,6                          |

| Power dissipation (4:1 MUX)                                        | $P_{D}$                                                    |                      | 1.4              | 1.6                  | W                    |        | 1,6                          |

| Power dissipation (2:1 DMUX)                                       | P <sub>D</sub>                                             |                      | 1.3              | 1.5                  | W                    |        | 1,6                          |

| DIGITAL DATA INPUTS, SYNC and IDC INPUTS                           |                                                            |                      |                  |                      |                      |        |                              |

| Logic compatibility                                                |                                                            |                      | LVDS             |                      |                      |        |                              |

| Digital input voltages: - Differential input voltage - Common mode | V <sub>ID</sub><br>V <sub>ICM</sub>                        | 100                  | 350<br>1.25      | 500                  | mV <sub>p</sub><br>V |        | 1,6<br>4                     |

| Input capacitance from each single input to ground                 |                                                            |                      |                  | 2                    | pF                   |        | 5                            |

| Differential Input resistance                                      |                                                            | 80                   | 100              | 120                  | Ω                    |        | 1,6                          |

| CLOCK INPUTS                                                       |                                                            |                      |                  |                      |                      |        |                              |

| Input voltages (Differential operation swing)                      |                                                            | 0.56                 | 1                | 2.24                 | $V_{pp}$             |        | 4                            |

| Power level (Differential operation)                               |                                                            | -4                   | 1                | 8                    | dBm                  |        | 4                            |

| Common mode                                                        |                                                            | 2.4                  | 2.5              | 2.6                  | V                    |        | 4                            |

| Input capacitance from each single input to ground (at die level)  |                                                            |                      | 2                |                      | pF                   |        | 5                            |

| Differential Input resistance                                      |                                                            | 80                   | 100              | 120                  | Ω                    |        | 1,6                          |

Table 3-3.

Electrical Characteristics (Continued)

| Parameter                                                                                                                                            | Symbol                                                | Min      | Тур                      | Max        | Unit                 | Note       | Test<br>Level <sup>(2)</sup> |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------|--------------------------|------------|----------------------|------------|------------------------------|

| DSP CLOCK OUTPUT                                                                                                                                     |                                                       |          |                          |            |                      |            |                              |

| Logic compatibility                                                                                                                                  |                                                       |          | LVDS                     |            |                      |            |                              |

| Digital output voltages:                                                                                                                             |                                                       |          |                          |            |                      |            |                              |

| - Differential output voltage<br>- Common mode                                                                                                       | V <sub>OD</sub><br>V <sub>OCM</sub>                   | 240      | 350<br>1.30              | 450        | mV <sub>p</sub><br>V |            | 1,6<br>4                     |

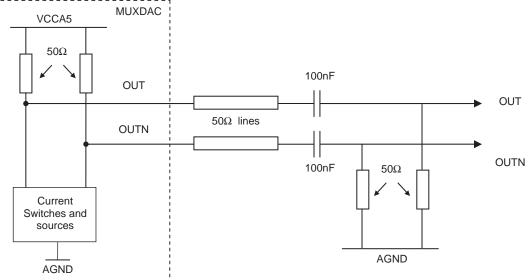

| ANALOG OUTPUT                                                                                                                                        |                                                       |          |                          |            |                      |            |                              |

| Full-scale Differential output voltage (100 $\Omega$ differentially terminated)                                                                      |                                                       | 0.92     | 1                        | 1.08       | V <sub>pp</sub>      |            | 1,6                          |

| Full-scale output power (differential output)                                                                                                        |                                                       | 0.25     | 1                        | 1.64       | dBm                  |            | 1,6                          |

| Single-ended mid-scale output voltage (50 $\Omega$ terminated)                                                                                       |                                                       |          | V <sub>CCA5</sub> - 0.43 |            | V                    | (4)        |                              |

| Output capacitance                                                                                                                                   |                                                       |          | 1.5                      |            | pF                   |            | 5                            |

| Output internal differential resistance                                                                                                              |                                                       | 90       | 100                      | 110        | Ω                    |            | 1, 6                         |

| Output VSWR (using e2v evaluation board) 1.5 GHz 3 GHz 4.5 GHz                                                                                       |                                                       |          | 1.17<br>1.54<br>1.64     |            |                      |            | 4                            |

| Output bandwidth                                                                                                                                     |                                                       |          | 6                        |            | GHz                  |            | 4                            |

| FUNCTIONS                                                                                                                                            |                                                       |          |                          |            |                      |            |                              |

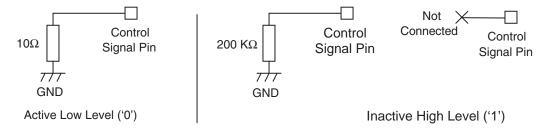

| Digital functions: MODE, OCDS, PSS, MUX                                                                                                              |                                                       |          |                          |            |                      |            |                              |

| - Logic 0<br>- Logic 1<br>- Input Current                                                                                                            | V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IN</sub> | 1.6      | 0<br>V <sub>CCD</sub>    | 0.8<br>150 | V<br>V<br>μA         | (6)        |                              |

| Gain Adjustment function                                                                                                                             | GA                                                    |          | 0<br>V <sub>CCA3</sub>   |            |                      |            | 1,6                          |

| Digital output function (HTVF, STVF)                                                                                                                 |                                                       |          |                          |            |                      |            |                              |

| - Logic 0<br>- Logic 1<br>- Output Current                                                                                                           | V <sub>OL</sub><br>V <sub>OH</sub><br>I <sub>O</sub>  | _<br>2.1 | -                        | 0.8<br>80  | V<br>V<br>μA         | (5)<br>(6) | 1,6                          |

| DC ACCURACY                                                                                                                                          |                                                       |          |                          |            |                      |            |                              |

| Differential Non-Linearity                                                                                                                           | DNL+                                                  |          |                          | 0.90       | LSB                  |            | 1,6                          |

| Differential Non-Linearity                                                                                                                           | DNL-                                                  | -0.90    |                          |            | LSB                  |            | 1,6                          |

| Integral Non-Linearity                                                                                                                               | INL+                                                  |          |                          | 1.5        | LSB                  |            | 1,6                          |

| Integral Non-Linearity                                                                                                                               | INL-                                                  | -1.5     |                          |            | LSB                  |            | 1,6                          |

| DC gain:                                                                                                                                             |                                                       |          |                          |            |                      |            |                              |

| <ul><li>Initial gain error</li><li>DC gain adjustment</li><li>DC gain sensitivity to power supplies</li><li>DC gain drift over temperature</li></ul> |                                                       | -8       | 0<br>±11<br>±2           | +8<br>+6   | %<br>%<br>%<br>%     | (3)        | 1,6<br>4<br>1,6<br>4         |

Notes: 1. For use in higher Nyquist zone, it is recommended to use higher power clock within the limit.

- 2. See Section 3.6 on page 14 for explanation of test levels.

- 3. Initial gain error corresponds to the deviation of the DC gain center value from unity gain. The DC gain adjustment (GA function) ensures that the initial gain deviation can be cancelled.

The DC gain sensitivity to power supplies is given according the rule:

Chip Control of Contro

4. Single-ended operation is not recommended, this line is given for better understanding of what is output by the DAC.

- GainSensVsSupply = |Gain@VccMin Gain@VccMax| / Gain@Vccnom

- 5. In order to modify the V<sub>OL</sub>/V<sub>OH</sub> value, potential divider could be used.

- 6. Sink or source.

- Only for EV10DS130A dependency between power supplies:

Within the applicable power supplies range, the following relationship shall always be satisfied V<sub>CCA3</sub> ≥ V<sub>CCD</sub>, taking into account AGND and DGND planes are merged and power supplies accuracy.

- 8. Please refer Section 7.9 "Power Up Sequencing" on page 42.

#### 3.4 AC Electrical Characteristics

Values in the tables below are based on our conditions of measurement and valid over temperature range respectively for M, and Space quality level and for typical power supplies ( $V_{CCA5} = 5.0V$ ,  $V_{CCA3} = 3.3V$ ,  $V_{CCD} = 3.3V$ ), typical swing, unless specified and in MUX4:1 mode.

**Table 3-4.** AC Electrical Characteristics NRZ Mode (First Nyquist Zone)

| Symbol | Min      | Тур            | Max            | Unit           | Note            | Test<br>level <sup>(1)</sup> |

|--------|----------|----------------|----------------|----------------|-----------------|------------------------------|

|        |          |                |                |                |                 |                              |

| SFDR   | 55<br>56 | 66<br>67       |                | dBc            |                 | 1,6<br>1,6                   |

|        |          |                |                |                |                 |                              |

|        |          | -66<br>-69     | -54<br>-57     | dBm            |                 | 1,6<br>1,6                   |

|        |          | ±2             |                | dB             |                 | 4                            |

|        |          |                |                |                |                 |                              |

|        |          | -82            |                | dBm            |                 | 4                            |

|        |          | -85            |                | dBm            |                 | 4                            |

| NPR    | 43       | 45             |                | dB             | (2)             | 1,6                          |

|        | SFDR     | SFDR  55<br>56 | SFDR  55 66 67 | SFDR  55 66 67 | SFDR   55 66 67 | SFDR   55                    |

Table 3-4.

AC Electrical Characteristics NRZ Mode (First Nyquist Zone) (Continued)

| Parameter                                                | Symbol | Min | Тур | Max  | Unit       | Note | Test<br>level <sup>(1)</sup> |

|----------------------------------------------------------|--------|-----|-----|------|------------|------|------------------------------|

| Equivalent ENOB Computed from NPR figure at 3 GSps       | ENOB   | 8.6 | 9.0 |      | Bit        | (2)  | 1,6                          |

| Signal to Noise Ratio Computed from NPR figure at 3 GSps | SNR    | 54  | 56  |      | dB         | (2)  | 1,6                          |

| DAC self noise density at code 0 or 1023                 |        |     |     | -150 | dBm/H<br>z |      | 1,6                          |

2. Figures in tables are derived from industrial screening; for practical reasons (necessity to cover also 2nd and 3rd Nyquist Zones) the balun used for industrial test is not optimum for first Nyquist performances, and results when Fout or folded low order hamonics are between DC to 400 MHz are very pessimistic.

**Table 3-5.** AC Electrical Characteristics NRTZ Mode (First & Second Nyquist Zone)

| Parameter                                                        | Symbol | Min | Тур | Max         | Unit   | Note | Test<br>level <sup>(1)</sup> |

|------------------------------------------------------------------|--------|-----|-----|-------------|--------|------|------------------------------|

| Single-tone Spurious Free Dynamic Range                          |        |     |     |             |        |      |                              |

| MUX4:1                                                           |        |     |     |             |        |      |                              |

| Fs = 3 GSps @ Fout = 700 MHz 0 dBFS                              |        | 51  | 60  |             |        |      | 1,6                          |

| Fs = 3 GSps @ Fout = 1800 MHz 0 dBFS                             |        | 50  | 59  |             |        |      | 1,6                          |

|                                                                  | SFDR   |     |     |             | dBc    |      |                              |

| Fs = 3 GSps @ Fout = 700 MHz -3 dBFS                             |        | 55  | 61  |             |        |      | 1,6                          |

| MUX2:1                                                           |        |     |     |             |        |      |                              |

| Fs = 1.5 GSps @ Fout = 700 MHz 0 dBFS                            |        | 50  | 60  |             |        |      | 1,6                          |

| Highest spur level                                               |        |     |     |             |        |      |                              |

| MUX4:1                                                           |        |     |     |             |        |      |                              |

| Fs = 3 GSps @ Fout = 700 MHz 0 dBFS                              |        |     | -64 | <b>-</b> 55 |        |      | 1,6                          |

| Fs = 3 GSps @ Fout = 1800 MHz 0 dBFS                             |        |     | -63 | <b>-</b> 55 |        |      | 1,6                          |

|                                                                  |        |     |     |             | dBm    |      |                              |

| Fs = 3 GSps @ Fout = 700 MHz $-3$ dBFS                           |        |     | -67 | -60         |        |      | 1,6                          |

| MUX2:1                                                           |        |     |     |             |        |      |                              |

| Fs = 1.5 GSps @ Fout = 700 MHz 0 dBFS                            |        |     | -64 | -52         |        |      | 1,6                          |

| SFDR sensitivity & high spur level variation over power supplies |        |     | ±2  |             | dB     |      | 4                            |

| Signal independent Spur (clock-related spur)                     |        |     |     |             |        |      |                              |

| Fc                                                               |        |     | -29 |             | dBm    |      | 4                            |

| Fc/2                                                             |        |     | -80 |             | dBm    |      | 4                            |

| Fc/4                                                             |        |     | -80 |             | dBm    |      | 4                            |

| DAC self noise density at code 0 or 1023                         |        |     |     | -138        | dBm/Hz |      | 1,6                          |

Table 3-5. AC Electrical Characteristics NRTZ Mode (First & Second Nyquist Zone) (Continued)

| Parameter                                                                                                                                   | Symbol | Min | Тур | Max | Unit | Note | Test<br>level <sup>(1)</sup> |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|------|------------------------------|

| Noise Power Ratio  -14 dBFS peak to rms loading factor  Fs = 3 GSps  20 MHz to 900 MHz broadband pattern,  25 MHz notch centered on 450 MHz | NPR    | 44  | 46  |     | dB   | (2)  | 1,6                          |

| Equivalent ENOB Computed from NPR figure at 3 GSps                                                                                          | ENOB   | 8.8 | 9.2 |     | Bit  | (2)  | 1,6                          |

| Signal to Noise Ratio Computed from NPR figure at 3 GSps                                                                                    | SNR    | 55  | 57  |     | dB   | (2)  | 1,6                          |

Table 3-6.

AC Electrical Characteristics RTZ Mode (Second Nyquist Zone)

| Parameter                                                        | Symbol | Min | Тур | Max         | Unit   | Note | Test<br>level <sup>(1)</sup> |

|------------------------------------------------------------------|--------|-----|-----|-------------|--------|------|------------------------------|

| Single-tone Spurious Free Dynamic Range                          |        |     |     |             |        |      |                              |

| MUX4:1                                                           | SFDR   |     |     |             | dBc    |      |                              |

| Fs = 3 GSps @ Fout = 1600 MHz 0 dBFS                             | 1- 1   |     | 58  |             |        |      | 4                            |

| Fs = 3 GSps @ Fout = 2900 MHz 0 dBFS                             |        | 48  | 55  |             |        |      | 1,6                          |

| Highest spur level                                               |        |     |     |             |        |      |                              |

| MUX4:1                                                           |        |     |     |             | dBm    |      |                              |

| Fs = 3 GSps @ Fout =1600 MHz 0 dBFS                              |        |     | -66 |             | ubili  |      | 4                            |

| Fs = 3 GSps @ Fout = 2900 MHz 0 dBFS                             |        |     | -64 | <b>-</b> 56 |        |      | 1,6                          |

| SFDR sensitivity & high spur level variation over power supplies |        |     | ±2  |             | dB     |      | 4                            |

| Signal independent Spur (clock-related spur)                     |        |     |     |             |        |      |                              |

| Fc                                                               |        |     | -25 |             | dBm    |      | 4                            |

| Fc/2                                                             |        |     | -80 |             | dBm    |      | 4                            |

| Fc/4                                                             |        |     | -80 |             | dBm    |      | 4                            |

| DAC self noise density at code 0 or 1023                         |        |     |     | -139        | dBm/Hz |      | 1,6                          |

<sup>2.</sup> Figures in tables are derived from industrial screening; for practical reasons (necessity to cover also 2nd and 3rd Nyquist Zones) the balun used for industrial test is not optimum for first Nyquist performances, and results when Fout or folded low order hamonics are between DC to 400 MHz are very pessimistic.

Table 3-6.

AC Electrical Characteristics RTZ Mode (Second Nyquist Zone) (Continued)

| Parameter                                                                                                                                      | Symbol | Min | Тур | Max | Unit | Note | Test<br>level <sup>(1)</sup> |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|------|------------------------------|

| Noise Power Ratio  -14 dBFS peak to rms loading factor  Fs = 3 GSps  1520 MHz to 2200 MHz broadband pattern, 25 MHz notch centered on 1850 MHz | NPR    | 37  | 40  |     | dB   |      | 1,6                          |

| Equivalent ENOB  Computed from NPR figure at 3 GSps                                                                                            | ENOB   | 7.6 | 8.2 |     | Bit  |      | 1,6                          |

| Signal to Noise Ratio Computed from NPR figure at 3 GSps                                                                                       | SNR    | 48  | 51  |     | dB   |      | 1,6                          |

**Table 3-7.** AC Electrical Characteristics RF Mode (Second and Third Nyquist Zones)<sup>(2)</sup>

| Parameter                                                        | Symbol | Min | Тур | Max  | Unit   | Note | Test<br>level <sup>(1)</sup> |

|------------------------------------------------------------------|--------|-----|-----|------|--------|------|------------------------------|

| Single-tone Spurious Free Dynamic Range                          |        |     |     |      |        |      |                              |

| 2 <sup>nd</sup> Nyquist                                          |        |     |     |      |        |      |                              |

| Fs = 3 GSps @ Fout = 1600 MHz 0 dBFS                             |        | 42  | 50  |      |        |      | 1,6                          |

|                                                                  | SFDR   |     |     |      | dBc    |      |                              |

| 3 <sup>rd</sup> Nyquist                                          |        |     |     |      |        |      |                              |

| Fs = 3 GSps @ Fout = 3800 MHz 0 dBFS                             |        | 43  | 50  |      |        |      | 1,6                          |

| Fs = 3 GSps @ Fout = 4400 MHz 0 dBFS                             |        | 43  | 50  |      |        |      | 1,6                          |

| Highest spur level                                               |        |     |     |      |        |      |                              |

| 2 <sup>nd</sup> Nyquist                                          |        |     |     |      |        |      |                              |

| Fs = 3 GSps @ Fout = 1600 MHz 0 dBFS                             |        |     | -58 | -49  |        |      | 1,6                          |

|                                                                  |        |     |     |      | dBm    |      |                              |

| 3 <sup>rd</sup> Nyquist                                          |        |     |     |      |        |      |                              |

| Fs = 3 GSps @ Fout = 3800 MHz 0 dBFS                             |        |     | -60 | -51  |        |      | 1,6                          |

| Fs = 3 GSps @ Fout = 4400 MHz 0 dBFS                             |        |     | -60 | -54  |        |      | 1,6                          |

| SFDR sensitivity & high spur level variation over power supplies |        |     | ±2  |      | dB     |      | 4                            |

| Signal independent Spur (clock-related spur)                     |        |     |     |      |        |      |                              |

| Fc                                                               |        |     | -28 |      | dBm    |      | 4                            |

| Fc/2                                                             |        |     | -80 |      | dBm    |      | 4                            |

| Fc/4                                                             |        |     | -80 |      | dBm    |      | 4                            |

| DAC self noise density at code 0 or 1023                         |        |     |     | -138 | dBm/Hz |      | 1,6                          |

**Table 3-7.** AC Electrical Characteristics RF Mode (Second and Third Nyquist Zones)<sup>(2)</sup> (Continued)

| Parameter                                                                                                                                                               | Symbol | Min | Тур | Max | Unit | Note | Test<br>level <sup>(1)</sup> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|------|------------------------------|

| Noise Power Ratio (2 <sup>nd</sup> Nyquist)  -14 dBFS peak to rms loading factor Fs = 3 GSps  1520 MHz to 2200 MHz broadband pattern, 25 MHz notch centered on 1850 MHz | NPR    | 35  | 38  |     | dB   |      | 1,6                          |

| Equivalent ENOB Computed from NPR figure at 3 GSps                                                                                                                      | ENOB   | 7.3 | 7.8 |     | Bit  |      | 1,6                          |

| Signal to Noise Ratio Computed from NPR figure at 3 GSps                                                                                                                | SNR    | 46  | 49  |     | dB   |      | 1,6                          |

| Noise Power Ratio  -14 dBFS peak to rms loading factor  Fs = 3 GSps  2200 MHz to 2880 MHz broadband pattern,  25 MHz notch centered on 2550 MHz                         | NPR    | 35  | 38  |     | dB   |      | 1,6                          |

| Equivalent ENOB Computed from NPR figure at 3 GSps                                                                                                                      | ENOB   | 7.3 | 7.8 |     | Bit  |      | 1,6                          |

| Signal to Noise Ratio Computed from NPR figure at 3 GSps                                                                                                                | SNR    | 46  | 49  |     | dB   |      | 1,6                          |

| Noise Power Ratio  -14 dBFS peak to rms loading factor  Fs = 3 GSps  3050 MHz to 3700 MHz broadband pattern,  25 MHz notch centered on 3375 MHz                         | NPR    | 35  | 38  |     | dB   | (2)  | 1,6                          |

| Equivalent ENOB Computed from NPR figure at 3 GSps                                                                                                                      | ENOB   | 7.3 | 7.8 |     | Bit  | (2)  | 1,6                          |

| Signal to Noise Ratio Computed from NPR figure at 3 GSps                                                                                                                | SNR    | 46  | 49  |     | dB   | (2)  | 1,6                          |

<sup>2.</sup> Figures in tables are derived from industrial screening without any correction to take in account the balun effect, but for practical reasons (necessity to cover also 2nd and 3rd Nyquist Zones) the balun used for industrial test is not optimum for first Nyquist performances, and results when Fout or folded low order hamonics are between DC to 400 MHz are very pessimistic.

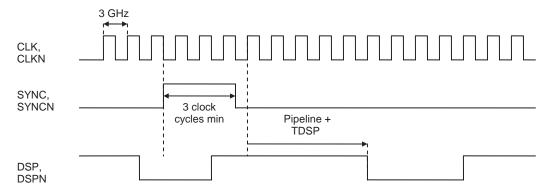

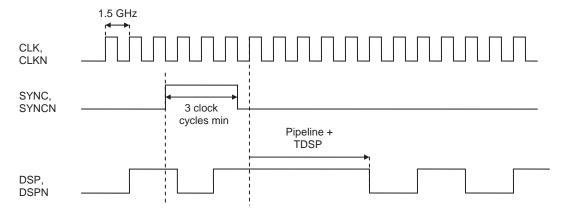

#### 3.5 **Timing Characteristics and Switching Performances**

**Table 3-8. Timing Characteristics and Switching Performances**

| Parameter                                     | Symbol                             | Min | Тур  | Max  | Unit         | Note   | Test<br>level <sup>(1)</sup> |

|-----------------------------------------------|------------------------------------|-----|------|------|--------------|--------|------------------------------|

| SWITCHING PERFORMANCE AND CHARACTERISTICS     |                                    |     |      |      |              |        |                              |

| Operating clock frequency                     |                                    |     |      |      |              |        |                              |

| 4:1 MUX mode                                  |                                    | 300 |      | 3000 | MHz          |        | 4                            |

| 2:1 MUX mode                                  |                                    | 300 |      | 1500 |              |        |                              |

| TIMING CHARACTERISTICS                        |                                    |     |      |      |              |        |                              |

| Analog output rise/fall time                  | T <sub>OR</sub><br>T <sub>OF</sub> |     | 60   |      | ps           | (2)    | 4                            |

| Data Tsetup (Fc = 3 Gsps)                     |                                    | 250 |      |      | ps           | (3)    | 4                            |

| Data Thold (Fc = 3 Gsps)                      |                                    | 100 |      |      | ps           | (3)    | 4                            |

| Max Input data rate (Mux 4:1)                 |                                    | 75  |      | 750  | MSps         |        | 4                            |

| Max Input data rate (Mux 2:1)                 |                                    | 150 |      | 750  | MSps         |        | 4                            |

| Master clock input jitter                     |                                    |     |      | 100  | fs rms       | (4)    | 5                            |

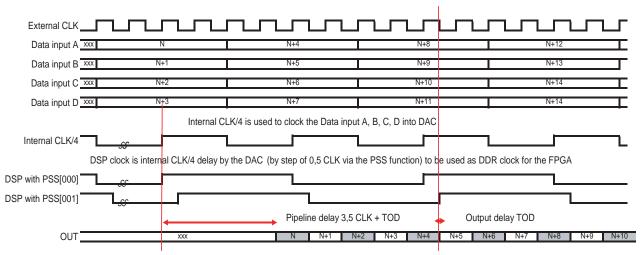

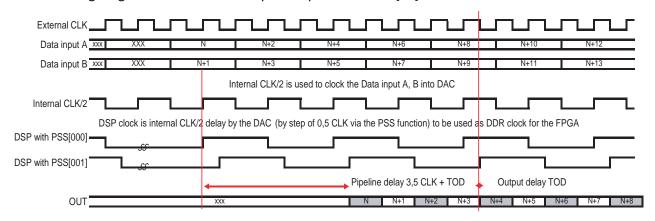

| DSP clock phase tuning steps                  |                                    |     | 0.5  |      | Clock period |        | 5                            |

| Master clock to DSP, DSPN delay               | TDSP                               |     | 1.6  |      | ns           |        | 4                            |

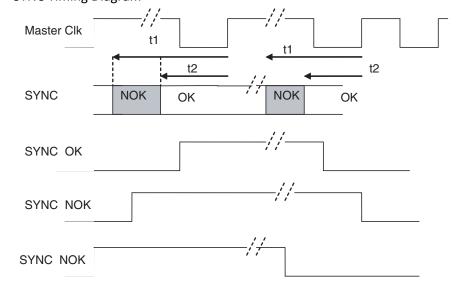

| SYNC forbidden area lower bound (Fc = 3 Gsps) | T <sub>1</sub>                     |     | 200  |      | ps           | (5)(6) | 4                            |

| SYNC forbidden area upper bound (Fc = 3 Gsps) | T <sub>2</sub>                     |     | 180  |      | ps           | (5)(6) | 4                            |

| SYNC to DSP, DSPN                             |                                    |     |      |      |              |        |                              |

| MUX 2:1                                       |                                    |     | 880  |      | ps           |        | 4                            |

| MUX4:1                                        |                                    |     | 1600 |      |              |        |                              |

| Data Pipeline Delay                           |                                    |     |      |      |              |        |                              |

| MUX4:1                                        | TPD                                |     | 3.5  |      | Clock period |        | 4                            |

| MUX2:1                                        |                                    |     | 3.5  |      |              |        |                              |

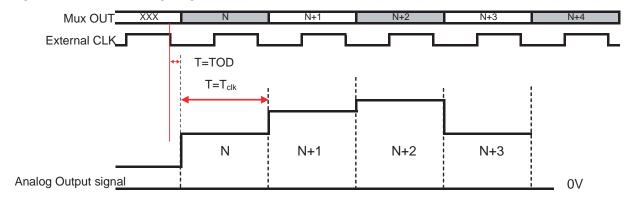

| Data Output Delay                             | TOD                                |     | 160  |      | ps           |        | 4                            |

- Notes: 1. See Section 3.6 on page 14 for explanation of the test level.

- 2. Analog output rise/fall time measured from 20% to 80% of a full scale jump, after probe de-embedding.

- 3. Exclusive of period (pp) jitter on Data. Setup and hold time for DATA at input relative to DSP clock at output of the component, at PSS = 000; also applicable for IDC signal.

- 4. Master clock input jitter defined over 5 GHz bandwidth.

- 5. T<sub>C</sub> represents the master clock period. See Figure 3-3.

- 6. For EV10DS130A, please refer to erratasheet 1125

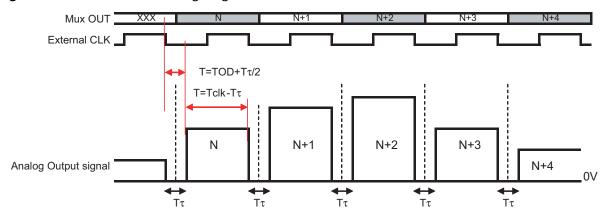

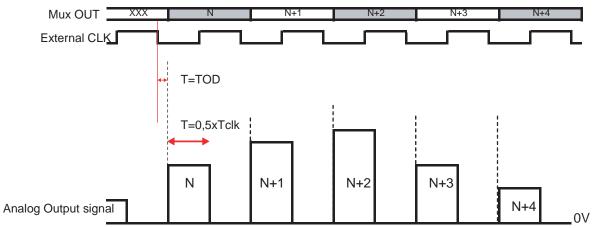

**Figure 3-1.** Timing Diagram for 4:1 MUX Principle of Operation OCDS[00]

Figure 3-2. Timing Diagram for 2:1 MUX Principle of Operation OCDS[00]

Figure 3-3. SYNC Timing Diagram

Please refer to Section 5.9 "Synchronization Functions for Multi-DAC Operation" on page 30.

# 3.6 Explanation of Test Levels

| 1 | 100% production tested at +25°C <sup>(1)</sup>                                                                                |

|---|-------------------------------------------------------------------------------------------------------------------------------|

| 2 | 100% production tested at +25°C <sup>(1)</sup> , and sample tested at specified temperatures.                                 |

| 3 | Sample tested only at specified temperatures                                                                                  |

| 4 | Parameter is guaranteed by design and/or characterization testing (thermal steady-state conditions at specified temperature). |

| 5 | Parameter value is only guaranteed by design                                                                                  |

| 6 | 100% production tested over specified temperature range (for Space/Mil grade <sup>(2)</sup> )                                 |

Only MIN and MAX values are guaranteed.

Notes: 1. Unless otherwise specified.

2. If applicable, please refer to "Ordering Information"

# 3.7 Digital Input Coding Table

**Table 3-9.** Coding Table

| Digital output MSBLSB | Differential analog output |

|-----------------------|----------------------------|

| 000000000             | –500 mV                    |

| 010000000             | −250 mV                    |

| 011000000             | −125 mV                    |

| 100000000             | 0 mV                       |

| 101000000             | +125 mV                    |

| 110000000             | +250 mV                    |

| 111111111             | +500 mV                    |

# 4. **DEFINITION OF TERMS**

| Abbreviation | Term                            | Definition                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Fs max)     | Maximum conversion<br>Frequency | Maximum conversion frequency                                                                                                                                                                                                                                                                                                                                                                                              |

| (Fs min)     | Minimum conversion frequency    | Minimum conversion Frequency                                                                                                                                                                                                                                                                                                                                                                                              |

| (SFDR)       | Spurious free dynamic range     | Ratio expressed in dB of the RMS signal amplitude, set at Full Scale, to the RMS value of the highest spectral component (peak spurious spectral component). The peak spurious component may or may not be a harmonic. It may be reported in dB (i.e., related to converter 0 dB Full Scale), or in dBc (i.e, related to input signal level).                                                                             |

| (HSL)        | High Spur Level                 | Power of highest spurious spectral component expressed in dBm.                                                                                                                                                                                                                                                                                                                                                            |

| (ENOB)       | Effective Number Of Bits        | ENOB is determinated from NPR measurement with the formula:                                                                                                                                                                                                                                                                                                                                                               |

| (SNR)        | Signal to noise ratio           | SNR is determinated from NPR measurement with the formula: $ {\sf SNR}_{\sf [dB]} = {\sf NPR}_{\sf [dB]} + {\sf ^1_{\sf LF}}_{\sf [dB]} {\sf ^1_{\sf -3}} $ Where LF "Loading factor" is the ratio between the Gaussian noise standard deviation versus amplitude full scale.                                                                                                                                             |

| (DNL)        | Differential non linearity      | The Differential Non Linearity for an given code i is the difference between the measured step size of code i and the ideal LSB step size. DNL (i) is expressed in LSBs. DNL is the maximum value of all DNL (i). DNL error specification of less than 1 LSB guarantees that there are no missing point and that the transfer function is monotonic.                                                                      |

| (INL)        | Integral non linearity          | The Integral Non Linearity for a given code i is the difference between the measured voltage at which the transition occurs and the ideal value of this transition.  INL (i) is expressed in LSBs, and is the maximum value of all  INL (i) .                                                                                                                                                                             |

| (TPD/TOD)    | Output delay                    | The analog output propagation delay measured between the rising edge of the differential CLK, CLKN clock input (zero crossing point) and the zero crossing point of a full-scale analog output voltage step. TPD corresponds to the pipeline delay plus an internal propagation delay (TOD) including package access propagation delay and internal (on-chip) delays such as clock input buffers and DAC conversion time. |

| (NPR)        | Noise Power Ratio               | The NPR is measured to characterize the DAC performance in response to broad bandwidth signals. When applying a notch-filtered broadband white-noise pattern at the input to the DAC under test, the Noise Power Ratio is defined as the ratio of the average noise measured on the shoulder of the notch and inside the notch on the same integration bandwidth.                                                         |

| (VSWR)       | Voltage Standing Wave Ratio     | The VSWR corresponds to the insertion loss linked to power reflection. For example a VSWR of 1:2 corresponds to a 20dB return loss (ie. 99% power transmitted and 1% reflected).                                                                                                                                                                                                                                          |

| (IUCM)       | Input under clocking mode       | The IUCM principle is to apply a selectable division ratio between DAC section clock and the MUX section clock.                                                                                                                                                                                                                                                                                                           |

| (PSS)        | Phase Shift Select              | The Phase Shift Select function allow to tune the phase of the DSPclock.                                                                                                                                                                                                                                                                                                                                                  |

| (OCDS)       | Output Clock Division Selectt   | It allows to divide the DSPclock frequency by the OCDS coded value factor                                                                                                                                                                                                                                                                                                                                                 |

| (NRZ)        | Non Return to Zero mode         | Non Return to Zero mode on analog output                                                                                                                                                                                                                                                                                                                                                                                  |

| (RF)         | Radio Frequency mode            | RF mode on analog output                                                                                                                                                                                                                                                                                                                                                                                                  |

| (RTZ)        | Return to zero                  | Return to zero mode                                                                                                                                                                                                                                                                                                                                                                                                       |

| (NRTZ)       | Narrow return to zero           | Narrow return to zero mode                                                                                                                                                                                                                                                                                                                                                                                                |

# 5. FUNCTIONAL DESCRIPTION

Figure 5-1. DAC Functional Diagram

**Table 5-1.** Functions Description

| Name              | Function                                    | Name         | Function                                           |

|-------------------|---------------------------------------------|--------------|----------------------------------------------------|

| V <sub>CCD</sub>  | 3.3V Digital Power Supply                   | CLK          | In-phase Master clock                              |

| V <sub>CCA5</sub> | 5.0V Analog Power Supply                    | CLKN         | Inverted phase Master clock                        |

| V <sub>CCA3</sub> | 3.3V Analog Power Supply                    | DSP_CK       | In-phase Output clock                              |

| DGND              | Digital Ground                              | DSP_CKN      | Inverted phase Output clock                        |

| AGND              | Analog ground (for analog supply reference) | PSS[02]      | Phase shift select                                 |

| A[90]             | In-phase digital input Port A               | GA           | Gain Adjust                                        |

| A[90]N            | Inverted phase digital input Port A         | MUX          | MUX Selection                                      |

| B[90]             | In-phase digital input Port B               | MODE[01]     | DAC Mode: NRZ, RTZ, NRTZ, RF                       |

| B[90]N            | Inverted phase digital input Port B         | STVF         | Setup time Violation flag                          |

| C[90]             | In-phase digital input Port C               | HTVF         | Hold time Violation flag                           |

| C[90]N            | Inverted phase digital input Port C         | IDC_P, IDC_N | Input data check                                   |

| D[90]             | In-phase digital input Port D               | OCDS[01]     | Output Clock Division factor Selection (by 4 or 8) |

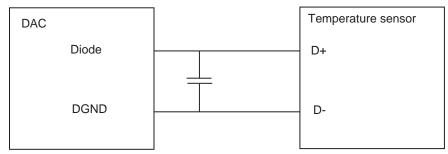

| D[90]N            | Inverted phase digital input Port D         | Diode        | Diode for temperature monitoring                   |

| OUT               | In-phase analog output                      | SYNC/SYNCN   | Synchronization signal (Active High)               |

| OUTN              | Inverted phase analog output                | IUCM         | Input underclocking mode                           |

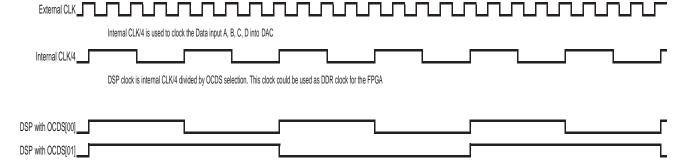

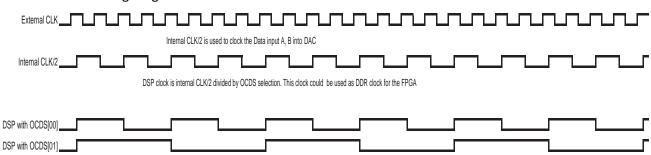

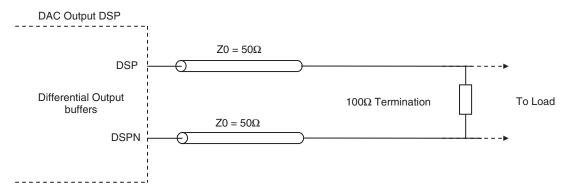

#### 5.1 DSP Output Clock

The DSP output clock DSP, DSPN is an LVDS signal which is used to synchronize the FPGA generating the digital patterns with the DAC sampling clock.

The DSP clock frequency is a fraction of the sampling clock frequency. The division factor depends on OCDS settings. The DSP clock frequency is equal to (sampling frequency / [2N\*X]) where N is the MUX ratio and X is the output clock division factor, determined by OCDS[0..1] bits.

For example, in a 4:1 MUX ratio application with a sampling clock of 3 GHz and OCDS set to "00" (ie. Factor of 1), the input data rate is 750 MSps and the DSP clock frequency is 375 MHz.

This DSP clock is used in the FPGA to control the digital data sequencing. Its phase can be adjusted using the PSS[2:0] bits (refer to Section 5.5 on page 25) in order to ensure a proper synchronization between the data coming to the DAC and the sampling clock.

The HTVF and STVF bits should be used to check whether the timing between the FPGA and the DAC is correct. HTVF and STVF bits will indicate whether the DAC and FPGA are aligned or not. PSS bits should then be used to shift the DSP clock and thus the input data of the DAC, so that a correct timing is achieved between the FPGA and the DAC.

Important note: Maximum supported sampling frequency when using DSP to clock digital data is 2.1 Gsps on EV10DS130B. Please refer to application note AN1141 to use EV10DS130B at sampling frequency beyond 2.1 GHz.

#### 5.2 Multiplexer

Two multiplexer ratio are allowed:

- 4:1, which allows operation at full sampling rate (ie. 3 GHz)

- 2:1, which can only be used up to 1.5 GHz sampling rate, except in IUCM mode

| Label | Value | Description |

|-------|-------|-------------|

|       | 0     | 4:1 mode    |

| MUX   | 1     | 2:1 mode    |

In 2:1 MUX ratio, the unused data ports (ports C and D) can be left open.

# 5.3 MODE Function

| Label     | Value | Description                   | Default Setting (Not Connected) |  |

|-----------|-------|-------------------------------|---------------------------------|--|

|           | 00    | NRZ mode                      |                                 |  |

|           | 01    | Narrow RTZ (a.k.a. NRTZ) mode | 11                              |  |

| MODE[1:0] | 10    | RTZ Mode (50%)                | RF mode                         |  |

|           | 11    | RF mode                       |                                 |  |

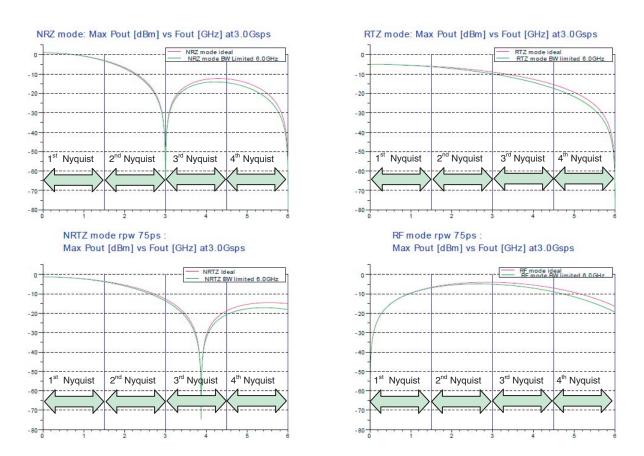

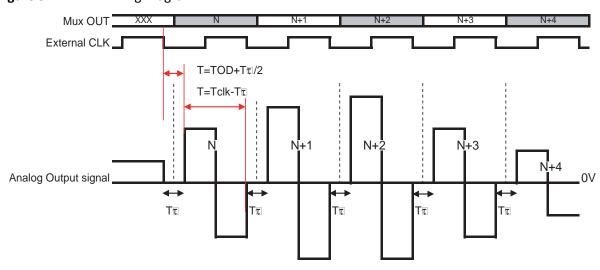

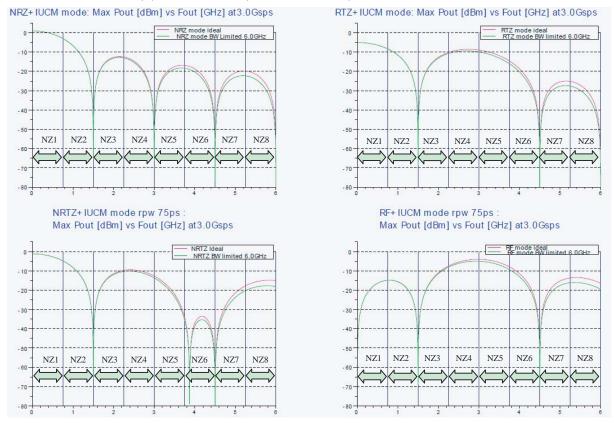

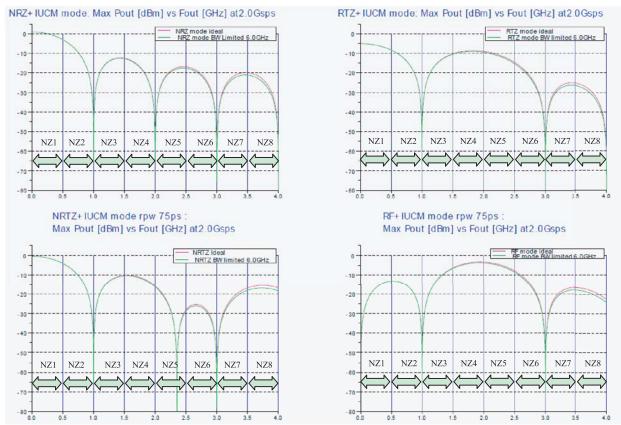

The MODE function allows choosing between NRZ, NRTZ, RTZ and RF functions. NRZ and narrow RTZ should be chosen for use in 1<sup>st</sup> Nyquist zone while RTZ should be chosen for use in 2<sup>nd</sup> and RF for 3<sup>rd</sup> Nyquist zones.

Theory of operation: see following subsections for time domain waveform of the different modes.

Ideal equations describing max available Pout for frequency domain in the four modes are given hereafter, with X = normalised output frequency (that is Fout/Fclock, edges of Nyquist zones are then at X = 0, 1/2, 1, 3/2, 2, ...).

Due to limited bandwidth, an extra term must be added to take in account a first order low pass filter.

#### NRZ mode:

$$Pout(X) = 20 \cdot log_{10} \cdot \left[ \frac{|k \cdot sinc(k \cdot \pi \cdot X)|}{0.893} \right]$$

where sinc(x) = sin(x)/x, and k = 1

#### NRTZ mode:

$$\text{Pout}(\textbf{X}) \, = \, 20 \cdot \text{log}_{10} \cdot \left[ \frac{|\textbf{k} \cdot \text{sinc}(\textbf{k} \cdot \boldsymbol{\pi} \cdot \textbf{X})|}{0.893} \right] \hspace{1cm} \textbf{k} \, = \, \frac{\text{Tclk} - T\tau}{\text{Tclk}}$$

where  $T\tau$  is width of reshaping pulse,  $T\tau$  is about 75ps.

#### RTZ mode:

$$Pout(X) = 20 \cdot log_{10} \cdot \left[ \frac{|k \cdot sinc(k \cdot \pi \cdot X)|}{0.893} \right]$$

where k is the duty cycle of the clock presented at the DAC input, please note that due to phase mismatch in balun used to convert single ended clock to differential clock the first zero may move around the limit of the  $4^{th}$  and the  $5^{th}$  Nyquist zones. Ideally k = 1/2.

#### RF mode:

$$Pout(X) = 20 \cdot log_{10} \cdot \left\lceil \frac{k \cdot sinc(\frac{k \cdot \pi \cdot X}{2}) \cdot sin(\frac{k \cdot \pi \cdot X}{2})}{0.893} \right\rceil$$

where k is as per in NRTZ mode.

As a consequence:

- NRZ mode offers max power for 1<sup>st</sup> Nyquist operation

- RTZ mode offers slow roll off for 2<sup>nd</sup> Nyquist or 3<sup>rd</sup> Nyquist operation

- RF mode offers maximum power over 2<sup>nd</sup> and 3<sup>rd</sup> Nyquist operation

- NRTZ mode offers optimum power over full 1<sup>st</sup> and first half of 2<sup>nd</sup> Nyquist zones. This is the most relevant in term of performance for operation over 1<sup>st</sup> and beginning of 2<sup>nd</sup> Nyquist zone, depending on the sampling rate the zero of transmission moves in the 3<sup>rd</sup> Nyquist zone from begin to end when sampling rate increases.

Note in the two following figures: Pink line is ideal equation's result, and green line includes a first order 6 GHz cut-off low pass filter to take in account finite bandwidth effect due to die and package.

**Figure 5-2.** Max available Pout[dBm] at nominal gain vs Fout[GHz] in the four output modes at 3 GSps, over four nyquist zones, computed for  $T\tau = 75$  ps.

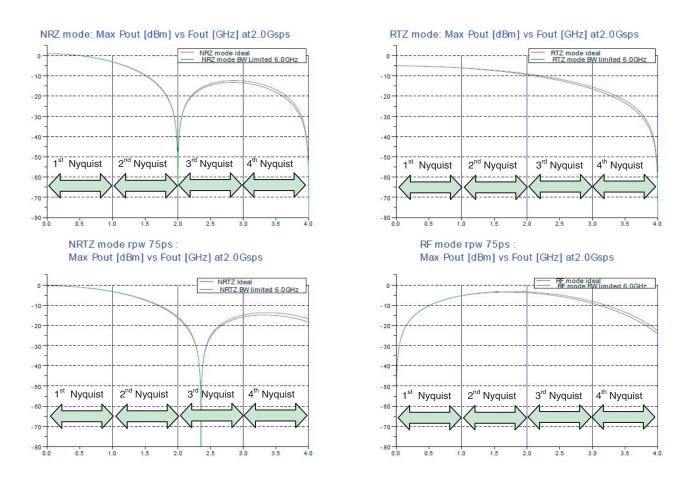

**Figure 5-3.** Max available Pout[dBm] at nominal gain vs Fout[GHz] in the four output modes at 2 GSps, over four nyquist zones, computed for  $T\tau = 75$  ps

#### 5.3.1 NRZ Output Mode

This mode does not allow for operation in the  $2^{nd}$  Nyquist zone because of the Sin(x)/x notch.

The advantage is that it gives good results at the beginning of the 1<sup>st</sup> Nyquist zone (less attenuation than in RTZ architecture), it removes the parasitic spur at the clock frequency (in differential).

# 5.3.2 Narrow RTZ (NRTZ) Mode

This mode has the following advantages:

- Optimized power in 1st Nyquist zone

- Extended dynamic through elimination of noise on transition edges

- Improved spectral purity

- Trade off between NRZ and RTZ

Figure 5-5. Narrow RTZ Timing Diagram

Note:  $T\tau$  is independant of Fclock.

#### 5.3.3 RTZ Mode

The advantage of the RTZ mode is to enable the operation in the 2<sup>nd</sup> zone but the drawback is a highest attenuation of the signal in the first Nyquist zone.

# Advantages:

- Extended roll off of sinc

- Extended dynamic through elimination of noise on transition edges

#### Weakness:

• By construction clock spur at Fs.

Figure 5-6. RTZ Timing Diagram

#### 5.3.4 RF Mode

RF mode is optimal for operation at high output frequency, since the decay with frequency occurs at higher frequency than for RTZ. Unlike NRZ or RTZ modes, RF mode presents a notch at DC and 2N\*Fs, and minimum attenuation for Fout = Fs.

## Advantages:

- Optimized for 2<sup>nd</sup> and 3<sup>rd</sup> Nyquist operation

- Extended dynamic range through elimination of noise on transition edges.

- Clock spur pushed to 2.Fs

Figure 5-7. RF Timing Diagram

Note: The central transition is not hazardous but its elimination allows to push clock spur to 2.Fs  $T\tau$  is independant of Fclock.

# 5.4 Input Under Clocking Mode (IUCM), Principle and Spectral Response

An Input Under Clocking Mode has been added to the DAC in order to allow the DAC input data rate to be at half the nominal rate with respect of the DAC sampling rate.

When the under clocking mode is activated, the DAC expects data at half the nominal rate: if the DAC works at Fs sampling rate, then in 4:1 MUX mode, the input data rate should be Fs/4 and the DSP clock should be Fs/(2N\*OCDS), with N = MUX ratio and OCDS = OCDS Ratio.

When the IUCM is active, the input data rate can be Fs/8 and the DSP clock frequency is Fs/(2N\*OCDS\*2), with N = MUX ratio and OCDS = OCDS Ratio. This means that in input under clocking mode, the DAC is capable to treat data at half the nominal rate. In this case, the DSP clock is also half its nominal speed.

| Label | Logic Value | Description                        |

|-------|-------------|------------------------------------|

| HIGNA | 0           | Input Under Clocking Mode inactive |

| IUCM  | 1           | Input Under Clocking Mode active   |

To disable this mode, the IUCM pin must be connected to GND.

To enable this mode, IUCM must be connected to V<sub>CCD</sub> or left unconnected

The IUCM mode affects spectral response of the different modes.

The first effect is that Nyquist zone edges are not anymore at n\*Fclock/2 but at n\*/Fclock/4 (direct consequence of the division by 2 of the data rate).

The second effect is the modification of the equations ruling the spectral responses in the different modes.

Ideal equations describing max available Pout for frequency domain in the four output modes when IUCM mode is activated are given hereafter, with X= normalised output frequency (that is Fout/Fclock, edges of Nyquist Zones are then at X=0, 1/4, 1/2, 3/4, 1, ...)

In fact due to limited bandwidth, an extra term must be added to take in account a first order low pass filter with a 6 GHz cut-off frequency.

#### NRZ mode:

$$Pout(X) = 20 \cdot log_{10} \cdot \left[ \frac{|k \cdot sinc(k \cdot \pi \cdot X) \cdot cos(\pi \cdot X)|}{0.893} \right]$$

where sinc(x) = sin(x)/x, and k = 1

# NRTZ mode:

$$Pout(X) \ = \ 20 \cdot log_{10} \cdot \left[ \frac{\left| k \cdot sinc(k \cdot \pi \cdot X) . cos(\pi \cdot X) \right|}{0.893} \right] \\ k \ = \ \frac{Tclk - T\tau}{Tclk}$$

where  $T\tau$  is width of reshaping pulse,  $T\tau$  is about 75ps.

#### RTZ mode:

$$Pout(X) = 20 \cdot log_{10} \cdot \left[ \frac{\left| k \cdot sinc(k \cdot \pi \cdot X) . cos(\pi \cdot X) \right|}{0.893} \right]$$

where k is the duty cycle of the clock presented at the DAC input, please note that due to phase mismatch in balun used to convert single ended clock to differential clock the first zero may move around the limit of the  $4^{th}$  and the  $5^{th}$  Nyquist zones. Ideally k = 1/2.

#### RF mode:

$$\text{Pout(X)} = 20 \cdot \log_{10} \cdot \left\lceil \frac{\left| k \cdot \text{sinc}\left(\frac{k \cdot \pi \cdot X}{2}\right) \cdot \text{sin}\left(\frac{k \cdot \pi \cdot X}{2}\right) \cdot \cos(\pi \cdot X) \right|}{0.893} \right\rceil$$

where k is as per in NRTZ mode.

**Figure 5-8.** Max available Pout[dBm] at nominal gain vs Fout[GHz] in the four output modes at 3 GSps, combined with IUCM, over four nyquist zones, computed for  $T\tau$  =75 ps.

**Figure 5-9.** Max available Pout[dBm] at nominal gain vs Fout[GHz] in the four output modes at 2 GSps, combined with IUCM, over four nyquist zones, computed for  $T\tau = 75$  ps

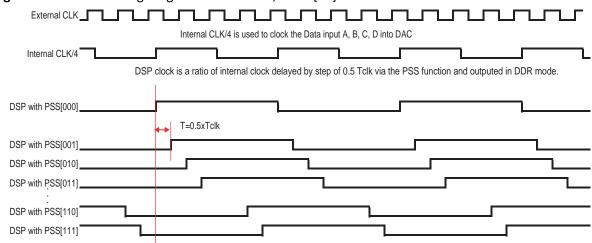

#### 5.5 PSS (Phase Shift Select Function)

It is possible to adjust the timings between the sampling clock and the DSP output clock (which frequency is given by the following formula: Sampling clock / 2NX where N is the MUX ratio, X the output clock division factor).

The DSP clock output phase can be tuned over a range of 3.5 input clock cycles (7 steps of half a clock cycle) in addition to the intrinsic propagation delay between the DSP clock (DSP, DSPN) and the sampling clock (CLK, CLKN).

Three bits are provided for the phase shift function: PSS[2:0].

By setting these 3 bits to 0 or 1, one can add a delay on the DSP clock in order to properly synchronize the input data of the DAC and the sampling clock (the DSP clock should be applied to the FPGA and should be used to clock the DAC digital input data).

**Table 5-2.** PSS Coding Table

| Label    | Value | Description                               |

|----------|-------|-------------------------------------------|

|          | 000   | No additional delay on DSP clock          |

|          | 001   | 0.5 input clock cycle delay on DSP clock  |

|          | 010   | 1 input clock cycle delay on DSP clock    |

| DCC[2.0] | 011   | 1.5 input clock cycle delay on DSP clock  |

| PSS[2:0] | 100   | 2 input clock cycles delay on DSP clock   |

|          | 101   | 2.5 input clock cycles delay on DSP clock |

|          | 110   | 3 input clock cycles delay on DSP clock   |

|          | 111   | 3.5 input clock cycles delay on DSP clock |

In order to determine how much delay needs to be added on the DSP clock to ensure the synchronization between the input data and the sampling clock within the DAC, the HTVF and STVF bits should be monitored. Refer to Section 5.7 on page 28.

Note: In MUX 4:1 mode the 8 settings are relevant, in MUX 2:1 only the four first settings are relevant since the four last ones will yield exactly the same results.

**Figure 5-10.** PSS Timing Diagram for 4:1 MUX, OCDS[00]

Figure 5-11. PSS Timing Diagram for 2:1 MUX, OCDS[00]

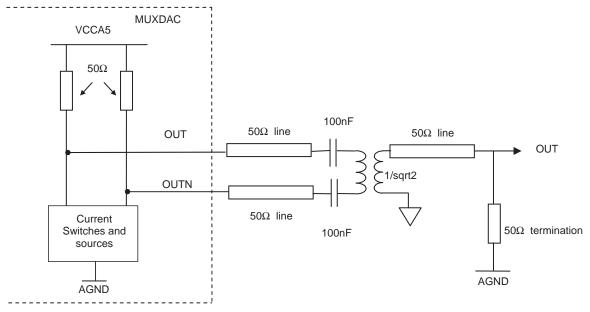

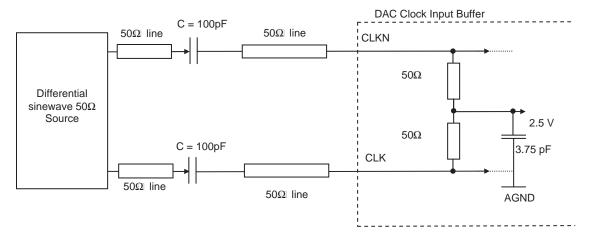

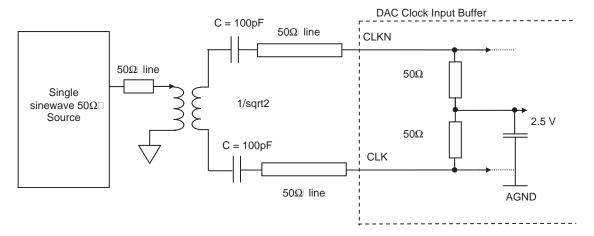

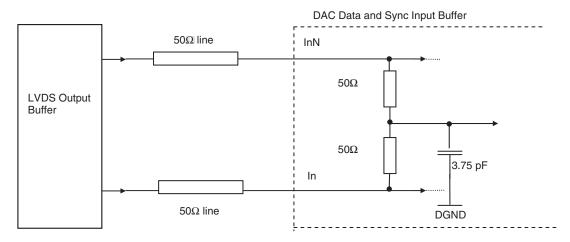

External CLK Internal CLK/2 is used to clock the Data input A, B into DAC