| OKI NETWORK PRODUC <sup>-</sup> | ΤS |

|---------------------------------|----|

|---------------------------------|----|

# ML53301/ML53311 TC-622Pro/Pro+ ATM Framer

December 1999

#### **Revision Information**

December 1999 Stock No. 320120-002

Typographical errors corrected:

Signal symbol corrected to "tSTSC" in table 7 on page 73.

Signal symbol corrected to "tHTXD" in table 7 on page 73.

Extraneous parameter "Receive frame hold from RxCLK high" deleted from table 8 on page 74.

Signal symbol corrected to "tHTLD" in table 9 on page 75.

Signal symbol corrected to "tHRFRM" in table 10 on page 76.

Signal symbol corrected to "tPARHLD" in table 19 on page 88.

# CONTENTS

| 1. Description                         | 1  |

|----------------------------------------|----|

| 2. Features                            | 1  |

| 3. KEY Features                        | 3  |

| 3.1 Transmit Test Cell Generator       |    |

| 3.2 Receive Test Cell Analyzer         | 3  |

| 3.3 Transmit Cell Processor            |    |

| 3.4 Receive Cell Processor             | 3  |

| 3.5 STS-12/12c Line Interface          | 4  |

| 3.6 STS-12/12c Transmit Framer         | 4  |

| 3.7 STS-12/12c Receive Framer          |    |

| 3.8 PCI Bus Interface (TC-622Pro)      | 5  |

| 3.9 MPI Bus Interface (TC-622Pro+)     | 5  |

| 3.10 Transmit and Receive UTOPIA       | 5  |

| 4. Functional Description              | 6  |

| 4.1 Architectural Overview             |    |

| Transmit Framer and Overhead Processor |    |

| Transmit Cell Processors               |    |

| Transmit UTOPIA                        |    |

| Test Cell Generator                    |    |

| Receive Framer and Overhead Processor  |    |

| Receive Cell Processors                |    |

| Test Cell Analyzer                     |    |

| Receive UTOPIA                         |    |

| PCI Bus Interface (TC-622Pro)          |    |

| MPI Bus Interface (TC-622Pro+)         |    |

| 4.2 Transmit Architecture              |    |

| Transmit Data Flow                     | 9  |

| Transmit UTOPIA PHY                    | 10 |

| Transmit Cell Processor                |    |

| Test Cell Generator                    |    |

| Transmit Framer And Overhead Processor | 13 |

| 4.3 Receive Architecture               | 14 |

| Receive Data Flow                      | 15 |

| Receive Framer And Overhead Processor  |    |

| Receive Cell Processor                 | 22 |

| Test Cell Analyzer                     | 23 |

| Receive UTOPIA Phy                     |    |

| 4.4 PCI Bus Architecture (TC-622Pro)   |    |

| 4.5 MPI Bus Architecture (TC-622Pro+)  |    |

| 5. Signal Descriptions                 |    |

| Registers                                                                       |  |

|---------------------------------------------------------------------------------|--|

| 5.2 Receive B1 Error Count (default = 0xFFFC) Read Only                         |  |

| 5.3 Receive B2 Error Count (default = 0xFFFC) Read Only                         |  |

| 6.4 Receive B2 Error Count 3 (default = 0xFFFC) Read Only                       |  |

| 6.5 Receive B3 Error Count 2 (default = 0xFFFC) Read Only                       |  |

| 6.6 Receive B3 Error Count 1 (default = 0xFFFC) Read Only                       |  |

| 5.7 Receive B3 Error Count 0 (default = 0xFFFC) Read Only                       |  |

| b.8 Test Cell Analyzer 3 Error Count (default = 0xFFFC) Read Only               |  |

| 5.9 Test Cell Analyzer 2 Error Count (default = 0xFFFC) Read Only               |  |

| 5.10 Test Cell Analyzer 1 Error Count (default = 0xFFFC) Read Only              |  |

| 5.11 Test Cell Analyzer 0 Error Count (default = 0xFFFC) Read Only              |  |

| 0.12 Received Line FEBE Accumulator (default = 0xFFFC) Read Only                |  |

| .13 Received Path FEBE Accumulator 3 (default = 0xFFFC) Read Only               |  |

| 5.14 Received Path FEBE Accumulator 2 (default = 0xFFFC) Read Only              |  |

| 6.15 Received Path FEBE Accumulator 1 (default = 0xFFFC) Read Only              |  |

| 5.16 Received Path FEBE Accumulator 1 (default = 0xFFFC) Read Only              |  |

| 6.17 Test Cell Generator 3 Transmitted Cells Count (default = 0xFFFC) Read Only |  |

| 5.18 Test Cell Generator 2 Transmitted Cells Count (default = 0xFFFC) Read Only |  |

| 5.19 Test Cell Generator 1 Transmitted Cells Count (default = 0xFFFC) Read Only |  |

| 5.20 Test Cell Generator 0 Transmitted Cells Count (default = 0xFFFC) Read Only |  |

| 5.21 Test C ell Analyzer 3 Received Cells Count (default = 0xFFFC) Read Only    |  |

| 5.22 Test Cell Analyzer 2 Received Cells Count (default = 0xFFFC) Read Only     |  |

| 5.23 Test Cell Analyzer 1 Received Cells Count (default = 0xFFFC) Read Only     |  |

| 5.24 Test Cell Analyzer 0 Received Cells Count (default = 0xFFFC) Read Only     |  |

| 5.25 Assigned Cells Transmitted Count 3 (default = 0xFFFC) Read Only            |  |

| 5.26 Assigned Cells Transmitted Count 2 (default = 0xFFFC) Read Only            |  |

| 5.27 Assigned Cells Transmitted Count 1 (default = 0xFFFC) Read Only            |  |

| 6.28 Assigned Cells Transmitted Count 0 (default = 0xFFFC) Read Only            |  |

| 5.29 Idle Cells Transmitted Count 3 (default = 0xFFFC) Read Only                |  |

| 5.30 Idle Cells Transmitted Count 2 (default = 0xFFFC) Read Only                |  |

| 5.31 Idle Cells Transmitted Count 1 (default = 0xFFFC) Read Only                |  |

| 5.32 Idle Cells Transmitted Count 0 (default = 0xFFFC) Read Only                |  |

| 6.33 Assigned Cells Received Count 3 (default = 0xFFFC) Read Only               |  |

| 6.34 Assigned Cells Received Count 2 (default = 0xFFFC) Read Only               |  |

| 6.35 Assigned Cells Received Count 1 (default = 0xFFFC) Read Only               |  |

| 5.36 Assigned Cells Received Count 0 (default = 0xFFFC) Read Only               |  |

| 5.37 Idle Cells Received Count 3 (default = 0xFFFC) Read Only                   |  |

| 5.38 Idle Cells Received Count 2 (default = 0xFFFC) Read Only                   |  |

| 5.39 Idle Cells Received Count 1 (default = 0xFFFC) Read Only                   |  |

| 5.40 Idle Cells Received Count 0 (default = 0xFFFC) Read Only                   |  |

| 5.41 Cell Discard Count 3 (default = 0xFFFC) Read Only                          |  |

| 6.42 Cell Discard Count 2 (default = 0xFFFC) Read Only                          |  |

| 6.43 Cell Discard Count 1 (default = 0xFFFC) Read Only                          |  |

| 6.44 Cell Discard Count 0 (default = 0xFFFC) Read Only                          |  |

| (450) $(-100)$ $(-100)$ $(-100)$ $(-100)$ $(-100)$ $(-100)$                                                                         | 40 |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.45 Signal Mismatch Count 3 (default = 0x0006) Read Only                                                                           |    |

| 6.46 Signal Mismatch Count 2 (default = 0x0006) Read Only                                                                           |    |

| 6.47 Signal Mismatch Count 1 (default = 0x0006) Read Only                                                                           |    |

| 6.48 Signal Mismatch Count 0 (default = 0x0006) Read Only                                                                           |    |

| <ul><li>6.49 Received Pointer 3 (default = 0x0000) Read Only</li><li>6.50 Received Pointer 2 (default = 0x0000) Read Only</li></ul> |    |

|                                                                                                                                     |    |

| <ul><li>6.51 Received Pointer 1 (default = 0x0000) Read Only</li><li>6.52 Received Pointer 0 (default = 0x0000) Read Only</li></ul> |    |

| 6.53 Received Fointer 0 (default = 0x0000) Read Only                                                                                |    |

| 6.55 Received K1 and K2 Bytes (default = 0x0000) Read Only                                                                          |    |

| 6.55 Receiver Alarms Register 2 (default = 0x0F00) Read Only                                                                        |    |

| 6.56 Transmit Test Cell 3 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                        |    |

|                                                                                                                                     |    |

| 6.57 Transmit Test Cell 2 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                        |    |

| 6.58 Transmit Test Cell 1 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                        |    |

| 6.59 Transmit Test Cell 0 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                        |    |

| 6.60 Transmit Test Cell 3 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                        |    |

| 6.61 Transmit Test Cell 2 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                        |    |

| 6.62 Transmit Test Cell 1 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                        |    |

| 6.63 Transmit Test Cell 0 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                        |    |

| 6.64 Receive Test Cell 3 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                         |    |

| 6.65 Receive Test Cell 2 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                         |    |

| 6.66 Receive Test Cell 1 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                         |    |

| 6.67 Receive Test Cell 0 Header Bytes 1 and 2 (default = 0x0000) Read/Write                                                         |    |

| 6.68 Receive Test Cell 3 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                         |    |

| 6.69 Receive Test Cell 2 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                         |    |

| 6.70 Receive Test Cell 1 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                         |    |

| 6.71 Receive Test Cell 0 Header Bytes 3 and 4 (default = 0x0000) Read/Write                                                         |    |

| 6.72 User Commands To UTOPIA (default = 0x0000) Read/Write                                                                          |    |

| 6.73 UTOPIA 3 Address Register (default = 0x0063) Read/Write                                                                        |    |

| 6.74 UTOPIA 2 Address Register (default = 0x0042) Read/Write                                                                        |    |

| 6.75 UTOPIA 1 Address Register (default = 0x0021) Read/Write                                                                        |    |

| 6.76 UTOPIA 0 Address Register (default = 0x0000) Read/Write                                                                        |    |

| 6.77 TxUTOPIA FIFO Status Register (default = 0x0000) Read Only                                                                     |    |

| 6.78 TxUTOPIA Cell Drop Status Register (default = 0x0000) Read Only                                                                |    |

| 6.79 Receive Cell Processor User Commands (default = 0x000F) Read/Write                                                             |    |

| 6.80 Transmit Framer User Commands (default = 0x0000) Read/Write                                                                    |    |

| 6.81 Transmit Cell Processor User Commands (default = 0x00F0) Read/Write                                                            |    |

| 6.82 Parity Error Roll-Over (default = 0x0000) Read/Write/Set                                                                       |    |

| 6.83 Receiver Alarm Roll-Over (default = 0x0000) Read/Write/Set                                                                     |    |

| 6.84 Test Cell Count Roll-over (default = 0x0000) Read/Write/Set                                                                    |    |

| 6.85 Transmit/Receive Count Roll-over (default = 0x0000) Read/Write/Set                                                             |    |

| 6.86 Interrupt Mask Register (default = 0x0000) Read/Write                                                                          |    |

| 6.87 Interrupt Status Register (default = 0x0000) Read/Write                                                                        | 68 |

| 7. TC-622Pro/Pro+ Specifications                           | 71  |

|------------------------------------------------------------|-----|

| 7.1 Maximum Ratings and Operating Conditions               |     |

| 7.2 DC Characteristics                                     |     |

| 7.3 AC Specifications                                      |     |

| ATM Layer Transmit                                         |     |

| ATM Layer Receive                                          |     |

| Line-Side Transmit                                         |     |

| Line-Side Receive                                          |     |

| 7.4 Mechanical Specifications                              |     |

| 8. ML53301 TC-622Pro PCI Bus interface and specifications  |     |

| 8.1 PCI Bus Architectural Overview                         | 77  |

| Target Control                                             |     |

| Register Read/Write Control                                |     |

| Interrupt Control                                          |     |

| Parity Control                                             |     |

| Byte Swap Control                                          |     |

| Register Types                                             |     |

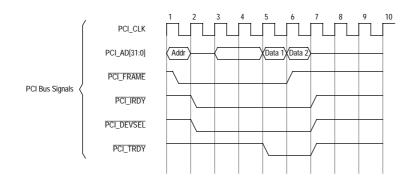

| 8.2 PCI Bus Transactions                                   |     |

| 8.3 TC-622Pro Signal Descriptions                          |     |

| 8.4 PCI Bus AC Specifications                              |     |

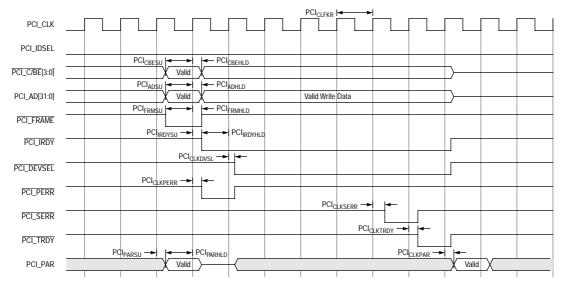

| PCI Bus Register Write                                     |     |

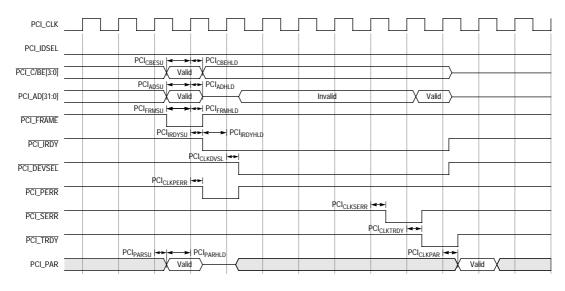

| PCI Bus Register Read                                      |     |

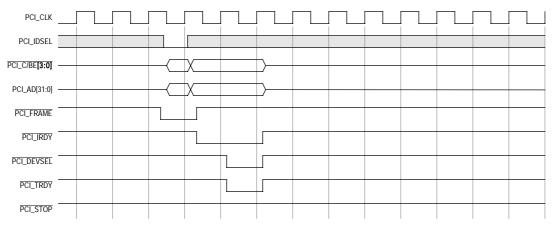

| PCI Bus Configuration Write                                |     |

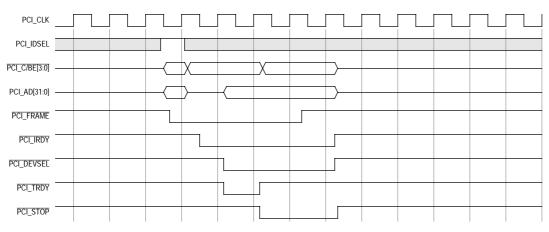

| PCI Bus Configuration Read                                 |     |

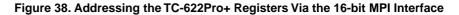

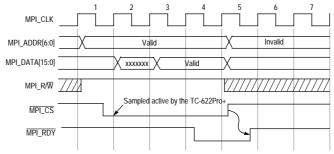

| 9. ML53311 TC-622Pro+ MPI Bus interface and specifications |     |

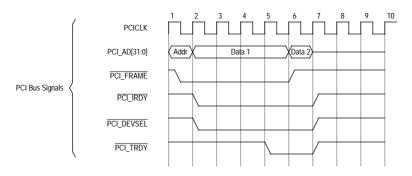

| 9.1 MPI Bus Architectural Overview                         |     |

| 9.2 MPI Bus Transactions                                   |     |

| MPI Bus Register Read                                      |     |

| MPI Bus Register Write                                     |     |

| 9.3 TC-622Pro+ Signal Descriptions                         |     |

| 9.4 MPI Bus AC Specifications                              |     |

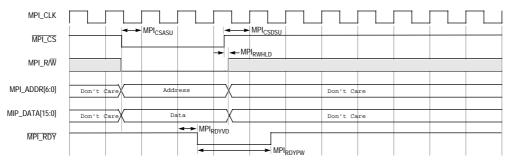

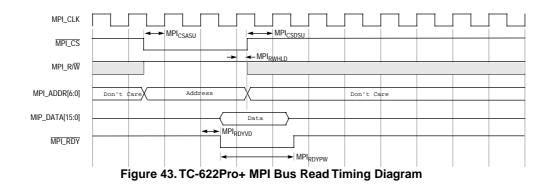

| MPI Bus Write Timing                                       |     |

| MPI Bus Read Timing                                        |     |

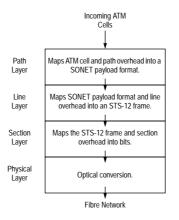

| 10. SONET Frames and ATM Cell Structure                    |     |

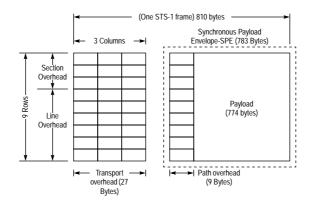

| 10.1 SONET Frame Structure                                 |     |

| Section, Line, and Path Overheads                          |     |

| Physical layer                                             |     |

| 10.2 ATM Cell Structure                                    |     |

| 11. Glossary                                               | 112 |

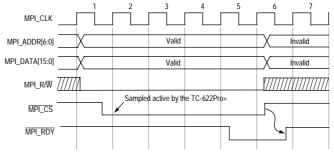

# Oki Semiconductor ML53301/ML53311 TC-622Pro/Pro+

622 Mbps ATM Transmission Convergence Sublayer SONET Framer

# 1. DESCRIPTION

The ML53301 TC-622Pro and ML53311 TC-622Pro+ are single-chip integrated circuit devices that perform Asynchronous Transfer Mode (ATM) transmission convergence sub-layer functions for the public User Network Interface (UNI) using the Synchronous Optical Network (SONET) processing standard. The physical layer supports the STS-12/STS-12c 622 Mbps SONET/SDH format. The STS-12 mode of operation supports four separate STS-3c (155 Mbps) channels. STS-12c mode supports a single 622 Mbps channel. The TC-622Pro/Pro+ can be used to interface an ATM terminal to an ATM switching system via the SONET/SDH Interface.

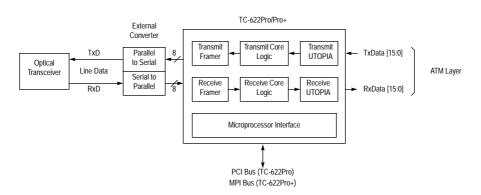

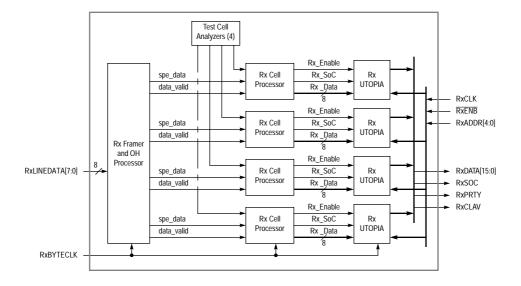

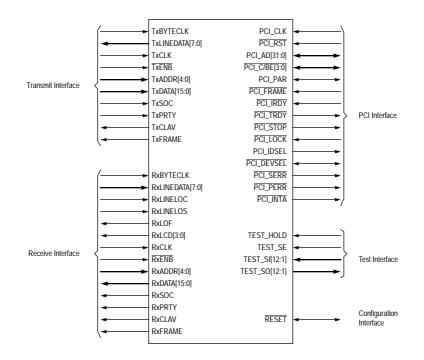

The ML53301 TC-622Pro contains a full-featured 32-bit PCI Bus interface for accessing the register array. The ML53311 TC-622Pro+ contains a simplified 16-bit microprocessor interface (MPI) ideal for use in low-cost applications. *Figure 1* shows a typical STS-12/12c application using the TC-622Pro/Pro+. *Figure 2* shows a block diagram of the ML53301 TC-622Pro and ML53311 TC-622Pro+ devices.

# 2. FEATURES

- STS-12/12c modes under register control

- UTOPIA level 2 Multi-PHY (MPHY) interface

- Full-featured 32-bit PCI bus interface (TC-622Pro)

- Low cost 16-bit MPI bus interface (TC-622Pro+)

- Test cell insertion and extraction

- Four receive and four transmit cell processors

- Lower power mode reduces power consumption to 1.3 W maximum

- Four STS-3c frames multiplexed to construct one STS-12 frame.

- One STS-12 frame demultiplexed to construct four STS-3 frames

- Separate performance monitors for individual cell processors

- Line and Path alarm indication signal inserted into the transmit signal

- Loss of signal (LOS), loss of frame synchronization (LOF), loss of pointer (LOP), and loss of cell delineation (LCD) conditions detected in the incoming signal

- Transmit processor handles single or octet-wide cell streams

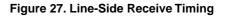

- 176-pin LQPF package for both devices

Figure 1. Typical STS12/12c Application

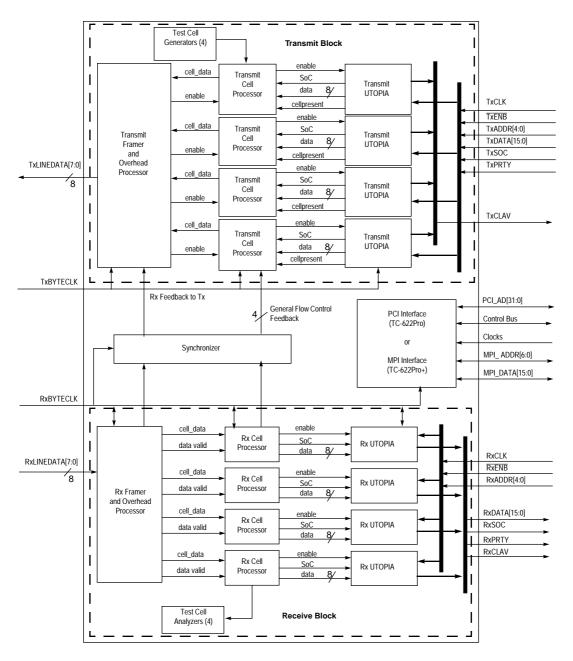

Figure 2. TC-622Pro/Pro+ Block Diagram

# **3. KEY FEATURES**

This section describes some of the features of the block shown in the block diagram in Figure 2.

# 3.1 Transmit Test Cell Generator

- Four separate test cell generators, one for each of the four transmit cell processors

- Alternate source of idle cells for transmit cell processors

- Programmable cell header

- Random payload

- Counts number of test cells transmitted

# 3.2 Receive Test Cell Analyzer

- Four separate test cell analyzers

- Test cells filtered

- Programmable cell header

- Counts number of bit errors detected in payload

- Counts number of test cells received

# 3.3 Transmit Cell Processor

- Handles single or quad octet-wide cell streams

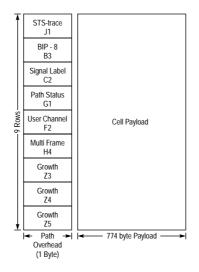

- Accepts both 52-byte cells, computes and inserts Header Error Check (HEC)

- Always adds coset polynomial  $(X^6 + X^4 + X^2 + 1)$

- Cell rate adaptation—inserts idle cells when no cell is available from the UTOPIA or FIFO

- Optionally inserts cells from an internal test cell generator in the place of idle cells

- Flow control—halts valid cell transmission when Generic Flow Control (GFC) is enabled

- Scrambles cell payload using the X<sup>43</sup> + 1 polynomial. Contains a self-synchronizing scrambler

- Counts assigned and idle cells

# 3.4 Receive Cell Processor

- Handles single or quad octet-wide cell streams

- Cell delineation state machine

- Cell delineation using HEC

- Hunt, Pre-Sync, Sync, LCD defect, LCD Defect Pre-Sync, LCD Defect Verify, and LCD Failure Verify states

- Correction and Detection states within Sync state

- Single- and multiple-bit error detection

- Single-bit error correction if correction is enabled

- Cell payload de-scrambling

- Idle cells discarded

- Performance Monitors

- Discarded cell (due to HEC violation, when in Sync state) counter

- Assigned and Idle cell counters

## 3.5 STS-12/12c Line Interface

- 8-bit parallel input and output

- 77.76 MHz clock

# 3.6 STS-12/12c Transmit Framer

- Timing control

- External timing reference—77.76 MHz clock

- A pulse given out for every frame transmitted

- STS-12/12c Pointer Insertion

- Normal mode

- No pointer increment

- No pointer decrement

- No NDF insertion

- Pointer value-620A

- Path Alarm Indication Signal (P-AIS) insertion on user command

- Path Remote Defect Indication (P-RDI) insertion on user command and on receiver alarm conditions

- Line AIS (L-AIS) insertion on user command

- Line RDI (L-RDI) insertion on user command and on receiver alarm conditions

- Path overhead insertion

- Section overhead insertion

- Line overhead insertion

- Fixed Stuff insertion in the case of STS-12c

- Fixed value inserted (00hh)

- Frame scrambling according to the ITU-T I.432 standard

# 3.7 STS-12/12c Receive Framer

- Framing

- Loss of signal state machine (LOS)

- Parallel Frame Search, Byte-alignment

- Out of frame state machine (OOF)

- Loss of frame state machine (LOF)

- A pulse for every received frame given out

- Automatic Protection Switching (APS) bytes (K1, K2) written into registers

- Section Overhead Processing

- B1 parity error counter

- Line Overhead Processing

- B2 parity error frames counter

- Line AIS state machine

- Line RDI state machine

- Line FEBE accumulator

- STS-12/12c Pointer Tracking

- H1, H2 state machines

- NDF detection

- New pointer when three consecutive valid pointers are identical

- Pointer increment

- Pointer decrement

- Detection of invalid pointer (value > 782)

- Loss of Pointer (LOP) state machine

- Path AIS state machine

- Handles SONET/SDH modes as set by a register bit

- Fixed Stuff extraction

- 4 POH Processors

- Path overhead processing

- C2 byte—number of mismatches counted

- Path FEBE accumulated

- Path RDI state machine

- B3 parity error counter

# 3.8 PCI Bus Interface (TC-622Pro)

- Supports industry-standard 32-bit PCI data path at 33 MHz

- Provides even parity for data and address

- Multiplexed address/data architecture reduces pin count

- Supports multiple families of microprocessors

# 3.9 MPI Bus Interface (TC-622Pro+)

- Supports 16-bit MPI data path at 33 MHz

- Geared toward low cost applications

- Supports multiple families of microprocessors

# 3.10 Transmit and Receive UTOPIA

- Complete compliance with UTOPIA Level 2 Version 1.0 specifications for Multi-PHY (MPHY)

- Four UTOPIA ports with separate 4-cell rate matching buffers

- 50-MHz operation

- 16-bit wide data path

- MPHY operation with single TxCLAV and RxCLAV status signals

- Support of 52-byte and 53-byte cells

- Discarding of runt cells

- Optional discarding of cells with parity errors on transmit side

- Parity computation on receive side

# 4. FUNCTIONAL DESCRIPTION

This section is divided into the following subsections:

- Section 4.1, "Architectural Overview": Defines each block in *Figure 2*

- Section 4.2, "Transmit Architecture": Discusses the operation of the Transmit module

- Section 4.3, "Receive Architecture": Discusses the operation of the Receive module

- Section 4.4, "PCI Bus Architecture (TC-622Pro)": Provides a brief overview of the ML53301 TC-622Pro PCI Bus Interface

- Section 4.5, "MPI Bus Architecture (TC-622Pro+)": Provides a brief overview of the ML53311 TC-622Pro+ low-cost MPI Bus interface.

Throughout this data sheet there are references to SONET frames and ATM cells. For an overview on SONET frames and ATM cell structures, refer to Section 10.

# 4.1 Architectural Overview

This section defines the logic blocks shown in the block diagram in Figure 2.

#### 4.1.1 Transmit Framer and Overhead Processor

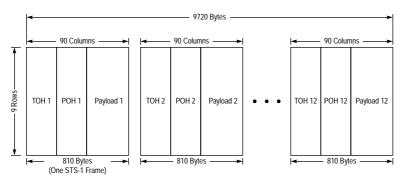

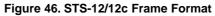

The transmit framer contains a frame generator, transportation overhead generator, path overhead generator, and a frame scrambler. The transmit framer generates the actual STS-12 or STS-12c frame from ATM cells received from the transmit cell processors. In addition to the Synchronous Payload Envelope (SPE) which contains the actual data, each 9720-byte SONET frame consists of a 324-byte *Transportation Overhead* and 9-byte or 36-byte *Path Overhead*.

The *Transportation Overhead* (TOH) is 324 bytes in size and contains a 108 byte *Section overhead* and an 216 byte *Line overhead*. The *Section overhead* generator includes bytes for frame synchronization, error monitoring and voice communication. The *Line overhead* generator consists of 216 bytes that include pointers to the start of the synchronous payload envelope (SPE), SPE frequency adjustment, error monitoring and automatic protection switching.

The *Path overhead* (POH) generator contains 9 bytes that form the first column of the SPE. These bytes support path error monitoring, connection continuity verification, monitoring of the end-to-end path performance, and STS-1 frame status.

The Frame Scrambler scrambles the SONET frame using a frame synchronous scrambler implementing a specific polynomial. Frames are scrambled to minimize the possibility of payload data looking like a header pattern and simplifies the frame recovery process at the destination.

For more information on these overheads, refer to Section 10, "SONET Frames and ATM Cell Structure".

# 4.1.2 Transmit Cell Processors

The TC-622Pro/Pro+ consists of four transmit cell processors. All four processors are enabled in STS-12 mode. Only one processor is enabled in STS-12c mode. The two main functions of each transmit cell processor are cell rate adaptation and Header Error Check (HEC) byte insertion. If the UTOPIA FIFO does not contain one or more complete cells, the cell processor inserts idle cells to achieve the correct cell adaptation. The HEC computation block computes the HEC byte from the first four bytes of any cell using a special algorithm. The cell processor also counts the number of assigned cells transmitted as well as the number of idle cells inserted. For more information on the transmit cell processor, refer to Section 4.1.2, "Transmit Cell Processors".

#### 4.1.3 Transmit UTOPIA

The Transmit UTOPIA consists of four identical ports, one for each transmit cell processor. Each UTOPIA has a unique programmable port address. The function of each port is to facilitate the transfer of data between the transmit cell processors and the ATM layer device.

#### 4.1.4 Test Cell Generator

There are four test cell generators, one for each of the four transmit cell processors. The test cell generator provides a source for idle cells as well as test cells. Whenever a cell processor does not have an assigned cell to transmit, it reads an idle cell from the corresponding test cell generator. Test cells can also be inserted into the data stream without interrupting the normal flow of data and are used for monitoring purposes and to help maintain data integrity.

#### 4.1.5 Receive Framer and Overhead Processor

The receive framer accepts non-aligned bytes from an external serial to parallel converter and extracts the frame payload. The receive framer performs frame synchronization, synchronous payload envelope extraction, overhead processing to detect alarm and error conditions, and performance monitoring.

#### 4.1.6 Receive Cell Processors

The TC-622Pro/Pro+ contains four receive cell processors. All four processors are enabled in STS-12 mode. Only one processor is enabled in STS-12c mode. The processor delineates data received from the receive framer to form cells. It computes the Header Error Check (HEC) over the first four bytes, compares it with the received HEC byte, and discards idle cells. The receive cell processor also counts the number of assigned cells written to the UTOPIA FIFO and the number of idle cells dropped.

#### 4.1.7 Test Cell Analyzer

There are four test cell analyzers, one for each of the four receive cell processors. Whenever a cell processor receives a cell with the header pattern matching one that is programmed for test cells, that cell is passed to the corresponding Test Cell Analyzer instead of the UTOPIA FIFO.

#### 4.1.8 Receive UTOPIA

The Receive UTOPIA consists of four identical ports, one for each Receive Cell processor. Each UTOPIA has a unique port address. The function of each port is to facilitate the transfer of data between the Receive Cell processors and the ATM layer device.

#### 4.1.9 PCI Bus Interface (TC-622Pro)

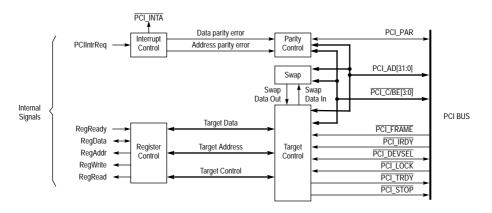

The TC-622Pro contains an industry-standard PCI interface that allows the host to read and write the TC-622Pro registers using a standard on-chip microprocessor. The PCI interface contains signal translation logic that interfaces to the PCI bus signals and generates TC-622Pro register control signals. A parity calculator calculates even parity over the address, data, and command busses, and the byte enables. The interrupt manager receives interrupts from the TC-622Pro and generates a corresponding interrupt on the PCI bus. The byte swap block swaps the address bytes depending on the Little Endian/Big Endian requirements of the host. Refer to Section 8 for more information on the PCI bus interface.

### 4.1.10 MPI Bus Interface (TC-622Pro+)

The TC-622Pro+ provides a generic microprocessor interface (MPI) intended for use in low-cost applications where a full PCI interface is not required. In the TC-622Pro+, registers are accessed directly by driving the required address onto the bus. No memory mapping of registers is required. In the TC-622Pro (PCI) the registers are memory-mapped to a specific 8-kbyte space. In the TC-622Pro+ (MPI) the registers are not memory mapped and are accessed directly using a separate 7-bit address bus.

Refer to Section 9 for more information on the MPI bus interface.

# 4.2 Transmit Architecture

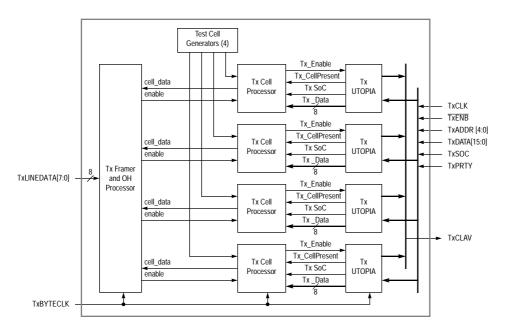

The TC-622Pro/Pro+ block diagram in *Figure 2* is broken into three major interfaces; transmit interface, receive interface, and PCI/MPI interface. This section discusses the transmit interface. Refer to Section 4.3 for more information on the receive interface. Refer to Section 4.4 for more information on the PCI Bus interface. Refer to Section 4.5 for more information on the MPI Bus interface. *Figure 3* shows a block diagram of the transmit interface.

Figure 3. TC-622Pro/Pro+ Transmit Architecture Block Diagram

The transmit architecture in the TC-622Pro/Pro+ contains the following four modules below which are discussed, along with the transmit data flow, in the following sections:

- Four Transmit UTOPIA channels

- Four Transmit Cell Processors

- Four Transmit Test Cell Generators

- Transmit Framer

#### 4.2.1 Transmit Data Flow

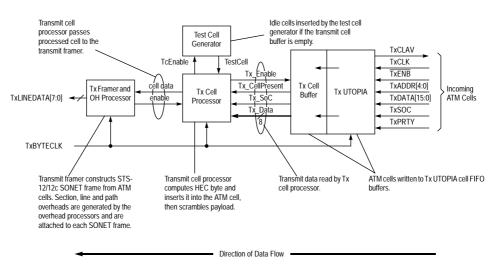

During a transmit operation, ATM cells are written into the transmit UTOPIA buffers by the ATM layer device. The transmit UTOPIA provides an industry standard ATM PHY interface. Four transmit UTO-PIA buffers are provided to serve four independent ATM sources.

Once the ATM cells have been written to the PHY and placed in the cell buffers, they are read out by the transmit cell processors. There are four processors, one for each transmit UTOPIA PHY. The transmit cell processor calculates the HEC byte and inserts this information into byte 5 of the ATM cell header. The cell payload is then scrambled to minimize the potential for false headers in the payload, and to avoid deliberate transmission of line alarm patterns.

Once the entire cell has been processed it is passed to the transmit framer where a SONET STS-12/12c frame, complete with section, line, and path overheads, is constructed from the stream of ATM cells. The cell processor then reads another ATM cell from the transmit UTOPIA. If the UTOPIA cell buffer is empty, the corresponding test cell generator inserts an idle cell into the transmit stream.

*Figure 4* shows a flow diagram of a transmit operation for one transmit path. The other three paths are identical.

Figure 4. Data Flow During a Transmit Operation

#### Microprocessor Interface to Transmit Architecture

The TC-622Pro/Pro+ contains a number of registers that contain performance monitoring, status, and alarm indication information. These registers are accessed by the host through the PCI (TC-622Pro) or MPI (TC-622Pro+) bus interface. Refer to Section 4.4 for more information on the PCI interface. Refer to Section 4.5 for more information on the MPI Interface. Refer to Section 6 for a listing and description of TC-622Pro/Pro+ registers.

#### **Performance Monitors**

The TC-622Pro/Pro+ maintains running counters that monitor various error events as they occur. These counters are maintained within the transmit block and are not reset when read. Rather, a sticky bit is used to indicate count roll-over. Four roll-over registers, located at addresses 0x52 - 0x55, are used to store these sticky bit values. The user can read the appropriate roll-over register and reset the bit manually if desired.

The TC-622Pro/Pro+ transmit counters perform the following functions:

- Counts the number of cells and frames transmitted

- Counts the number of cells discarded because of multiple-bit errors

- Counts the number of idle cells inserted into the data stream to achieve cell rate adaptation

#### 4.2.2 Transmit UTOPIA PHY

The TC-622Pro/Pro+ consists of four identical transmit UTOPIA PHY ports. Each port has a unique address and supports a different ATM stream. The function of each port is to facilitate the transfer of data between the transmit cell processors and the ATM physical layer. Each port conforms to the UTOPIA Level 2 Version 1.0 specification and supports Multi-PHY (MPHY) operation using a 16-bit data path.

Operation with an 8-bit ATM cell path is not supported. In STS-12c mode only port 0 is active. The ATM master device can transfer data by driving the address of that port on the *TxADDR[4:0]* lines such that the *TxCLAV* output is driven permanently by that port only.

#### ATM Layer Interface

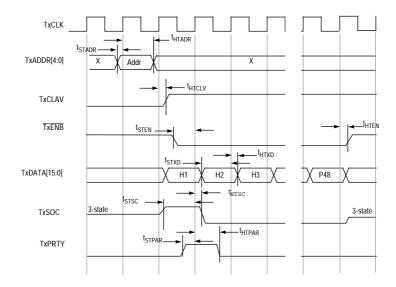

The transmit interface is controlled by the ATM layer. This layer provides an interface clock to the UTO-PIA PHY for synchronizing all interface transfers. The transmit interface has data flowing in the same direction as the ATM enable. The following UTOPIA interface signals; TxENB, TxDATA[15:0], TxA-DDR[4:0], TxSOC, and TxPRTY, are all sampled on the rising edge of TxCLK.

The UTOPIA slave controls the flow of data through the *TxCLAV* signal. Once this signal is asserted, the ATM layer responds by driving data onto *TxDATA*[15:0] and asserting  $\overline{TxENB}$ .

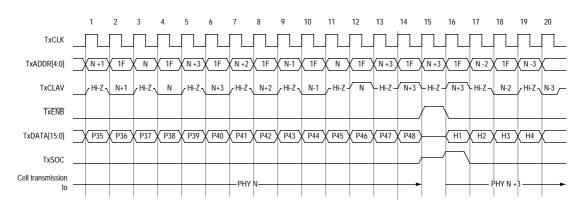

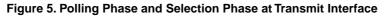

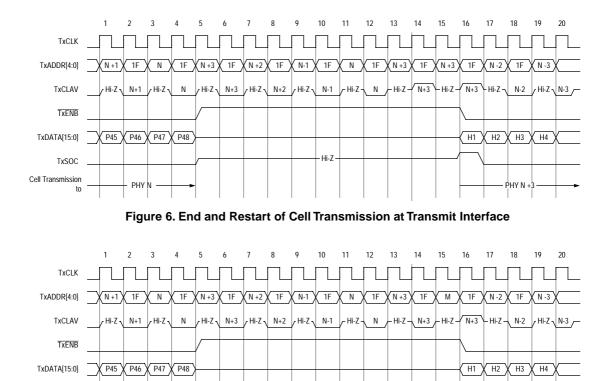

Figure 5, Figure 6, and Figure 7 show three different conditions under which data is transmitted.

Cell transmission to PHY M PHY

Hi-7

#### Transmit Cell Processor Interface

TxSOC

Each of the four transmit cell processors provides an interface clock to the UTOPIA slave block for synchronizing all interface transfers. The cell processor generates all signals on the rising edge of an internal *cell processor* signal clock.

Once at least one or more ATM cells have been received from the ATM layer and stored to the UTOPIA cell buffer, the UTOPIA indicates to the cell processor that cell data is ready for transfer. The cell processor uses internal handshake signals to control the flow of data between the UTOPIA and the cell processor.

#### 4.2.3 Transmit Cell Processor

The TC-622Pro/Pro+ contains four transmit cell processors which operate independently of one another. Each transmit cell processor performs two primary functions; *Header Error Check (HEC)* insertion and *cell rate adaptation*.

The TC-622Pro/Pro+ supports two SONET frame modes which determine how many processors are enabled. In STS-12 mode, all four cell processors are enabled and one at a time is selected. The four pro-

#### ML53301/ML53311 TC-622Pro/Pro+

cessors are enabled in a fixed order. In STS-12c mode one processor is enabled and the other three are disabled. The UTOPIA PHY asserts the internal  $Tx\_CellPresent$  signal to inform the cell processor that an ATM cell is in the cell FIFO buffer and is ready for transmission. The cell processor asserts the internal  $Tx\_Cenable$  signal and reads the 52-byte ATM cell from the FIFO. These signals are provided for clarity and are not available externally.

Once the cell has been read, the HEC computation block computes the HEC based on the first four bytes read from the FIFO using the CRC-8 polynomial ( $X^8 + X^2 + X + 1$ ) and always adds the coset polynomial ( $X^6 + X^4 + X^2 + 1$ ). The coset is a derivative of the CRC-8 polynomial. In the TC-622Pro/Pro+ devices the coset polynomial is always enabled. The HEC computation is then inserted into the fifth byte position of the cell, during which time the cell processor stops reading from the FIFO for one clock cycle. Except for the first five header bytes, the 48-byte cell payload is scrambled using a self-synchronizing scrambler employing the polynomial ( $X^{43} + 1$ ). Cell payloads are scrambled to minimize the possibility of payload data looking like a header pattern. Scrambling the data helps simplify the frame recovery process at the destination by increasing the level of differentiation between the header and the cell payload.

If the UTOPIA FIFO does not contain a complete cell, the cell processor inserts idle cells from the test cell generator to achieve the correct cell rate adaptation. The idle cells have a fixed header pattern of 0x(00, 00, 00, 01, 52), and a fixed payload of (0x6A).

The cell processor can also send test cells from the test cell generator instead of idle cells. The header for these test cells is programmed in registers. The processor computes the HEC of these test cells. When test cells are inserted, availability of a cell in the FIFO is checked at the end of every cell. Anytime a full cell is available in the FIFO, it is read by the cell processor and inserted into the data stream.

In addition to HEC computation and cell rate adaptation, the cell processor also counts the number of assigned cells transmitted and the number of idle cells inserted. These counters are free-running and indicate roll-over using a sticky-bit. Each counter register is 16-bits in size and uses a 17th bit to indicate the roll-over status for that register. The sticky bits from each counter register are concatenated into a series of 16-bit registers called 'roll-over' registers. These registers are located at addresses 0x52 - 0x55 in TC-622Pro/Pro+ register address space.

The transmit cell processor receives general flow control (GFC) feedback from the receive cell processor. When a GFC Halt is enabled by the user and the GFC feedback is received, the ATM cells are not accepted and transmitted from the FIFO, even if cells in the FIFO are available for transmission.

#### 4.2.4 Test Cell Generator

The TC-622Pro/Pro+ contains four transmit test cell generators, one for each transmit cell processor. The test cell generators provide a source of idle cells for the corresponding cell processor. Whenever the cell processor does not have assigned cells to read from the UTOPIA buffer, it reads idle cells from the test cell generator in order to meet the correct cell rate adaptation.

When the internal *TcEnable* signal is asserted by the cell processor, the test cell generator places a test cell on cell data bus in the following clock. The cell data is generated by a Pseudo Random Sequence Generator (PRBS). The PRBS is a shift register that generates a random number and then repeats the sequence after some period of time. There are four different maximum-length polynomials used to ensure random data for all of the four cell streams independent of one another.

- Polynomial 1  $(x^{22} + X^{17} + 1)$

- Polynomial 2  $(x^{22} + X^{11} + 1)$

- Polynomial 3  $(x^{22} + X^{19} + 1)$

- Polynomial 4  $(x^{22} + X^{14} + 1)$

#### 4.2.5 Transmit Framer And Overhead Processor

The transmit framer receives processed ATM cells from the cell processors and constructs an STS-12/12c frame depending on the mode. Each STS frame contains a 108-byte section overhead, an 216-byte line overhead, and a 9- or 36-byte path overhead, all of which contain information about the frame. This information is calculated by the overhead processor within the transmit framer. *Table 1* shows the values generated for each overhead field by the overhead processors. All fields in *Table 1* are 8-bits wide. Once the entire frame is assembled, all bytes of the frame except the framing bytes (A1, A2, C1) are scrambled using a frame synchronous scrambler that implements the polynomial ( $X^7 + X^6 + 1$ ).

Refer to Section 10 for the definition and physical location of each field within the corresponding overhead.

| Field            | Byte Type             | Value                                                                                                                                                                   |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section Overhead | d Processor (9 bytes) |                                                                                                                                                                         |

| A1               | Framing               | 0xF6                                                                                                                                                                    |

| A2               | Framing               | 0x28                                                                                                                                                                    |

| C1               | Identity              | SONET mode: 0x01, 0x02, 0x0C<br>SDH mode: 0x01, 0x02, 0x04. Remaining 8 bytes = 0xCC                                                                                    |

| B1               | BIP-8                 | 8-bit parity field. Value depends on data.                                                                                                                              |

| All others       |                       | Fixed at 0x00                                                                                                                                                           |

| Line Overhead Pr | rocessor (18 bytes)   |                                                                                                                                                                         |

| H1               | Pointer               | STS-12 mode: First four bytes are 0x62.<br>Remaining 8 bytes = 0x93.<br>STS-12c mode: First byte is 0x62.<br>Remaining 11 bytes are 0x93.                               |

| H2               | Pointer               | STS-12 mode: First four bytes are 0x0A.<br>Remaining 8 bytes = H2*<br>STS-12c mode: First byte is 0x0A.<br>Remaining 11 bytes are H2*<br>*(H2 = 0xFF)                   |

| H3               | Pointer Action        | 0x00                                                                                                                                                                    |

| B2               | Parity                | Calculates 96-bit BIP parity over the line overhead and entire SPE before scrambling, then inserts the value into the current frame. The actual value is data-dependent |

| K1               | APS                   | AIS insertion: User command AIS code 0x07is inserted into the K1 byte.                                                                                                  |

| К2               | APS                   | RDI insertion: User command RDI code 0x06is inserted into the K2 byte if one or more error conditions (LOS, LOF, LOC) are detected in the receiver.                     |

| D4 - D12         | Datacomm              | Fixed at 0x00                                                                                                                                                           |

| Z1 - Z2          | Growth                | Fixed at 0x00                                                                                                                                                           |

| Path Overhead Pr | rocessor (9 bytes)    |                                                                                                                                                                         |

| J1               | Trace                 | Fixed at 0x00                                                                                                                                                           |

| B3               | BIP - 8               | 8-bit parity value depends on data                                                                                                                                      |

| C2               | Signal label          | Fixed at 0x13                                                                                                                                                           |

| G1               | Path status           | Path FEBE value is inserted in this byte                                                                                                                                |

#### **Table 1. Transmit Overhead Values**

**Table 1. Transmit Overhead Values**

| Field   | Byte Type    | Value         |

|---------|--------------|---------------|

| F2      | User channel | Fixed at 0x00 |

| H4      | Multi-frame  | Fixed at 0x00 |

| Z3 - Z5 | Growth       | Fixed at 0x00 |

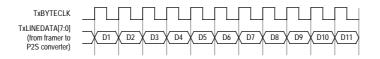

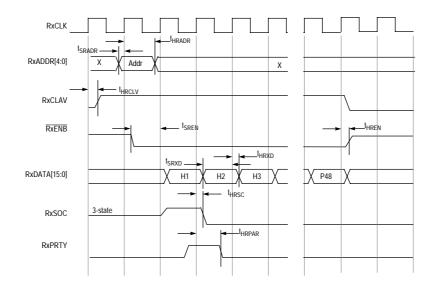

The transmit framer uses the *TxBYTECLK* Clock to transfer information to the external parallel-to-serial converter. Transmit line data is transferred in 8-bit quantities at the rising edge of each *TxBYTECLK*. *Figure 8* shows a timing diagram of a typical line data transfer. Note that the acronym P2S in the diagram below is for the 'Parallel-to-Serial' converter.

#### Figure 8. Transmit Line Interface Timings

#### **4.3 Receive Architecture**

The receive architecture in the TC-622Pro/Pro+ contains the following four modules below which are discussed, along with the receive data flow, in the following sections:

- Receive Framer and Overhead Processor

- Four Receive Test Cell Analyzers

- Four Receive Cell Processors

- Four Receive UTOPIA's

The TC-622Pro/Pro+ block diagram in *Figure 2* is broken into three major interfaces; transmit interface, receive interface, and PCI/MPI interface. This section discusses the architecture of the receive interface. Refer to Section 4.2 and Section 4.4 for more information on the transmit and PCI (TC-622Pro) interfaces. Refer to Section 4.5 for more information on the TC-622Pro+ MPI interface. *Figure 9* shows a block diagram of the receive architecture.

#### Figure 9. Receive Architecture Block Diagram

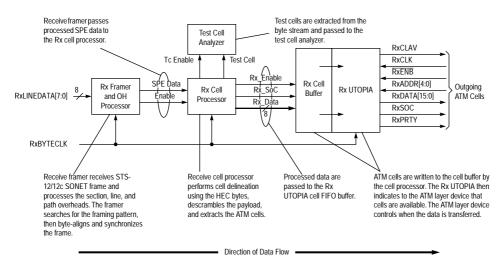

#### 4.3.1 Receive Data Flow

During a receive operation, the incoming serial bit stream is converted into bytes by an external serial-toparallel converter and driven to the receive framer on RxLINEDATA[7:0]. This 8-bit value is not bytealigned when it enters the framer and the framer must search the byte stream for the framing pattern. Once the framing pattern is located, frame synchronization is declared and the byte boundaries of the received data are determined.

Each of the three overhead processors (section, line, and path) contained in the receive framer processes the corresponding overhead bytes. The Synchronous Payload Envelope (SPE) contained in the frame is extracted and passed to the receive cell processor. The receive framer detects various error conditions and alarm indications in the incoming signal.

The cell processor performs cell delineation using the Header Error Control (HEC) bytes and extracts the appropriate cells. All cells with multiple-bit errors are discarded along with all idle cells. The cell processor descrambles the cell payload and writes the cell into the receive UTOPIA cell buffer.

Once the cells have entered the buffer, the receive UTOPIA indicates the availability of these cells to the ATM layer, where they are subsequently read out by the ATM layer device.

Figure 10 shows a flow diagram of a receive operation.

Figure 10. Data Flow During a Receive Operation

#### Microprocessor Interface to Receive Architecture

The TC-622Pro/Pro+ contains a number of registers containing performance monitoring, status, and alarm indication information. In the ML53301 TC-622-Pro device, these registers are accessed by the host through the PCI bus. In the ML53311 TC-622Pro+ device, these registers are accessed directly through the MPI Bus Interface. Refer to Section 4.4 for more information on the PCI interface. Refer to Section 4.5 for more information on the MPI Interface. Refer to Section 6 for a listing and description of TC-622Pro registers.

#### **Performance Monitors**

The TC-622Pro/Pro+ maintains running counters that monitor various error events as they occur during a receive operation. These counters are maintained within the receive block and are not reset when read. Rather, a sticky bit is used to indicate count roll-over. The sticky bits for all counter registers are concatenated together into four 16-bit registers that are located at addresses 0x52 - 0x55. The user can read the appropriate roll-over register and reset the bit manually if desired.

The TC-622Pro/Pro+ counters perform the following functions:

- Counts the number of cells and frames received

- Counts the number of cells discarded because of multiple-bit errors

- Counts the number of B1, B2, and B3 parity errors detected in the incoming signal. B1 corresponds to errors detected in the section overhead, B2 corresponds to errors detected in the line overhead, and B3 corresponds to errors detected in the path overhead.

- Counts the number of line and path Far End Block Error (FEBE) values received.

#### 4.3.2 Receive Framer And Overhead Processor

The receive framer receives byte line data after the bit stream has been converted using an external serialto-parallel converter. The receive framer takes in non-aligned bytes and extracts the frame payload. In STS-12c mode only one of the four processor modules is active, hence there is only one payload (SPE) to extract. In STS-12 mode the framer extracts four independent payloads. The receive framer performs the following functions:

- STS-12/12c frame recovery and synchronization

- Pointer processing to extract the Synchronous Payload Envelope (SPE)

- Overhead processing to detect alarm conditions in the incoming signal

- Performance monitoring

Each of these functions is explained in the following sections.

#### Frame Recovery and Synchronization

Data entering the receive framer is stored in a 31-bit buffer where the framer searches for the framing patterns. During normal frame transmission the framer is in the 'sync' state and expects twelve 0xF6 values followed immediately by twelve 0x28 values at a fixed location within the buffer. Each of these values must be received exactly 125  $\mu$ s apart, the duration of a typical SONET frame. Once these patterns are found, that portion of the buffer is used to give out the byte-aligned data. When the framer detects an out-of-frame condition, it searches for a pattern equivalent to 0x6F6282. A change of byte alignment occurs only when the receive framer makes a transition from the Out-Of-Frame (OOF) state to the Sync state.

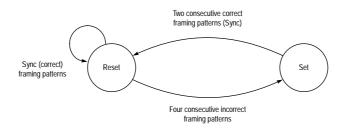

#### **Out-Of-Frame State Machine**

The OOF state machine is used to monitor the out-of-frame condition and is set whenever there are four consecutive incorrect framing patterns. The machine is reset once two consecutive correct patterns are observed. *Figure 11* shows a diagram of the OOF state machine.

Figure 11. Out-Of-Frame State Machine

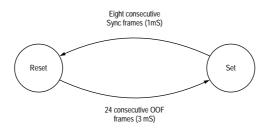

#### Loss-Of-Frame State Machine

The OOF condition above is generated at  $125 \,\mu$ S intervals. This is the rate at which the framing patterns are extracted by the receive framer. If 24 consecutive frames (3 mS) generate an OOF condition, the LOF state machine is set. The LOF state machine is reset after 8 frames (1 mS) of continuous Sync condition (no OOF condition). *Figure 12* shows a diagram of the LOF state machine.

#### Figure 12. Loss-Of-Frame State Machine

#### Loss-of-Signal State Machine

The TC-622Pro/Pro+ implements a frame synchronous descrambler that implements the polynomial ( $X^7 + X^6 + 1$ ) which is used to descramble the overheads and the cell payload. Note that framing bytes A1, A2, and A3 of the section overhead are not descrambled. The descrambler is initialized at the start of each frame.

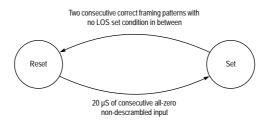

The LOS state machine is set when the receive framer gets an external LOS indication. This external LOS indication is logically OR'ed with an internally detected LOS and then used throughout the device. The LOS state machine is set when at least 20  $\mu$ S of continuous all zero non-descrambled inputs are detected. The machine is reset when two correct framing patters are detected exactly 125  $\mu$ S apart with no LOS set condition in between. *Figure 13* shows a diagram of the LOS state machine.

Figure 13. Loss-Of-Signal State Machine

#### Loss-Of-Pointer State Machine

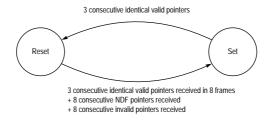

The LOP state machine is set when under any one of the following conditions:

- · Three consecutive valid identical pointers are received in eight frames

- Eight consecutive NDF pointers are received

- · Eight consecutive invalid pointers are received

The machine is reset when three consecutive identical valid pointers are received. *Figure 14* shows a diagram of the LOP state machine.

#### Figure 14. Loss-Of-Pointer State Machine

#### Path AIS State Machine

The P-AIS state machine is set when three consecutive H1 and H2 bytes are all ones (invalid pointers). The machine is reset when three consecutive identical valid pointers are received. *Figure 15* shows a diagram of the Path-AIS state machine.

Figure 15. Path-AIS State Machine

#### Synchronous Payload Envelope (SPE) Extraction

The line overhead processor examines the H1 and H2 bytes of the line overhead to locate the start of the SPE. In STS-12 mode four pointers are processed and maintained. In STS-12c mode only one pointer is processed. The following functions are performed to extract the SPE.

- **Invalid Pointer Detection:** An invalid pointer is declared when the received H1H2[9:0] decimal value is either greater than 782, not persistent for three frames, or the NDF flag is set. This value is comprised of all 8 bits of the H2 byte and the lower 2 bits of the H1 byte.

- NDF Detection: A New Data Flag (NDF) condition is declared when bits [7:4] of the H1 byte match one of the following patterns; 0001, 1000, 1001, 1011, or 1101. If an NDF condition is detected with a valid pointer, the current pointer is changed to the received pointer which has the highest priority. The NDF is a mechanism that provides for the sudden change in data alignment in a SONET frame.

- Three Consecutive Identical Pointers Detection: The occurrence of three consecutive identical valid pointers is used to change the current pointer. This has the second highest priority after NDF.

- **Justification Detection:** The TC-622Pro/Pro+ supports both positive and negative justification. Positive justification is declared if the received H1H2[9:0] value, after the inversion of all evennumbered bits, matches with the inverted current pointer in at least 8 or more bits. Negative justification is declared if the received H1H2[9:0] value, after inversion of all odd-numbered bits, matches with the inverted current pointer in at least 8 or more bits.

#### **Overhead Processing**

The TC-622Pro/Pro+ devices contain section, line, and path overhead processors for extraction and processing of the section and line overheads of the SONET frame, and the path overheads of each SPE. *Table 2* lists the various bytes of each overhead and how they are handled in the TC-622Pro and TC622-Pro+ devices.

| Field             | Byte Type           | Value                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section Overhead  | Processor (9 bytes) |                                                                                                                                                                                                                                                                                                                                                               |

| A1                | Framing             | Contains frame synchronization information.                                                                                                                                                                                                                                                                                                                   |

| A2                | Framing             | Contains frame synchronization information.                                                                                                                                                                                                                                                                                                                   |

| C1                | Identity            | Identifies each STS-1 within a SONET frame.                                                                                                                                                                                                                                                                                                                   |

| B1                | BIP-8               | 8-bit parity field. Value depends on data. This 8-bit interleaved field is calculated over the com-<br>plete frame before descrambling. The result is compared with the received B1 byte in the next<br>frame. The number of bit errors are accumulated. The accumulation of B1 errors is stopped<br>under OOF, LOF, LOS, and LOC conditions.                 |

| E1, F1, D1-D3     |                     | Ignored.                                                                                                                                                                                                                                                                                                                                                      |

| Line Overhead Pro | cessor (18 bytes)   |                                                                                                                                                                                                                                                                                                                                                               |

| H1, H2            | Pointers            | The processing of these bytes is discussed in the above section on "SPE Extraction".                                                                                                                                                                                                                                                                          |

| H3                | Pointer Action      | If negative justification is declared then the H3 byte contains valid SPE data. Otherwise it is ignored. Justification is discussed in the above section on "SPE Extraction".                                                                                                                                                                                 |

| B2 BIP-8          |                     | The 96-bit line bit-interleaved parity is calculated over the SPE and the line overhead bits. The result is compared with the received B2 byte in the next frame. The number of mismatches are accumulated. The accumulation of B2 errors and FEBE feedback are stopped under OOF, LOF, LOS, and LOC conditions.                                              |

| K1, K2            | Pointer Action      | These bytes are written to a register for user purposes. Automatic Protection Switching (APS) is not supported in the TC-622Pro/Pro+.                                                                                                                                                                                                                         |

| Z2 Growth         |                     | If the value contained in the third received Z2 byte is less than 97 decimal it is accumulated in a counter. Overflow of the counter is indicated by a sticky bit. Accumulation of the received line FEBE is stopped under OOF, LOF, LOS, and LOC conditions.                                                                                                 |

| Z1, E3, D4-D12    |                     | Ignored.                                                                                                                                                                                                                                                                                                                                                      |

| Path Overhead Pro | ocessor (9 bytes)   |                                                                                                                                                                                                                                                                                                                                                               |

| J1                | Trace               | Ignored.                                                                                                                                                                                                                                                                                                                                                      |

| ti<br>C           |                     | Used to calculate the 8-bit interleaved parity over the entire SPE. The result is compared with the B3 byte of the next SPE. The number of bit errors are accumulated using a counter. Counter overflow is indicated by a sticky bit. The accumulation of B3 errors and the FEBE feedback are stopped under OOF, LOF, LOS, LOC, LOP, and Path AIS conditions. |

| C2                | Signal label        | The received C2 byte is compared with a fixed value of 0x13. The number of mismatches is maintained in a 3-bit counter. Counter overflow is indicated by a sticky bit. The counting of C2 byte mismatches is stopped under OOF, LOF, LOS, LOC, LOP, and Path AIS conditions.                                                                                  |

| G1                | Path status         | If the received value of path FEBE contained in the G1 byte is less than 9, then it is accumu-<br>lated using a counter. Counter overflow is indicated by a sticky bit. The counting of path FEBE<br>is stopped under OOF, LOF, LOS, LOC, LOP, and Path AIS conditions.                                                                                       |

#### **Table 2. Receive Overhead Values**

-----

Ignored.

F2, H4, Z3-Z5

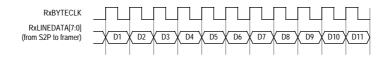

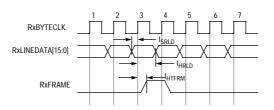

The receive framer uses the *RxBYTECLK* signal to transfer information between the receive framer and the external converter. Receive line data is transferred in 8-bit quantities at the rising edge of each *RxBYTECLK*. *Figure 16* shows a timing diagram of a typical receive line data transfer. Note that the acronym S2P stands for 'Serial-to-Parallel'.

#### Figure 16. Receive Line Interface Timing Example

#### **Receive Overhead State Machines**

There are three state machine associated with receive overhead processing. Two machines pertain to the K2 byte in the line overhead, and one machine pertains to the G1 byte in the path overhead. Each of these machines is explained below.

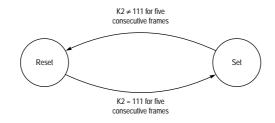

The *Line-AIS* state machine is used for detecting an alarm indication on the line side (remote end). The machine is set (Line-AIS condition declared) when a Line-AIS code (111 in the lower 3-bits of the K2 byte of the section overhead) is received for five consecutive frames. The machine is reset when a Line-AIS code other than '111' in the K2 byte is received for five consecutive frames. *Figure 17* shows a diagram of the Line-AIS state machine.

Figure 17. Line-AIS State Machine

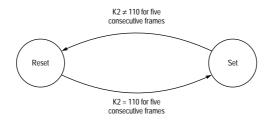

The *Line-RDI* state machine is used to detect a remote defect indication on the line side. The machine is set (Line-RDI condition declared) when a Line-RDI code (110 in the lower 3-bits of the K2 byte in the section overhead) is received for five consecutive frames. The machine is reset when a Line-RDI code other than '110' in the K2 byte is received for five consecutive frames. *Figure 18* shows a diagram of the Line-RDI state machine.

Figure 18. Line-RDI State Machine

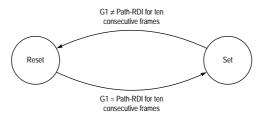

The *Path-RDI* state machine is used for remote defect indication in the path overhead. The machine is set (Path-RDI condition declared) when a path RDI indication in the G1 byte (bit 5) of the path overhead is received for ten consecutive frames. The machine is reset when no path RDI indication in the G1 byte is received for ten consecutive frames. *Figure 19* shows a diagram of the Path-RDI state machine.

Figure 19. Path-RDI State Machine

#### 4.3.3 Receive Cell Processor

The TC-622Pro/Pro+ contains four receive cell processors which operate independently of one another. In STS-12 mode all four processors are enabled. In STS-12c mode only one processor is enabled and it writes to only one UTOPIA channel. All receive cell processors operate in an identical manner.

The receive cell processor receives data from the receive framer and delineates the data to form ATM cells. The processor descrambles delineated cells using a self-synchronizing descrambler that uses the polynomial ( $X^{43}$  + 1). The cell delineation state machine computes the Header Error Control (HEC) over the first four bytes of each ATM cell and compares it with the received HEC byte. The processor is capable of correcting single-bit errors in a cell header and detecting multi-bit errors. Idle cells are discarded. The first four bits of each ATM cell header (in UNI mode) are the Generic Flow Control (GFC) bits.

Each cell processor counts the number of assigned cells written to the UTOPIA FIFO and the number of idle cells dropped. It also counts the number of cells with multiple-bit HEC errors and the number of transitions from the *Sync* state to the *Out-of-Cell-Delineation* state. The *Sync* state is declared when more than seven ATM cells have been transmitted successfully. In this state the received ATM cells are extracted and written to the FIFO. In the *Out-of-Cell-Delineation* state cells cannot be extracted. The state machine transitions from the *Sync* state to the *Out-of-Cell-Delineation* state when more than 8 consecutive ATM cells have an incorrect HEC value.

#### 4.3.4 Test Cell Analyzer

The TC-622Pro/Pro+ contains four test cell analyzers, one for each receive cell processor. Whenever a cell processor receives a cell with a header pattern matching one that is programmed for test cells, that cell is passed to the corresponding test cell analyzer and is not written to the UTOPIA FIFO. The test cell analyzer uses the test cell to check the integrity of the payload and detect the number of bit errors present. It also counts the number of test cells received. The test cell analyzer uses a pseudo-random generator that has two phases of operation.

- Phase 1: The test cell analyzer is synchronized to the incoming data.

- Phase 2: Once synchronization is achieved, the test cell analyzer detects all bit errors present in the payload.

The PRBS polynomials used in the test cell analyzer give a maximum length random sequence. Four different polynomials are used to check data integrity for all four data streams from the four test cell analyzers.

- Polynomial 1  $(X^{22} + X^{17} + 1)$

- Polynomial 2  $(X^{22} + X^{11} + 1)$

- Polynomial 3  $(X^{22} + X^{19} + 1)$

- Polynomial 4  $(X^{22} + X^{14} + 1)$

The internal *TcEnable* signal from the cell processor qualifies the cell payload. Whenever *TcEnable* is asserted the PBRS starts functioning. Note that this signal is not available external to the device.

#### 4.3.5 Receive UTOPIA Phy

The TC-622Pro/Pro+ consists of four identical receive UTOPIA PHY ports. Each port has a unique address and supports a different ATM stream. The function of each port is to facilitate the transfer of data between the TC-622Pro/Pro+ receive cell processors and the ATM physical layer. Each port conforms to the UTOPIA Level 2 Version 1.0 specification and supports Multi-PHY (MPHY) operation using a 16-bit data path. MPHY mode indicates that all four UTOPIA ports on the TC-622Pro/Pro+ are active.

Operation with an 8-bit ATM cell path is not supported. If the ATM master intends to transfer data in STS-12c mode where only port 0 is active, it can do so by driving the address of that port on the TxA-DDR[4:0] lines such that the TxCLAV output is driven permanently by that port only.

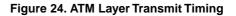

#### ATM Layer Receive Interface

The receive interface is controlled by the ATM layer. This layer provides an interface clock to the UTO-PIA PHY for synchronizing all interface transfers. The receive interface has data flowing in the opposite direction as the ATM enable. The receive UTOPIA interface signals; *RxENB*, *RxDATA*[15:0], *RxA-DDR*[4:0], *RxSOC*, and *RxPRTY*, are all sampled or driven on the rising edge of *RxCLK*. The UTOPIA slave controls the flow of data through the *RxCLAV* signal.

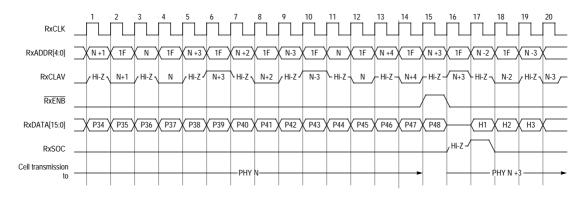

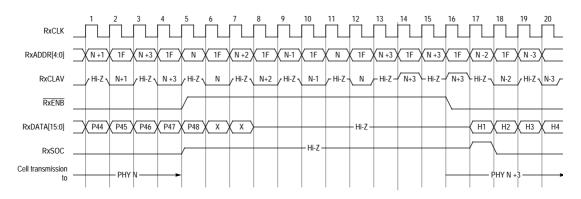

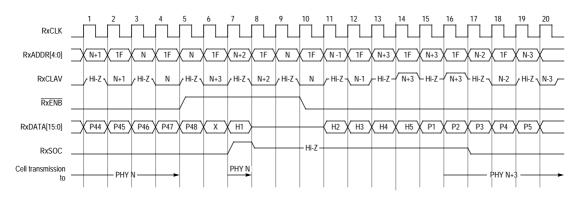

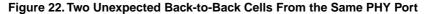

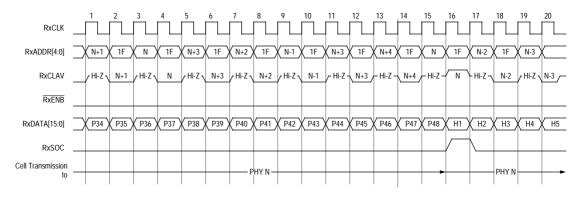

*Figures* 20 through 23 show three different conditions under which data is read from the receive UTOPIA by the ATM layer device.

#### ML53301/ML53311 TC-622Pro/Pro+

Figure 20. Polling Phase and Selection Phase at Receive Interface

Figure 21. End and Restart of Cell Transmission at Receive Interface

Figure 23. Two Subsequent Cells From the Same PHY Port

#### **Receive Cell Processor Interface**

Each of the four receive cell processors provides an interface clock to the UTOPIA slave block for synchronizing all interface transfers. The cell processor generates all signals on the rising edge of the internal *RxCellClk* signal.

Internal handshake signals are used to control the flow of data between the receive cell processor and the receive UTOPIA. At the beginning of each cell transfer the receive UTOPIA checks whether an entire cell can be written to the FIFO. If there is insufficient space in the FIFO to accommodate an entire cell the receive UTOPIA simply ignores the data and indicates an overrun condition by asserting an internal *Overrun* signal.

# 4.4 PCI Bus Architecture (TC-622Pro)

The ML53301 TC-622Pro incorporates a standard microprocessor with a PCI interface for accessing of onchip registers and control functions. Refer to Section 8 for more information on the ML53301 TC-622Pro PCI Bus Architecture.

#### 4.5 MPI Bus Architecture (TC-622Pro+)

The ML53311 TC-622Pro+ incorporates a standard microprocessor with a low-cost MPI interface for accessing of on-chip registers and control functions. Refer to Section 9 for more information on the ML53311 TC-622Pro+ MPI Bus Architecture.

# **5. SIGNAL DESCRIPTIONS**

The ML53301 TC-622Pro contains a 32-bit PCI interface. The ML53311 TC-622Pro+ contains a low cost 16-bit MPI interface. Refer to Section 8 for the TC-622Pro signal descriptions. Refer to Section 9 for the TC-622Pro+ signal descriptions.

# 6. REGISTERS

*Table 3* shows a register map of the TC-622Pro and TC-622Pro+ devices. Each register is then described in the order that it appears in the table. Throughout the register descriptions in this section, the word 'set' means to set the register bit to a logic 1. The word 'clear' means to reset the bit to a logic 0.

Refer to Section 8 for more information on accessing these registers using the PCI interface in the TC-622Pro. Refer to Section 9 for more information on accessing these registers using the MPI interface in the TC-622Pro+.

| Address | Width (bits) | Register Type [1] | Description                                                |

|---------|--------------|-------------------|------------------------------------------------------------|

| 0x00    | 16           | R/W               | STS-12/12c and SONET/SDH mode selection                    |

| 0x01    | 16           | R/O               | Receive B1 error count                                     |

| 0x02    | 16           | R/O               | Receive B2 error count                                     |

| 0x03    | 16           | R/O               | Receive B3 error count for SPE 3                           |

| 0x04    | 16           | R/O               | Receive B3 error count for SPE 2                           |

| 0x05    | 16           | R/O               | Receive B3 error count for SPE 1                           |

| 0x06    | 16           | R/O               | Receive B3 error count for SPE 0                           |

| 0x07    | 16           | R/O               | Test Cell Analyzer 3 error count                           |

| 0x08    | 16           | R/O               | Test Cell Analyzer 2 error count                           |

| 0x09    | 16           | R/O               | Test Cell Analyzer 1 error count                           |

| 0x0A    | 16           | R/O               | Test Cell Analyzer 0 error count                           |

| 0x0B    | 16           | R/O               | Received Line FEBE count                                   |

| 0x0C    | 16           | R/O               | Received Path FEBE count for SPE 3                         |

| 0x0D    | 16           | R/O               | Received Path FEBE count for SPE 2                         |

| 0x0E    | 16           | R/O               | Received Path FEBE count for SPE 1                         |

| 0x0F    | 16           | R/O               | Received Path FEBE count for SPE 0                         |

| 0x10    | 16           | R/O               | Test Cell Generator 3 transmitted cells count              |

| 0x11    | 16           | R/O               | Test Cell Generator 2 transmitted cells count              |

| 0x12    | 16           | R/O               | Test Cell Generator 1 transmitted cells count              |

| 0x13    | 16           | R/O               | Test Cell Generator 0 transmitted cells count              |

| 0x14    | 16           | R/O               | Test Cell Analyzer 3 received cells count                  |

| 0x15    | 16           | R/O               | Test Cell Analyzer 2 received cells count                  |

| 0x16    | 16           | R/O               | Test Cell Analyzer 1 received cells count                  |

| 0x17    | 16           | R/O               | Test Cell Analyzer 0 received cells count                  |

| 0x18    | 16           | R/O               | Transmit Cell Processor 3 assigned cells transmitted count |

#### Table 3. Register Organization

| Address | Width (bits) | Register Type [1] | Description                                                |

|---------|--------------|-------------------|------------------------------------------------------------|

| 0x19    | 16           | R/O               | Transmit Cell Processor 2 assigned cells transmitted count |

| 0x1A    | 16           | R/O               | Transmit Cell Processor 1 assigned cells transmitted count |

| 0x1B    | 16           | R/O               | Transmit Cell Processor 0 assigned cells transmitted count |

| 0x1C    | 16           | R/O               | Transmit Cell Processor 3 idle cells transmitted count     |

| 0x1D    | 16           | R/O               | Transmit Cell Processor 2 idle cells transmitted count     |

| 0x1E    | 16           | R/O               | Transmit Cell Processor 1 idle cells transmitted count     |

| 0x1F    | 16           | R/O               | Transmit Cell Processor 0 idle cells transmitted count     |

| 0x20    | 16           | R/O               | Receive Cell Processor 3 assigned cells received count     |

| 0x21    | 16           | R/O               | Receive Cell Processor 2 assigned cells received count     |

| 0x22    | 16           | R/O               | Receive Cell Processor 1 assigned cells received count     |