# ASSP For Screen Display Control

# **On-Screen Display Controller**

# **MB90099**

#### **■ DESCRIPTION**

The MB90099 is an on-screen display controller for displaying text and graphics on the TV screen. The three-channel output control function, compact package and low voltage operation make this device suitable for on-screen displays in portable devices including camera-integrated VTRs and digital still cameras.

The MB90099 controls a display area of 28 characters by 12 lines, and provides 1,024 different characters, each composed of  $12 \times 18$  dots. All 1,024 characters in font ROM can be set by the user. The display functions include a wealth of characters with qualifying functions such as character background shading (shadow casting) and individual character size setting, with 16-color display selection for each character. Also included are the line background, screen background, and sprite character functions, providing a wide variety of screen display capabilities.

#### **■ FEATURES**

Character screen 28 characters × 12 lines (maximum) configuration :

• Character types: 1,024 characters (integrated in ROM, user definable through the entire area)

(Continued)

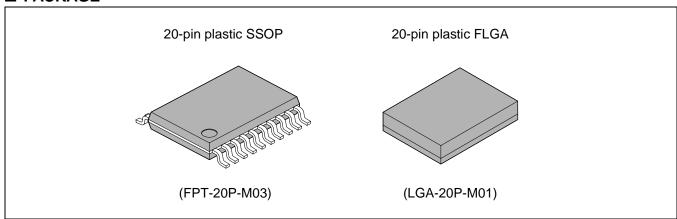

#### **■ PACKAGE**

(Continued)

• Font configuration : 12 × 18 dots (font ROM comfiguration)

Horizontal/vertical character display size setting enabled.

Two horizontal width settings (S/L) per character.

S size : 6 dots L size : 12 dots

Two vertical height settings (HA/HB) per line.

HA: 18 dots HB: 12 dots

• Display modes : Character trimming : Enabled/Disabled (set for each line)

Character background:

None/Solid-fill/Shaded background (concave) /Shaded background (convex)

(set for each character)

Horizontal character merge/independent display with shaded background (set for

each character)

Vertical line merge/independent display with shaded background (set for each line)

Character background display extended to line spacings: Enabled/Disabled (set

for

each line)

Line background:

None/Solid-fill/Shaded background (concave) /Shaded background (convex)

(set for each line)

(Display extends into left and right screen margins and into line spacings)

Character enlargement:

4 types: Normal, Double width, Double height, Double width x double height (set

for each line)

Enlarged character dot interpolation function (set for each line)

Character screen display position control: Horizontal display position:

Control in 2-dot units (movable through the entire screen)

Vertical display position:

Control in 2-dot units (movable through the entire screen)

Line spacing control:

Control in 1-dot units (set between 0 to 7 dots for each line, applied simultaneously

to two areas above and below the line)

Sprite character control :

Sprite character display: Enable/Disabled

Sprite character types: 256 types (character codes 000H to 0FFH)

Sprite character trimming: Enabled/Disabled

Sprite character configuration: 2 types: 1 character/Stack of 2 characters

Sprite character horizontal display position: Control in 1-dot units (movable through

the entire screen)

Sprite character vertical display position : Control in 1-dot units (movable through

the entire screen)

Screen background

Screen background color: Enabled/Disabled

control:

• Display colors : Character color: 16 colors (set for each character)

Character trimming color: 16 colors (set for each line)

Character background color: 16 colors (set for each character) \*

Line background color: 16 colors (set for each line)

Screen background color: 16 colors Sprite character color: 16 colors

Sprite character trimming color: 16 colors

Shaded background frame highlight color: 16 colors Shaded background frame shadow color: 16 colors

· Display signal Color signal output: 4 bits (supports 16 colors)

output: Display period signals: 3 channels (output selector circuit provided)

• External interface : 16-bit serial input:

Chip select Serial clock Serial data

• Package: SSOP-20

FLGA-20

2.4 V to 3.6 V Supply voltage :

<sup>\*:</sup> Character background color (color code) = "0" is transparent (displays lower-layer color).

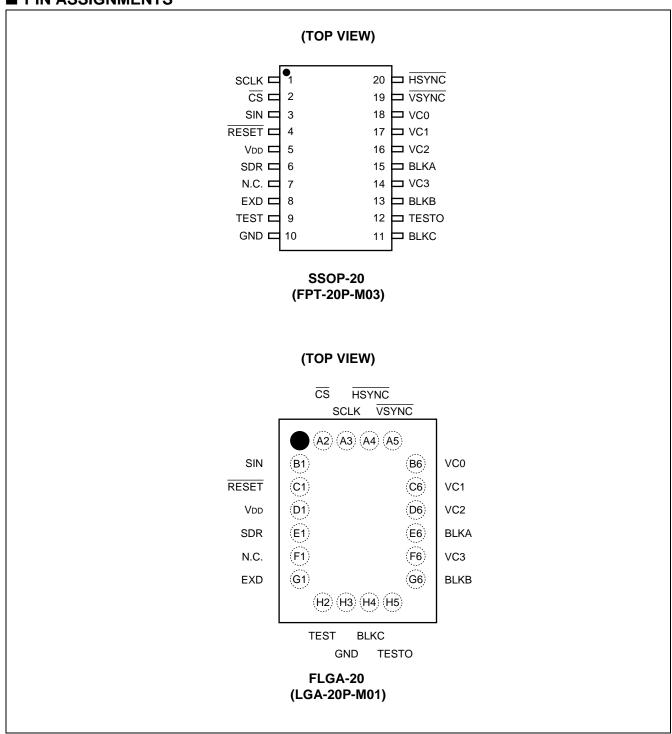

#### **■ PIN ASSIGNMENTS**

## **■ PIN DESCRIPTIONS**

| Pin                  | no.                  | Pin name                 | I/O         | Circuit | Function                                                                                                                                                     |

|----------------------|----------------------|--------------------------|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP                 | FLGA                 | Pin name                 | 1/0         | type    | Function                                                                                                                                                     |

| 1                    | А3                   | SCLK                     | I           | А       | Shift clock input pin for serial transfer. This pin has an internal pull-up resistor.                                                                        |

| 2                    | A2                   | <del>CS</del>            | I           | А       | Chip select pin. Input a low level signal during serial transfer. This pin has an internal pull-up resistor.                                                 |

| 3                    | B1                   | SIN                      | I           | Α       | Serial data input pin. This pin has an internal pull-up resistor.                                                                                            |

| 4                    | C1                   | RESET                    | I           | В       | Reset input pin. Input a low level signal at power-on time.                                                                                                  |

| 5                    | D1                   | V <sub>DD</sub>          |             |         | +3 V power supply pin.                                                                                                                                       |

| 6                    | E1                   | SDR                      | I           | С       | Data input direction select pin for serial transfer. Input a low level signal at LSB-first transfer mode, or a high level signal at MSB-first transfer mode. |

| 7                    | F1                   | N.C.                     |             |         | Not connected. This pin should be left open.                                                                                                                 |

| 8                    | G1                   | EXD                      | I           | В       | Display dot clock input pin.                                                                                                                                 |

| 9                    | H2                   | TEST                     | I           | С       | LSI test input pin. Input a low level signal during normal use.                                                                                              |

| 10                   | НЗ                   | GND                      |             |         | Ground pin.                                                                                                                                                  |

| 11                   | H4                   | BLKC                     | 0           | D       | Display period signal output pin for output channel C.                                                                                                       |

| 12                   | H5                   | TESTO                    | 0           | D       | LSI test output pin. This pin should be left open during normal use.                                                                                         |

| 13                   | G6                   | BLKB                     | 0           | D       | Display period signal output pin for output channel B.                                                                                                       |

| 15                   | E6                   | BLKA                     | 0           | D       | Display period signal output pin for output channel A.                                                                                                       |

| 14<br>16<br>17<br>18 | F6<br>D6<br>C6<br>B6 | VC3<br>VC2<br>VC1<br>VC0 | 0<br>0<br>0 | D       | Color code signal output pins.                                                                                                                               |

| 19                   | A5                   | VSYNC                    | l           | В       | Vertical synchronization signal input pin.                                                                                                                   |

| 20                   | A4                   | HSYNC                    | Ī           | В       | Horizontal synchronization signal input pin.                                                                                                                 |

# ■ I/O CIRCUIT TYPES

| Туре | Circuit | Remarks                                                                              |

|------|---------|--------------------------------------------------------------------------------------|

| А    |         | CMOS level, hysteresis input, pullup resistance (25 k $\Omega$ to 200 k $\Omega$ ) . |

| В    |         | CMOS level, hysteresis input.                                                        |

| С    |         | CMOS level input.                                                                    |

| D    | Output  | CMOS level output.                                                                   |

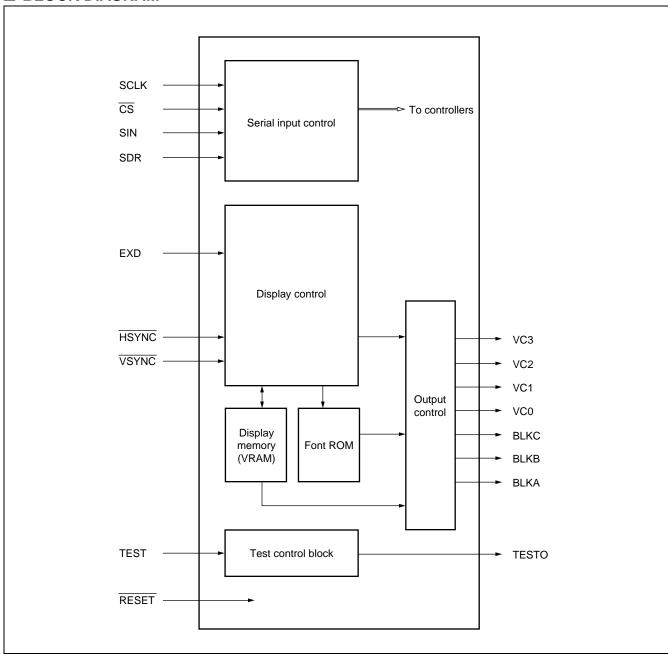

# **■ BLOCK DIAGRAM**

#### **■ COMPONENT ELEMENTS**

- Serial input control block

- Receives serial commands and data. Decodes commands, and allocates commands and data to the appropriate control blocks.

- · Display control block

- Performs display control functions synchronized with the input sync signals.

- Display memory (VRAM) block VRAM memory for character data (24 bits  $\times$  28 characters  $\times$  12 lines) and line data (24 bits  $\times$  12 lines) .

- Font ROM block

- ROM memory for display character fonts. Configured for 1,024 characters of 12 dots  $\times$  18 dots.

- Output control block

- Generates output signals by applying display processing to the font data read from the font ROM.

- Test control block

- Circuits for factory testing of the LSI before delivery.

#### ■ ABSOLUTE MAXIMUM RATINGS

$(V_{GND} = 0 V)$

| Parameter             | Symbol          | Rat                    | ing                    | Unit | Remarks |

|-----------------------|-----------------|------------------------|------------------------|------|---------|

| Farameter             | Syllibol        | Min.                   | Max.                   | Onit | Remarks |

| Power supply voltage  | V <sub>DD</sub> | $V_{\text{GND}}-0.5$   | V <sub>GND</sub> + 4.0 | V    |         |

| Input voltage         | Vin             | V <sub>GND</sub> - 0.5 | V <sub>DD</sub> + 0.5  | V    |         |

| Output voltage        | Vouт            | V <sub>GND</sub> - 0.5 | V <sub>DD</sub> + 0.5  | V    |         |

| Power consumption     | Pd              |                        | 100                    | mW   |         |

| Operating temperature | Та              | -20                    | +70                    | °C   |         |

| Storage temperature   | Tstg            | <b>-55</b>             | +150                   | °C   |         |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### **■ RECOMMENDED OPERATING CONDITIONS**

$(V_{GND} = 0 V)$

| Parameter                 | Symbol          | Va                  | lue                   | Unit  | Remarks |

|---------------------------|-----------------|---------------------|-----------------------|-------|---------|

| Faranietei                | Syllibol        | Min.                | Max.                  | Oille | Remarks |

| Power supply voltage      | V <sub>DD</sub> | 2.4                 | 3.6                   | V     |         |

| "H" level input voltage 1 | Vihs            | $0.8 \times V_{DD}$ | V <sub>DD</sub> + 0.3 | V     | *1      |

| "L" level input voltage 1 | VILS            | V <sub>GND</sub>    | 0.2 × V <sub>DD</sub> | V     | *1      |

| "H" level input voltage 2 | ViH             | $0.7 \times V_{DD}$ | V <sub>DD</sub> + 0.3 | V     | *2      |

| "L" level input voltage 2 | VIL             | V <sub>GND</sub>    | $0.3 \times V_{DD}$   | V     | *2      |

| Operating temperature     | Та              | -20                 | +70                   | °C    |         |

<sup>\*1:</sup> Input pins excluding TEST and SDR pins.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

> No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

<sup>\*2:</sup> TEST and SDR input pins.

# **■ ELECTRICAL CHARACTERISTICS**

## 1. DC Characteristics

$(V_{GND} = 0 \text{ V}, \text{ Ta} = -20 \text{ }^{\circ}\text{C to } +70 \text{ }^{\circ}\text{C})$

| Parameter                | Sym-  | Pin name              | Conditions                                                         |                       | Value |                 | Unit |

|--------------------------|-------|-----------------------|--------------------------------------------------------------------|-----------------------|-------|-----------------|------|

| Faranietei               | bol   | Finitianie            | Conditions                                                         | Min.                  | Тур.  | Max.            | Onne |

| "H" level output voltage | Vон   | VC3, VC2, VC1, VC0,   | $V_{DD} = 3.3 \text{ V}$<br>$I_{OH} = -4 \text{ mA}$               | V <sub>DD</sub> - 0.5 |       | V <sub>DD</sub> | V    |

| "L" level output voltage | Vol   | BLKC, BLKB, BLKA      | $V_{DD} = 3.3 \text{ V}$ $I_{OL} = 4 \text{ mA}$                   | Vgnd                  | _     | 0.4             | V    |

| "H" level input current  | Іін   | SDR,<br>HSYNC, VSYNC, | $\begin{array}{c} V_{DD} = 3.3 \ V \\ V_{IH} = V_{DD} \end{array}$ | _                     | _     | +10             | μА   |

| "L" level input current  | IIL   | EXD, TEST,<br>RESET   | V <sub>DD</sub> = 3.3 V<br>V <sub>IL</sub> = 0 V                   | _                     | _     | -10             | μА   |

| Pull-up resistance       | Rpull | SIN, SCLK, CS         | $V_{DD} = 3.3 \text{ V}$                                           | 25                    | 50    | 200             | kΩ   |

| Power supply current     | Icc   | V <sub>DD</sub>       | $V_{DD} = 2.4 \text{ V}$<br>$f_{DC} = 8 \text{ MHz}$               | _                     | _     | 5               | mA   |

| Fower supply current     | ICC   | טט ע                  | $V_{DD} = 3.6 \text{ V}$<br>$f_{DC} = 8 \text{ MHz}$               | _                     | _     | 6               | mA   |

| Input capacitance        | С     | Except VDD, GND       | _                                                                  |                       |       | 16              | pF   |

#### 2. AC Characteristics

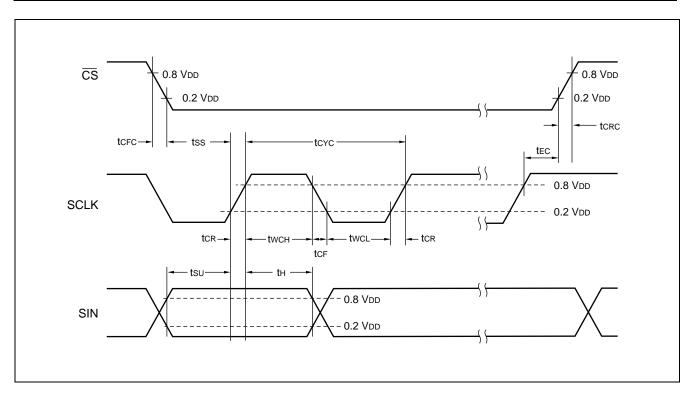

## (1) Serial input timings

(VDD = 2.4 V to 3.6 V, VGND = 0 V, Ta = -20 °C to +70 °C)

| Parameter                                                | Symbol       | Pin name     | Val  | lue  | Unit  |

|----------------------------------------------------------|--------------|--------------|------|------|-------|

| Farameter                                                | Syllibol     | Pili liaille | Min. | Max. | Offic |

| Shift clock cycle time                                   | <b>t</b> cyc | SCLK         | 250  |      | ns    |

| Shift clock pulse width                                  | twcн         | SCLK         | 100  | _    | ns    |

| Shift clock pulse width                                  | twcL         | SOLK         | 100  |      | ns    |

| Shift clock signal rise/fall time Shift clock start time | <b>t</b> cr  | SCLK         |      | 200  | ns    |

|                                                          | <b>t</b> CF  | SOLK         | _    | 200  | ns    |

| Shift clock start time                                   | tss          | SCLK         | 100  |      | ns    |

| Data setup time                                          | <b>t</b> su  | SIN          | 100  | _    | ns    |

| Data hold time                                           | tн           | SIN          | 50   |      | ns    |

| Chip select end time                                     | <b>t</b> EC  | CS           | 100  |      | ns    |

| Chip select signal rise/fall time                        | tcrc         | - CS         |      | 200  | ns    |

| Chip select signal fise/fall time                        | <b>t</b> cFC |              | _    | 200  | ns    |

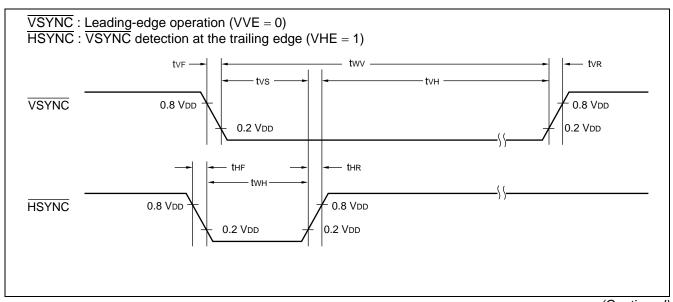

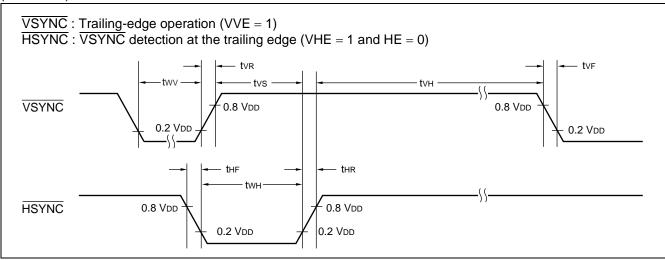

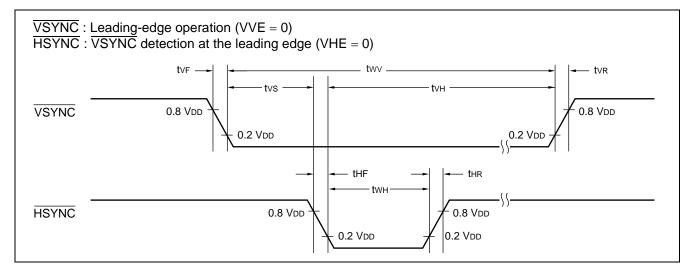

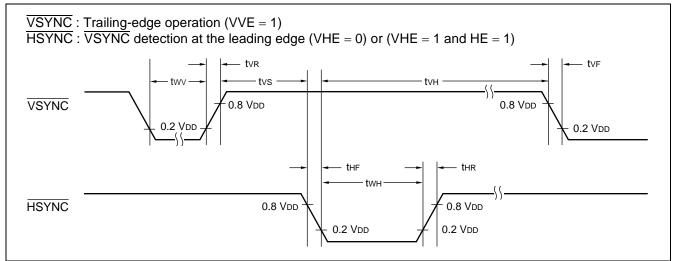

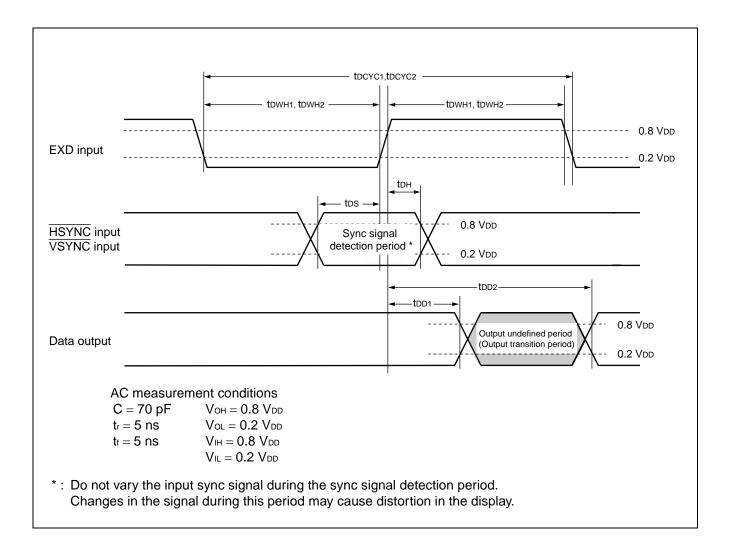

#### (2) Vertical and horizontal sync signal input timing

| Parameter                                                                    | Symbol      | Pin name     | Val  | ue      | Unit      |  |

|------------------------------------------------------------------------------|-------------|--------------|------|---------|-----------|--|

| Farameter                                                                    | Symbol      | riii iiaiiie | Min. | Max.    | Onit      |  |

| Horizontal sync signal rise time                                             | <b>t</b> HR | HSYNC        | _    | 200     | ns        |  |

| Horizontal sync signal fall time                                             | thf         | HOTING       | _    | 200     | ns        |  |

| Vertical sync signal rise time                                               | tvr         | VSYNC        | _    | 200     | ns        |  |

| Vertical sync signal fall time                                               | t∨F         | VOTING       | _    | 200     | ns        |  |

| Horizontal sync signal pulse width *1                                        | <b>t</b> wн | HSYNC        | 18   | _       | Dot clock |  |

| Fiorizoniai sync signai puise widin                                          |             | TISTING      | _    | 6       | μS        |  |

| Vertical sync signal setup time1 *2 (Except for VVE = 1, VHE = 1, HE = 1) *3 | tvs         | VSYNC        | 4    | 1H – 4  | Dot clock |  |

| Vertical sync signal setup time2 *2 (VVE = 1, VHE = 1, HE = 1) *3            | tvs         | VSYNC        | - 6  | 1H – 14 | Dot clock |  |

| Vertical sync signal detection hold time                                     | tvн         | VSYNC        | 2    |         | Н         |  |

| Vertical sync signal pulse width                                             | twv         | VSYNC        | 2    | 20      | Н         |  |

<sup>\*1 :</sup> During the horizontal sync signal pulse period, the MB90099 stops its internal operation, disabling writing to the internal VRAM. Therefore, the horizontal sync signal pulse width and VRAM write cycle (command 2 or command 4 issuance cycle) should be set so that the horizontal sync signal pulse width is shorter than the VRAM write cycle.

- \*2 : In the vertical sync signal detection cycle, do not change the vertical sync signal (detection edge) when it is close to the horizontal sync signal edge. This may result in distortion of the display due to fluctuations in the sync signal.

- \*3: VVE, VHE and HE are control bits of Command 13-0 (I/O pin control).

(Continued)

### (Continued)

Note: The above diagrams assume that I/O pin control command (command 13-0) has set the sync signal input logic control setting (SIX bit) to negative logic ("0"). However, if the positive logic setting (SIX bit = "1")□ is used, the H and L levels are reversed.

#### (3) Dot clock external input timing

$(V_{DD} = 2.7 \text{ V to } 3.3 \text{ V}, V_{GND} = 0 \text{ V}, Ta = -20 ^{\circ}\text{C to } +70 ^{\circ}\text{C})$

| Parameter                | Symbol                        | Pin name         | Va           | lue          | Unit  | Note |  |

|--------------------------|-------------------------------|------------------|--------------|--------------|-------|------|--|

| raiailletei              | Syllibol                      | Fili lialile     | Min.         | Max.         | Oilit | Note |  |

| Dot clock cycle time     | tDCYC1                        | EXD              | 112          | 166          | ns    | *1   |  |

| Dot clock cycle time     | tDCYC2                        | EXD              | 56           | 83           | ns    | *2   |  |

|                          | <b>t</b> DWH1                 | EXD              | 48           |              | ns    | - *1 |  |

| Dot clock pulse time     | <b>t</b> DWL1                 | LAD              | 48           |              | ns    |      |  |

| Dot clock pulse time     | <b>t</b> DWH2                 | EXD              | 24           |              | ns    | *2   |  |

|                          | t <sub>DWL2</sub>             | LAD              | 24           |              | ns    | 7 4  |  |

| HSYNC, VSYNC setup time  | <b>t</b> DS                   | HSYNC,           | 13           |              | ns    | *3   |  |

| HSYNC, VSYNC hold time   | tон                           | VSYNC            | 0            |              | ns    | *3   |  |

| Data output delay time 1 | Data output delay time 1 toD1 |                  | 7            | <b>t</b> DD2 | ns    | *3   |  |

| Data output delay time 2 | <b>t</b> DD2                  | BLKA, BLKB, BLKC | <b>t</b> DD1 | 45           | ns    | ] 3  |  |

Note : The above items assume a supply voltage of  $V_{DD} = 2.7 \text{ V}$  to 3.3 V.

<sup>\*1 :</sup> Assuming input frequency = dot clock  $\times$  1.

<sup>\*2 :</sup> Assuming input frequency = dot clock  $\times$  2.

<sup>\*3 :</sup> Assuming input frequency = dot clock  $\times$  1 or dot clock  $\times$  2.

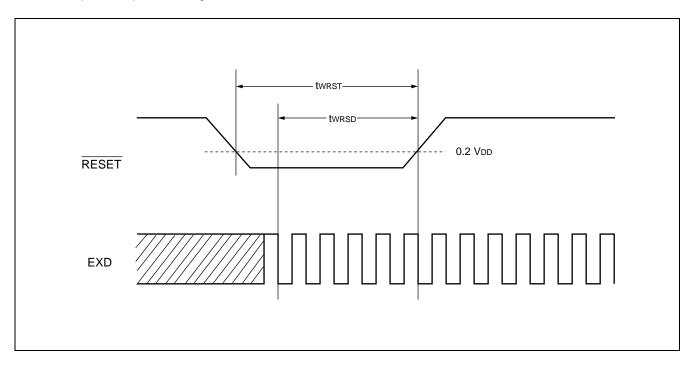

### (4) Reset input timing

(V<sub>DD</sub> = 2.4 V to 3.6 V, V<sub>GND</sub> = 0 V, Ta = -20 °C to +70 °C)

| Parameter         | Symbol        | Pin name    | Va   | lue  | Unit      | Note |

|-------------------|---------------|-------------|------|------|-----------|------|

| Faranietei        | Syllibol      | Fill Hallie | Min. | Max. | Offic     | Note |

| Reset pulse width | <b>t</b> wrst | RESET       | 1    | _    | μS        |      |

| Clock input       | twrsd         | EXD         | 5    |      | Dot clock | *    |

<sup>\*:</sup> Clock input is required during reset.

# ■ DISPLAY CONTROL COMMANDS

## 1. Command list

| Com-        | Frantian                                    |          |     |     |     | Со  | mman | d cod | e/data | l   |     |     |     |     |

|-------------|---------------------------------------------|----------|-----|-----|-----|-----|------|-------|--------|-----|-----|-----|-----|-----|

| mand<br>no. | Function                                    | 15 to 12 | 11  | 10  | 9   | 8   | 7    | 6     | 5      | 4   | 3   | 2   | 1   | 0   |

| 0           | VRAM write address setting                  | 0000     | AY3 | AY2 | AY1 | AY0 | FL   | 0     | 0      | AX4 | AX3 | AX2 | AX1 | AX0 |

| 1           | Character data setting 1                    | 0001     | MO1 | MO0 | MM1 | MM0 | MB3  | MB2   | MB1    | MB0 | МС3 | MC2 | MC1 | MC0 |

| 2           | Character data setting 2                    | 0010     | MR  | MS  | M9  | M8  | M7   | M6    | M5     | M4  | МЗ  | M2  | M1  | МО  |

| 3           | Line control data setting 1                 | 0011     | LHS | LW2 | LW1 | LW0 | LFD  | LFC   | LFB    | LFA | LF3 | LF2 | LF1 | LF0 |

| 4           | Line control data setting 2                 | 0100     | LDS | LGS | LG1 | LG0 | LD   | LE    | LM1    | LM0 | L3  | L2  | L1  | L0  |

| 5-00        | Screen output control 1A                    | 0101     | 0   | 0   | 0   | 0   | SDS  | UDS   | 0      | DSP | 0   | OA2 | OA1 | OA0 |

| 5-01        | Screen output control 1B                    | 0101     | 0   | 0   | 0   | 1   | SOB  | BGB   | BLB    | 0   | 0   | OB2 | OB1 | ОВ0 |

| 5-02        | Screen output control 1C                    | 0101     | 0   | 0   | 1   | 0   | SOC  | BGC   | BLC    | 0   | 0   | OC2 | OC1 | OC0 |

| 5-2         | Vertical display position control           | 0101     | 1   | 0   | 0   | Y8  | Y7   | Y6    | Y5     | Y4  | Y3  | Y2  | Y1  | Y0  |

| 5-3         | Horizontal display position control         | 0101     | 1   | 1   | 0   | X8  | X7   | X6    | X5     | X4  | Х3  | X2  | X1  | X0  |

| 6-1         | Shaded<br>background frame<br>color control | 0110     | 0   | 1   | 0   | 0   | ВН3  | BH2   | BH1    | ВН0 | BS3 | BS2 | BS1 | BS0 |

| 7-3         | Screen<br>background<br>control             | 0111     | 1   | 1   | 0   | 0   | 0    | 0     | 0      | 0   | U3  | U2  | U1  | U0  |

| 8-0         | Sprite character control 1                  | 1000     | 0   | 0   | SFB | SFA | SF3  | SF2   | SF1    | SF0 | SC3 | SC2 | SC1 | SC0 |

| 8-1         | Sprite character control 2                  | 1000     | 0   | 1   | SD1 | SD0 | SM7  | SM6   | SM5    | SM4 | SM3 | SM2 | SM1 | SM0 |

| 9-0         | Sprite character control 4                  | 1001     | 0   | 0   | SY9 | SY8 | SY7  | SY6   | SY5    | SY4 | SY3 | SY2 | SY1 | SY0 |

| 9-1         | Sprite character control 5                  | 1001     | 1   | 0   | SX9 | SX8 | SX7  | SX6   | SX5    | SX4 | SX3 | SX2 | SX1 | SX0 |

| 11-0        | Screen extension control                    | 1011     | 0   | 0   | 0   | 0   | 0    | EG0   | 0      | 0   | 0   | 0   | 0   | 0   |

| 11-2        | Dot clock control 1                         | 1011     | 1   | 0   | 0   | 0   | 0    | 0     | 0      | 0   | 0   | DC2 | DC1 | DC0 |

(Continued)

# (Continued)

| Com-<br>mand<br>no. | Function                      | Command code/data |    |    |     |     |     |     |     |     |     |     |     |     |

|---------------------|-------------------------------|-------------------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                     |                               | 15 to 12          | 11 | 10 | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 13-0                | I/O pin control               | 1101              | 0  | 0  | VVE | VHE | HE  | 0   | SIX | 0   | 0   | 0   | DBX | DCX |

| 13-1                | Horizontal blanking control 1 | 1101              | 0  | 1  | 0   | 0   | 0   | 0   | BB5 | BB4 | BB3 | BB2 | BB1 | BB0 |

| 13-2                | Horizontal blanking control 2 | 1101              | 1  | 0  | 0   | BF8 | BF7 | BF6 | BF5 | BF4 | BF3 | BF2 | BF1 | BF0 |

#### 2. Command Description

#### • Command 0 (VRAM write address setting)

Command 0 sets the write address in VRAM, and controls the execution of "VRAM fill". The write address is specified by row and column addresses. VRAM fill is activated by executing character data setting 2 (command 2).

| 15 | 14 | 13 | 12 | 11  | 10  | 9   | 8   | 7  | 6 | 5 | 4   | 3   | 2   | 1   | 0   |   |

|----|----|----|----|-----|-----|-----|-----|----|---|---|-----|-----|-----|-----|-----|---|

| 0  | 0  | 0  | 0  | AY3 | AY2 | AY1 | AY0 | FL | 0 | 0 | AX4 | AX3 | AX2 | AX1 | AX0 | l |

AY3 to AY0: Row address (0 to B<sub>H</sub>)

AX4 to AX0 : Column address (0 to 1B<sub>H</sub>)

FL: VRAM Fill control (0: OFF, 1: ON)

#### • Command 1 (Character data setting 1)

Command 1 specifies character data. The character data is written to VRAM and reflected on the screen by the execution of command 2 (character data setting 2).

| 15 | 14 | 13 | 12 | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _ |

|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 0  | 0  | 0  | 1  | MO1 | MO0 | MM1 | ММО | MB3 | MB2 | MB1 | МВ0 | МС3 | MC2 | MC1 | MC0 |   |

MO1, MO0: Character output control

MM1, MM0: Character background control

(0, 0 : Off) (0, 1 : Solid fill)

(1, 0 : Concaved shaded)

(1, 1: Convexed shaded)

MC3 to MC0 : Character color (16 colors)

MB3 to MB0: Background color (16 colors)

#### • Command 2 (Character data setting 2)

Command 2 writes additional character data to the location in VRAM spacified by command 0 (VRAM write address setting), along with the character data set by command 1 (character data setting 1).

The VRAM write address is automatically incremented after command 2 is executed.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | /  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   | 0  | 0  | 1  | 0  | MR | MS | М9 | M8 | M7 | M6 | M5 | M4 | МЗ | M2 | M1 | M0 |

MR: Shaded background succeeding character merge control

(0 : Not merged with succeeding character)

(1 : Merged with succeeding character)

MS: Character horizontal size control

(0 : S size, 6 dots) (1 : L size, 12 dots)

M9 to M0: Character code

#### • Command 3 (Line control data setting 1)

Command 3 specifies line control data. The line control data is written to VRAM and reflected on the screen by the execution of command 4 (line control data setting 2).

| 15 | 14 | 13 | 12 | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 1  | 1  | LHS | LW2 | LW1 | LW0 | LFD | LFC | LFB | LFA | LF3 | LF2 | LF1 | LF0 |

LHS: Line character vertical size type control

(0 : Character vertical size A)

(1 : Character vertical size B)

LW2 to LW0 : Line spacing control

(0 to 7 dots, in 1-dot units)

LF3 to LF0: Trimming color (16 colors)

LFD, LFC: Trimming output control

(0, 0 : All Off)

(0, 1: Trimming On for a character only, no character background)

(1, 0 : Trimming On for a solid-fill character or no character background)

(1, 1 : All On)

LFB, LFA: Trimming control

(0, 0: Trimming Off)

(0, 1: Reserved (setting prohibited))

(1, 0: Reserved (setting prohibited))

(1, 1 : Eight-direction trimming)

#### • Command 4 (Line control data setting 2)

Command 4 specifies additional line control data and writes this data, along with the line control data set by command 3 (line control data setting 1) to the row address in VRAM specified by command 0 (VRAM write address setting).

Executing this command will not alter the VRAM write address.

| 15 | 14 | 13 | 12 | 11  | 10  | 9   | 8   | 7  | 6  | 5   | 4   | 3  | 2  | 1  | 0  |

|----|----|----|----|-----|-----|-----|-----|----|----|-----|-----|----|----|----|----|

| 0  | 1  | 0  | 0  | LDS | LGS | LG1 | LG0 | LD | LE | LM1 | LM0 | L3 | L2 | L1 | LO |

LDS: Line character output control (control of a character + trimming + character background)

(0: Off, 1: On)

LGS: Line enlargement interpolation control

(0: Off, 1: On)

LG1, LG0: Line enlargement control

(0, 0 : Normal)

(0, 1 : Double width)

(1, 0 : Double height)

$(1, 1 : Double width \times double height)$

LE: Character background extension control

(0 : Normal, 1 : Extended)

LD: Shaded background succeeding line merge control

(0: Independent)

(1 : Merged with succeeding line)

LM1, LM0: Line background control

(0, 0 : Off)

(0, 1 : Solid fill)

(1, 0 : Concaved shaded)

(1, 1 : Convexed shaded)

L3 to L0: Line background color (16 colors)

#### • Command 5-00 (Screen output control 1A)

Command 5-00 controls screen display output.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5 | 4   | 3 | 2   | 1   | 0   |

|---|----|----|----|----|----|----|---|---|-----|-----|---|-----|---|-----|-----|-----|

|   | 0  | 1  | 0  | 1  | 0  | 0  | 0 | 0 | SDS | UDS | 0 | DSP | 0 | OA2 | OA1 | OA0 |

SDS: Sprite character output control

(0: Off, 1: On) \*

UDS: Screen background output control

(0: Off, 1: On) \*

DSP: Display output control (Control of a character + trimming + character background + line background)

(0: Off, 1: On) \*

OA2 to OA0: Output-A character control (8 types)

#### • Command 5-01 (Screen output control 1B)

Command 5-01 controls output-B screen display output.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4 | 3 | 2   | 1   | 0   |

|---|----|----|----|----|----|----|---|---|-----|-----|-----|---|---|-----|-----|-----|

|   | 0  | 1  | 0  | 1  | 0  | 0  | 0 | 1 | SOB | BGB | BLB | 0 | 0 | OB2 | OB1 | ОВ0 |

SOB: Output-B sprite character output control

(0: Off, 1: On)

BGB: Output-B screen background output control

(0: Off, 1: On)

BLB: Output-B line background output control

(0: Off, 1: On)

OB2 to OB0 : Output-B character control (8 types)

<sup>\*:</sup> Input of an 'L' level signal to the RESET pin will initialize SDS = 0, UDS = 0, and DSP = 0.

#### • Command 5-02 (Screen output control 1C)

Command 5-02 controls output-C screen display output.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4 | 3 | 2   | 1   | 0   |

|---|----|----|----|----|----|----|---|---|-----|-----|-----|---|---|-----|-----|-----|

|   | 0  | 1  | 0  | 1  | 0  | 0  | 1 | 0 | soc | BGC | BLC | 0 | 0 | OC2 | OC1 | OC0 |

SOC: Output-C sprite character output control

(0: Off, 1: On)

BGC: Output-C screen background output control

(0: Off, 1: On)

BLC: Output-C line background output control

(0: Off, 1: On)

OC2 to OC0 : Output-C character control (8 types)

#### • Command 5-2 (Vertical display position control)

Command 5-2 controls the vertical display position on the screen.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|---|----|----|----|----|----|----|----|----|----|

| 0  | 1  | 0  | 1  | 1  | 0  | 0 | Y8 | Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 |

Y8 to Y0: Vertical display position control (0 to 1022 in 2-dot units)

#### • Command 5-3 (Horizontal display position control)

Command 5-3 controls the horizontal display position on the screen.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|---|----|----|----|----|----|----|----|----|----|

| 0  | 1  | 0  | 1  | 1  | 1  | 0 | X8 | Х7 | X6 | X5 | X4 | Х3 | X2 | X1 | X0 |

X8 to X0: Horizontal display position control (0 to 1022 in 2-dot units)

#### • Command 6-1 (Shaded background frame color control)

Command 6-1 controls the frame color of the shaded background.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|----|----|----|----|----|----|---|---|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 1  | 1  | 0  | 0  | 1  | 0 | 0 | ВН3 | BH2 | BH1 | ВН0 | BS3 | BS2 | BS1 | BS0 |

BH3 to BH0: Shaded background frame highlight color (16 colors)

BS3 to BS0 : Shaded background frame shadow color (16 colors)

#### Command 7-3 (Screen background control)

Command 7-3 controls the screen background color.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|---|----|----|----|----|----|----|---|---|---|---|---|---|----|----|----|----|

|   | 0  | 1  | 1  | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | U3 | U2 | U1 | U0 |

U3 to U0: Screen background color (16 colors)

#### • Command 8-0 (Sprite character control 1)

Command 8-0 controls sprite characters.

| 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _ |

|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 1  | 0  | 0  | 0  | 0  | 0  | SFB | SFA | SF3 | SF2 | SF1 | SF0 | SC3 | SC2 | SC1 | SC0 |   |

SFB, SFA: Sprite character trimming control

(0, 0 : Trimming Off) (0, 1 : Reserved) (1, 0 : Reserved)

(1, 1: Eight-direction trimming)

SF3 to SF0: Sprite character trimming color (16 colors)

SC3 to SC0: Sprite character color (16 colors)

#### • Command 8-1 (Sprite character control 2)

Command 8-1 controls sprite characters.

| 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0  | 0  | 0  | 0  | 1  | SD1 | SD0 | SM7 | SM6 | SM5 | SM4 | SM3 | SM2 | SM1 | SM0 |

SD1, SD0: Sprite character configuration control

(0, 0 : 1 character)

(0, 1: Reserved (setting prohibited))

(1, 0: Stack of 2 characters)

(1, 1: Reserved (setting prohibited))

SM7 to SM0 : Sprite character code

(000H to 0FFH for 256 different characters)

#### • Command 9-0 (Sprite character control 4)

Command 9-0 controls the vertical display position of sprite characters.

|   |   |   |   |   |   | 9   |     |     |     |     |     |     |     |     |     |

|---|---|---|---|---|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 | 0 | 0 | 1 | 0 | 0 | SY9 | SY8 | SY7 | SY6 | SY5 | SY4 | SY3 | SY2 | SY1 | SY0 |

SY9 to SY0: Sprite character vertical display position control

(0 to 1023 in 1-dot units)

#### • Command 9-1 (Sprite character control 5)

Command 9-1 controls the horizontal display position of sprite characters.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1  | 0  | 0  | 1  | 1  | 0  | SX9 | SX8 | SX7 | SX6 | SX5 | SX4 | SX3 | SX2 | SX1 | SX0 |

SX9 to SX0 : Sprite character horizontal display position control

(0 to 1023 in 1-dot units)

#### • Command 11-0 (Screen extension control)

(Reserved)

|   |   |   |   |   |   |   |   |   |     |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | EG0 | 0 | 0 | 0 | 0 | 0 | 0 |

EG0: (Reserved) (0: Normal)

(1: Reserved (setting prohibited))

#### • Command 11-2 (Dot clock control 1)

Command 11-2 controls dot clock selection.

| _ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|---|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|-----|-----|

|   | 1  | 0  | 1  | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DC2 | DC1 | DC0 |

DC2 to DC0 : Dot clock selection control (0, 1, 0) : External dot clock input

(0, 1, 1): Frequency-doubled external dot clock input

#### • Command 13-0 (I/O pin control)

Command 13-0 controls I/O pin functions.

|   |   |   |   |   |   |     | 8   |    |   |     |   |   |   |     |     |

|---|---|---|---|---|---|-----|-----|----|---|-----|---|---|---|-----|-----|

| 1 | 1 | 0 | 1 | 0 | 0 | VVE | VHE | HE | 0 | SIX | 0 | 0 | 0 | DBX | DCX |

VVE: Edge selection for vertical synchronization detection\*1

(0 : Leading edge, 1 : Trailing edge)

VHE: HSYNC edge selection for vertical synchronization detection\*1

(0 : Leading edge, 1 : Trailing edge)

HE: Edge selection for horizontal synchronization operation\*1

(0 : Trailing edge, 1 : Leading edge)

SIX: Logic control for sync signal input

(0 : Negative logic, 1 : Positive logic)

DCX: Logic control for display color signal output

(0 : Positive logic, 1 : Negative logic) \*2

DBX: Logic control for display output period signal

(0 : Positive logic, 1 : Negative logic) \*2

| *1 : When it is set up VVE = 1, VHE = 1 and HE = 1, the vertical sync detection | HSYNC edge is the standard of |

|---------------------------------------------------------------------------------|-------------------------------|

| "Leading edge".                                                                 |                               |

| VVE | VHE | HE | Contents of vertical sync detection | Position of vertical sync detection* |

|-----|-----|----|-------------------------------------|--------------------------------------|

| 0   | 0   | 0  | Detection of VSYNC Leading edge     | HSYNC Leading edge                   |

| 0   | 0   | 1  | Detection of VSYNC Leading edge     | HSYNC Leading edge                   |

| 0   | 1   | 0  | Detection of VSYNC Leading edge     | HSYNC Trailing edge                  |

| 0   | 1   | 1  | Detection of VSYNC Leading edge     | HSYNC Trailing edge                  |

| 1   | 0   | 0  | Detection of VSYNC Trailing edge    | HSYNC Leading edge                   |

| 1   | 0   | 1  | Detection of VSYNC Trailing edge    | HSYNC Leading edge                   |

| 1   | 1   | 0  | Detection of VSYNC Trailing edge    | HSYNC Trailing edge                  |

| 1   | 1   | 1  | Detection of VSYNC Trailing edge    | HSYNC Leading edge + 10 clock        |

<sup>\*:</sup> If there is the change of level for direction of VSYNC pin signal detection in the vicinity of vertical sync detection, it may occur disorder in the display (deflection of vertical direction). Input the meaningful edge of VSYNC signal without this position of vertical sync detection.

#### • Command 13-1 (Horizontal blanking control 1)

Command 13-1 controls the back porch of the horizontal blanking function.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|----|----|----|----|----|----|---|---|---|---|-----|-----|-----|-----|-----|-----|

| 1  | 1  | 0  | 1  | 0  | 1  | 0 | 0 | 0 | 0 | BB5 | BB4 | BB3 | BB2 | BB1 | BB0 |

BB5 to BB0 : Back porch control (0 to 126, in 2-dot units)

#### • Command 13-2 (Horizontal blanking control 2)

Command 13-2 controls the front porch of the horizontal blanking function.

| _ |   |   |   |   |   | 10 |   |     |     |     |     |     |     |     |     |     |

|---|---|---|---|---|---|----|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1 | 1 | 0 | 1 | 1 | 0  | 0 | BF8 | BF7 | BF6 | BF5 | BF4 | BF3 | BF2 | BF1 | BF0 |

BF8 to BF0: Front porch control (0 to 1022, in 2-dot units)

<sup>\*2 :</sup> Input of an 'L' level signal to the  $\overline{RESET}$  pin will initialize DCX = 0, and DBX = 0.

#### 3. Notes on Issuing Commands

#### (1) Initialization

When a reset signal is input ("L" level signal input to the RESET pin), the MB90099 enters display-off state(\*). The contents of VRAM (the character RAM and the line RAM) are undefined.

Immediately after release of the input signal to the MB90099, issue the following commands to initialize control operation.

- Dot clock control 1 (command 11-2)

- I/O pin control (command 13-0)

This must be done before setting all command data and all RAM contents. (VRAM settings require normal dot clock input and normal sync signal input.)

\*: The reset input initializes control bits as follows.

Screen output control 1A (command 5-00)

SDS = 0 Sprite Off

UDS = 0 Screen background Off

DSP = 0 Character, character background, line background Off

I/O pin control (command 13-0)

DCX = 0 VC0, VC1, VC2, VC3 pins set to positive logic output

DBX = 0 BLKA, BLKB, BLKC pins set to positive logic output

#### (2) Command refresh

Command data to the MB90099 and the contents of internal VRAM are stored as long as power is supplied to the MB90099. However, there may be cases in which the serial control, sync, or dot clock signals become abnormal due to causes such as external noise, preventing the internal registers and VRAM from being set properly. It is therefore recommended that all command data and VRAM data be refreshed periodically to ensure that this data is correct.

#### (3) Command issue timing

When any control command, including a VRAM write command such as a character data setting or line control data setting command is issued, the command is executed immediately and the result is reflected on the screen. When such a command is issued during a display period, the display in the relevant field may experience momentary distortion. To avoid this, it is recommended that commands be issued during the vertical blanking interval. However that with a command 5-00 (screen output control 1A) in which one or more of the DSP, SDS, or UDS control bits is switched from OFF to ON, the display will wait until the next vertical sync signal after the command is issued and the display will start from the top of the scanning field.

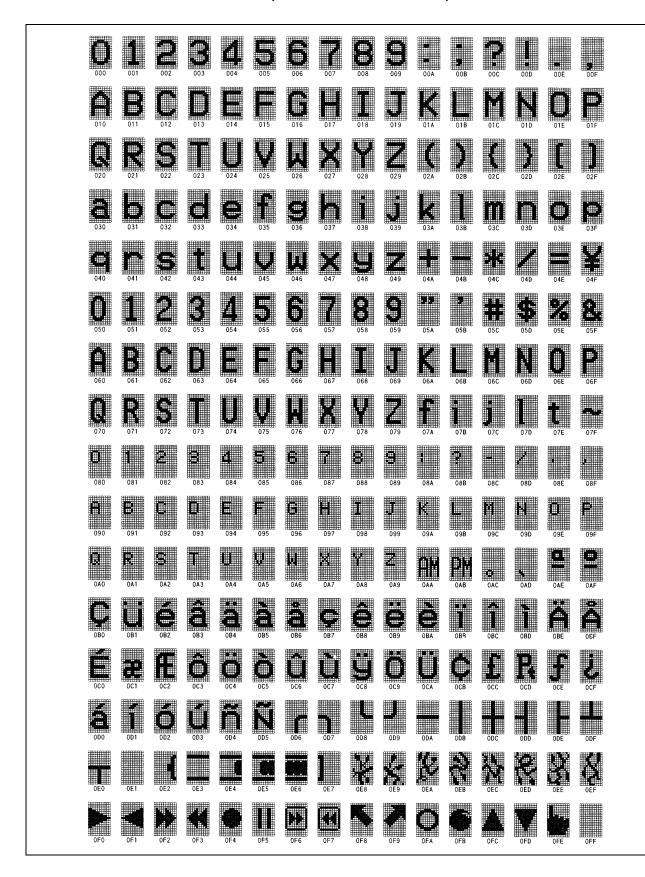

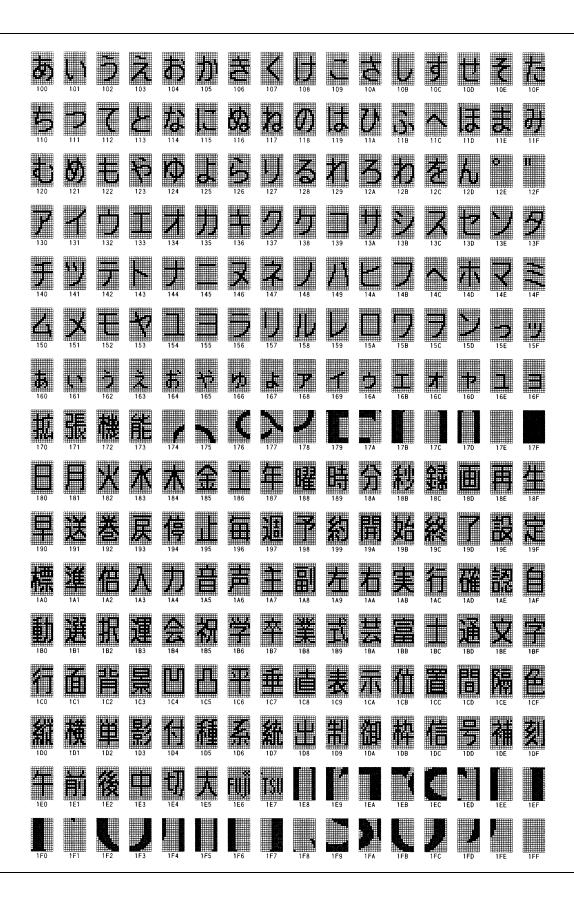

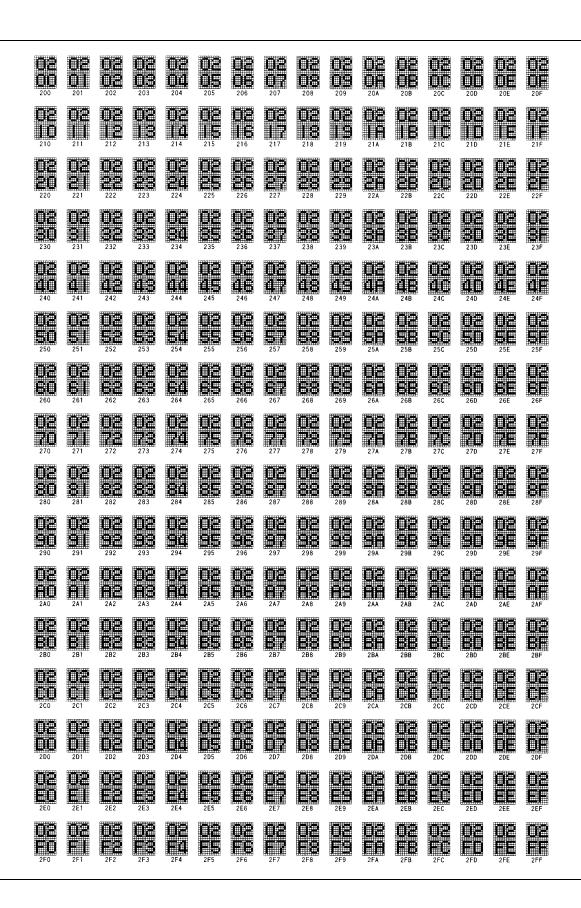

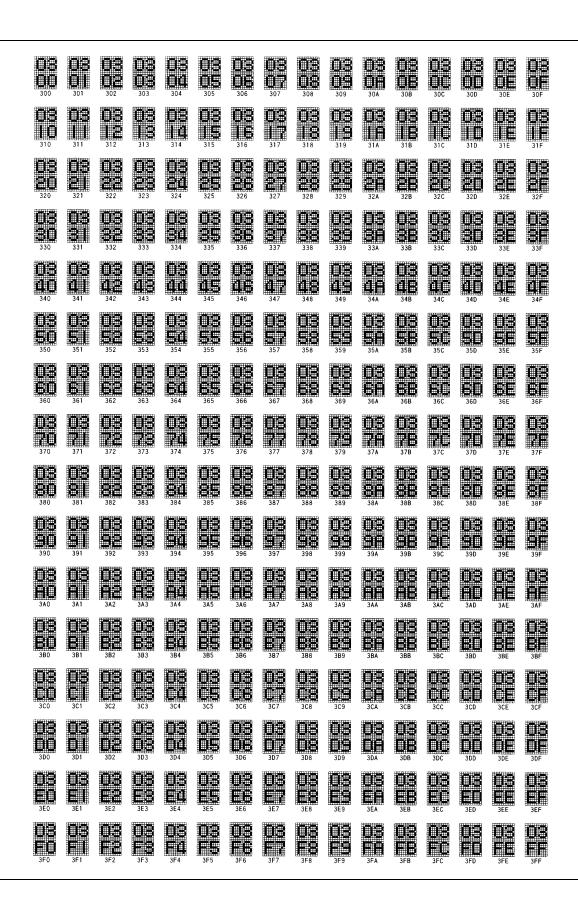

### ■ CONTENTS OF MB90099-001 (STANDARD PRODUCT) FONT DATA

#### **■ FONT DEVELOPMENT AND DATA RELEASE**

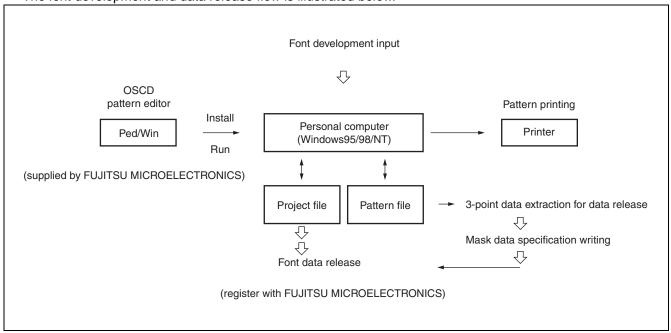

The MB90099 features the font ROM in which all 1024 characters are user-definable. For font data development, use the OSDC pattern editor Ped/Win. Ped/Win is an OSCD proprietary pattern editor for use on personal computers operating Windows95/98/NT4.0 (Japanese language) environments.

The font development and data release flow is illustrated below.

#### (1) Font data release

Font data is released in project files only. Pattern files should not be released. A portion of the pattern file data will be used for data matching in order to verify registration of release data by FUJITSU MICROELECTRONICS. For this reason, users are requested to write a portion of the pattern data content in mask data specifications.

Note: Pattern data output should not be generated until after the completion of font creation and project creation. Also, the project file should not be updated after pattern file generation is completed. If the project contents are updated after pattern file generation, pattern files should be generated again.

#### (2) Project files

After font data and other supplementary data is created, it is stored in a project file. Normally one project file is created for each model.

#### Project file names

Project file names should be in the format "MB90099-XXX" where "XXX" is a ROM number assigned by FUJITSU MICROELECTRONICS. Users should contact their FUJITSU MICROELECTRONICS sales representative. If no ROM number has been assigned, any number preceded by an alphabetic character may be used. Project files which are developed solely for test purposes and not intended for font release may be assigned any file name.

#### · Comments related to new project files

Comment lines in the form of any desired character strings may be added at the time a project file is created. Comments will be printed when the font is printed, and can be modified as needed whenever that Ped/Win is operating.

#### (3) Pattern files

Font data may be placed in pattern files. Because pattern data is saved in the project file, normally it is only necessary to create a pattern file at the time of font release for the purpose of extracting verification data (writing to mask data specifications). Pattern files should not be released.

#### · Pattern file loading

Pattern files can be loaded for some OSCD models other than the MB90099.

#### Pattern file output generation

Do not create more than one pattern file for the same project. This may cause errors . In such cases, the project name should be altered to create another project.

#### · Extracting verification data

Three data points, the first and last addresses and one other random address, should be extracted from pattern file data and written into the mask data specifications. The random address should not include the data values "00" or "FF."

Note: Ped/Win display functions are based on OSDC specifications, however some display specifications may not be identical to actual OSDC specifications. Users should consult specification documents for details.

#### (Data comparison)

After data release, once ROM mask processing is completed FUJITSU MICROELECTRONICS will extract the ROM data used in this process. Users should verify that the extracted data is identical to the pattern file data that was submitted, and return a written statement of data comparison indicating whether that data is identical or not . If the data is not identical, contact FUJITSU MICROELECTRONICS's sales representative immediately. Data errors may cause errors in ES production.

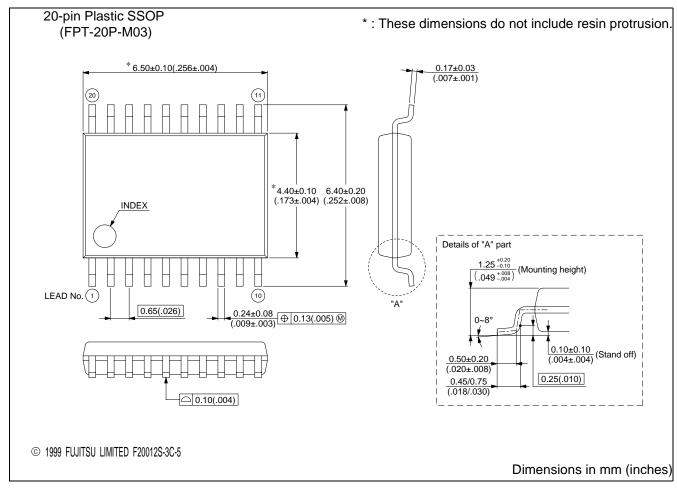

## **■** ORDERING INFORMATION

| Part Number | Package                              | Remarks |

|-------------|--------------------------------------|---------|

| MB90099PFV  | 20-pin Plastic SSOP<br>(FPT-20P-M03) |         |

| MB90099LGA  | 20-pin Plastic FLGA<br>(LGA-20P-M01) |         |

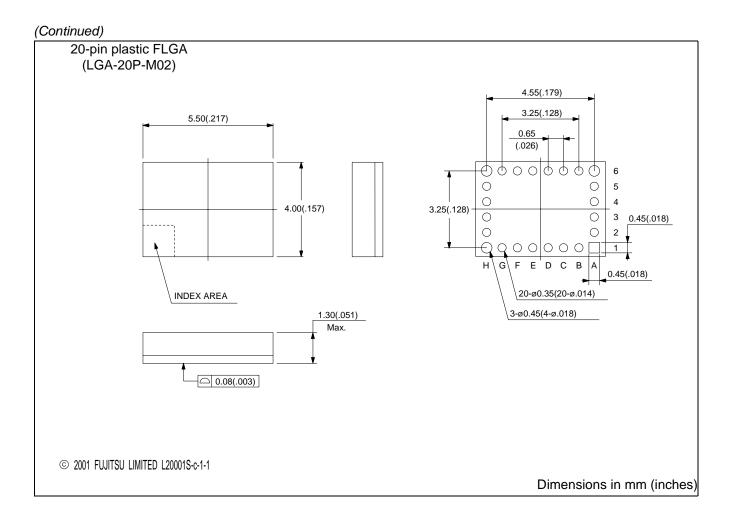

### **■ PACKAGE DIMENSION**

(Continued)

### **FUJITSU MICROELECTRONICS LIMITED**

Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0722, Japan Tel: +81-3-5322-3347 Fax: +81-3-5322-3387 http://jp.fujitsu.com/fml/en/

For further information please contact:

#### **North and South America**

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

#### Europe

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122

Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 206 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu,Seoul 135-280 Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

http://www.fmk.fujitsu.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD.

151 Lorong Chuan, #05-08 New Tech Park,

Singapore 556741

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm.3102, Bund Center, No.222 Yan An Road(E), Shanghai 200002, China Tel: +86-21-6335-1560 Fax: +86-21-6335-1605 http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD.

10/F., World Commerce Centre, 11 Canton Road

Tsimshatsui, Kowloon

Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/tw

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.