# DEI1282, 1284 8CH BIT PROGRAMMABLE GND/OPN & 28V/OPN DISCRETE INTERFACE IC

## **FEATURES**

- Eight discrete inputs

- Individually configurable as either GND/OPEN or 28V/OPEN(GND) inputs.

- Input threshold and hysteresis per AirBus ABD0100H specification.

- GND/OPEN mode: 4.5V/10.5V threshold, 3V hysteresis

- 28V/OPEN mode: 6V/12V threshold, 3V hysteresis

- 1mA input current to prevent dry relay contacts.

- Internal isolation diodes

- Inputs protected from Lightning Induced Transients per DO160F, Section 22, Cat A3 and B3

- 1284 version supports higher lightning levels and input filtering via use of off-chip input resistors

- Withstands inadvertent application of 115VAC/400Hz power

- o Built-in Test (BIT) to test internal circuits including input comparator

- Serial I/O interface to read data register and write configuration register

- o Direct interface to Serial Peripheral Interface (SPI) port.

- TTL/CMOS compatible inputs and Tristate output

- 8.6MHz Max Data Rate

- Serial input to expand Shift Register

- Logic Supply Voltage (VCC): 3.3V +/-5%

Analog Supply Voltage (VDD): 12V to 16.5V

- 16L SOIC EP package

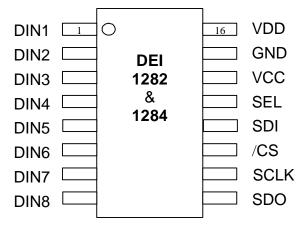

#### PIN ASSIGNMENTS

Figure 1 DEI1282, 1284 Pin Assignment (16 Lead SOIC)

#### FUNCTIONAL DESCRIPTION

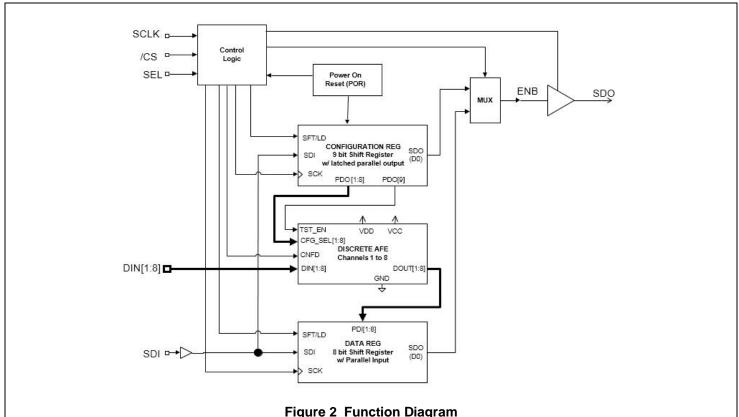

DEI1282 and DEI1284 are eight-channel discrete-to-digital interface ICs implemented in a High Voltage Dielectric Isolated technology. They sense eight discrete signals of the type commonly found in avionic systems and convert them to serial logic data. Each input can be individually configured as either GND/OPEN or 28V/OPEN format input via a serial data input. The discrete data is read from the device via an eight-bit serial shift register with 3-state output. This serial interface is compatible with the industry standard Serial Peripheral Interface (SPI) bus.

The discrete inputs are implemented with a high voltage technology to provide immunity to lightning induced transients. The DEI1282 tolerates DO160F Level 3 (600V) stress directly to the input pins without the need for additional protection components.

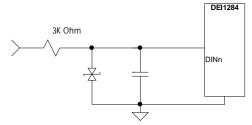

The DEI1284 version operates with 3K Ohm off-chip series resistors on the inputs. These are used in combination with Transient Voltage Suppressor (TVS) devices to achieve Level 4 (1500V) and Level 5 (3200V) immunity. The resistors act to limit surge current, thus allowing small TVS devices. The resistors are also used to implement low pass filtering by adding capacitors on the inputs. The filtering provides noise rejection and anti-aliasing of the sampled signal.

The on-chip Built-in Test (BIT) feature provides a Test Mode which provides a means to inject a test signal into each input comparator without interfering with the discrete input signals. The test coverage includes each DIN comparator as well as the digital logic and IO.

## **Table 1 Pin Descriptions**

| PINS | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-8  | DIN[1:8] | Discrete Inputs. Eight discrete signals which can be individually configured as either GND/OPEN or 28V/OPEN format inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9    | SDO      | Logic Output. Serial Data Output. This pin is the output from MSB (Bit 8) of the selected shift register (Data/Configuration). It is clocked by the rising edge of SCLK. This is a 3-state output enabled by /CS.                                                                                                                                                                                                                                                                                                                                                     |

| 10   | SCLK     | Logic Input. Serial Shift Clock. A low-to-high transition on this input shifts data on the serial data input into Bit 0 of the selected shift register. The selected shift register is shifted from Bit 1 to Bit 8. Bit 8 of the selected shift register is driven on SDO.                                                                                                                                                                                                                                                                                            |

| 11   | /CS      | Logic Input. Chip Select. A low level on this input enables the SDO 3-state output and the selected shift register. A high level on this input forces SDO to the high impedance state and disables the shift registers so SCLK transitions have no effect. When the Data Register is selected, a high-to-low transition causes the Discrete Input data to be loaded into the Data Register. When the Configuration Register is selected, a low-to-high transition causes the Serial Configuration Register data to be loaded into the parallel configuration outputs. |

| 12   | SDI      | Logic Input. Serial Data Input. Data on this input is shifted into the LSB (Bit 1) of the selected shift register on the rising edge of the SCLK when /CS input is low.                                                                                                                                                                                                                                                                                                                                                                                               |

| 13   | SEL      | Logic Input. Selects between the Data Register and Configuration Register. H = DATA, L = CONF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14   | VCC      | Logic Supply Voltage. 3.3V+/-5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15   | GND      | Logic/Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16   | VDD      | Analog Supply Voltage. 12V to 16.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 2 Function Diagram

#### Table 2 Truth Table

|     | Serial Interface Operation |          |       |          |        |                                                  |  |

|-----|----------------------------|----------|-------|----------|--------|--------------------------------------------------|--|

| SEL | /CS                        | SCLK     | SDI   | DIN[1:8] | SDO    | Description                                      |  |

| Χ   | Ι                          | Χ        | Χ     | X        | HI Z   | Not Selected                                     |  |

| Ι   | $\rightarrow$              | لــ      | Χ     | Valid    | DIN[8] | DR[1:8]← DIN[1:8]                                |  |

| Η   | L                          | <b>↑</b> | DR[1] | Χ        | DR[8]  | $DR[n+1] \leftarrow DR[n], DR[1] \leftarrow SDI$ |  |

| L   | L                          | 1        | CR[1] | Х        | CR[8]  | $CR[n+1] \leftarrow CR[n], CR[1] \leftarrow SDI$ |  |

| Ĺ   | 1                          | L        | Χ     | Χ        | HI Z   | CL[1:8]← CR[1:8]                                 |  |

#### Legend:

DR = Data Register

CR = Configuration Register

CL = Configuration Latch

X = Don't Care

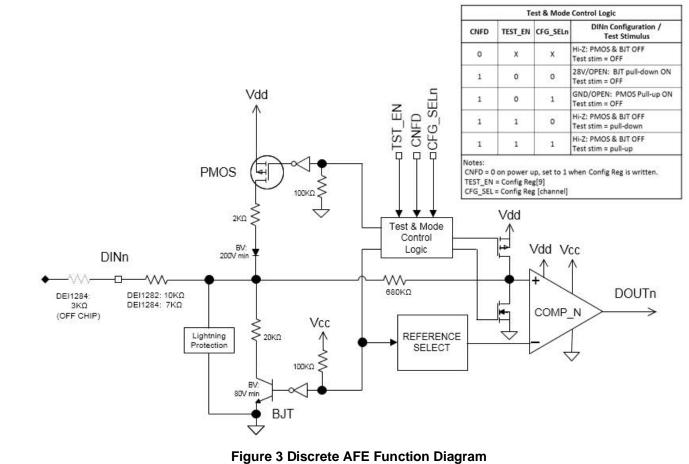

## DIN [1:8] Discrete AFE

The Discrete Input Analog Front End circuit function is represented in Figure 3. Each DINn signal is conditioned by the resistor / diode network and presented to a comparator with hysteresis. When the input is configured for GND/OPEN operation, the pull-up resistor and diode are enabled and comparator threshold voltage is selected. When the input is configured for 28V/OPEN operation, the pull-down resistor is enabled and the comparator is appropriately configured. Prior to configuration (after power up) and during BIT, neither pull-up nor pull-down is enabled and the AFE presents a high impedance (Hi-Z).

#### Some notable features are:

- Input voltage levels and hysteresis:

- o 28V/OPEN

High level input voltage: 12.0 to 49 V Low level input voltage: -4 to 6.0 V Hysteresis: > 3 V

GND/OPEN

High level input voltage: 10.5 to 49 V Low level input voltage: -4 to 4.5 V Hysteresis: > 3 V

- The input current is ~ 1mA. This current will prevent a "dry" relay contact.

- Input noise immunity is maximized with a combination of voltage hysteresis and use of a slow input voltage comparator.

- The inputs can withstand continuous input voltages of 49V, lightning transient voltages per DO160 Level 3 pin injection tests, and survive inadvertent application of 115VAC/400Hz.

# **Data Register**

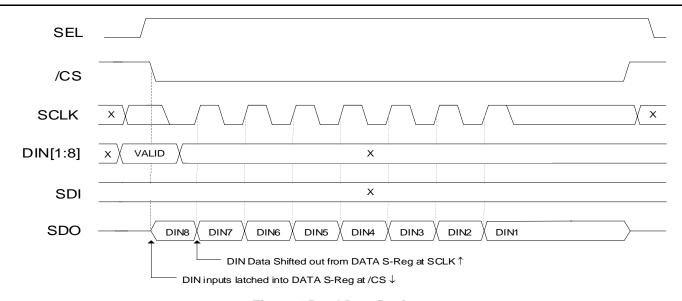

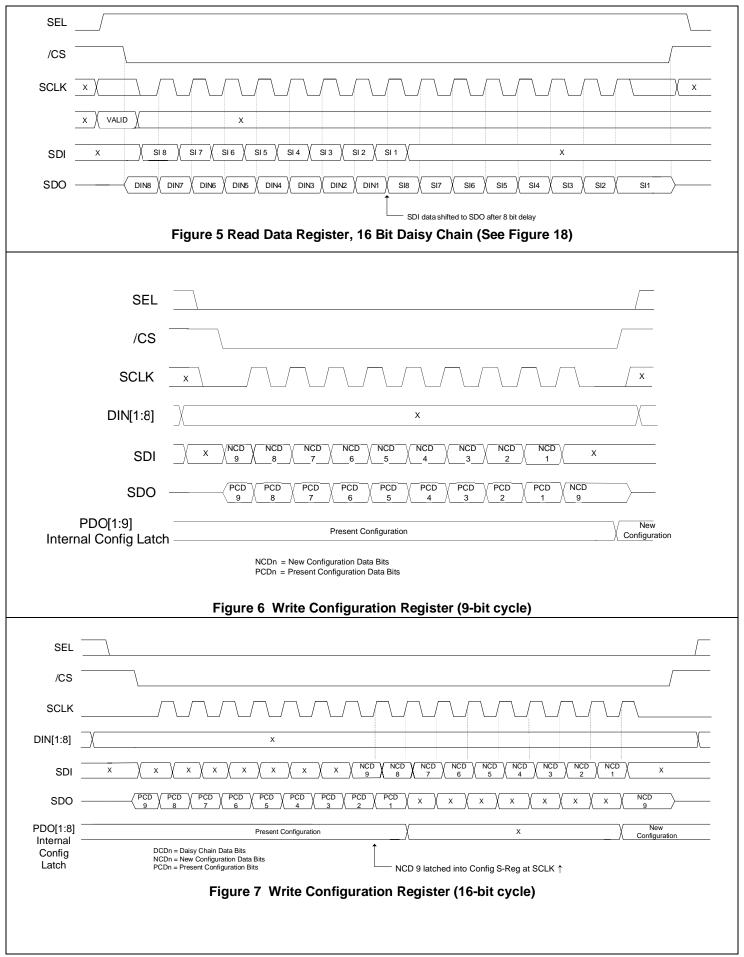

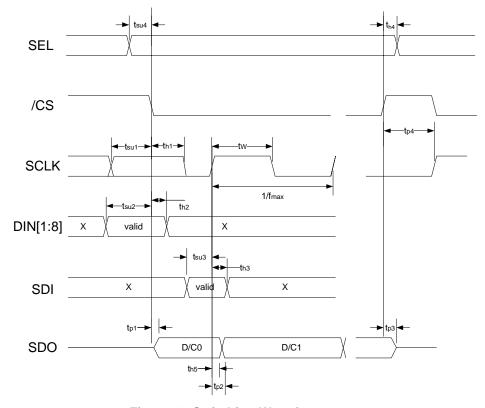

The 8-bit Data Register is a "parallel-input, serial-output" register that samples the input channels and reads-out the data to the Serial Data Output. The register is read via the SDO output as described in Figure 4 and Figure 5. A low DIN input level results in a Logic 0, and a high input level results in a Logic 1.

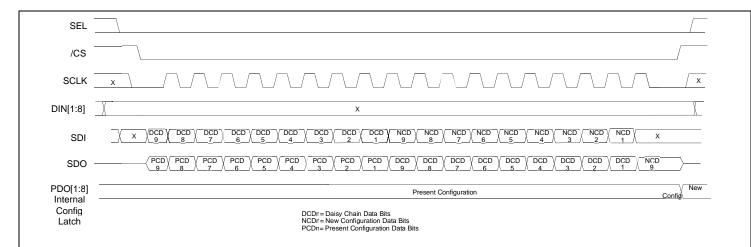

## Configuration Register

The 9-bit Configuration Register (CR) is a "serial-input, parallel-output with data latch" register that individually configures each AFE input as either GND/OPEN or 28V/OPEN format. (CR[n]: 0 sets DIN[n] to 28V/OPEN mode (pull-down); CR[n]: 1 sets DIN[n] to GND/OPEN mode (pull-up). The register is reset to 0's at Power Up and the AFE inputs are forced into high impedance mode until the CR is programmed (see Power Up Initialization). Bit 9 is used to enable or disable Built-in Test (see BIT Operation). The register is programmed via the serial data input as described in Figures 6–8.

## Serial Interface

The DEI1282/1284 incorporates a serial IO interface for programming the Discrete Input configuration and for reading the Discrete Input status. Refer to Figure 2. The interface is SPI Mode 0 compatible and consists of /CS, SEL, SCLK, SDO, and SDI signals. Figures 4 – 5 depict the Data Read sequence and Configuration Write sequence for both a single device and dual "daisy chained" devices; refer to Figure 16 for connection details.

# Power Up Initialization

The DEI1282/1284 incorporates an on-chip power-up reset (POR) circuit and logic to force the DIN inputs to a high impedance state at power up; the AFE pull-up and pull-down circuits are disabled. POR monitors the Vcc logic supply and forces the AFE to the high impedance state while Vcc is stabilizing. It remains high impedance until the Configuration Register is programmed by the first Write Configuration Register cycle when the pull-up or pull-down state is defined.

The POR rising Vcc threshold is ~2.5V with ~0.4V of hysteresis. The POR includes a ~200µs delay from the Vcc threshold to reset output; the Configuration Register ignores attempts to program it during this POR delay time.

The POR will reset when there is sufficient voltage sag on Vcc. When Vcc drops below ~2.0V for ~9µs, POR will activate, the Configuration and Data Registers will reset to "0", and the AFEs (DIN's) are set to Hi-Z.

The part may be intentionally operated in the non-configured Hi-Z mode in order to read the inputs without presenting a pull-up or pull-down load. Hi-Z mode is only accessible after POR and before the device configuration register is programmed. In Hi-Z mode, the input thresholds are approximately:

$VT_{\rm LH}$  = low to high threshold = ~14V  $VT_{\rm HL}$  = high to low threshold = ~11V

# **BIT Operation**

Bit 9 of the Configuration Register (CR) is used to enable or disable Built-in Test (1 = BIT enabled, 0 = NORMAL). When BIT is enabled, each channel configuration bit value is used to drive a test stimulus on the respective channel comparator (see Figure 3). Thus all channels can be tested by setting the BIT mode, programming test stimulus patterns into the CR, and reading the results from the DR. The DIN inputs are placed in Hi-Impedance mode (pull up and pull down switches are OFF) during test mode, so the test does not interfere with the DIN signals. The BIT test stimulus is isolated from the DIN pin by  $680 \text{K}\Omega$ .

If a DINn input voltage is stuck within the input hysteresis voltage range during the time when the CR is programmed from BIT to NORMAL mode and the DINn value read via a Read DR cycle, then the corresponding DINn bit will be reported as the last BIT test value programmed in the CR BIT command.

Figure 4 Read Data Register

Figure 8 Write Configuration Register, 18 bit Daisy Chain (See Figure 18)

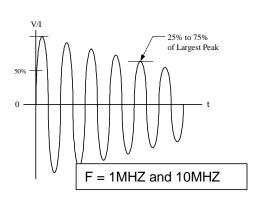

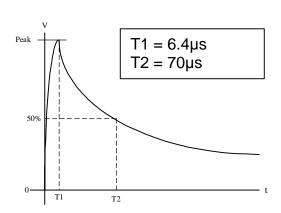

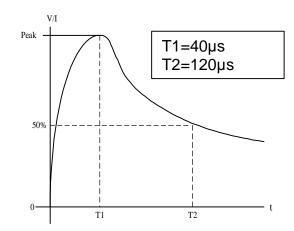

#### LIGHTNING TRANSIENT IMMUNITY

The DIN inputs are designed to survive lightning induced transients as defined by RTCA DO160F, Section 22, Cat A3 and B3, Waveforms 3, 4 and 5A, Level 3. The DEI1282 withstands this stress applied directly to the DIN pins. Contact factory for lightning test report.

The DEI1284 withstands Level 3 stress applied to the 3K Ohm series resistor in series with DINn pins. Insert a Transient Voltage Suppressor (48V bidirectional TVS) to ground on the DIN pin to implement higher immunity levels (i.e. Level 4 (1500V) or Level 5 (3200V)), see Figure 12. The 3K Ohm resistor limits surge current, thus allowing use of small TVS devices.

Figure 9 Voltage / Current Waveform 3

Figure 10 Voltage Waveform 4

Waveform Source Impedance characteristics:

- Waveform 3 Voc/Isc = 600V / 24A => 25 Ω

- Waveform 4 Voc/Isc = 300 V / 60 A => 5  $\Omega$

- Waveform 5A Voc / Isc =  $300V / 300A \Rightarrow 1 \Omega$

- Waveform 5A Voc / Isc =  $500V / 500A \Rightarrow 1 \Omega$

Figure 11 Voltage / Current Waveform 5A

## **INADVERTENT SHORT TO 115VAC POWER**

The DIN inputs can withstand inadvertent shorts to 115VAC/400Hz aircraft power. Contact factory for test report.

## **ELECTRICAL DESCRIPTION**

# **Table 3 Absolute Maximum Ratings**

| PARAMETER                               |     | MIN  | MAX       | UNITS |

|-----------------------------------------|-----|------|-----------|-------|

| VCC Supply Voltage                      |     | -0.3 | +5.0      | V     |

| VDD Supply Voltage                      |     | -0.3 | 18        | V     |

| Operating Temperature                   |     |      |           |       |

| Exposed pad soldered to heat sink       |     | -55  | +125      | °C    |

| Storage Temperature                     |     |      |           |       |

| Plastic Package                         |     | -55  | +150      | °C    |

| Input Voltage                           |     |      |           |       |

| DIN[1:8] Continuous                     | (3) | -10  | +49       | Vdc   |

| DO160F, Waveform 3, Level 3             | (3) | -600 | +600      | Vpk   |

| DO160F, Waveform 4 and 5, Level 3       | (3) | -300 | +300      | Vpk   |

| DO160F, Abnormal Surge Voltage, 100ms   | (3) |      | 80        | Vpk   |

| Logic Inputs                            |     | -1.5 | VCC + 1.5 | V     |

| DOUT                                    |     | -0.5 | VCC + 0.5 | V     |

| Power Dissipation @ 125°C, Steady state |     |      |           |       |

| 16L SOIC                                |     |      | 0.63      | W     |

| Junction Temperature:                   |     |      |           |       |

| Tjmax, Plastic Packages                 |     | 150  | °C        |       |

| ESD per JS-001-2017 Human Body Model 1B |     |      |           |       |

| Peak Body Temperature (10 sec duration) |     |      | 260       | °C    |

| N                                       |     |      |           |       |

- 1. Stresses above absolute maximum ratings may cause permanent damage to the device.

- 2. Voltages referenced to Ground.

- 3. Stress applied to external 3K Ohm series resistor in series with DINn pin. Applies to DEI1284 only.

**Table 4 Recommended Operating Conditions**

| PARAMETER                     | SYMBOL     | CONDITIONS              |

|-------------------------------|------------|-------------------------|

| Supply Voltage                | VCC<br>VDD | 3.3V±5%<br>12V to 16.5V |

| Logic Inputs and Outputs      |            | 0 to VCC                |

| Discrete Inputs               | DIN[1:8]   | 0 to 49V                |

| Operating Temperature Plastic | Та         | -55°C to 125°C          |

#### **Table 5 DC Electrical Characteristics**

| SYMBOL              | PARAMETER                                  | CONDITIONS (1)                                                                    | MIN<br>LIMIT | NOM         | MAX<br>LIMIT | UNIT     |

|---------------------|--------------------------------------------|-----------------------------------------------------------------------------------|--------------|-------------|--------------|----------|

|                     |                                            | Logic Inputs/Outputs                                                              |              |             |              | •        |

| $V_{\mathrm{IH}}$   | HI level input voltage                     | VCC = 3.3V                                                                        | 2.0          |             |              | V        |

| V <sub>IL</sub>     | LO level input voltage                     | VCC = 3.3V                                                                        |              | 1           | 0.8          | V        |

| $V_{\mathrm{Ihst}}$ | Input hysteresis<br>voltage,<br>SCLK input | (3)                                                                               | 50           |             |              | mV       |

| $V_{\mathrm{OH}}$   | HI level output voltage                    | IOUT = -20μA                                                                      | VCC -<br>0.1 |             |              | V        |

|                     |                                            | IOUT = -4mA, VCC = 3V                                                             | 2.4          |             |              | V        |

| $V_{\mathrm{OL}}$   | LO level output voltage                    | IOUT = 20µA                                                                       |              |             | 0.1          | V        |

| V OL                | Lo level odipat voltage                    | IOUT = 4mA, VCC = 3V                                                              |              |             | 0.4          | V        |

| $I_{ m IN}$         | Input leakage, except SEL                  | VIN = VCC<br>or GND                                                               | -10          |             | 10           | μA       |

| $I_{\text{IN-SEL}}$ | Input leakage, SEL                         | VIN = VCC<br>VIN = GND                                                            | -10<br>-50   |             | 10<br>10     | μA       |

| l <sub>oz</sub>     | 3-state leakage current                    | Output in Hi Impedance state. VOUT = VIHmin, VILmax                               | -10          |             | 10           | μA       |

|                     | Discrete Input                             | s, Configured as Ground/Open                                                      | (internal p  | ull-up) (4) |              |          |

| $V_{\mathrm{IH}}$   | HI level input voltage                     |                                                                                   | 10.5         | 1           | 49           | V        |

| R <sub>IH</sub>     | HI level DIN-to-GND resistance             | Resistor from DIN to GND to guarantee HI input condition.                         | 100          |             |              | kΩ       |

| I <sub>IH</sub>     | HI level input current                     | VIN = 28V, VDD = 15V<br>VIN = 49V, VDD = 15V                                      |              | 17<br>45    | 100<br>250   | μA<br>μA |

| V <sub>IL</sub>     | LO level input voltage                     |                                                                                   | -4.0         | 1.0         | 4.5          | V        |

| R <sub>IL</sub>     | LO level DIN-to-GND resistance             | Resistor from DIN to GND to guarantee LO input condition.                         |              |             | 500          | Ω        |

| $I_{\mathrm{IL}}$   | LO level input current                     | VIN = 0V, VDD = 15V                                                               | -0.8         | -1.0        | -1.8         | mA       |

| $V_{Ihst}$          | Input hysteresis voltage                   |                                                                                   | 3            |             |              | V        |

| mst                 | , ,                                        | s, Configured as 28V/Open (in                                                     | ternal pull- | down) (4)   | 1            |          |

| $V_{\mathrm{IH}}$   | HI level input voltage                     |                                                                                   | 12.0         |             | 49           | V        |

| I <sub>IH</sub>     | HI level input current                     | VIN = 28V, VDD = 15V                                                              | 0.6          | 0.8         | 1.35         | mA       |

| V <sub>IL</sub>     | LO level input voltage                     | 7.11. 201, 122 101                                                                | -4           | 0.0         | 6.0          | V        |

| I <sub>IL</sub>     | LO level input current                     | VIN = 1V, VDD = 15V                                                               |              | †           | 50           | μA       |

| V <sub>Ihst</sub>   | Input hysteresis voltage                   | VIII - 1 V, VBB - 10 V                                                            | 3            | †           | - 00         | V        |

| ▼ IIISt             | i inpat nyotorodio voltago                 | Power Supply                                                                      |              | 1           | 1            | , v      |

| ICC                 | Max quiescent logic supply current         | VIN(logic) = VCC or GND<br>VIN[1:8] = open                                        |              | 1.8         | 3            | mA       |

| IDD                 | Max quiescent analog supply current        | VIN(logic) = VCC or GND<br>Ground/Open Mode,<br>VIN[1:8] = Open<br>VIN[1:8] = GND |              | 15<br>22    | 24<br>33     | mA       |

- 1. Unless otherwise noted: Ta = -55°C to 85/125°C (-SES/-SMS). VDD = 12V to 16.5V. VCC = 3.3V+/5%.

- 2. Current flowing into device is '+'. Current flowing out of device is '-'. Voltages are referenced to Ground.

- 3. Guaranteed by design. Not production tested.

- 4. With 3K Ohm, 2% resistor in series with DIN input pin. Applies to DEI1284 only.

#### **Table 6 AC Electrical Characteristics**

| SYMBOL           | PARAMETER                                          | CONDITIONS (5,6,7) | MIN<br>LIMIT | MAX<br>LIMIT | UNIT |

|------------------|----------------------------------------------------|--------------------|--------------|--------------|------|

| f <sub>MAX</sub> | SCLK frequency.                                    | 50% duty cycle     | 0.1          | 8.6          | MHz  |

| tw               | SCLK pulse width.                                  |                    | 50           |              | ns   |

| t <sub>su1</sub> | Setup time, SCLK to /CS↓.                          |                    | 30           |              | ns   |

| t <sub>h1</sub>  | Hold time, /CS↓ to SCLK.                           |                    | 25           |              | ns   |

| t <sub>su2</sub> | Setup time, DIN valid to /CS↓.                     |                    | 15           |              | μs   |

| t <sub>h2</sub>  | Hold time, /CS↓ to DIN not valid.                  |                    | 500          |              | ns   |

| t <sub>su3</sub> | Setup time, SDIN valid to SCLK↑.                   |                    | 25           |              | ns   |

| t <sub>h3</sub>  | Hold time, SCLK↑ to SDIN not valid.                |                    | 25           |              | ns   |

| t <sub>su4</sub> | Setup time, SEL valid to /CS↓.                     |                    | 30           |              | ns   |

| t <sub>h4</sub>  | Hold time, SEL valid to /CS↑.                      |                    | 25           |              | ns   |

| $t_{p1}$         | Propagation delay, /CS↓ to DOUT valid.             | (1)                |              | 105          | ns   |

| t <sub>p2</sub>  | Propagation delay, SCLK↑ to DOUT valid.            | (1)                |              | 90           | ns   |

| t <sub>p3</sub>  | Propagation delay, /CS↑ to DOUT HI-Z.              | (1) (2) (3)        |              | 80           | ns   |

| t <sub>p4</sub>  | Delay time between /CS active.                     |                    | 20           |              | ns   |

| t <sub>h5</sub>  | Hold time, SCLK↑ to DOUT                           | (1)                | 10           |              | ns   |

| Cin              | Maximum logic input pin Capacitance.               |                    |              | 10           | pF   |

| Cout             | Maximum SDO pin capacitance, output in HI-Z state. |                    |              | 15           | pF   |

- 1. SDO loaded with 50pF to GND.

- 2. SDO loaded with 1K $\Omega$  to GND for Hi output, 1K $\Omega$  to VCC for Low output.

- 3. Timing measured at 25%VCC for "0" to Hi-Z, 75%VCC for "1" to Hi-Z.

- 4. Sample tested on lot basis.

- 5. Guaranteed by design. Not production tested.

- 6. Ta = -55°C to 85 or 125°C, VCC = 3V, VDD = 15V, VIL = 0V, VIH = VCC unless otherwise noted.

- 7. Measurements made at 50%VCC.

Figure 12 Switching Waveforms

#### APPLICATION INFORMATION

## **Discrete Input Filtering**

The DEI1282/84 Analog Front End provides a moderate level of noise immunity via a combination of hysteresis and limited bandwidth. The Hysteresis is 3V minimum and the comparator bandwidth is approximately 10MHz. A capacitor may be installed in parallel with a TVS on the DEI1284 DIN pin to provide additional noise filtering.

Figure 13 DEI1284 DIN with Filter Cap and TVS on DIN input.

Applications may require additional noise immunity by means of debounce/filtering in software or in digital circuitry (i.e.: FPGA). Common input debounce techniques are readily found with a web search of the term "software debounce" and range from simple detectors of two or more sequential stable readings to FIR filters emulating RC time constants.

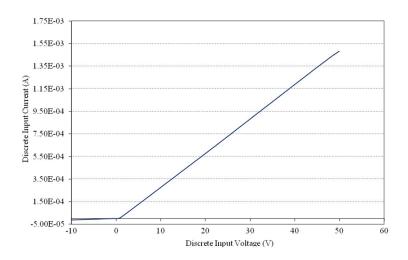

## **Input Current Characteristics**

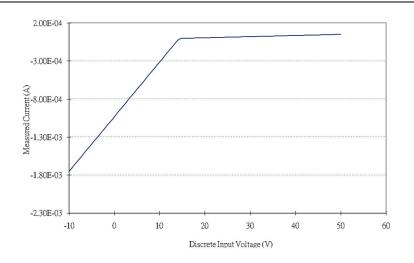

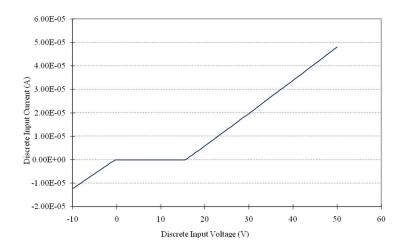

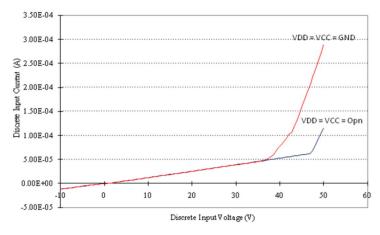

Figures 14-17 depicts the DIN Input Current vs. Voltage characteristics for the various operating and non-operating modes. Measurements are at Room temperature.

Figure 14 28V/Open Mode Input IV Characteristics (VDD = 15V)

Figure 15 GND/OPEN Mode Input IV Characteristics (VDD = 15V)

Figure 16 Hi-Z (Un-configured and BIT) Mode Input IV Characteristics (VDD = 15V)

Figure 17 VDD = VCC= GND and VDD = VCC = Open Input IV Characteristics

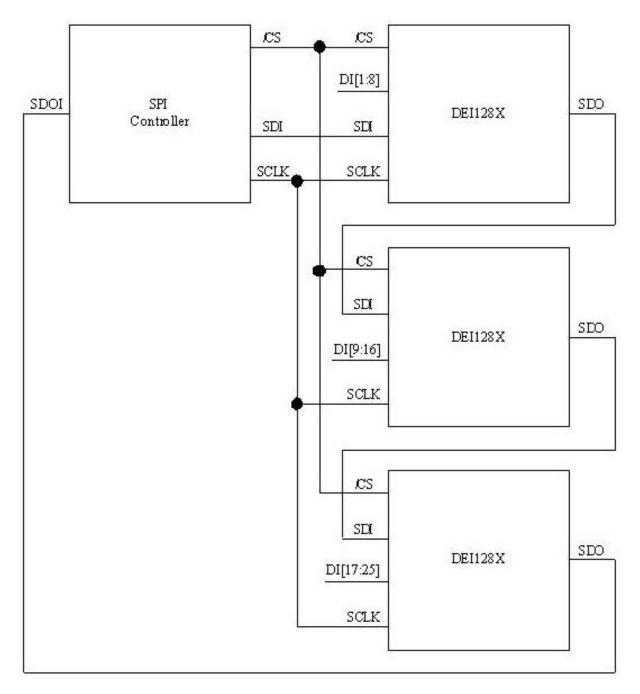

# **Daisy Chain Connection**

Multiple DEI1282/1284 ICs can be connected as daisy chain. Figure 16 shows three devices connected in SPI series mode. The critical timing is Tsu3 (see Fig 12), minimum SDIN valid to SCLK setup time.

Figure 18 Example connection of three DEI128X's connected as daisy chain

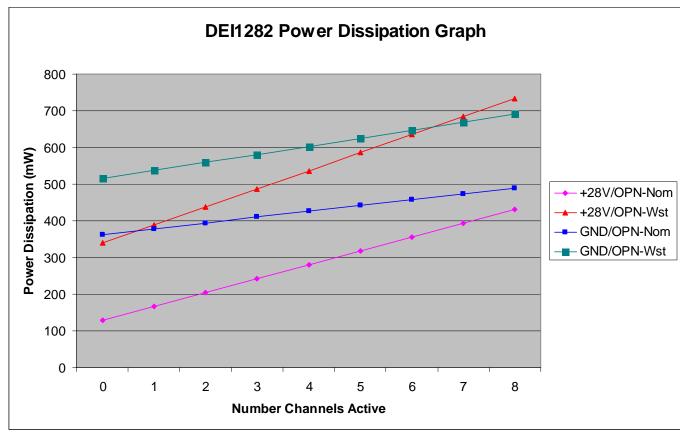

# **Package Power Dissipation**

The DEI1282/84 power dissipation varies with channel configuration and operating conditions. Figure 18 shows the device package power dissipation for various conditions. This includes the contributions from Supply currents and Input currents. The four curves are as follows:

**Table 7 Legend for Power Dissipation Curves**

| CURVE ID      | SUPPLY VOLTAGE, TEMPERATURE,<br>IC VARIATION      |

|---------------|---------------------------------------------------|

| +28V/OPEN-Nom | 3.3V, 12V / 27°C / typical IC parameters          |

| +28V/OPEN-Wst | 3.3V, 16.5V / 125°C /<br>Worst case IC parameters |

| GND/OPEN-Nom  | 3.3V, 12V / 27°C / typical IC parameters          |

| GND/OPEN-Wst  | 3.3V, 16.5V / 125°C /<br>Worst case IC parameters |

- 1. The active channels are forced to Ground for GND/OPEN type and forced to 28V for 28V/OPEN type.

- 2. The DEI1284 package power dissipation is lower than the DEI1282 because a portion of the power is shifted to the external resistors. The DEI1284 incremental Pd is ~20% lower for GND/OPEN and ~15% lower for 28V/OPEN.

Figure 19 Power Dissipation for Various Conditions

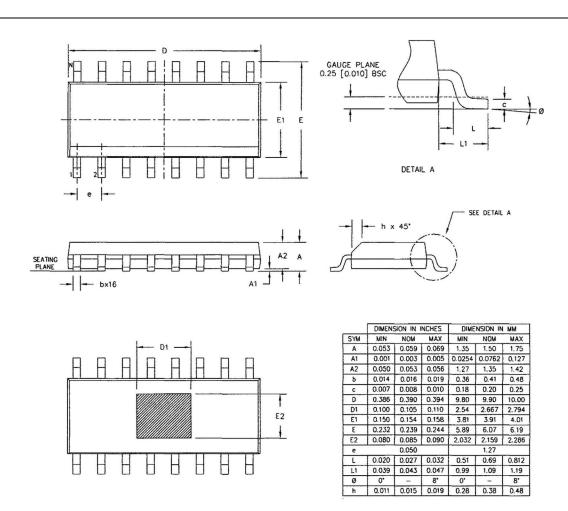

# PACKAGE DESCRIPTION - 16L Narrow Body, Exposed Pad SOIC

## **Table 8 Package Information**

| Package Type                 | Package<br>Ref   | Θjc/ Θja<br>(°C/W)<br>/1 | JEDEC<br>Moisture<br>Sensitivity<br>Level | Lead Finish /<br>JEDEC Pb-<br>Free Code | Pb Free<br>Designation | JEDEC<br>MO   |

|------------------------------|------------------|--------------------------|-------------------------------------------|-----------------------------------------|------------------------|---------------|

| 16L SOIC NB<br>SnPb          | 16 EP<br>SOICN   | ~10 / ~40                | MSL 1 /<br>260°C                          | 85/15 SnPb<br>plate<br>na               | Not Pb-free            | MS-<br>012-AC |

| 16L SOIC NB<br>Matte Sn RoHS | 16 EP<br>SOICN G | ~10 / ~40                | MSL 1 /<br>260°C                          | 100% Matte Sn<br>e3                     | RoHS                   | MS-<br>012-AC |

#### Notes:

Mounted on 4 layer PCB with exposed pad soldered to PCB land with thermal VIAs to internal GND plane

The PCB design and layout is a significant factor in determining thermal resistance (Oja) of the IC package. Use maximum trace width on all power and signal connections at the IC; these traces serve as heat spreaders which improve heat flow from the IC leads.

The exposed pad on the bottom of the SOIC package must be soldered to a heat-spreader land pattern on the PCB. The IC exposed pad is electrically isolated, but must be connected to some potential on the PCB, typically Ground or Vcc. Maximize the PCB land size by extending it beyond the IC outline if possible. A grid of thermal VIAs, which drop down and connect to the buried copper plane(s), should be placed under the heat-spreader land. A typical VIA grid is 12mil plated holes on a 50mil pitch. Use as many VIAs as space allows. VIAs should be plugged to prevent voids being formed between the exposed pad and PCB heat-spreader land due to solder escaping by the capillary effect. Wicking can be avoided by tenting the VIAs with solder mask.

Note: The bottom thermal contact (exposed pad) is electrically isolated.

Figure 20 16 Lead Narrow Body EP SOIC Outline

#### ORDERING INFORMATION

**Table 9 Ordering Information**

| Part Number   | Marking            | Package (1)  | Requires 3KΩ<br>Resistor on<br>DIN | Temperature   |

|---------------|--------------------|--------------|------------------------------------|---------------|

| DEI1282-SES   | DEI1282-SES        | 16 EP SOIC   | No                                 | -55°C / 85°C  |

| DEI1282-SMS   | DEI1282-SMS        | 16 EP SOIC   | No                                 | -55°C / 125°C |

| DEI1282-SES-G | DEI1282-SES-G / e3 | 16 EP SOIC G | No                                 | -55°C / 85°C  |

| DEI1282-SMS-G | DEI1282-SMS-G / e3 | 16 EP SOIC G | No                                 | -55°C / 125°C |

| DEI1284-SES-G | DEI1284-SES-G / e3 | 16 EP SOIC G | Yes                                | -55°C / 85°C  |

| DEI1284-SMS-G | DEI1284-SMS-G / e3 | 16 EP SOIC G | Yes                                | -55°C / 125°C |

| Notes:        |                    |              |                                    |               |

1. Refer to Table 8

DEI reserves the right to make changes to any products or specifications herein. DEI makes no warranty, representation, or guarantee regarding suitability of its products for any particular purpose.