# TERSTENION OF THE COLUMN OF TH

MB 4053 MB 4063

> May 1986 Edition 3.0

#### 6-CHANNEL 8-BIT A/D CONVERTER SUBSYSTEM

The Fujitsu MB 4053 and MB 4063 are 6-channel, 8-bit, single-slope A/D converter subsystem designed to be used in a microprocessor based data control system. These devices provide the analog functions while the addressing, counting and timing functions are provided by a microprocessor such as the MB 8840/50, MBL 8048, MBL 8086, or MBL 8088.

The MB 4053 and MB 4063 are single monolithic bipolar IC providing a 1 of 8 address decoder, 8-channel analog multiplier, sample and hold, constant current generator, ramp integrator and comparator in a 16-pin package.

These A/D converter subsystems are suitable for a wide range of applications. The resolution required by an application can be obtained by arbitrarily selecting a suitable integration time. Also zero offset and full-scale error corrections can be made automatically (auto-zero and auto-calibration) to minimize conversion error.

- Microprocessor/TTL compatible

- · Zero offset and full-scale error correction capability

- · Ratiometric conversion capability

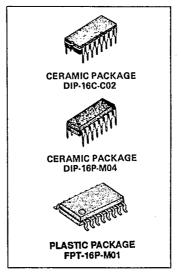

- Available in 16-pin DIP and Flat Pack

- Compatible with MC14443 and μA9708 (DIP package)

- Single power supply : +4.75 V to +15 V

Excellent linearity : ±0.2% max. error

- Fast conversion time : 300 μs/ch typ.

Analog input volgage : 0 V to V<sub>CC</sub> 2 V (5.25 V max.)

- Power Dissipation : 25 mW typ, at V<sub>CC</sub> = 5 V

- Standard 16-pin DIP or flat package,

#### ABSOLUTE MAXIMUM RATINGS

| Parameter              | Symbol          | Value            | Unit        |    |

|------------------------|-----------------|------------------|-------------|----|

| Supply Voltage         | Vcc             | 18               | ٧           |    |

| Digital Input Voltage  | V <sub>ID</sub> | -0.5 to +30      | ٧           |    |

| Digital Output Voltage | V <sub>OH</sub> | -0.5 to +18      | ٧           |    |

| Analog Input Voltage   | V <sub>tA</sub> | -0.5 to +30      | ٧           |    |

| Output Current         | l <sub>o</sub>  | 10               | mA          |    |

| Storage Temperature    | Ceramic         | _                | -55 to +150 | °C |

|                        | Plastic         | Т <sub>STG</sub> | -55 to +125 | °c |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

FUJITSU MB 4053

MB 4053 FUJITSU MB 4063

# RECOMMENDED OPERATING CONDITIONS

| Parameter Supply Voltage |         |                  |      | Condition | Condition        |      |

|--------------------------|---------|------------------|------|-----------|------------------|------|

|                          |         | Symbol Min,      |      | Тур.      | Max.             | Unit |

|                          |         | Vcc              | 4.75 | 5.0       | 15               | ٧    |

| Reference Voltage*       | MB 4053 | V <sub>REF</sub> | 2.0  |           | 5.25             | ٧    |

|                          | MB 4063 |                  | 2.8  |           |                  |      |

| Ramp Capacity            |         | Сн               | 300  |           |                  | pF   |

| Reference Current        |         | I <sub>R</sub>   | 12   |           | 50               | μА   |

| Analog Input Voltage     |         | VIA              | 0    |           | V <sub>REF</sub> | V    |

| Output Current           |         | I <sub>O</sub>   |      |           | 1.6              | mA   |

| Operating Temperature    |         | TA               | -40  |           | +85              | °c   |

NOTE:  $^{\circ}$ 2V  $\leq$  V  $_{\text{REF}}$   $\leq$  V  $_{\text{CC}}$  -2V for MB 4053, 2.8V  $\leq$  V  $_{\text{REF}}$   $\leq$  V  $_{\text{CC}}$  -2V for MB 4063

# **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 4.75 \text{ V to } 15 \text{ V}, T_{\Delta} = -40^{\circ} \text{C to } 85^{\circ} \text{C})$

| Parameter                          | Symbol           | Value |       | Unit | Remarks |                                                                                                             |  |

|------------------------------------|------------------|-------|-------|------|---------|-------------------------------------------------------------------------------------------------------------|--|

| Laramete.                          | Jymboi -         | Min.  | Тур.  | Max. |         | (,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                     |  |

| Conversion Error                   | EA               |       | ±0.2  | ±0.3 | %       | †1                                                                                                          |  |

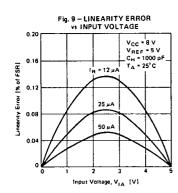

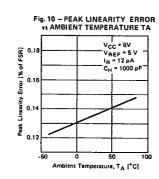

| Linearity Error                    | ER               |       | ±0.08 | ±0.2 | %       | †2                                                                                                          |  |

| Analog Input Current               | I <sub>B</sub>   |       | -50   | -250 | nA      |                                                                                                             |  |

| Crosstalk Between Any Two Channels | V <sub>CR</sub>  | 60    |       |      | dB      | †3                                                                                                          |  |

| Multiplexer Input Offset Voltage   | V <sub>OSM</sub> |       | 2.0   | 4.0  | mV      |                                                                                                             |  |

| Conversion Time                    | t <sub>C</sub>   |       | 296   | 350  | μs/ch   | See test circuit<br>Analog input: 0 thru V <sub>RE</sub><br>C <sub>H</sub> = 3300 pF, I <sub>R</sub> = 50 µ |  |

| Acquisition Time                   | t <sub>A</sub>   |       | 20    | 40   | μs      | See test circuit<br>C <sub>H</sub> = 1000 pF †4                                                             |  |

| Acquisition Current                | IA               | 150.  |       |      | μΑ      |                                                                                                             |  |

| Ramp Start Delay Time              | to               | Ī     | 100   |      | ns      |                                                                                                             |  |

| Multiplexer Address Time           | t <sub>M</sub>   |       | 1     |      | μs      |                                                                                                             |  |

| Digital High Level Input Voltage   | V <sub>IH</sub>  | 2.0   |       |      | V       |                                                                                                             |  |

| Digital Low Level Input Voltage    | VIL              |       |       | 0.8  | V       |                                                                                                             |  |

| Digital Low Level Input Current    | I <sub>I</sub> L |       | -5    | -15  | μΑ      | V <sub>IL</sub> = 0.4 V                                                                                     |  |

| Digital High Level Input Current   | I <sub>IH</sub>  |       |       | 1    | μΑ      | V <sub>IH</sub> = 5.5 V                                                                                     |  |

| High Level Output Current          | 1он              |       |       | 10   | μΑ      | V <sub>OH</sub> = 15 V                                                                                      |  |

| Low Level Output Voltage           | VoL              |       |       | 0.4  | V       | I <sub>OL</sub> = 1.6 mA                                                                                    |  |

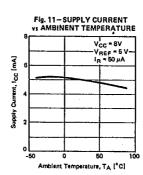

| Supply Current                     | Icc              |       | 5     | 10   | mA      |                                                                                                             |  |

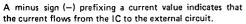

- †1 Conversion error: For all channels, deviation from a straight line between two points obtained by channel addresses 000 (0 scale) and 111 (full scale).

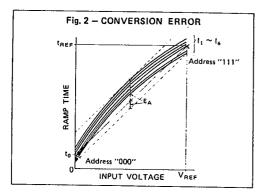

- †2 Linearity error: Deviation from a straight line between the 0 and full scale points for each channel.

- †3 Crosstalk between channels: Voltage change  $V_{\text{CH}}$  of

$C_H$  terminal occurring when an input voltage of a channel is changed by  $\Delta V_I$  while another channel is already charged (RAMP START = 0). This calculated by  $20\log \frac{\Delta V_{CH}}{\Delta V_1}$ .

†4 Acquisition time: Sum of multiplexer delay time, RAMP START delay time, and time required to charge the selected input voltage to the ramp capacitor.

T-57-07-07

FUJITSU MB 4053 MB 4063

CHANNEL SELECTION

| In             | put addres     | Selected |                  |

|----------------|----------------|----------|------------------|

| A <sub>2</sub> | A <sub>1</sub> | Ao       | analog input     |

| 0              | 0              | 0        | GND              |

| 0              | 0              | 1        | l <sub>1</sub>   |

| 0              | 1              | 0        | l <sub>2</sub>   |

| 0              | 1              | 1        | 13               |

| 1              | 0              | 0        | 14               |

| 1              | 0              | 1        | l <sub>s</sub>   |

| 1              | 1              | 0        | 16               |

| 1              | 1              | 1        | V <sub>REF</sub> |

Adjust R\_REF in the range 40 to 200 k $\Omega$  so that I R is 12 to 50  $\mu A.$

MB 4053 FUJITSU

MB 4063

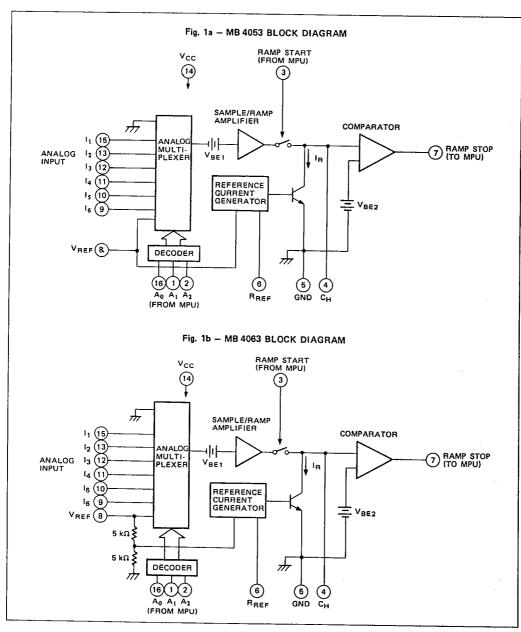

#### **OPERATION DISCRIPTION**

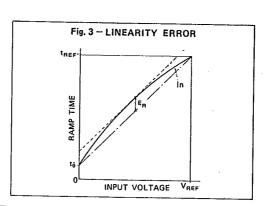

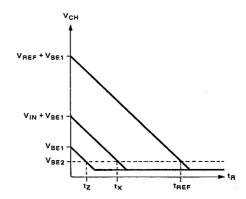

Refer to Fig. 1 MB 4053/MB 4063 BLOCK DIAGRAM, and Fig. 5 Timing Chart. Address inputs A<sub>0</sub> to A<sub>2</sub> are used to select the analog input to be converted, (one of the six analog inputs  $I_1$  to  $I_6$ ). The RAMP START input is switched from a logic 1 to a logic zero. This causes the external ramp capacitor C<sub>H</sub> to charge at a fixed rate. (Note 1) until it reaches the sum of the selected analog input voltage and a constant offset voltage  $V_{\mbox{\footnotesize{BE1}}}.$  The RAMP STOP output (open-collector switches from a logic 0 to logic 1 when the voltage on CH reaches the comparator reference voltage V<sub>RE2</sub>. The RAMP START input is switched back to a logic 1 after CH is completely charged. This disconnects the analog input from  $C_H$  and allows it to be gin discharging at a fixed rate (Note 2). When the voltage on  $C_H$  reaches the comparator reference voltage  $V_{BE2}$  the RAMP STOP output switches back to a logic 0. This completes a conversion cycle for 1 channel.

The time between the RAMP START input switching (0→1) and RAMP STOP output switching (1→0) is the RAMP TIME  $\boldsymbol{t}_{\text{R}}.$  This would be directly proportional to the analog input voltage for the ideal situation where there was no comparator switching level error, leakage, switching delay times or effect of the impedance of the internal reference current source,  $t_{\mbox{\scriptsize R}}$  can be calculated for the ideal case as follows:

$$t_R = V_{IN} \times \frac{C_H}{I_R}$$

Where: V<sub>IN</sub> = Analog input voltage to be measured CH = External ramp capacitor

$$I_{\rm P} = \frac{V_{\rm CC} - V_{\rm REF}}{R_{\rm REF}} \text{ for MB 4053}$$

$$I_{R} = \frac{V_{REF}}{2 - R_{REF}} \text{ for MB 4063}$$

This ramp time is converted to a digital representation by counting t<sub>R</sub> with the microprocessor. If a small error can be tolerated, the A/D conversion software can be reduced and the conversion time minimized by omitting corrections.

#### NOTE:

\*1 Charge slope =

$$\frac{I_A - I_R}{C_H} \ge \frac{150\mu A - I_R}{C_H}$$

Where: IA is the acquisition current whose value is determined from the circuit constant in the IC.

\*2 Discharge slope =

$$-\frac{I_R}{C_H}$$

### ZERO OFFSET AND FULL-SCALE FACTOR CORRECTIONS

High precision conversions can be achieved by correcting for zero offset and full scale factor as follows:

The channel select address ( $A_0$  to  $A_2$ ) is set to 000. Ground (GND) is selected (internally) as the analog input and converted. This results in ramp time t<sub>R</sub>. Next the address is set to 111. VREF is selected (internally) and converted, This results in ramp time, tage. Finally the desired analog input (one of 1, to 16) is selected and converted. This results in ramp time  $t_{\rm X}.$  This conversion sequence is arbitrary and the GND and  $V_{\rm REF}$  conversions are not needed each time a channel is converted but only as required for calibration. The relationships between the inputs and ramp times are shown below.

$$(V_{BE1})_c = t_Z$$

$(V_{REF} + V_{BE1})_c = t_{REF}$

$(V_{IN} + V_{BE1})_c = t_X$

$(V_{REF})_c = t_{REF} - t_Z$

$(V_{IN})_c = t_X - t_Z$

$(V_{IN})_c = t_X - t_Z$

$(V_{REF})_c = t_{REF} - t_Z$

The conversion error can then be minimized by using the above results in the expression below to calculate the corrected analog input voltage.

$$(V_{IN})_C = (V_{REF})_C \times \frac{t_X - t_Z}{t_{REF} - t_Z}$$

Where:  $V_{IN}$  = Analog input voltage to be measured

V<sub>REF</sub> = Reference voltage

V<sub>BE1</sub> = Shift voltage in sample/ramp amplifier

V<sub>BE2</sub> = Threshold voltage of comparator

V<sub>CH</sub> = C<sub>H</sub> voltage

The GND and VREF conversion sequence is arbitrary, the GND and  $V_{\text{REF}}$  conversions not being needed each time a channel (I<sub>1</sub> to I<sub>6</sub>) is converted.

FUJITSU MB 4053 MB 4063

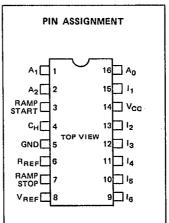

# PIN DESCRIPTION

|            |              |                                                 |                                                    | ** · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------|--------------|-------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin number |              | Name                                            | Symbol                                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|            | 9 ~ 13<br>15 | Analog input I <sub>1</sub> thru I <sub>6</sub> |                                                    | Analog inputs for the six channels. One of the 6 is selected by a specific bit pattern on $A_0$ to $A_2$ .                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|            | 16<br>1<br>2 | Channel selection input                         | A <sub>0</sub><br>A <sub>1</sub><br>A <sub>2</sub> | Inputs for selecting an analog input channel. Either GND, one of channels $\mathbf{I}_1$ to $\mathbf{I}_6$ or $\mathbf{V}_{REF}$ is selected by a specific bit pattern on the 3 inputs.                                                                                                                                                                                                                                                        |  |  |  |

|            | 3            | RAMP START signal input                         | RAMP START                                         | A/D conversion start signal input. RAMP START (1 $\rightarrow$ 0) Ramp time start signal input. RAMP START (0 $\rightarrow$ 1)                                                                                                                                                                                                                                                                                                                 |  |  |  |

|            | 7            | RAMP STOP signal output                         | RAMP STOP                                          | Indicates that $C_H$ is charged over comparator reference voltage $V_{BE2}$ . RAMP STOP (0 $\rightarrow$ 1) A/D conversion end signal ( $C_H$ discharged to comparator reference voltage). RAMP STOP (0 $\rightarrow$ 1)                                                                                                                                                                                                                       |  |  |  |

|            | 4            | Ramp capacitor<br>pin                           | Сн                                                 | Pin for externally connecting the ramp capacitor. The value of $C_{\rm H}$ in conjunction with $V_{\rm REF}$ and $R_{\rm REF}$ establishes the ramp time.                                                                                                                                                                                                                                                                                      |  |  |  |

|            | 8            | Reference voltage<br>supply pin                 | V <sub>REF</sub>                                   | Reference voltage supply pin.  This is the reference voltage source for determining the discharge current and the analog reference voltage for full-scale factor correction.  When the channel selection input is set to 111, this pin is selected for channel conversion. The full-scale factor is corrected using the conversion results.  The voltage at this pin must be set to (GND + 2 V) to (V <sub>CC</sub> - 2 V) and 5.25 V or less. |  |  |  |

|            | 6            | Reference<br>resistance pin                     | R <sub>REF</sub>                                   | Pin for external reference resistance for setting the discharge current. MB 4053: The external resistance is connected between the power source pin $(V_{CC})$ and the reference resistance pin $\{R_{REF}\}$ . The discharge current is, then, $I_R = (V_{CC} - V_{REF})/R_{REF}$ .                                                                                                                                                           |  |  |  |

|            |              |                                                 |                                                    | (V <sub>CC</sub> ) and the reference resistance pin (R <sub>REF</sub> ). The discharge current is, then, I <sub>R</sub> = (V <sub>CC</sub> - V <sub>REF</sub> )/R <sub>REF</sub> .  MB 4053: The external resistance is connected between the reference voltage                                                                                                                                                                                |  |  |  |

|            |              |                                                 |                                                    | supply pin ( $V_{REF}$ ) and the reference resistance pin ( $R_{REF}$ ). The discharge current is, then $I_R \approx V_{REF}/2R_{REF}$ .                                                                                                                                                                                                                                                                                                       |  |  |  |

|            | 14           | Power supply                                    | V <sub>cc</sub>                                    | Power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|            | 5            | Ground                                          | GND                                                | Ground pin This pin is grounded. When the channel selection input is set to 000, this terminal is selected for channel conversion. The zero offset is corrected using the conversion results.                                                                                                                                                                                                                                                  |  |  |  |

MB 4053 FUJITSU

MB 4063

# **NOTES ON USE**

- 1. Since the impedance of th ramp capacitor pin is approximately 30  $M\Omega$  (high), a resistance must not be connected in paralleled with this input. A ramp capacitor with no leakage must be used.

- 2. At VIN = 0 V, tn has a finite value.

- 3. Since RAMP STOP is an open collector output, an external pull-up resistor is required. (For example, when a 20 K $\Omega$  external pull-up resistor is used.)

- 4. All digital inputs/output are TTL compatible.

- 5. The time from RAMP START input switching  $(0 \rightarrow 1)$ to RAMP STOP output switching (1  $\rightarrow$  0) is ramp time

6.

$$t_{SL} \ge t_A \text{ (max)} = \frac{C_H}{150 \, \mu A - I_B} x \text{ (V}_{REF} + 0.7 \text{ V)}$$

- 7.  $t_R = \frac{C_H}{I_R} \times V_{IN}$ ,  $t_R$  (max)  $= \frac{C_H}{I_R} \times V_{REF}$

- $\frac{V_{CC} V_{REF}}{R_{REF}} \text{ for MB 4053, } I_{R} = \frac{v_{REF}}{2 R_{REF}}$ for MB'4063

- 9.  $2 \text{ V} \leq \text{V}_{\text{REF}} \leq (\text{V}_{\text{CC}} 2 \text{ V})$  and  $\text{V}_{\text{REF}} \leq 5.25 \text{ V}$ for MB 4053  $2.8 \text{V} \leqq \text{V}_{\text{REF}} \leqq (\text{V}_{\text{CC}} - 2 \text{ V})$  and  $\text{V}_{\text{REF}} \leqq 5.25 \text{ V}$ for MB 4063

- 10. While and analog input voltage is being sampled, channel, selection signals  $A_0$ ,  $A_1$ , and  $A_2$  must not be changed for (t<sub>SL</sub>).

# TYPICAL CHARACTERISTIC CURVES

# **APPLICATION EXAMPLES**

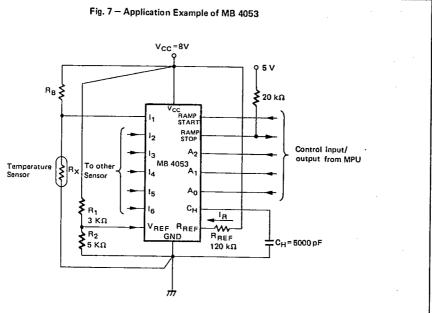

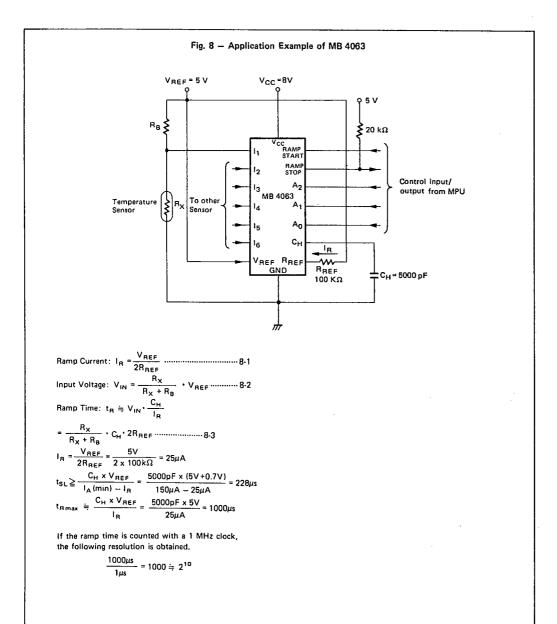

Examples of analog voltage (0 - 5V) A/D conversion with 10-bit resolution are shown in Fig.7 and Fig.8.

If the ramp time is counted with a 1 MHz clock, the following resolution is obtained.

25 μA

$$\frac{1000 \ \mu s}{1 \ \mu s} = 1000 \Rightarrow 2^{10}$$

As shown in this example, the voltage output of the sensor is proportional to  $V_{CC}$  (Eq. 7-3) and  $V_{REF}$  is also proportional to  $V_{CC}$  (Eq. 7-1), the sensor output conversion results (Eq. 7-4) are not influenced by power supply voltage fluctuation. Such a conversion is called ratio metric conversion and is effective for minimizing the effects of conversion error. Supply voltage fluctuations during discharge do result in error, however.

MB 4053 FUJITSU MB 4063

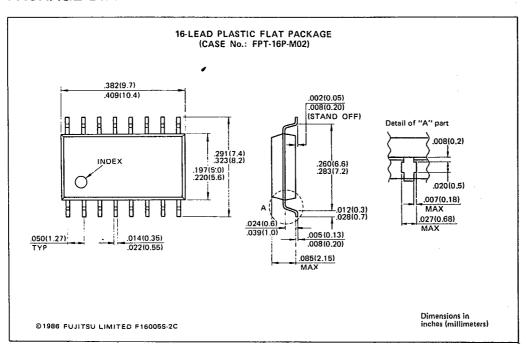

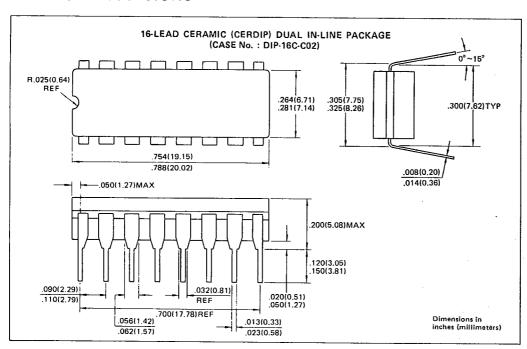

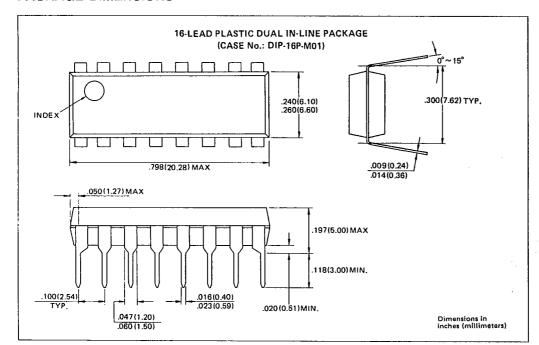

# PACKAGE DIMENSIONS

MB 4053 FUJITSU

MB 4063

# PACKAGE DIMENSIONS

# PACKAGE DIMENSIONS