# 5.0 DETAILED FUNCTIONAL DESCRIPTION

# 5.1 PCI Interface

# 5.1.1 PCI COMMAND SET

Bus commands indicate to the slave the type of transaction the master is requesting. Bus Commands are encoded on the C/BE[3:0] # lines during the address phase of a PCI cycle.

# 5.1.2 PCI BUS TRANSFER BASICS

Details of PCI Bus operations can be found in the *Peripheral Component Interconnect (PCI) Specification*. Only details of the PCI Bus unique to the SIO are included in this data sheet.

**Table 7. PCI Commands**

| C/BE[3:0]# | Command Type As Slave       | Supported As Slave | Supported As Master |

|------------|-----------------------------|--------------------|---------------------|

| 0000       | Interrupt Acknowledge       | Yes                | No                  |

| 0001       | Special Cycle(4)            | No/Yes             | No                  |

| 0010       | I/O Read                    | Yes                | No                  |

| 0011       | I/O Write                   | Yes                | No                  |

| 0100       | Reserved <sup>(3)</sup>     | No                 | No                  |

| 0101       | Reserved <sup>(3)</sup>     | No                 | No                  |

| 0110       | Memory Read                 | Yes                | Yes                 |

| 0111       | Memory Write                | Yes                | Yes                 |

| 1000       | Reserved <sup>(3)</sup>     | No                 | No                  |

| 1001       | Reserved <sup>(3)</sup>     | No                 | No                  |

| 1010       | Configuration Read          | Yes                | No                  |

| 1011       | Configuration Write         | Yes                | No                  |

| 1100       | Memory Read Multiple        | No <sup>(2)</sup>  | No                  |

| 1101       | Reserved <sup>(3)</sup>     | No                 | No                  |

| 1110       | Memory Read Line            | No(2)              | No                  |

| 1111       | Memory Write and Invalidate | No(1)              | No                  |

#### NOTES

- 1. Treated as Memory Write.

- 2. Treated as Memory Read.

- Reserved Cycles are considered invalid by the SIO and are to be competely ignored. All internal address decoding is ignored and DEVSEL# is never to be asserted.

- 4. The 82378 responds to a Stop Grant Special Cycle.

## 5.1.2.1 PCI Addressing

PCI address decoding uses the AD[31:0] signals. AD[31:2] are always used for address decoding while the information contained in the two low order bits AD[1:0] varies for memory, I/O, and configuration cycles.

For I/O cycles, AD[31:0] are decoded to provide a byte address. AD[1:0] are used for generation of DEVSEL# only and indicate the least significant valid byte involved in the transfer. For example, if only BE0# is asserted, AD[1:0] are 00. If only BE3# is asserted, then AD[1:0] are 11. If BE3# and BE2# are asserted, AD[1:0] are 10. If all BEx#'s are asserted, then AD[1:0] are 00. The byte enables determine which byte lanes contain valid data. The SIO requires that PCI accesses to byte-wide internal registers must assert only one byte enable.

When the SIO is the target of any PCI transaction in which BE[3:0] # = 1111, the SIO terminates the cycle normally by asserting TRDY #. No data is written into the SIO during write cycles and the data driven by the SIO during read cycles is indeterminate.

For memory cycles, accesses are decoded as Dword accesses. This means that AD[1:0] are ignored for decoding memory cycles. The byte enables determine which byte lanes contain valid data. When the SIO is a PCI master, it drives 00 on AD[1:0] for all memory cycles.

For configuration cycles, DEVSEL# is a function of IDSEL and AD[1:0]. DEVSEL# is selected during a configuration cycle only if IDSEL is active and both AD[1:0] = 00. The cycle is ignored by the SIO if either AD1 or AD0 is non-zero. Configuration registers are selected as Dwords using AD[7:2]. The byte enables determine which byte lanes contain valid data.

# 5.1.2.2 DEVSEL# Generation

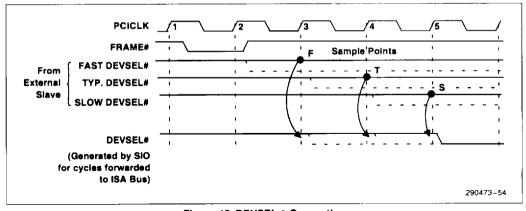

As a PCI slave, the SIO asserts the DEVSEL# signal to indicate it is the slave of the PCI transaction. DEVSEL# is asserted when the SIO positively or

subtractively decodes the PCI transaction. The SIO asserts DEVSEL# (claim the transaction) before it issues any other slave response, i.e., TRDY#, STOP#, etc. After the SIO asserts DEVSEL#, it does not negate DEVSEL# until the same edge that the master uses to negate the final IRDY#.

It is expected that most (perhaps all) PCI target devices will be able to complete a decode and assert DEVSEL# within 1 or 2 clocks of FRAME#. Since the SIO subtractively decodes all unclaimed PCI cycles (except configuration cycles), it provides a configuration option to pull in (by 1 or 2 clocks) the edge when the SIO samples DEVSEL#. This allows faster access to the expansion bus. Use of such an option is limited by the slowest positive decode agent on the bus. This is described in more detail in Section 5.5.1.4, Subtractively Decoded Cycles to ISA.

As a PCI master, the SIO waits for 5 PCICLKs after the assertion of FRAME# for a slave to assert DEVSEL#. If the SIO does not receive DEVSEL# in this time, it will master-abort the cycle. See Section 5.1.3.1, SIO as MasterMaster-Initiated Termination, for further details.

# 5.1.2.3 Basic PCI Read Cycles (I/O and Memory)

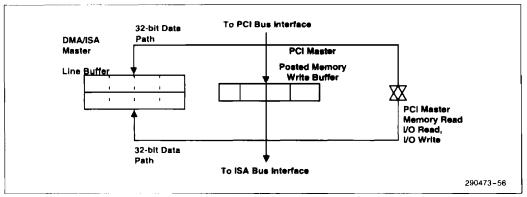

As a PCI master, the SIO only performs memory read transfers (i.e. I/O read transfers are not supported). When reading data from PCI memory, the SIO requests a maximum of 8 bytes via a two data phase burst read cycle to fill its internal 8 byte line buffer. If the line buffer is programmed for single transaction mode, fewer bytes are requested (refer to Section 5.6.1, DMA/ISA Master Line Buffer). Read cycles from PCI memory are generated on behalf of ISA masters and DMA devices.

As a PCI slave, the SIO responds to both I/O read and memory read transfers. For multiple read transactions, the SIO always target-terminates after the first data read transaction by asserting STOP# and TRDY# at the end of the first data phase. For single read transactions, the SIO finishes the cycle in a normal fashion, by asserting TRDY# without asserting STOP#.

## 5.1,2.4 Basic PCI Write Cycles (I/O and Memory)

As a PCI master, the SIO generates a PCI memory write cycle when it decodes an ISA-originated/PCI-bound memory write cycle. I/O write cycles are never initiated by the SIO. When writing data to PCI memory, the SIO writes a maximum of 4 bytes via a single data transaction write cycle. If the SIO's internal ISA master/DMA line buffer is programmed for single transaction mode, fewer bytes will be generated (refer to Section 5.6.1, DMA/ISA Master Line Buffer). In either case, only one data transaction will be performed. Cycles to PCI memory are generated on behalf of ISA masters, DMA devices, and the SIO needs to flush the ISA master/DMA line buffer.

As a PCI master, the SIO drives the AD0 and AD1 signals low during the address phase of the cycle. This is done to indicate to the slave that the address will increment during the transfer. If there is no response on the PCI Bus, the SIO will master-abort due to the DEVSEL# time out.

As a PCI slave, the SIO will respond to both I/O write and memory write transfers. For multiple write transactions, the SIO will always target-terminate after the first data write transaction by asserting STOP# and TRDY# at the end of the first data phase. For single write transactions, the SIO will finish the cycle normally by asserting TRDY# without asserting STOP#.

### 5.1.2.5 Configuration Cycles

The configuration read or write command defined by the bus control signals C/BE[3:0] # is used to configure the SIO. During the address phase of the configuration read or write command, the SIO will sample its IDSEL (ID select). If IDSEL is active and AD[1:0] are both zero, the SIO generates DEVSEL#. Otherwise, the cycle is ignored by the SIO. During the configuration cycle address phase, bits AD[7:2] and C/BE[3:0] # are used to select particular bytes within a configuration register. Note that IDSEL is normally a "don't care" except during the address phase of a transaction.

## NOTE:

An unclaimed configuration cycle is never forwarded to the ISA Bus.

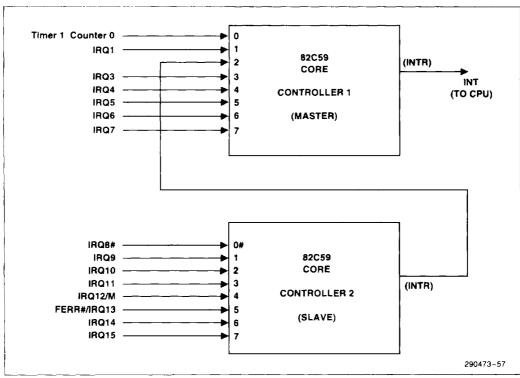

#### 5.1.2.6 Interrupt Acknowledge Cycle

The interrupt acknowledge command is a single byte read implicitly addressed to the SIO's interrupt controller. The address bits are logical "don't cares" during the address phase and the byte enables will indicate to the SIO an 8-bit interrupt vector is to be returned on AD[7:0]. The SIO converts this single cycle transfer into two cycles that the internal 8259 pair can respond to (see Section 5.8, Interrupt Controller). The SIO will hold the PCI Bus in wait states until the 8 bit interrupt vector is returned.

SIO responses to an interrupt acknowledge cycle can be disabled by setting bit 5 in the PCI Control Register to a 0. However, if disabled, the SIO will still respond to accesses to the interrupt register set and allow poll mode functions.

#### 5.1.2.7 Exclusive Access

The SIO marks itself locked anytime it is the slave of the access and LOCK# is sampled negated during the address phase. As a locked slave, the SIO responds to a master only when it samples LOCK# negated and FRAME# asserted. The locking master may negate LOCK# at the end of the last data phase. The SIO unlocks itself when FRAME# and LOCK# are both negated. The SIO will respond by asserting STOP# with TRDY# negated (retry) to all transactions when LOCK# is asserted during the address phase.

Locked cycles are never generated by the SIO.

## 5.1.2.8 PCI Special Cycle

When the SCE bit (bit 3) in the COM PCI configuration register (configuration offset 04h) is set to a "0", the SIO will ignore all PCI Special Cycles. When the SCE bit is set to a "1", the SIO will recognize PCI Special Cycles.

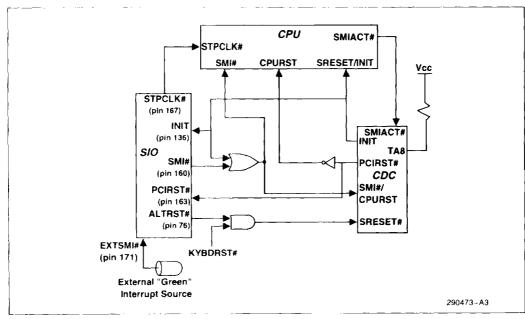

The only PCI Special Cycle currently recognized is the Stop Grant Special Cycle which is broadcast onto the PCI bus when an S-series processor enters the Stop Grant State. The SCE bit must be set to a "1" when the Stop Clock feature is being used.

## **5.1.3 TRANSACTION TERMINATION**

The SIO supports both Master-initiated Termination as well as Target-initiated Termination.

# 5.1.3.1 SIO As Master—Master-Initiated Termination

The SIO supports two forms of master-initiated termination:

- 1. Normal termination of a completed transaction.

- 2. Abnormal termination due to no slave responding to the transaction (Abort).

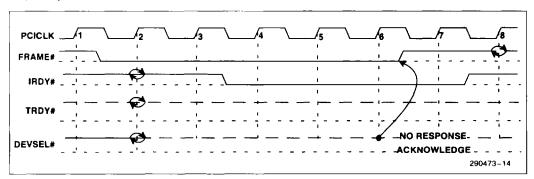

Figure 5 shows the SIO performing master-abort termination. This occurs when no slave responds to the SIO's master transaction by asserting DEVSEL# within 5 PCICLK's after FRAME# assertion. This master-abort condition is abnormal and it indicates an error condition. The SIO will not retry the cycle. The Received Master-abort Status bit in the PCI Status Register will be set indicating that the SIO experienced a master-abort condition.

If an ISA master or the DMA is waiting for the PCI cycle to terminate (CHRDY negated), the master-abort condition will cause the SIO to assert CHRDY to terminate the ISA cycle. Note that write data will be lost and the read data will be all 1's at the end of the cycle. This is identical to the way an unclaimed cycle is handled on the "normally ready" ISA Bus. If the line buffer is the requester of the PCI transaction, the master-abort mechanism will end the PCI cycle, but no data will be transferred into or out of the line buffer. The line buffer will not be allowed to retry the cycle.

# 5.1.3.2 SIO As A Master—Response To Target-Initiated Termination

SIO's response as a master to target-termination:

- 1. For a target-abort, the SIO will not retry the cycle. If an ISA master or the DMA is waiting for the PCI cycle to complete (CHRDY negated), the target-abort condition will cause the SIO to assert CHRDY and end the cycle on the ISA Bus. If the ISA master or DMA device was reading from PCI memory, the SIO will drive all 1's on the data lines of the ISA Bus. The Received Target-abort Status bit in the PCI Status Register will be set indicating that the SIO experienced a target-abort condition.

- If the SIO is retried as a master on the PCI Bus, it will remove it's request for 2 PCI clocks before asserting it again to retry the cycle.

- 3. If the SIO is disconnected as a master on the PCI Bus, it will respond very much as if it had been retried. The difference between retry and disconnect is that the SIO did not see any data phase for the retry. Disconnect may be generated by a PCI slave when the SIO is running a burst memory read cycle to fill it's 8-byte Line Buffer. In this case, the SIO may need to finish a multi-data phase transfer, and thus, must recycle through arbitration as required for a retry. An example of this is when the on-board DMA requests an 8-byte Line Buffer transfer and the SIO is disconnected before the Line Buffer is completely filled.

Figure 5. Master—Initiated Termination (Master-Abort)

## 5.1.3.3 SIO As A Target—Target-Initiated Termination

The SIO supports three forms of Target-initiated Termination:

Disconnect Disconnect refers to termination re-

quested because the SIO is unable to respond within the latency guidelines of the PCI specification. Note that this is not usually done on the first data

phase.

Retry refers to termination requested Retry

because the target is currently in a state which makes it unable to pro-

cess the transaction.

Abort Abort refers to termination requested

because the target will never be able to respond to the transaction.

The SIO will initiate Disconnect for PCI-originated/

ISA-bound cycles after the first data phase due to incremental latency requirements. Since the SIO has only one Posted Write Buffer and every PCI to ISA incremental data phase will take longer than the specified 8 clocks, the SIO will always terminate burst cycles with a disconnect protocol. An example of this is when the SIO receives a burst memory write. Since the SIO only has one Posted Write Buffer, the transaction will automatically be disconnected after the first data phase.

The SIO will retry PCI masters:

- 1. For memory write cycles when the posted write buffer is full.

- 2. When the pending PCI cycle initiates some type of buffer management activity.

- 3. When the SIO is locked as a resource and a PCI master tries to access the SIO without negating the LOCK # signal in the address phase.

- 4. When the ISA Bus is occupied by an ISA master or DMA.

Target-abort is issued by the SIO when the internal SIO registers are the target of a PCI master I/O cycle and more than one byte enable is active. Accesses to the BIOS Timer Register and the Scatter/Gather Descriptor Table Pointer Registers are exceptions to this rule. Accesses to the Scatter/ Gather Descriptor Table Pointer Register must be 32-bits wide and accesses to the BIOS Timer Register must be 16- or 32-bits wide. These accesses will not result in a SIO target-abort. The SIO responds with a target-abort since the registers must be accessed as 8-bit quantities. Target-abort resembles a retry, although the SIO also negates DEVSEL# along with the assertion of STOP#. Bit 11 in the Device Status Register is set to a 1 when the SIO target-aborts.

# 5.1.4 BUS LATENCY TIME-OUT

## 5.1.4.1 Master Latency Timer

Because the SIO only bursts a maximum of two Dwords, the PCI master latency timer is not implemented.

# 5.1.4.2 Target Incremental Latency Mechanism

As a slave, the SIO supports the Incremental Latency Mechanism for PCI to ISA cycles. The PCI specification states that for multi-data phase PCI cycles, if the incremental latency from current data phase (N) to the next data phase (N+1) is greater than 8 PCICLK's, then the slave must manipulate TRDY# and STOP# to stop the transaction upon completion of the current data phase (N). Since all PCI-originated (SIO is a slave)/ISA-bound cycles will require greater than the stated 8 PCICLK's, the SIO will automatically terminate these cycles after the first data phase. Note that latency to the first data phase is not restricted by this mechanism.

#### 5.1.5 PARITY SUPPORT

As a master, the SIO generates address parity for read and write cycles, and data parity for write cycles. As a slave, the SIO generates data parity for read cycles. The SIO does not check parity and does not generate SERR#.

PAR is the calculated parity signal. PAR is "even" parity and is calculated on 36 bits; the 32 AD[31:0] signals plus the 4 C/BE[3:0] # signals. "Even" parity means that the number of 1's within the 36 bits plus PAR are counted and the sum is always even. PAR is always calculated on 36 bits, regardless of the valid byte enables. PAR is only guaranteed to be valid one PCI clock after the corresponding address or data phase.

## 5.1.6 RESET SUPPORT

The PCIRST# pin acts as the SIO hardware reset pin.

## **During Reset**

AD[31:0], C/BE[3:0] #, and PAR are always driven low by the SIO from the leading edge of PCIRST #, FRAME #, IRDY #, TRDY #, STOP #, DEVSEL #, MEMREQ #, FLSHREQ #, CPUGNT #, GNTO #/ SIOREQ #, and GNT1 #/ RESUME # are tri-stated from the leading edge of PCIRST #.

GNT2# and GNT3# are tri-stated from the leading edge of PCIRST#.

#### After Reset

AD[31:0], C/BE[3:0] #, and PAR are always tri-stated from the trailing edge of PCIRST #. If the internal arbiter is enabled (CPUREQ # sampled high on the trailing edge of PCIRST #), the SIO will drive these signals low again (synchronously 2-5 PCICLKs later) until the bus is given to another master. If the internal arbiter is disabled (CPUREQ # sampled low on the trailing edge of PCIRST #), these signals remain tri-stated until the SIO is required to drive them valid as a master or slave.

FRAME#, IRDY#, TRDY#, STOP#, and DEVSEL# remain tri-stated until driven by the SIO as either a master or a slave. MEMREQ#, FLSHREQ#, CPUGNT#, GNTO#/SIOREQ#, and GNT1#/RESUME# are tri-stated until driven by the SIO.

GNT2# and GNT3# are tri-stated until driven by the SIO.

After PCIRST, MEMREQ# and FLSHREQ# are driven inactive asynchronously from PCIRST# inactive. CPUGNT#, GNT0#/SIOREQ#, and GNT1#/RESUME# are driven based on the arbitration scheme and the asserted REQx#'s.

GNT2# and GNT3# are also driven based on the arbitration scheme and the asserted REQx#'s.

## 5.1.7 DATA STEERING

Data steering logic internal to the SIO provides the assembly/disassembly, copy up/copy down mechanism for cycles between the 32-bit PCI data bus and the 16-bit ISA Bus. The steering logic ensures that the correct bytes are steered to the correct byte lane and that multiple cycles are run where applicable.

#### 5.2 PCI Arbitration Controller

The 82378 contains a PCI Bus arbiter that supports six PCI masters; the Host Bridge, SIO, and four other masters. The SIO's REQ#/GNT# lines are internal. The integrated arbiter can be disabled by asserting CPUREQ# during PCIRST# (see Section 5.2.7, Power-up Configuration). When disabled, the SIO's REQ#, GNT#, and RESUME# signals become visible for an external arbiter. The internal arbiter is enabled upon power-up.

The internal arbiter contains several features that contribute to system efficiency:

- Use of a RESUME# signal to re-enable a backed-off initiator in order to minimize PCI Bus thrashing when the SIO generates a retry (Section 5.2.4.1).

- A programmable timer to re-enable retried initiators after a programmable number of PCICLK's (Section 5.2.4.2).

- The CPU (host bridge) can be optionally parked on the PCI Bus (Section 5.2.5).

- A programmable PCI Bus lock or PCI resource lock function (Section 5.2.6).

The PCI arbiter is also responsible for control of the Guaranteed Access Time (GAT) mode signals (Section 5.2.3.2).

#### 5.2.1 ARRITRATION SIGNAL PROTOCOL

The internal arbiter follows the PCI arbitration method as outlined in the Peripheral Component Interconnect (PCI) Specification. The SIO's arbiter is discussed in this section.

#### 5.2.1.1 Back-To-Back Transactions

The SIO as a master does not generate fast backto-back accesses since it does not know if it is accessing the same target.

The SIO as a target supports fast back-to-back transactions. Note that for back-to-back cycles, the SIO treats positively decoded accesses and subtractively decoded accesses as different targets. Therefore, masters can only run fast back-to-back cycles to positively decoded addresses or to subtractively decoded addresses. Fast back-to-back cycles must not mix positive and subtractive decoded addresses. See the address decoding section to determine what addresses the SIO positively decodes and subtractively decodes.

## **5.2.2 PRIORITY SCHEME**

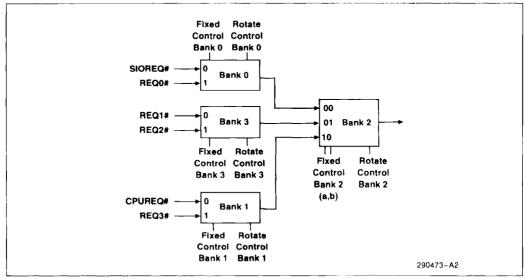

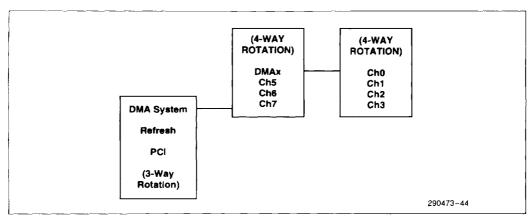

The PCI arbitration priority scheme is programmable through the PCI Arbiter Priority Control and Arbiter Priority Control Extension Register. The arbiter consists of four banks that can be configured for the six masters to be arranged in a purely rotating priority scheme, one of twenty-four fixed priority schemes, or a hybrid combination (Figure 6).

Note that SIOREQ#/SIOGNT# are SIO internal signals.

The PCI Arbiter Priority Control (PAPC) and PCI Arbiter Priority Control Extension Register bits are shown below:

# PCI Arbiter Priority Control Register Bits (PAPC)

| 7 | Bank 3 Rotate Control |

|---|-----------------------|

| 6 | Bank 2 Rotate Control |

Description

Di+

- 5 Bank 1 Botate Control

- Bank 0 Rotate Control 1

- 3 Bank 2 Fixed Priority Mode select B

- 2 Bank 2 Fixed Priority Mode select A

- Bank 1 Fixed Priority Mode select 1

- Λ Bank 0 Fixed Priority Mode select

# PCI Arbiter Priority Control Extension Register Bits (ARBPRIX)

| Bit | Description                       |

|-----|-----------------------------------|

| 7:1 | Reserved. Read as 0               |

| Λ   | Bank 3 Fixed Priority Mode select |

PAPC defaults to 04h and ARBPRIX to 00h at reset selecting fixed mode #10 (Table 8) with the CPU the highest priority device guaranteeing access to BIOS.

Figure 6. Arbiter Configuration Diagram for 82378ZB

# 5.2.2.1 Fixed Priority Mode

The 24 selectable fixed priority schemes are listed in Table 8.

Table 8. Fixed Priority Mode Bank Control Bits

| Mode  | ode Bank |    |    | Priority |   |          |         |         |         |         |         |

|-------|----------|----|----|----------|---|----------|---------|---------|---------|---------|---------|

| Mode  | 3        | 2b | 2a | 1        | 0 | Highest  |         |         |         |         | Lowest  |

| 00    | 0        | 0  | 0  | 0        | 0 | SIOREQ#  | REQ0#   | REQ2#   | REQ3#   | CPUREQ# | REQ1#   |

| 01    | 0        | 0  | 0  | 0        | 1 | REQ0#    | SIOREQ# | REQ2#   | REQ3#   | CPUREQ# | REQ#    |

| 02    | 0        | 0  | 0  | 1        | 0 | SIOREQ#  | REQ0#   | REQ2#   | REQ3#   | REQ1#   | CPUREQ# |

| 03    | 0        | 0  | 0  | 1        | 1 | REQ0#    | SIOREQ# | REQ2#   | REQ3#   | REQ1#   | CPUREQ# |

| 04    | 0        | 0  | 1  | 0        | 0 | CPUREQ#  | REQ1#   | SIOREQ# | REQ0#   | REQ2#   | REQ3#   |

| 05    | 0        | 0  | 1  | 0        | 1 | CPUREQ#  | REQ1#   | REQ0#   | SIOREQ# | REQ2#   | REQ3#   |

| 06    | 0        | 0  | 1  | 1        | 0 | REQ1#    | CPUREQ# | SIOREQ# | REQ0#   | REQ2#   | REQ3#   |

| 07    | 0        | 0  | 1  | 1        | 1 | REQ1#    | CPUREQ# | REQ0#   | SIOREQ# | REQ2#   | REQ3#   |

| 08    | 0        | 1  | 0  | 0        | 0 | REQ2#    | REQ3#   | CPUREQ# | REQ1#   | SIOREQ# | REQ0#   |

| 09    | 0        | 1  | 0  | 0        | 1 | REQ2#    | REQ3#   | CPUREQ# | REQ1#   | REQ0#   | SIOREQ# |

| 0A    | 0        | 1  | 0  | 1        | 0 | REQ2#    | REQ3#   | REQ1#   | CPUREQ# | SIOREQ# | REQ0#   |

| 0B    | 0        | 1  | 0  | 1        | 1 | REQ2#    | REQ3#   | REQ1#   | CPUREQ# | REQ0#   | SIOREQ# |

| 0C-0F | 0        | 1  | 1  | х        | x |          |         | Rese    | erved   |         |         |

| 10    | 1        | 0  | 0  | 0        | 0 | SIOREQ#  | REQ0#   | REQ3#   | REQ2#   | CPUREQ# | REQ1#   |

| 11    | 1        | 0  | 0  | 0        | 1 | REQ0#    | SIOREQ# | REQ3#   | REQ2#   | CPUREQ# | REQ1#   |

| 12    | 1        | 0  | 0  | 1        | 0 | SIOREQ#  | REQ0#   | REQ3#   | REQ2#   | REQ1#   | CPUREQ# |

| 13    | 1        | 0  | 0  | 1        | 1 | REQ0#    | SIOREQ# | REQ3#   | REQ2#   | REQ1#   | CPUREQ# |

| 14    | 1        | 0  | 1  | 0        | 0 | CPUREQ#  | REQ1#   | SIOREQ# | REQ0#   | REQ3#   | REQ2#   |

| 15    | 1        | 0  | 1  | 0        | 1 | CPUREQ#  | REQ1#   | REQ0#   | SIOREQ# | REQ3#   | REQ2#   |

| 16    | 1        | 0  | 1  | 1        | 0 | REQ1#    | SPUREQ# | SIOREQ# | REQ0#   | REQ3#   | REQ2#   |

| 17    | 1        | 0  | 1  | 1        | 1 | REQ1#    | CPUREQ# | REQ0#   | SIOREQ# | REQ3#   | REQ2#   |

| 18    | 1        | 1  | 0  | 0        | 0 | REQ3#    | REQ2#   | CPUREQ# | REQ1#   | SIOREQ# | REQ0#   |

| 19    | 1        | 1  | 0  | 0        | 1 | REQ3#    | REQ2#   | CPUREQ# | REQ1#   | REQ0#   | SIOREQ# |

| 1A    | 1        | 1  | 0  | 1        | 0 | REQ3#    | REQ2#   | REQ1#   | CPUREQ# | SIOREQ# | REQ0#   |

| 1B    |          | 1  | 0  | 1        | 1 | REQ3#    | REQ2#   | REQ1#   | CPUREQ# | REQ0#   | SIOREQ# |

| 1C-1F | 1        | 1  | 1  | x        | x | Reserved |         |         |         |         |         |

The fixed bank control bit(s) selects which requester is the highest priority device within that particular bank. For fixed priority mode, bits[7:4] of the PAPC Register and bit zero of ARBPRIX must be 0's (rotate mode disabled).

The selectable fixed priority schemes provide 24 of the 64 possible fixed mode permutations possible for the six masters

## 5.2.2.2 Rotating Priority Mode

When any bank rotate control bit is set to a one, that particular bank rotates between the requesting inputs. Any or all banks can be set in rotate mode. If all four banks are set in rotate mode, the six supported masters are all rotated and the arbiter is in a pure rotating priority mode. If, within a rotating bank, the highest priority device (a) does not have an active request, the lower priority device (b or c) will be granted the bus. However, this does not change the rotation scheme. When the bank toggles, device b is the highest priority. Because of this, the maximum latency a device can encounter is two complete rotations.

# 5.2.2.3 Mixed Priority Mode

Any combination of fixed priority and rotate priority modes can be used in different arbitration banks to achieve a specific arbitration scheme.

## 5.2.2.4 Locking Masters

When a master acquires the LOCK # signal, the arbiter gives that master highest priority until the LOCK # signal is negated and FRAME # is negated. This ensures that a master that locked a resource will eventually be able to unlock that same resource.

# 5.2.3 MEMREQ#, FLSHREQ#, AND MEMACK# PROTOCOL

Before an ISA master or the DMA can be granted the PCI Bus, it is necessary that all PCI system posted write buffers be flushed (including the SIO's Posted Write Buffer). Also, since the ISA originated cycle could access memory on the host bridge, it's possible that the ISA master or the DMA could be held in wait states (via IOCHRDY) waiting for the host bridge arbitration for longer than the 2.5 μs ISA specification. The SIO has an optional mode called the Guaranteed Access Time Mode (GAT) that ensures that this timing specification is not violated. This is accomplished by delaying the ISA REQ# signal to the requesting master or DMA until the ISA Bus, PCI Bus, and the System Memory Bus are arbitrated for and owned.

Three PCI sideband signals, MEMREQ#, FLSHREQ#, and MEMACK# are used to support the System Posted Write Buffer Flushing and Guaranteed Access Time mechanisms. The MEMACK# signal is the common acknowledge signal for both mechanisms. Note that when MEMREQ# is asserted, FLSHREQ# is also asserted. Table 9 shows the relationship between MEMREQ# and FLSHREQ#:

Table 9. FLSHREQ #, MEMREQ #

| FLSHREQ# | MEMREQ# | Meaning                                                     |

|----------|---------|-------------------------------------------------------------|

| 1        | 1       | Idle                                                        |

| 0        | 1       | Flush buffers pointing towards PCI to avoid ISA deadlock    |

| 1        | 0       | Reserved                                                    |

| 0        | 0       | GAT mode, Guarantee PCI Bus immediate access to main memory |

## 5.2.3.1 Flushing the System Posted Write Buffers

Once an ISA master or the DMA begins a cycle on the ISA Bus, the cycle can not be backed-off. It can only be held in wait states via IOCHRDY. In order to know the destination of ISA master cycles, the cycle needs to begin. However, after the cycle has started, no other device can intervene and gain ownership of the ISA Bus until the cycle has completed and arbitration is performed. A potential deadlock condition exists when an ISA originated cycle to the PCI Bus finds the PCI target inaccessible due to an interacting event that also requires the ISA Bus. To avoid this potential deadlock, all PCI posted write buffers in the system must be disabled and flushed before DACK can be returned. The buffers must remain disabled while the ISA Bus is occupied by an ISA master or the DMA.

When an ISA master or the DMA requests the ISA Bus, the SIO asserts FLSHREQ#. FLSHREQ# is an indication to the system to flush all posted write buffers pointing towards the PCI Bus. The SIO also flushes it's own Posted Write Buffer. Once the posted write buffers have been flushed and disabled, the system asserts MEMACK#. Once the SIO receives the MEMACK# acknowledgment signal, it asserts the DACK signal giving the requesting master the bus. FLSHREQ# stays active as long as the ISA master or DMA owns the ISA Bus.

# 5.2,3.2 Guaranteed Access Time Mode

Guaranteed Access Time (GAT) Mode is enabled/disabled via the PCI Arbiter Control Register. When this mode is enabled, the MEMREQ# and MEMACK# signals are used to guarantee that the ISA 2.5 µs IOCHRDY specification is not violated.

When an ISA master or DMA slave requests the ISA Bus (DREQ# active), the ISA Bus, the PCI Bus, and the memory bus must be arbitrated for and all three must be owned before the ISA master or DMA slave is granted the ISA Bus. After receiving the DREQ# signal from the ISA master or DMA slave, MEMREQ# and FLSHREQ# are asserted (FLSHREQ# is driven active, regardless of GAT

mode being enabled or disabled). MEMREQ# is a request for direct access to main memory. MEMREQ# and FLSHREQ# will be asserted as long as the ISA master or the DMA owns the ISA Bus. When MEMACK# is received by the SIO (all posted write buffers are flushed and the memory bus is dedicated to the PCI interface), it will request the PCI Bus. When it is granted the PCI Bus, it asserts the DACK signal releasing the ISA Bus to the requesting master or the DMA.

The use of MEMREQ#, FLSHREQ#, and MEMACK# does not guarantee functionality with ISA masters that don't acknowledge IOCHRDY. These signals just guarantee the IOCHRDY inactive specification.

#### NOTE:

Usage of an external arbiter in GAT mode will require special logic in the arbiter.

#### 5.2.4 RETRY THRASHING RESOLVE

When a PCI initiator's access is retried, the initiator releases the PCI Bus for a minimum of two PCI clocks and will then normally request the PCI Bus again. To avoid thrashing the bus with retry after retry, the PCI arbiter provides REQ# masking. The REQ# masking mechanism differentiates between SIO target retries and all other retries.

For initiators which were retried by the SIO as a target, the masked REQ# is flagged to be cleared upon RESUME# active. All other retries trigger the Master Retry Timer, if enabled. Upon expiration of this timer, the mask is cleared.

# 5.2.4.1 Resume Function (RESUME #)

The conditions under which the SIO forces a retry to a PCI master and will mask the REQ# are:

- Any required buffer management

- 2. ISA Bus occupied by ISA master or DMA

- 3. The PCI to ISA Posted Write Buffer is full

- The SIO is locked as a resource and LOCK# is asserted during the address process.

# 82378 SYSTEM I/O (SIO)

The RESUME \* signal is pulsed whenever the SIO has retried a PCI cycle for one of the above reasons and that condition has passed. When RESUME \* is asserted, the SIO will unmask the REQ \* s that are masked and flagged to be cleared by RESUME \*.

If the internal arbiter is enabled, RESUME # is an internal signal. The RESUME # signal becomes visible as an output when the internal arbiter is disabled. This allows an external arbiter to optionally avoid retry thrashing associated with the SIO as a target. The RESUME # signal is asserted for one PCI clock.

## 5.2.4.2 Master Retry Timer

To re-enable a PCI master's REQ# which resulted in a retry to a slave other than the SIO, a SIO programmable Master Retry Timer has been provided. This timer can be programmed for 0 (disabled), 16, 32, or 64 PCICLKs. Once the SIO has detected that a PCI slave has forced a retry, the timer will be triggered and the corresponding master's REQ# will be masked. All subsequent PCI retries by this REQ# signal will by masked by the SIO. Expiration of this timer will unmask all of the masked requests. This timer has no effect on the request lines that have been masked due to a SIO retry.

If no other PCI masters are requesting the PCI Bus, all of the REQ\*'s masked for the timer will be cleared and the timer will be reset. This is necessary to assist the host bridge in determining when to reenable any disabled posted write buffers.

#### 5.2.5 BUS PARKING

The SIO arbitration logic supplies a mechanism for PCI Bus parking. Parking is only allowed for the device which is tied to CPUREQ# (typically the system CPU). When bus parking is enabled, CPUGNT# will be asserted when no other agent is currently using or requesting the bus. This achieves the minimum PCI arbitration latency possible. Enabling of bus parking is achieved by programming the Arbiter Control Register. REQ0#, REQ1#, and the internal SIOREQ# are not allowed to park on the PCI Bus.

Upon assertion of CPUGNT# due to bus parking enabled and the PCI Bus idle, the CPU (or the

parked agent) must ensure that AD[31:0], C/BE[3:0], and (one PCICLK later) PAR are driven. If bus parking is disabled, the SIO takes responsibility for driving the bus when it is idle.

## 5.2.6 BUS LOCK MODE

As an option, the SIO arbiter can be configured to run in Bus Lock Mode or Resource Lock Mode. The Bus Lock Mode is used to lock the entire PCI Bus. This may improve performance in some systems that frequently run quick read-modify-write cycles Bus Lock Mode emulates the LOCK environment found in today's PC by restricting bus ownership when the PCI Bus is locked. With Bus Lock enabled. the arbiter recognizes a LOCK # being driven by any initiator and does not allow any other PCI initiator to be granted the PCI Bus until LOCK# and FRAME# are both negated indicating the master released lock. When Bus Lock is disabled, the default resource lock mechanism is implemented (normal resource lock) and a higher priority PCI initiator could intervene between the read and write cycles and run non-exclusive accesses to any unlocked resource.

#### 5.2.7 POWER-UP CONFIGURATION

The SIO's arbiter is enabled if CPUREQ# is sampled high on the trailing edge of PCIRST#. When enabled, the arbiter is set in fixed priority mode 4 with CPU bus parking turned off. Fixed mode 4 quarantees that the CPU will be able to run accesses to the BIOS in order to configure the system, regardless of the state of the other REQ # 's. Note that the Host Bridge should drive CPUREQ# high during the trailing edge of PCIRST#. When the arbiter is enabled, the SIO acts as the central resource responsible for driving the AD[31:0], C/BE[3:0] #, and PAR signals when no one is granted the PCI Bus and the bus is idle. The SIO is always responsible for driving AD[31:0], C/BE[3:0] #, and PAR when it is granted the bus and as appropriate when it is the master of a transaction. After reset, if the arbiter is enabled, CPUGNT#, GNT0#, GNT1#, and the internal SIOGNT# will be driven based on the arbitration scheme and the asserted REQ #'s.

If an external arbiter is present in the system, the CPUREQ# signal should be tied low. When CPUREQ# is sampled low on the trailing edge of PCIRST#, the internal arbiter is disabled. When the internal arbiter is disabled, the SIO does not drive AD[31:0], C/BE[3:0] #, and PAR as the central resource. In this case, the SIO is only responsible for driving AD[31:0], C/BE[3:0] #, and PAR when it is granted the bus. If the SIO's arbiter is disabled, GNT0# becomes SIOREQ#, GNT1# becomes RESUME#, and REQ0# becomes SIOGNT#. This exposes the normally embedded SIO arbitration signals.

#### NOTE:

Usage of an external arbiter in GAT mode will require special logic in the arbiter.

# 5.3 ISA Interface

#### 5.3.1 ISA INTERFACE OVERVIEW

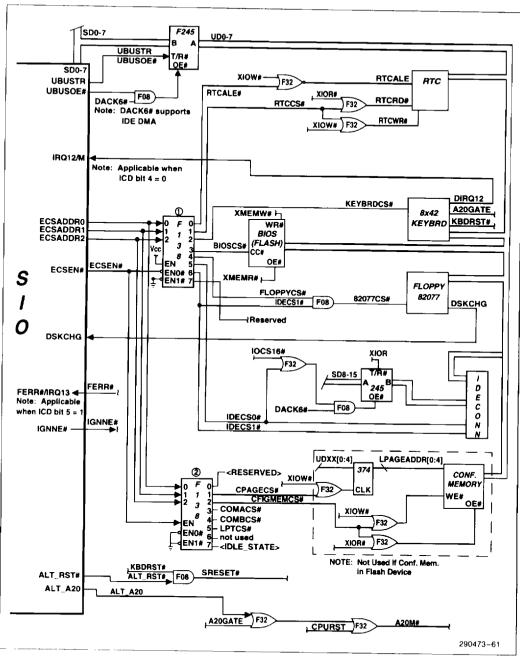

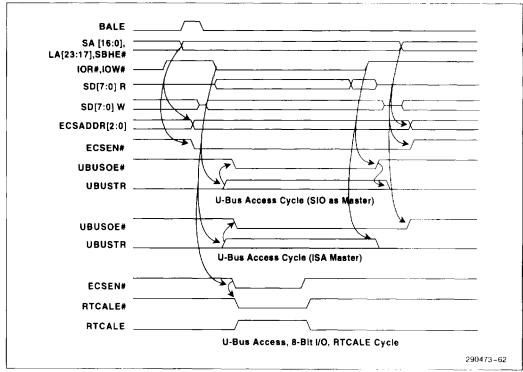

The SIO incorporates a fully ISA Bus compatible master and slave interface. The SIO directly drives six ISA slots without external data or address buffers. The ISA interface also provides byte swap logic, I/O recovery support, wait-state generation, and SYSCLK generation.

The ISA interface supports the following types of cycles:

- PCI-initiated I/O and memory cycles to the ISA Rus

- DMA compatible cycles between PCI memory and ISA I/O and between ISA I/O and ISA memory, DMA type "A", type "B", and type "F" cycles between PCI memory and ISA I/O.

- ISA Refresh cycles initiated by either the SIO or an external ISA master.

- ISA master-initiated memory cycles to the PCI Bus and ISA master-initiated I/O cycles to the internal SIO registers.

The refresh and DMA cycles are shown and described in Section 5.4.

#### 5.3.2 SIO AS AN ISA MASTER

The SIO executes ISA cycles as an ISA master whenever a PCI initiated cycle is forwarded to the ISA Bus. The SIO also acts as an ISA master on behalf of DMA and refresh.

ISYSCLK is an internal 8 MHz clock.

#### 5.3.3 SIO AS AN ISA SLAVE

The SIO operates as an ISA slave when:

- · An ISA master accesses SIO internal registers.

- An ISA master accesses PCI memory on the PCI Bus.

# 5.3.3.1 ISA Master Accesses To SIO Registers

An ISA Bus master has access to SIO internal registers as shown in Table 19. An ISA master to SIO register cycle will always run as an 8-bit extended cycle (IOCHRDY will be held inactive until the cycle is completed).

**Table 10. Arbitration Latency**

| Bus Condition | Arbitration Latency                            |

|---------------|------------------------------------------------|

| Parked        | 0 PCICLKs for Agent 0, 2 PCICLKs for All Other |

| Not Parked    | 1 PCICLK for All Agents                        |

#### 5.3.3.2 ISA Master Accesses to PCI Resource

An ISA master can access PCI memory, but not I/O devices residing on the PCI Bus. The ISA/DMA address decoder determines which memory cycles should be directed towards the PCI Bus. During ISA master read cycles to the PCI Bus, the SIO will return all 1's if the PCI cycle is target-aborted or does not respond.

If the SIO is programmed for GAT mode, the SIO arbiter will not grant the ISA Bus before gaining ownership of both the PCI Bus and system memory. However, if the SIO is not programmed in this mode, the SIO does not need to arbitrate for the PCI Bus before granting the ISA Bus to the ISA master. For more details on the arbitration, refer to Section 5.2.2.

All cycles forwarded to a PCI resource will run as 16-bit extended cycles (i.e. IOCHRDY will be held inactive until the cycle is completed).

Because the ISA bus size is different from the PCI bus size, the data steering logic inside the SIO is responsible for steering the data to the correct byte lanes on both buses, and assembling/disassemblying the data as necessary.

## 5.3.4 ISA MASTER TO ISA SLAVE SUPPORT

During ISA master cycles to ISA slaves, the SIO drives several signals to support the transfer:

# BALE:

This signal is driven high while the ISA master owns the ISA Bus.

# AEN:

This signal is driven low while the ISA master owns the ISA Bus.

# SMEMR # and SMEMW #:

These signals are driven active by the SIO whenever the ISA master drives a memory cycle to an address below 1 Mb.

# Utility Bus Buffer Control Signals and Chip Select Signals:

These signals are driven active as appropriate whenever an ISA master accesses devices on the Utility Bus. For more details, see Section 5.9.

## Data Swap Logic:

The data swap logic inside the SIO is activated as appropriate to swap data between the even and odd byte lanes. This is discussed in further detail in Section 5.3.5.

#### 5.3.5 DATA BYTE SWAPPING

The data swap togic is integrated in the SIO. For slaves that reside on the ISA Bus, data swapping is performed if the slave (I/O or memory) and ISA bus master (or DMA) sizes differ and the upper (odd) byte of data is being accessed. Table 11 shows when data swapping is provided during DMA. Table 12 shows when data swapping is provided during ISA master cycles to 8-bit ISA slaves.

Table 11. DMA Data Swap

| DMA I/O Device<br>Size | ISA Memory Slave<br>Size | Swap | 1/0      | Comments ←→              | Memory   |

|------------------------|--------------------------|------|----------|--------------------------|----------|

| 8-Bit                  | 8-Bit                    | No   | SD[7:0]  | <b>←</b> →               | SD[7:0]  |

| 8-Bit                  | 16-Bit                   | Yes  | SD[7:0]  | $\leftarrow \rightarrow$ | SD[7:0]  |

|                        |                          |      | SD[7:0]  | <del></del>              | SD[15:8] |

| 16-Bit                 | 8-Bit                    | No   | ,        | Not Supporte             | d        |

| 16-Bit                 | 16-Bit                   | No   | SD[15:0] | <del></del>              | SD[15:0] |

The SIO monitors the SBHE # and SA0 signals to determine when to swap the data. The SIO ensures that the data is placed on the appropriate byte lane.

Table 12. 16-Bit Master to 8-Bit Slave Data Swap

| SBHE # | SA0 | SD[15:8] | SD[7:0] | Comments                                   |

|--------|-----|----------|---------|--------------------------------------------|

| 0      | 0   | Odd      | Even    | Word Transfer (data swapping not required) |

| 0      | 1   | Odd      | Even    | Byte Swap <sup>(1,2)</sup>                 |

| 1      | 0   | _        | Even    | Byte Transfer (data swapping not required) |

| 1      | 1   | _        | _       | Not Allowed                                |

#### NOTES

- 1. For ISA master read cycles, the SIO swaps the data from the lower byte to the upper byte.

- 2. For ISA master write cycles, the SIO swaps the data from the upper byte to the lower byte.

# 5.3.6 ISA CLOCK GENERATION

The SIO generates the ISA system clock (SYSCLK). SYSCLK is a divided down version of the PCICLK (see Table 13). The clock divisor value is programmed through the ISA Clock Divisor Register.

Table 13. SYSCLK Generation from PCICLK

| PCICLK (MHz) | Divisor (Programmable) | SYSCLK (MHz) |

|--------------|------------------------|--------------|

| 25           | 3                      | 8.33         |

| 33           | 4 (default)            | 8.33         |

#### NOTE:

For PCI frequencies less than 33 MHz (not including 25 MHz), a clock divisor value must be selected that ensures that the ISA Bus frequency does not violate the 6 MHz to 8.33 MHz SYSCLK specification.

### 5.3.7 WAIT STATE GENERATION

The SIO will add wait states to the following cycles, if IOCHRDY is sampled active low. Wait states will be added as long as IOCHRDY is low.

- During Refresh and SIO master cycles (not including DMA) to the ISA Bus.

- During DMA compatible transfers between ISA I/O and ISA memory only.

For ISA master cycles targeted for the SIO's internal registers or PCI memory, the SIO will always extend the cycle by driving IOCHRDY low until the transaction is complete.

The SIO will shorten the following cycles, if ZEROWS# is sampled active.

- During SIO master cycles (not including DMA) to 8-bit and 16-bit ISA memory.

- During SIO master cycles (not including DMA) to 8-bit ISA I/O only.

For ISA master cycles targeted for the SIO's internal registers or PCI memory, the SIO will not assert ZEROWS#.

# NOTE:

If IOCHRDY and ZEROWS# are sampled active at the same time, IOCHRDY will take precedence and wait-states will be added.

## **5.3.8 I/O RECOVERY**

The I/O recovery mechanism in the SIO is used to add additional recovery delay between PCI originated 8-bit and 16-bit I/O cycles to the ISA Bus. The SIO automatically forces a minimum delay of four SYSCLKs between back-to-back 8- and 16-bit I/O cycles to the ISA Bus. This delay is measured from the rising edge of the I/O command (IOR# or IOW#) to the falling edge of the next BALE. If a delay of greater than four SYSCLKs is required, the ISA I/O Recovery Time Register can be programmed to increase the delay in increments of SYSCLKs. No additional delay is inserted for back-to-back I/O "sub cycles" generated as a result of byte assembly or disassembly.

### 5.4 DMA Controller

# **5.4.1 DMA CONTROLLER OVERVIEW**

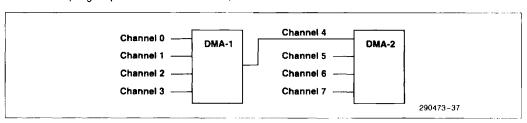

The DMA circuitry incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels (Channels 0-3 and Channels 5-7). DMA Channel 4 is used to cascade the two controllers and will default to cascade mode in the DMA Channel Mode (DCM) Register. In addition to accepting requests from DMA slaves, the

DMA controller also responds to requests that are initiated by software. Software may initiate a DMA service request by setting any bit in the DMA Channel Request Register to a 1. The DMA controller for Channels 0-3 is referred to as "DMA-1" and the controller for Channels 4-7 is referred to as "DMA-2".

Each DMA channel may be programmed for 8- or 16-bit DMA device size and ISA-compatible, Type "A", Type "B", or Type "F" transfer timing. Each DMA channel defaults to the compatible settings for DMA device size: channels [3:0] default to 8-bit, count-by-bytes transfers, and channels [7:5] default to 16-bit, count-by-words (address shifted) transfers. The SIO provides the timing control and data size translation necessary for the DMA transfer between the PCI and the ISA Bus. ISA-compatible is the default transfer timing.

Full 32-bit addressing is supported as an extension of the ISA-compatible specification. Each channel includes a 16-bit ISA compatible Current Register which holds the 16 least-significant bits of the 32-bit address, and an ISA compatible Low Page Register which contains the eight second most significant bits. An additional High Page Register contains the eight most significant bits of the 32-bit address.

Figure 7. Internal DMA Controller

The DMA controller also features refresh address generation, and auto-initialization following a DMA termination.

The DMA controller receives commands from the ISA Bus arbiter to perform either DMA cycles or refresh cycles. The arbiter determines which requester from among the requesting DMA slaves, the PCI Bus, and refresh should have the bus.

The DMA controller is at any time either in master mode or slave mode. In master mode, the DMA controller is either servicing a DMA slave's request for DMA cycles, or allowing a 16-bit ISA master to use the bus via a cascaded DREQ signal. In slave mode, the SIO monitors both the ISA Bus and the PCI, decoding and responding to I/O read and write commands that address its registers.

Note that a DMA device (I/O device) is always on the ISA Bus, but the memory device is either on the ISA or PCI Bus. If the memory is decoded to be on the ISA Bus, then the DMA cycle will run as a compatible cycle. If the memory is decoded to be on the PCI Bus, the cycle can run as compatible, "A", "B", or "F" type. The ISA controller will not drive a valid address for type "A", "B", and "F" DMA transfers on the ISA Bus.

When the SIO is running a DMA cycle in compatible timing mode, the SIO will drive the MEMR# or MEMW# strobes if the address is less than (00000000h-00FFFFFh). MBvtes memory strobes will be generated regardless of whether the cycle is decoded for PCI or ISA memory. The SMEMR# and SMEMW# will be generated if the address is less than 1 MBytes (00000000h-000FFFFFh). If the address is greater than 16 MBytes (01000000h-FFFFFFFh) the MEMR # or MEMW # strobe will not be generated in order to avoid aliasing problems. For type "A", "B", and "F" timing mode DMA cycles, the SIO will only generate the MEMR# or MEMW# strobe when the address is decoded for ISA memory. When this occurs, the cycle converts to compatible mode timing.

During DMA cycles, the ISA controller drives AEN high to prevent the I/O devices from misinterpreting the DMA cycle as a valid I/O cycle. The BALE signal is also driven high during DMA cycles. Also, during DMA memory read cycles to the PCI Bus, the SIO will return all 1's to the ISA Bus if the PCI cycle is either target-aborted or does not respond.

Further details can be found in the 82C37 data sheet

## 5.4.2 DMA TIMINGS

ISA Compatible timing is provided for DMA slave devices. Three additional timings are provided for I/O slaves capable of running at faster speeds. These timings are referred to as Type "A", Type "B", and Type "F".

#### 5.4.2.1 Compatible Timing

Compatible timing runs at 8 SYSCLKs during the repeated portion of a Block or Demand mode transfer.

## 5.4.2.2 Type "A" Timing

Type "A" timing is provided to allow shorter cycles to PCI memory. Type "A" timing runs at 6 SYSCLKs (720 ns/cycle) during the repeated portion of a block or demand mode transfer. This timing assumes an 8.33 MHz SYSCLK. Type "A" timing varies from compatible timing primarily in shortening the memory operation to the minimum allowed by system memory. The I/O portion of the cycle (data setup on write, I/O read access time) is the same as with compatible cycles. The actual active command time is shorter, but it is expected that the DMA devices which provide the data access time or write data setup time should not require excess IOR# or IOW # command active time. Because of this, most ISA DMA devices should be able to use type "A" timina.

# 5.4.2.3 Type "B" Timing

Type "B" timing is provided for 8-/16-bit ISA DMA devices which can accept faster I/O timing. Type "B" only works with PCI memory. Type "B" timing runs at 5 SYSCLKs (600 ns/cycle) during the repeated portion of a Block or Demand mode transfer. This timing assumes an 8.33 MHz SYSCLK. Type "B" timing requires faster DMA slave devices than compatible timing in that the cycles are shortened so that the data setup time on I/O write cycles is shortened and the I/O read access time is required to be faster. Some of the current ISA devices should be able to support type "B" timing, but these will probably be more recent designs using relatively fast technology.

# 5.4.2.4 Type "F" Timing

Type "F" timing provides high performance DMA transfer capability. These transfers are mainly for fast I/O devices (i.e. IDE devices). Type "F" timing runs at 3 SYSCLKs (360 ns/cycle) during the repeated portion of a Block or Demand mode transfer.

# 5.4.2.5 DREQ and DACK # Latency Control

The SIO DMA arbiter maintains a minimum DREQ to DACK# latency on DMA channels programmed to

operate in compatible timing mode. This is to support older devices such as the 8272A. The DREQs are delayed by eight SYSCLKs prior to being seen by the arbiter logic. Software requests will not have this minimum request to DACK # latency.

### 5.4.3 ISA BUS/DMA ARBITRATION

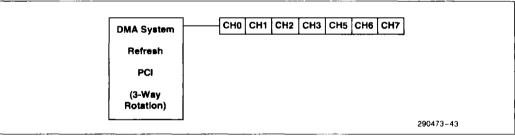

The ISA Bus arbiter evaluates requests for the ISA Bus coming from several different sources. The DMA unit, the refresh counter, and the PCI Bus (primarily the Host CPU) may all request access to the ISA Bus. Additionally, 16-bit ISA masters may request the bus through a cascaded DMA channel.

The SIO ISA arbiter uses a three-way rotating priority arbitration method. At each level, the devices which are considered equal are given a rotating priority. On a fully loaded bus, the order in which the devices are granted bus access is independent of the order in which they assert a bus request. This is because devices are serviced based on their position in the rotation. The arbitration scheme assures that DMA channels access the bus with minimal latency.

Figure 8. ISA Arbiter with DMA in Fixed Priority

Figure 9. ISA Arbiter with DMA in Rotating Priority

# 5.4.3.1 Channel Priority

For priority resolution the DMA consists of two logical channel groups: channels 0-3 and channels 4-7 (see Figure 7). Each group may be in either fixed or rotate mode, as determined by the DMA Command Register.

For prioritization purposes, the source of the DMA request is transparent. DMA I/O slaves normally assert their DREQ line to arbitrate for DMA service. However, a software request for DMA service can be presented through each channel's DMA Request

Register. A software request is subject to the same prioritization as any hardware request. Please see the detailed register description in Section 4.2.4 for Request Register programming information.

# **Fixed Priority**

The initial fixed priority structure is as follows:

**Table 14. Initial Fixed Priority Structure**

| High Priority Low Priority |

|----------------------------|

| (0, 1, 2, 3), 5, 6, 7      |

# 82378 SYSTEM I/O (SIO)

The fixed priority ordering is 0, 1, 2, 3, 5, 6, and 7. In this scheme, Channel 0 has the highest priority, and channel 7 has the lowest priority. Channels [3:0] of DMA-1 assume the priority position of Channel 4 in DMA-2, thus taking priority over channels 5, 6, and 7.

# **Rotating Priority**

Rotation allows for "fairness" in priority resolution. The priority chain rotates so that the last channel serviced is assigned the lowest priority in the channel group (0-3, 5-7).

Channels 0-3 rotate as a group of 4. They are always placed between Channel 5 and Channel 7 in the priority list.

Channel 5-7 rotate as part of a group of 4. That is, channels (5-7) form the first three positions in the rotation, while channel group (0-3) comprises the fourth position in the arbitration.

Table 15 demonstrates rotation priority.

Table 15. Rotating Priority Example

| Programmed Mode                 | Action                       | Priority<br>HighLow   |

|---------------------------------|------------------------------|-----------------------|

| Group (0−3) is in Rotation Mode | 1) Initial Setting           | (0, 1, 2, 3), 5, 6, 7 |

| Group (4-7) is in Fixed Mode    | 2) After Servicing Channel 2 | (3, 0, 1, 2), 5, 6, 7 |

|                                 | 3) After Servicing Channel 3 | (0, 1, 2, 3), 5, 6, 7 |

| Group (0−3) is in Rotation Mode | 1) Initial Setting           | (0, 1, 2, 3), 5, 6, 7 |

| Group (4-7) is in Rotation Mode | 2) After Servicing Channel 0 | 5, 6, 7, (1, 2, 3, 0) |

|                                 | 3) After Servicing Channel 5 | 6, 7, (1, 2, 3, 0), 5 |

|                                 | 4) After servicing Channel 6 | 7, (1, 2, 3, 0), 5, 6 |

|                                 | 5) After servicing Channel 7 | (1, 2, 3, 0), 5, 6, 7 |

# NOTE:

The first servicing of channel 0 caused double rotation.

# 5.4.3.2 DMA Preemption In Performance Timing Modes

A DMA slave device that is not programmed for compatible timing will be preempted from the bus by another device that requests use of the bus. This will occur, regardless of the priority of the pending request. For DMA devices not using compatible timing mode, the DMA controller stops the DMA transfer and releases the bus within 32 BCLK (4  $\mu$ s) of a preemption. Upon the expiration of the 4  $\mu$ s timer, the DACK will be inactivated after the current DMA cycle has completed. The bus will then be arbitrated for and granted to the highest priority requester. This feature allows flexibility in programming the DMA for long transfer sequences in a performance timing mode while guaranteeing that vital system services such as refresh are allowed access to the ISA Bus.

The 4 µs timer is not used in compatible timing mode. It is only used for DMA channels programmed for Type "A", Type "B", or Type "F" timing. It is also not used for 16-bit ISA masters cascaded through the DMA DREQ lines.

If the DMA channel that was preempted by the 4  $\mu s$  timer was operating in Block Mode, an internal bit will be set so that the channel will be arbitrated for again, independent of the state of DREQ.

# 5.4.3.3. Arbitration during Non-Maskable Interrupts

If a non-maskable interrupt (NMI) is pending, and the CPU is requesting the bus, then the DMA controller will be bypassed each time it comes up for rotation. This will give the CPU the bus bandwidth it requires to process the interrupt as fast as possible.

# 5.4.3.4 Programmable Guaranteed Access Time Mode (GAT Mode)

The PCI Arbiter Register contains a bit for configuring the SIO in "Guaranteed Access Time Mode" (GAT Mode). This mode guarantees that the 2.5  $\mu$ s CHRDY time-out specification for ISA masters running cycles to PCI will not be exceeded. When an

ISA master or DMA slave arbitrates for the ISA Bus, and the SIO is configured in Guaranteed Access Time Mode, the MEMREQ# pin will be asserted by the PCI arbiter in order to gain ownership of main memory. The arbitration for the PCI and then the main memory bus must be completed prior to granting the DACK# to the ISA master or DMA slave. A MEMACK# signal to the SIO indicates that the SIO now owns main memory and can grant the DACK# to the ISA master or DMA slave. A detailed description is contained in Section 5.2.3.2.

## **5.4.4 REGISTER FUNCTIONALITY**

Please see Section 4.2 for detailed information on register programming, bit definitions, and default values/functions of the DMA registers after a PCIRST#.

DMA Channel 4 is used to cascade the two DMA controllers together and should not be programmed for any mode other than cascade. The DMA Channel Mode Register for channel 4 will default to cascade mode. Special attention should also be take when programming the Command and Mask Registers as related to channel 4.

## 5.4.4.1 Address Compatibility Mode

Whenever the DMA is operating in address compatibility mode, the addresses do not increment or decrement through the High and Low Page Registers, and the High Page Register is set to 00h. This is compatible with the 82C37 and Low Page Register implementation used in the PC/AT. This mode is set when any of the lower three address bytes of a channel are programmed. If the upper byte of a channel's address is programmed last, the channel will go into extended address mode. In this mode, the high byte may be any value and the address will increment or decrement through the entire 32-bit address.

After PCIRST# is negated, all channels will be set to address compatibility mode. The DMA Master Clear command will also reset the proper channels to address compatibility mode.

# 5.4.4.2 Summary of DMA Transfer Sizes

Table 16 lists each of the DMA device transfer sizes. The column labeled "Current Byte/Word Count Register" indicates that the register contents represents either the number of bytes to transfer or the number of 16-bit words to transfer. The column labeled "Current Address Increment/Decrement" indicates the number added to or taken from the Current Address register after each DMA transfer cycle. The DMA Channel Mode Register determines if the Current Address Register will be incremented or decremented.

# 5.4.4.3 Address Shifting when Programmed for 16-Bit I/O Count by Words

To maintain compatibility with the implementation of the DMA in the PC/AT which used the 82C37, the DMA will shift the addresses when the DMA Channel Extended Mode Register is programmed for, or defaulted to, transfers to/from a 16-bit device countby-words. Note that the least significant bit of the Low Page Register is dropped in 16-bit shifted mode. When programming the Current Address Register when the DMA channel is in this mode, the Current Address must be programmed to an even address with the address value shifted right by one bit. The address shifting is shown in Table 17.

## 5.4.4.4 Autoinitialize

By programming a bit in the DMA Channel Mode Register, a channel may be set up as an autoinitialize channel. During Autoinitialize initialization, the original values of the Current Page, Current Address and Current Byte/Word Count Registers are automatically restored from the Base Page, Address, and Byte/Word Count Registers of that channel following TC. The Base Registers are loaded simultaneously with the Current Registers by the microprocessor and remain unchanged throughout the DMA service. The mask bit is not set when the channel is in autoinitialize. Following Autoinitialize, the channel is ready to perform another DMA service, without CPU intervention, as soon as a valid DREQ is detected.

Table 16. DMA Transfer Size

| DMA Device Date Size and Word Count          | Current Byte/Word<br>Count Register | Current Address<br>Increment/Decrement |

|----------------------------------------------|-------------------------------------|----------------------------------------|

| 8-Bit I/O, Count by Bytes                    | Bytes                               | 1                                      |

| 16-Bit I/O, Count by Words (Address Shifted) | Words                               | 1                                      |

| 16-Bit I/O, Count by Bytes                   | Bytes                               | 2                                      |

Table 17. Address Shifting in 16-Bit I/O DMA Transfers

| Output Address | 8-Bit I/O Programmed<br>Address |          |          |

|----------------|---------------------------------|----------|----------|

| <b>A</b> 0     | A0                              | 0        | A0       |

| A[16:1]        | A[16:1]                         | A[15:0]  | A[16:1]  |

| A[31:17]       | A[31:17]                        | A[31:17] | A[31:17] |

#### NOTE:

The least significant bit of the Low Page Register is dropped in 16-bit shifted mode.

# **5.4.5 SOFTWARE COMMANDS**

There are three additional special software commands which can be executed by the DMA controller. The three software commands are:

- 1. Clear Byte Pointer Flip-Flop

- 2. Master Clear

- Clear Mask Register

They do not depend on any specific bit pattern on the data bus.

# 5.4.5.1 Clear Byte Pointer Flip-Flop

This command is executed prior to writing or reading new address or word count information to/from the DMA controller. This initializes the flip-flop to a known state so that subsequent accesses to register contents by the microprocessor will address upper and lower bytes in the correct sequence.

When the Host CPU is reading or writing DMA registers, two Byte Pointer Flip-Flops are used; one for channels 0–3 and one for channels 4–7. Both of these act independently. There are separate software commands for clearing each of them (0Ch for channels 0–3, 0D8h for channels 4–7).

## 5.4.5.2 DMA Master Clear

This software instruction has the same effect as the hardware reset. The Command, Status, Request, and Internal First/Last Flip-Flop Registers are

cleared and the Mask Register is set. The DMA controller will enter the idle cycle.

There are two independent master clear commands, 0Dh which acts on channels 0-3, and 0DAh which acts on channels 4-7.

## 5.4.5.3 Clear Mask Register

This command clears the mask bits of all four channels, enabling them to accept DMA requests. I/O port 00Eh is used for channels 0-3 and I/O port 0DCh is used for channels 4-7.

#### 5.4.6 TERMINAL COUNT/EOP SUMMARY

This is a summary of the events that will happen as a result of a terminal count or external EOP when running DMA in various modes. (See Table 18.)

## 5.4.7 ISA REFRESH CYCLES

Refresh cycles are generated by two sources: the refresh controller inside the SIO component or by ISA bus masters other than the SIO. The ISA bus controller will enable the address lines SA[15:0] so that when MEMR# goes active, the entire ISA system memory is refreshed at one time. Memory slaves on the ISA Bus must not drive any data onto the data bus during the refresh cycle.

Counter 1 in the timer register set should be programmed to provide a request for refresh about every 15  $\mu$ s.

Table 18, Terminal Count/EOP Summary Table

| Conditions<br>AUTOINIT |     | No       |      | Yes      |

|------------------------|-----|----------|------|----------|

| Event                  |     |          |      |          |

| Word Counter Expired   | Yes | X        | Yes  | ×        |

| EOP Input              | X   | Asserted | Х    | Asserted |

| Result                 |     |          |      |          |

| Status TC              | set | set      | set  | set      |

| Mask                   | set | set      |      | _        |

| SW Request             | clr | clr      | clr  | clr      |

| Current Register       |     |          | load | load     |

# NOTES:

load load current from base

no changeX don't careclear

# 5.4.8 SCATTER/GATHER DESCRIPTION

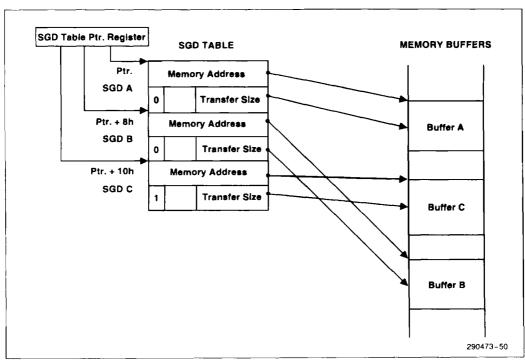

Scatter/Gather (S/G) provides the capability of transferring multiple buffers between memory and I/O without CPU intervention. In Scatter/Gather, the DMA can read the memory address and word count from an array of buffer descriptors, located in system memory (ISA or PCI), called the Scatter/Gather Descriptor (SGD) Table. This allows the DMA controller to sustain DMA transfers until all of the buffers in the SGD Table are transferred.

The S/G Command and Status Registers are used to control the operational aspect of S/G transfers. The SGD Table Pointer Register holds the address of the next buffer descriptor in the SGD Table.

The next buffer descriptor is fetched from the SGD Table by a DMA read transfer. DACK# will not be asserted for this transfer because the IO device is the SIO itself. The SIO will fetch the next buffer descriptor from either PCI memory or ISA memory, depending on where the SGD Table is located. If the SGD table is located in PCI memory, the memory read will use the line buffer to temporarily store the PCI read before loading it into the DMA S/G registers. The line buffer mode (8 byte or single transaction) for the S/G fetch operation will be the same as what is set for all DMA operations. If set in 8 byte mode, the SGD Table fetches will be PCI burst memory reads. The SGD Table PCI cycle fetches are subject to all types of PCI cycle termination (retry, disconnect, target-abort, master-abort). The fetched SGD Table data is subject to normal line buffer coherency management and invalidation. EOP will be asserted at the end of the complete link transfer.

To initiate a typical DMA Scatter/Gather transfer between memory and an I/O device, the following steps are required:

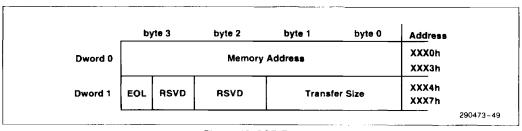

Software prepares a SGD Table in system memory. Each SGD is 8 bytes long and consists of an address pointer to the starting address and the transfer count of the memory buffer to be transferred. In any given SGD Table, two consecutive SGDs are offset by 8 bytes and are aligned on a 4-byte boundary.

Each Scatter/Gather Descriptor for the linked list contains the following information:

| <ul> <li>a. Memory Address (b)</li> </ul> | uffer start) |

|-------------------------------------------|--------------|

|-------------------------------------------|--------------|

4 bytes 2 bytes

b. Transfer Size (buffer size)

1 bit ( MSB)

- c. End of Link List

- d DMA Chan-

- Initialize the DMA Channel Mode and DMA Channel Extended Mode Registers with transfer specific information like 8-/16-bit I/O device, Transfer Mode, Transfer Type, etc.

- Software provides the starting address of the SGD Table by loading the SGD Table Pointer Register.

- Engage the Scatter/Gather function by writing a Start command to the S/G Command Register.

- The Mask register should be cleared as the last step of programming the DMA register set. This is to prevent the DMA from starting a transfer with a partially loaded command description.

- Once the register set is loaded and the channel is unmasked, the DMA will generate an internal request to fetch the first buffer from the SGD Table.

Figure 10. SGD Format

After the above steps are finished, the DMA will then respond to DREQ or software requests. The first transfer from the first buffer moves the memory address and word count from the Base register set to the Current register set. As long as S/G is active and the Base register set is not loaded and the last buffer has not been fetched, the channel will generate a request to fetch a reserve buffer into the Base register set. The reserve buffer is loaded to minimize latency problems going from one buffer to another. Fetching a reserve buffer has a lower priority than completing DMA transfers for the channel.

The DMA controller will terminate a Scatter/Gather cycle by detecting an End of List (EOL) bit in the SGD Table. After the EOL bit is detected, the channel transfers the buffers in the Base and Current register sets, if they are loaded. At terminal count the channel asserts EOP or IRQ13, depending on its programming and set the terminate bit in the S/G Status Register. If the channel asserted IRQ13, then the appropriate bit is set in the S/G Interrupt Status Register. The active bit in the S/G Status Register will be reset and the channel's Mask bit will be set.

# 5.5 Address Decoding

The SIO contains two address decoders; one to decode PCI master cycles and one to decode DMA/ISA master cycles. Two decoders are required to support the PCI and ISA Buses running concurrently. The PCI address decoder decodes the address from the multiplexed PCI address/data bus. The DMA/ISA master address decoder decodes the address from the ISA address bus for DMA and ISA master cycles. The address decoders determine how the cycle is handled.

#### 5.5.1 PCI ADDRESS DECODER

PCI address decoding is always a function of AD[31:2]. The information contained in the two low order bits (AD[1:0]) varies for memory, I/O, and configuration cycles.

Figure 11. Link List Example

# 82378 SYSTEM I/O (SIO)

For I/O cycles, AD[31:0] are all decoded to provide a byte address. The byte enables determine which byte lanes contain valid data. The SIO requires that PCI accesses to byte-wide internal registers must assert only one byte enable.

For memory cycles, accesses are decoded as Dword accesses. This means that AD[1:0] are ignored for decoding memory cycles. The byte enables are used only to determine which byte lanes contain valid data.

For configuration cycles, DEVSEL# is a function of IDSEL# and AD[1:0]. DEVSEL# is generated only when AD[1:0] are both zero. If either AD[1:0] are non-zero, the cycle is ignored by the SIO. Individual bytes of a configuration register can be accessed with the byte enables. A particular configuration register is selected using AD[7:2]. Again, the byte enables determine which byte lanes contain valid data.

All PCI cycles decoded in one of the following ways result in the SIO generating DEVSEL#. The PCI master cycle decoder decodes the following addresses based on the settings of the relevant configuration registers:

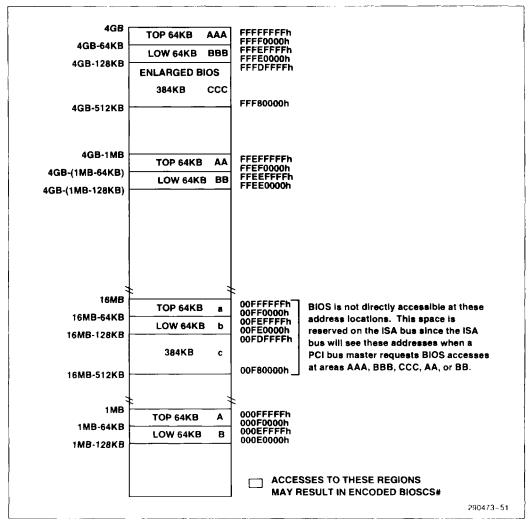

SIO I/O Addresses: Positively decodes I/O addresses for registers contained within the SIO (exceptions: 60h, 92h, 3F2h, 372h, and F0h).

**BIOS Memory Space:** Positively decodes BIOS memory space.

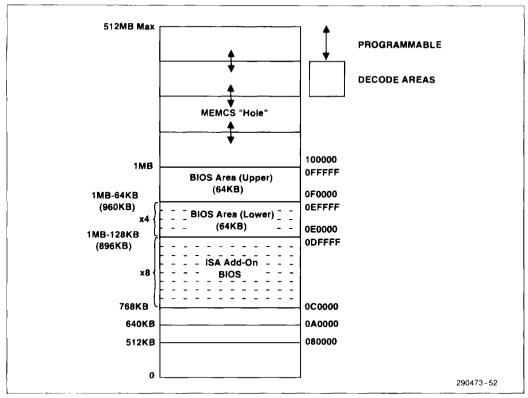

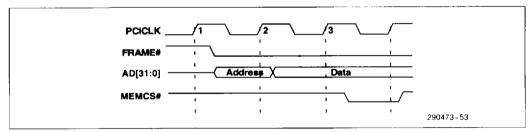

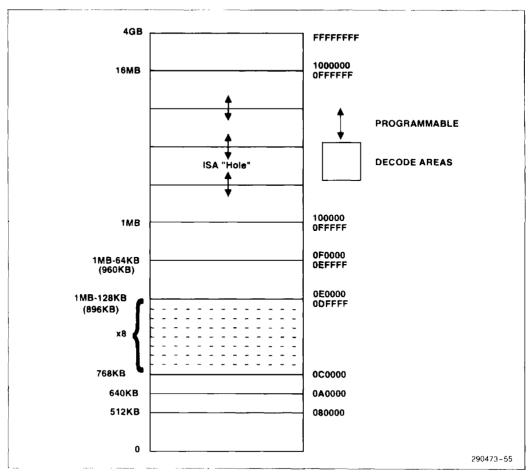

MEMCS\* Address Decoding: Decodes memory addresses that reside on the other side of the Host bridge and generates the MEMCS\* signal. (SIO does not generate DEVSEL\* in this case). The address range(s) used for this decoding is selected via the MEMCSCON, MEMCSBOH, MEMCSTOH, MEMCSTOH, MEMCSTOM, MAR1, MAR2, and MAR3 Registers (see Section 4.1).

Subtractively Decoding Cycles to ISA: Subtractively decodes cycles to the ISA Bus. Accesses to registers 60h, 92h, 3F2h, 372h, and F0h are also subtractively decoded to the ISA Bus.

One of the PCI requirements is that, upon power-up, PCI agents do not respond to any address. Typically, the only access to a PCI agent is through the IDSEL configuration mechanism until it is enabled through configuration. The SIO is an exception to this, since it controls access to the BIOS boot code. All addresses decoded by the PCI address decoder, that are enabled after chip reset, are accessible immediately after power-up.

#### 5.5.1.1 SIO I/O Addresses

These addresses are the internal, non-configuration SIO register locations and are shown in the SIO Address Decoding Table, Table 19. These addresses are fixed. Note that the Configuration Registers, listed in Table 3, are accessed with PCI configuration cycles as described in Section 5.1.2.5

In general, PCI accesses to the internal SIO registers will not be broadcast to the ISA Bus. However, PCI accesses to addresses 70h, 60h, 92h, 3F2h, 372h, and F0h are exceptions. Read and write accesses to these SIO locations are broadcast onto the ISA Bus. PCI master accesses to SIO registers will be retried if the ISA Bus is owned by an ISA master or the DMA controller. All of the registers are 8 bit registers. Accesses to these registers must be 8 bit accesses. Target-abort is issued by the SIO when the internal SIO non-configuration registers are the target of a PCI master I/O cycle and more than one byte enable is active. Refer to Table 19 for the SIO Address Decoding Map.

Accesses to the BIOS Timer Register (78h–7Bh) are broadcast to the ISA bus only if this register is disabled. If this register is enabled, the cycle is not broadcast to the ISA bus.

The address decoding logic includes the read/write cycle type. For example, read cycles to write only registers are not positively decoded and get forwarded to the ISA bus via subtractive decoding.

Table 19. SIO Address Decoding

| Address  | ress |      |      | Type | Name                                         | Block                                  |         |

|----------|------|------|------|------|----------------------------------------------|----------------------------------------|---------|

| Addiess  | FEDC | BA98 | 7654 | 3210 | 1,400                                        | Hame                                   | DIOUR   |

| 0000h    | 0000 | 0000 | 000x | 0000 | r/w                                          | DMA1 CH0 Base and Current Address      | DMA     |

| 0001h    | 0000 | 0000 | 000x | 0001 | r/w                                          | DMA1 CH0 Base and Current Count        | DMA     |

| 0002h    | 0000 | 0000 | 000x | 0010 | r/w                                          | DMA1 CH1 Base and Current Address      | DMA     |

| 0003h    | 0000 | 0000 | 000x | 0011 | r/w                                          | DMA1 CH1 Base and Current Count        | DMA     |

| 0004h    | 0000 | 0000 | 000x | 0100 | r/w                                          | DMA1 CH2 Base and Current Address      | DMA     |

| 0005h    | 0000 | 0000 | 000x | 0101 | r/w                                          | DMA1 CH2 Base and Current Count        | DMA     |

| 0006h    | 0000 | 0000 | 000x | 0110 | r/w                                          | DMA1 CH3 Base and Current Address      | DMA     |

| 0007h    | 0000 | 0000 | 000x | 0111 | r/w                                          | DMA1 CH3 Base and Current Count        | DMA     |

| 0008h    | 0000 | 0000 | 000x | 1000 | r/w                                          | DMA1 Status(r) Command(w) Register     | DMA     |

| 0009h    | 0000 | 0000 | 000x | 1001 | wo                                           | DMA1 Write Request Register            | DMA     |

| 000Ah    | 0000 | 0000 | 000x | 1010 | wo                                           | DMA1 Write Single Mask Bit             | DMA     |

| 000Bh    | 0000 | 0000 | 000x | 1011 | wo                                           | DMA1 Write Mode Register               | DMA     |

| 000Ch    | 0000 | 0000 | 000x | 1100 | wo                                           | DMA1 Clear Byte Pointer                | DMA     |

| 000Dh    | 0000 | 0000 | 000x | 1101 | wo                                           | DMA1 Master Clear                      | DMA     |

| 000Eh    | 0000 | 0000 | 000x | 1110 | wo                                           | DMA1 Clear Mask Register               | DMA     |

| 000Fh    | 0000 | 0000 | 000x | 1111 | r/w                                          | DMA1 Read/Write All Mask Register Bits | DMA     |

| 0020h    | 0000 | 0000 | 001x | xx00 | r/w                                          | INT 1 Control Register                 | PIC     |

| 0021h    | 0000 | 0000 | 001x | xx01 | r/w                                          | INT 1 Mask Register                    | PIC     |

| 0040h    | 0000 | 0000 | 010x | 0000 | r/w                                          | Timer Counter 1—Counter 0 Count        | TC      |

| 0041h    | 0000 | 0000 | 010x | 0001 | r/w                                          | Timer Counter 1—Counter 1 Count        | TC      |

| 0042h    | 0000 | 0000 | 010x | 0010 | r/w                                          | Timer Counter 1—Counter 2 Count        | TC      |