# SP9462, SP9472, SP9463, SP9473 12-BIT DATA ACQUISITION SYSTEM

#### **FEATURES**

- Complete 12-Bit Data Acquisition System

- Guaranteed No Missing Codes over Temperature

- Three State Output

- 33 KHz or 50KHz Throughput Rate

- Selectable Gains of 1, 10 and 100

- Small Pin Grid Array Package

- Input Ranges Selectable for Unipolar or Bipolar Operation

#### **DESCRIPTION**

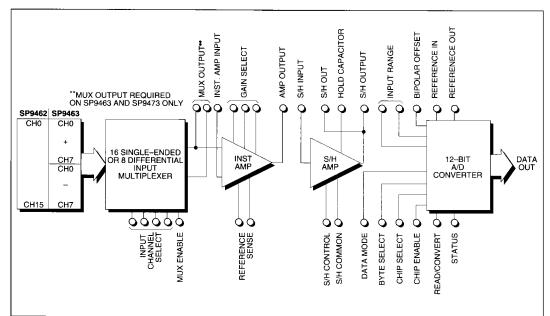

The SP9462/9472 and SP9463/9473 are complete data acquisition systems in a 68-pin grid array package. The SP9462/9472 include a 16-channel input multiplexer, selectable gain instrumentation amplifier, sample-and-hold amplifier, a single chip 12-Bit Analog to Digital Converter with 3-state output buffers. The SP9463/9473 are the 8 differential input

channel devices equivalent to the SP9462/9472. All models accept unipolar or bipolar voltage inputs of 0 to +10V, ±5V and ±10V. The instrumentation amplifier can be selected for gains of 1, 10 and 100 by pin-strapping pins. The SP9462/9472 and SP9463/9473 are available in two temperature ranges: 0 to +70°C, and -55 to +125°C, with MIL-STD-883C screening available.

11

## **SPECIFICATIONS**

At 25°C,  $V_{CC} = \pm 15V$ ,  $V_{DD} = 5V$ , external sample/hold capacitor at 4700pF. All grades are burned-in at +125°C for 168 hour.

| PARAMETERS                                                 | MIN.    | TYP.             | MAX.     | UNIT                   | CONDITIONS                 |

|------------------------------------------------------------|---------|------------------|----------|------------------------|----------------------------|

| RESOLUTION                                                 |         | 12               |          | BITS                   |                            |

| INPUT CHARACTERISTICS                                      |         |                  |          |                        |                            |

| ANALOG                                                     |         |                  |          |                        |                            |

| Voltage Ranges:                                            |         |                  |          |                        |                            |

| Bipolar                                                    |         | ±5, ±10          |          | V                      |                            |

| Unipolar                                                   |         | 0–10             |          | V                      |                            |

| Input impedence:                                           |         | 1010             |          |                        |                            |

| On Channel<br>Off Channel                                  |         | 10 <sup>10</sup> |          | Ω                      |                            |

| Input Capacitance:                                         |         | 10.0             |          | Ω                      |                            |

| On Channel                                                 |         | 20               |          | pF                     |                            |

| Off Channel                                                |         | 20               |          | pF                     |                            |

| CMRR <sup>7</sup>                                          | 80      | 85               | -80      | dB                     | (20VDC to 1KHz)            |

| Crosstalk <sup>7</sup>                                     |         | -85              | -80      | dB                     | (20VP-P. 1KHz)             |

| Feedthrough <sup>7</sup>                                   |         | -85              | 100      | dB                     | (at 1KHz)                  |

| Offset <sup>2</sup>                                        |         | 30               | 5        | μ∨                     | (channel to channel) G=1   |

| Input Bias Current/Channel                                 |         | 1                |          | nA                     |                            |

| Input Voltage Range <sup>3</sup>                           | +10     | +11              |          | \ \ \                  |                            |

| DIGITAL                                                    | -10     | -15              |          | V                      |                            |

| DIGITAL                                                    |         |                  |          |                        |                            |

| MUX Input Channel Select:<br>Logic '1' (4V)                |         | _                | 20       |                        |                            |

| Logic 1 (4V)<br>Logic '0' (0.8V)                           |         | 5<br>5           | 30<br>30 | μΑ                     |                            |

| S/H Command:                                               |         | 5                | 30       | μΑ                     |                            |

| Logic '1' (2.4V)                                           |         | 0.2              |          | nA                     |                            |

| Logic '0' (0.8V)                                           |         | 5                | 30       | μA                     |                            |

| ADC Section:                                               |         |                  |          | μ, ,                   |                            |

| Logic '1' (2.4V)                                           |         |                  | 10       | μА                     |                            |

| Logic '0' (0.8V)                                           |         | 10               |          | μA                     |                            |

| TRANSFER CHARACTERISTICS                                   |         |                  |          |                        |                            |

| ACCURACY                                                   |         |                  |          |                        |                            |

| Integral of Linearity <sup>4</sup> :                       |         |                  |          |                        |                            |

| JH, SH                                                     |         |                  | ±0.024   | %FSR                   |                            |

| KH, TH                                                     |         |                  | ±0.012   | %FSR                   |                            |

| Differential Linearity <sup>4</sup> :                      |         |                  |          |                        |                            |

| JH, SH                                                     |         |                  | ±0.024   | %FSR                   |                            |

| KH, TH<br>Gain Error <sup>5</sup>                          |         |                  | ±0.012   | %FSR                   |                            |

| Gain Error                                                 |         | 0.7              |          | %                      |                            |

| G=100                                                      |         | 0.7              |          | %<br>%                 |                            |

| Unipolar Offset Error <sup>5</sup>                         |         | 16               |          | m√v                    |                            |

| Bipolar Offset Error <sup>5</sup>                          |         | 50               |          | mV                     |                            |

| Noise Error <sup>7</sup>                                   |         | 0.5              | 1        | mV P-P                 | (Measured at S/H Output) G |

| Droop Rate <sup>7</sup>                                    |         | 50               | 500      | μV/mS                  |                            |

| Temperature Coefficients:                                  |         |                  |          |                        |                            |

| Unipolar Offset                                            |         |                  |          |                        |                            |

| JH, SH                                                     |         | 20               | ppm      | of FSR/°C              |                            |

| KH, TH                                                     |         | 15               | ppm      | of FSR/°C              |                            |

| Bipolar Offset                                             |         | 20               |          | of ECD (SC             |                            |

| JH, SH<br>KH, TH                                           |         | 30<br>25         |          | of FSR/°C<br>of FSR/°C |                            |

| Full Scale Calibration                                     |         | 20               | ppm      | i Oi FOR/°C            |                            |

| JH, SH                                                     | 1       | 60               | nnm      | <br>  of FSR/°C        |                            |

|                                                            |         | 35               | maa      | of FSR/°C              |                            |

| KH, TH                                                     |         |                  | 1-1-11   | 1 2 2 4 7 2            |                            |

| KH, TH                                                     |         |                  |          |                        |                            |

| KH, TH<br>SYSTEM TIMINGS                                   |         |                  |          |                        |                            |

| KH, TH                                                     | 15      | 20               | 25       | uS                     |                            |

| KH, TH  SYSTEM TIMINGS  ADC Conversion Time:               | 15<br>9 | 20<br>12         | 25<br>15 | μS<br>μS               |                            |

| KH, TH  SYSTEM TIMINGS  ADC Conversion Time: SP9462/SP9463 |         |                  |          | μS<br>μS<br>ns         |                            |

| PARAMETERS                 | MIN.           | TYP.        | MAX.       | UNIT  | CONDITIONS          |

|----------------------------|----------------|-------------|------------|-------|---------------------|

| TIMING                     | _              |             |            |       |                     |

| Acquisition Time:          |                |             |            |       |                     |

| (to 0.01% of final value   |                |             |            |       |                     |

| for full-scale step)       |                | 5           |            | μS    |                     |

| Throughput:                |                | _           |            | "     |                     |

| (Serial Mode)              |                |             |            |       |                     |

| SP9462/SP94637             |                |             | 22         | KHz   |                     |

| SP9472/SP9473 <sup>7</sup> |                |             | 22.8       | KHz   |                     |

| (Overlap Mode)             |                |             |            |       |                     |

| SP9462/SP9463 <sup>7</sup> |                |             | 31.7       | KHz   |                     |

| SP9472/SP9473 <sup>7</sup> |                | ]           | 46.5       | KHz   |                     |

| MULTIPLEXER <sup>6</sup>   |                |             |            |       |                     |

| Switching Time             |                | 1.5         |            | μS    | (between channels)  |

| Settling Time              |                | 2.5         |            | μS    | (10V step to 0.02%) |

| Enable Time:               |                |             |            |       | (,                  |

| On <sup>7</sup>            |                | 1           | 2          | μS    |                     |

| Off <sup>7</sup>           |                | 0.25        | 0.5        | μS    |                     |

| INSTRUMENTATION AMPLIFIE   | R <sup>6</sup> |             |            | -     |                     |

| Settling Time:             |                |             |            |       | (20V step to 0.01%) |

| G=1 <sup>7</sup>           |                | 5           | 12.5       | μS    | (2010)              |

| G=10 <sup>7</sup>          |                | 3           | 7.5        | μS    |                     |

| G=100 <sup>7</sup>         |                | 4           | 7.5        | μS    |                     |

| Slew Rate <sup>7</sup>     | 12             | 17          |            | V/μS  |                     |

| S/H AMPLIFIER              |                |             |            |       |                     |

| Acquisition Time           |                | 5           |            | μS    | (10V step to 0.01%) |

| Aperture Delay             |                | 50          |            | ns    | (101010)            |

| Hold mode settling time    |                | 1.5         |            | μS    |                     |

| Slew rate                  |                | 10          |            | V/μS  |                     |

| DIGITAL OUTPUT DATA        |                |             |            |       |                     |

| Output Codes:              |                |             |            |       |                     |

| Unipolar                   | Unip           | olar Straid | aht Binary | (USB) |                     |

| Bipolar                    |                |             | Binary (BC |       |                     |

| Logic Levels:              |                |             |            |       |                     |

| Logic 0                    |                |             | +0.4       | V     | sink = 1.6mA        |

| Logic 1                    | +2.4           |             |            | V     | source = 500µA      |

| Leakage (Data Bits Only)   | -5             | +0.1        | +5         | μА    | High–Z State        |

| POWER SUPPLY REQUIREMEN    | TS             |             |            |       |                     |

| Rated Voltage:             |                |             |            |       |                     |

| Analog                     | 14.25          | 15          | 15.75      | VDC   | ±V <sub>cc</sub>    |

| Digital                    | 4.75           | 5           | 5.25       | VDC   | V <sub>DD</sub>     |

| Supply Drain:              |                |             |            | _     |                     |

| +15V                       |                | 20          | 27         | mA    |                     |

| -15V                       |                | 10          | 18         | mA    |                     |

| +5V                        |                | 10          | 14         | mA    |                     |

| Power Dissipation          |                | 500         | 750        | mW    |                     |

| TEMPERATURE RANGE          |                |             |            |       |                     |

| Operating Temperature Rai  | nge:           |             |            |       |                     |

| JH, SH                     | ا ً 0          |             | 70         | °C    |                     |

| SH, TH                     | -55<br>-65     |             | +125       | °C    |                     |

| Storage Temp. Range        |                |             | +150       | °C    |                     |

NOTES: (1) Measured at the sample-and-hold output. (2) Measured with all input channels grounded. (3) The range of voltage on any input with respect to common over which accuracy and leakage current is guaranteed. (4) Applicable over full temperature range. NO MISSING CODES GUARANTEED OVER TEMPERATURE RANGE. (5) Adjustable to zero using external potentiometer or select-on-test resistor. (6) Specifications are at +25°C and measured at 50% level of transition. (7) Parameter guaranteed but not tested.

| ABSOLUTE MAXIMUM RATINGS               |                                                              |

|----------------------------------------|--------------------------------------------------------------|

| +V <sub>cc</sub> to A COM0.5V to +16V  | Analog Input Signal Range $(+V_{cc}+20V)$ to $(-V_{cc}-20V)$ |

| -V <sub>cc</sub> to A COM+0.5V to -16V | Digital Input Signal0.5V to +V <sub>DD</sub>                 |

| +V <sub>DD</sub> to D COM0.5V to +5.5V | A COM to D COM±1V                                            |

# OPERATING INSTRUCTIONS OPERATING MODES

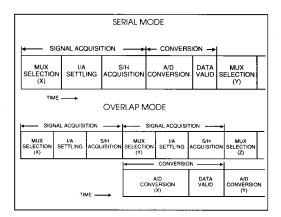

The DAS can operate in one of two modes. namely serial and overlap, as shown in Figure 1. In serial mode, control of the device is such that the multiplexer channel X is first selected. time is then allowed for the instrumentation amplifier to settle, the sample/hold amplifier is set to HOLD mode and finally a conversion is carried out. This procedure is then repeated for channel Y. Faster throughput can be obtained using overlap mode. While a conversion is being carried out by the ADC on avoltage from channel X held on the sample/ hold,channelYisselectedandthemultiplexer and instrumentation amplifier allowed to settle. In this way, the total throughput time is limited only by the sum of the sample/hold acquisition time and the ADC conversion time.

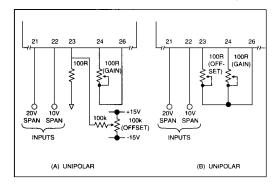

#### **CALIBRATION - UNIPOLAR**

If adjustment of unipolar is offset and gain are not required, then the gain set potentiometer in Figure 2a (Unipolar operation) may be replaced with a  $50\Omega$ , 1% metal film resistor, and the offset network replaced with a connection from pin 23 to ground.

### **CALIBRATION - BIPOLAR**

If adjustment of bipolar offset and gain are not required, then the gain set and offset potentiometers in Figure 2b (Bipolar operation) may both be replaced with  $50\Omega$ , 1% metal film resistors.

#### CALIBRATION - GENERAL

The input voltage ranges of the ADC are 0-10V,  $\pm 5V$  and  $\pm 10V$ . Calibration in all ranges is achieved by adjusting the offset

FIGURE 1. Operating Modes

and gain potentiometers (indicated in Figure 2a and b) such that the 000 to 001 code transition takes place at +1/2LSB from full-scale negative (-FS) and the FFE to FFF transition takes place at -3/ 2LSB from full-scale positive (+FS). The procedure is therefore to select the required range and apply the specified (-FS+1/2LSB) voltage to any selected input channel and adjust the offset potentiometer for the 000 to 001 transition. The (+FS-3/2LSB) voltage should then be applied to the same channel and the gain potentiometer adjusted for the FFE to FFF transition. The offset should always be made before the gain adjustment.

#### STAND-ALONE OPERATION

The stand-alone mode is used in systems containing dedicated input ports which do not require full bus interface capability.

Control of the converter is accomplished by a single control line connected to R/C. In this mode CS and BYTE SELECT are connected to LOW and CE and DATA MODE are connected to HIGH. The output data are presented as 12-bit words.

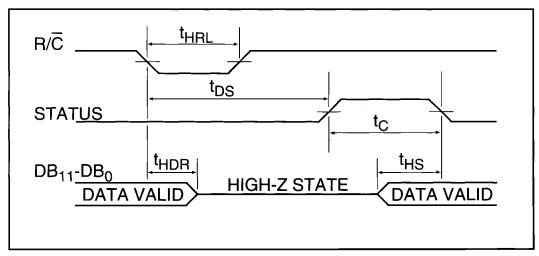

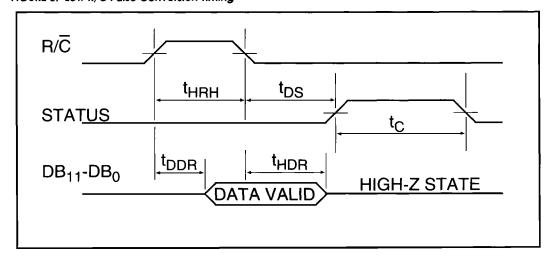

Conversion is initiated by a High-to-Low transition of R/C. The three-state data output buffers are enabled when R/C is high and STATUS is low. Thus, there are two possible modes of operation; conversion can be initiated with either positive or negative pulses. In each case the R/C pulse must remain low for a minimum of 50ns.

Figure 5 illustrates timing when conversion is initiated by an R/C pulse which goes

FIGURE 2. Calibration

low and returns to the high state during the conversion. In this case, the threestate outputs go to the high-impedance state in response to the falling edge of R/C and are enabled for external access of the data after completion of the conversion. Figure 6 illustrates the timina when conversion is initiated by a positive R/C pulse. In this mode the output data from the previous conversion is enabled during the positive portion of R/C. A new conversion is started on the falling edge of R/C, and the three-state outputs return to the high impedance state until the next occurrence of a high R/C pulse. Table 1 lists timing specifications for stand-alone operation.

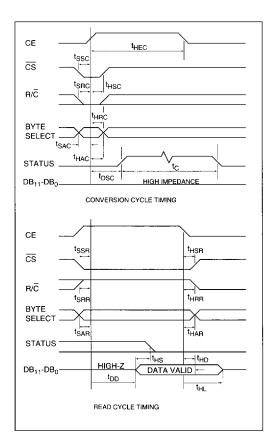

# FULLY CONTROLLED OPERATION Conversion Length

Conversion length (8-bit or 12-bit) is determined by the state of the BYTE SELECT input, which is latched upon receipt of a conversion start transition. BYTE SELECT is latched because it is also involved in enabling the output buffers. No other control inputs are latched. If BYTE SELECT is latched high, the conversion continues for 8-bits. The full 12-bit conversion will occur if BYTE SELECT is low. If all 12 bits are read following an 8-bit conversion, the 3LSB's (DB<sub>p</sub>-DB<sub>2</sub>) will be low (logic 0) and DB<sub>3</sub> will be high (logic 1).

#### Conversion Start

A conversion is initiated by a transition on any of three logic inputs (CE, CS and R/C) –refer to Figure 8. The last of the three to reach the required state start the conversion and thus all three may be dynamically controlled. If necessary, they may change state simultaneously,

| ١ | CE | CS | R/C | DATA | BYTE   | OPERATION                      |

|---|----|----|-----|------|--------|--------------------------------|

| l |    |    |     | MODE | SELECT |                                |

| I | 0  | X  | Х   | Х    | X      | NONE                           |

| ١ | Х  | ו  | х   | Х    | ×      | NONE                           |

| - | ₹  | 0  | 0   | х    | 0      | INITIATE 12-BIT CONVERSION     |

| Ì | Ŧ  | 0  | 0   | х    | ו (    | INITIATE 8-BIT CONVERSION      |

|   | 1  | Į  | 0   | X    | 0      | INITIATE 12-BIT CONVERSION     |

| 1 | 1  | Į  | 0   | X    | 1      | INITIATE 8-BIT CONVERSION      |

| 1 | 1  | ō  | Ŧ   | ×    | 0      | INITIATE 12-BIT CONVERSION     |

|   | 1  | 0  | Į   | Х    | 1      | INITIATE 8-BIT CONVERSION      |

|   | 1  | 0  | 1   | 1    | X      | ENABLE 12-BIT OUTPUT           |

|   | 1  | 0  | 1   | 0    | 0      | ENABLE 8 MSB's ONLY            |

|   | 1  | 0  | 1   | 0    | 1      | ENABLE 4 LSB's PLUS 4 TRAINING |

|   |    |    |     |      |        | ZEROS                          |

FIGURE 3. Control Input Truth Table

and the nominal delay time is independent of which input actually starts the conversion. If it is desired that a particular input establish the actual start of conversion, the other two should be stable a minimum of 50ns prior to the transition of that input. Timing relationships for start of conversion timing are illustrated in Conversion Cycle Timing of Digital Specifications.

The STATUS output indicates the state of the converter by being high only during a conversion. During this time the threestate buffers remain in a highimpedance state, and therefore, data is not valid. During this period additional transitions of the three control inputs will be ignored, so that conversion cannot be prematurely terminated or restarted. However, if BYTE SELECT chanes state after the beginning of conversion, any additional start conversion transition will latch the new state of BYTE SELECT, possibly resulting in an incorrect conversion length (8-bit versus 12-bits) for that conversion.

#### **READING OUTPUT DATA**

After a conversion is initiated, the output data buffers remain in a high-impedance state until the following four conditions are met: R/C high, STATUS low, CE high, and CS low. In this condition the data lines are enabled according to the state of the inputs DATA MODE and

|             |             |             |             |               |                     |             | _   |             |               |                             |

|-------------|-------------|-------------|-------------|---------------|---------------------|-------------|-----|-------------|---------------|-----------------------------|

|             |             | SP946       | 2/947       | 2             |                     |             | SP9 | 463/9       | 473           |                             |

| MUX<br>ADD3 | MUX<br>ADD2 | MUX<br>ADD1 | MUX<br>ADD0 | MUX<br>Enable | Channel<br>Selected | MUX<br>ADD2 |     | MUX<br>ADDO | MUX<br>Enable | Channel<br>Pair<br>Selected |

| X           | х           | Х           | Х           | L             | NONE                | Х           | х   | х           | L             | NONE                        |

| L           | L           | L           | L           | н             | 0                   | L           | L   | L           | L             | 0                           |

| lι          | L.          | L           | н           | н             | 1                   | L           | L   | н           | н             | 1                           |

| Ł           | L           | н           | Ł           | н             | 2                   | L           | н   | L           | н             | 2                           |

| l           | L           | н           | н           | н             | 3                   | L           | н   | н           | н             | 3                           |

| L           | н           | L           | L           | н             | 4                   | н           | L   | L           | Н             | 4                           |

| ι           | н           | L           | н           | н             | 5                   | н           | L   | н           | н             | 5                           |

| L           | н           | н           | L           | н             | 6                   | н           | н   | L           | н             | 6                           |

| ι           | н           | н           | н           | н             | 7                   | Н           | н   | н           | н             | 7                           |

| н           | L           | L           | L           | н             | 8                   | Ì           |     | -           |               |                             |

| н           | L           | L           | н           | н             | 9                   |             |     | -           |               |                             |

| н           | L           | н           | Ł           | Н             | 10                  |             | 1   | -           |               |                             |

| н           | L           | н           | н           | н             | 11                  |             |     | -           |               |                             |

| н           | н           | L           | L           | н             | 12                  | 1           |     | -           |               |                             |

| н           | н           | L           | н           | н             | 13                  | l           |     | -           | 1             |                             |

| н           | н           | н           | L           | н             | 14                  |             |     | -           |               |                             |

| н           | н           | н           | н           | Н             | 15                  |             |     | -           |               |                             |

FIGURE 4. Channel Select Truth Table

BYTE SELECT. See Read Cycle Timing for timing relationships and specification. In most applications the DATA MODE input will be hardwired in either the high or low condition, although it is fully TIL—and CMOS—compatible and may be actively driven if desired. When DATA MODE is high, all 12 outputs lines (DBO—DB11) are enabled simultaneously for full data word transfer to a 12—bit or 16—bit bus and the state of the BYTE SELECT is ignored.

When DATA MODE is low, the data is presented in the form of two 8-bit bytes, with the selection of each byte by the state of BYTE SELECT during the read cycle.

| PARAMETER <sup>7</sup>     | MIN                                                                                                                         | TYP                                                                                                                         | MAX                                                                                                                             | UN                                                                                                                                                                                                                                      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low R/C Pulse Width        | 50                                                                                                                          |                                                                                                                             |                                                                                                                                 | nS                                                                                                                                                                                                                                      |

| STS Delay from R/C .       |                                                                                                                             |                                                                                                                             | 200                                                                                                                             | nS                                                                                                                                                                                                                                      |

| Data Valid after R/C Low   | 25                                                                                                                          |                                                                                                                             |                                                                                                                                 | n\$                                                                                                                                                                                                                                     |

| STS Delay After Data Valid | 300                                                                                                                         | 500                                                                                                                         | 1000                                                                                                                            | nS                                                                                                                                                                                                                                      |

| 1                          | 100                                                                                                                         | 300                                                                                                                         | 600                                                                                                                             | nS                                                                                                                                                                                                                                      |

| High R/C Pulse Width       | 150                                                                                                                         |                                                                                                                             |                                                                                                                                 | nS                                                                                                                                                                                                                                      |

| Data Access Time           |                                                                                                                             |                                                                                                                             | 150                                                                                                                             | n\$                                                                                                                                                                                                                                     |

|                            | Low R/C Pulse Width<br>STS Delay from R/C<br>Data Valid after R/C Low<br>STS Delay After Data Valid<br>High R/C Pulse Width | Low R/C Pulse Width STS Delay from R/C Data Valid after R/C Low STS Delay After Data Valid 300 100 High R/C Pulse Width 150 | Low R/C Pulse Width STS Delay from R/C Data Valid after R/C Low STS Delay After Data Valid 300 500 100 300 High R/C Pulse Width | Low R/C Pulse Width       50         STS Delay from R/C       .         Data Valid after R/C Low       25         STS Delay After Data Valid       300       500         100       300       600         High R/C Pulse Width       150 |

The BYTE SELECT input is usually driven by the least significant bit of the address bus, allowing storage of the output data word in two consecutive memory locations.

When BYTE SELECT is low, the byte addressed contains the 8 MSBs. When BYTE SELECT is high, the byte addressed contains the 4 LSBs from the conversion

FIGURE 5. Low R/C Pulse Conversion Timina

FIGURE 6. High R/C Pulse Conversion Timing

followed by four zeros that have been forced by the control logic. The left-justified formats of the two 8-bit bytes are shown in Figure 7. The design of the DAS guarantees that the BYTE SELECT input may be toggled at any time without damage to the output buffers occuring.

In the majority of applications, the read operation will be attempted only after the conversion is complete and the status output has gone low. In those situations requiring the fastest possible access to

the data, the read may be started as much as (tpp max+tps max) before STATUS goes low. Refer to Read Cycle Timing for these timing relationships.

# GROUNDING, DECOUPLING AND LAYOUT CONSIDERATIONS

It should be noted that the multiplexer/instrumentation amplifier section and sample/hold plus ADC section of the DAS have separate power connections. This is to enable more flexible grounding

|           |      |      |     | WC  | RD 1 |     |     |     |     |     | W   | ORD | 2   |     |     |     |

|-----------|------|------|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PROCESSOR | DB7  | DB6  | DB5 | DB4 | DB3  | DB2 | DB1 | DB0 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| DAS       | DB11 | DB10 | DB9 | DB8 | DB7  | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | 0   | 0   | 0   | 0   |

|           |      |      |     |     |      |     |     |     |     |     |     |     |     |     |     |     |

FIGURE 7. 12-Bit Data Format for 8-Bit Systems.

| DIGITAL TIMING       |                                     |     |     |      | _     |

|----------------------|-------------------------------------|-----|-----|------|-------|

| SYMBOL               | PARAMETER <sup>7</sup>              | MIN | TYP | MAX  | UNITS |

| CONVERT MODE         |                                     |     |     |      |       |

| t <sub>DSC</sub>     | Status delay from CE                |     | 100 | 200  | nS    |

| † <sub>HEC</sub>     | CE Pulse width                      | 50  | 30  |      | nS    |

| t <sub>ssc</sub>     | CS to CE setup                      | 50  | 20  |      | nS    |

| t <sub>HSC</sub>     | CS low during CE high               | 50  | 20  |      | nS    |

| t <sub>src</sub>     | $R/\overline{C}$ to CE setup        | 50  | 0   |      | nS    |

| t <sub>HRC</sub>     | $R/\overline{C}$ low during CE high | 50  | 20  |      | n\$   |

| t <sub>sac</sub>     | Byte select to CE setup             | 0   | 0   |      | nS    |

| † <sub>HAC</sub>     | Byte selected valid during CE high  | 50  | 20  |      | nS    |

| t <sub>c</sub> 946X  | Conversion time:                    |     |     |      |       |

|                      | 12-bit cycle                        | 15  | 20  | 25   | μS    |

|                      | 8-bit cycle                         | 10  | 13  | 17   | μS    |

| t <sub>c</sub> 947X  | Conversion time:                    |     |     |      |       |

|                      | 12-bit cycle                        | 9   | 12  | 15   | μS    |

|                      | 8-bit cycle                         | 6   | 8   | 10   | μS    |

| READ MODE            |                                     |     |     |      |       |

| t <sub>pp</sub>      | Access time from CE                 |     | 75  | 150  | nS    |

| t <sub>HD</sub>      | Data valid after CE low             | 25  | 35  |      | nS    |

| t <sub>HL</sub>      | Output float delay                  |     | 100 | 150  | nS    |

| t <sub>ssr</sub>     | CS to CE setup                      | 50  | 0   |      | nS    |

| t <sub>srr</sub>     | R/C to CE setup                     | 0   | 0   |      | nS    |

| t <sub>SAR</sub>     | Byte select to Ce setup             | 50  | 25  |      | nS    |

| †                    | CS valid after CE low               | 0   | 0   |      | nS    |

| † <sub>HRR</sub>     | R/C high after CE low               | 0   | 0   |      | nS    |

| t <sub>HAR</sub>     | Byte select valid after CE low      | 50  | 25  |      | nS    |

| t <sub>HS</sub> 946X | Status delay after data valid       | 300 | 500 | 1000 | nS    |

| t <sub>HS</sub> 947X | Status delay after data valid       | 100 | 300 | 600  | n\$   |

techniques to be implemented as shown in Figure 8. It also facillitates the use of independent decoupling of the analog front–end power supply, and the ADC plus associated digital circuitry power supply if desired. In this way, a separately decoupled analog front–end can be made to be substantially more immune to power supply noise generated by the ADC circuitry than if the power supplies to the two sections were directly connected. This feature is important where low–level signals are in use or high input signal noise immunity is desired.

The output section has three grounds:

Pin 25 Analog Common, A/D

Converter

Pin 34 A/H Amp digital input reference Pin 19 Digital Common, A/D Converter

The input section has one ground:

Pin 53 Common for digital MUX inputs

and power supply decoupling.

| Compared to the control of the con

FIGURE 8. Recommended Decoupling of Power Supplies

All grounds have to be interconnected externally to the DAS, and it is recommended that all grounds are connected via one track to a single point as close as possible to the DAS. To check that the grounding structure is correct, the ground tracking should be sketched and a grounding "tree" should result whereby all grounds route to a central point.

In general, layout should be such that analog and digital tracks are sparated as much as possible with coupling between analog and digital lines minimized by careful layout. For instance, if the lines must cross they should do so at right angles to each other, Parallel analog and digital lines should be separated from each other by a pattern connected to common.

FIGURE 9. Conversion and Read Cycle Timing

| PIN DESIGNATION  | PIN NOS | DEFINITION                   | COMMENTS                                          |

|------------------|---------|------------------------------|---------------------------------------------------|

| STATUS           | 6       | Status of the A/D Conversion | This output is at logic '1' while the internal    |

|                  |         | ,                            | A/D converter is carrying out a conversion.       |

|                  |         |                              | This may be used to directly control the          |

|                  |         |                              | S/H amplifier.                                    |

| CE               | 28      | Chip Enable                  | This input must be at logic '1' to either         |

|                  |         | ,                            | initiate a conversion or read oputput data.       |

| CS               | 31      | Chip Select                  | This input must be at logic '0' to either         |

|                  |         | · ·                          | initiate a conversion or read output data.        |

| R/C              | 29      | Read/Convert                 | Data can be read when this pin is logic '1'       |

|                  |         | ·                            | or a conversion can be initiated when this        |

|                  |         |                              | pin is logic '0'. This pin is typically connected |

|                  |         |                              | to the R/W control line of a microprocessor-      |

|                  |         |                              | based system.                                     |

| DATA MODE        | 30      | Select 12 or 8 Bit Data      | When data mode is at logic '1' all 12             |

|                  |         |                              | output data bits are enabled simultaneously.      |

|                  |         |                              | When data mode is at logic '0' MSBs and           |

|                  |         |                              | LSBs are controlled by byte select (Pin 32).      |

| BYTE SELECT      | 32      | Byte Address, Short Cycle    | When reading output data, byte select at          |

|                  |         |                              | logic '0' enables the 8 MSBs. Byte select at      |

|                  |         |                              | logic '1' enables the 4 LSBs. The 4 LSBs can      |

|                  |         |                              | therefore be connected to four of the MSB         |

|                  |         |                              | lines for interconnection to an 8-bit bus. In     |

|                  |         |                              | start convert mode, logic '0' enables a 12 bit    |

|                  |         |                              | conversion while logic 1' will short cycle the    |

|                  |         |                              | conversion to 8 bits.                             |

| +15V(1), +15V(2) | 3,27    | Power Supply                 | Connect to +15V supply using decoupling           |

|                  |         |                              | as indicated in Figure 1.                         |

| -15V(1), -15V(2) | 4, 20   | Power Supply                 | Connect to -15V supply using decoupling           |

|                  |         |                              | as indicated in Figure 1.                         |

| A COM(2)         | 25      | Analog Common                | Analog common connection. Note that a             |

|                  |         |                              | common (including digital common) should          |

|                  |         |                              | be connected together at one point closesss       |

|                  |         |                              | to the device.                                    |

| D COM(1)         | 53      | Reference for MUX Logic      | Connect to digital Common.                        |

|                  |         | Control                      |                                                   |

| +5V              | 5       | Logic Power Supply           | Connect to +5V digital supply line with           |

|                  |         | Amplifier                    | decoupling as in Figure 1.                        |

| D COM(2)         | 19      | Reference for A/D Converter  | Connect to S/H common at one point                |

|                  |         | Control Lines                | close to the device.                              |

| NC               | 38      | No Internal Connection       |                                                   |

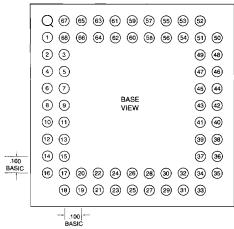

### **PIN ASSIGNMENTS**

| PIN FUNCTION  1                                                                                                                                                                                                                                                       |     |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| 2 Amp Ref 3 +15V(1) 4 -15V(1) 5 +5V 6 Status 7 D11 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15V(2) 21 ADC in (10V) 23 Bipolar Offset Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select | PIN | FUNCTION    |

| 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out +15V (2) 27 RC 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                   | . 1 | Amp Out     |

| 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out +15V (2) 27 RC 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                   | 2   | Amp Ref     |

| 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out +15V (2) 27 RC 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                   | 3   | +15V(1)     |

| 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out +15V (2) 27 RC 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                   | 4   | -15V(1)     |

| 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out +15V (2) 27 RC 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                   | 5   | +5V         |

| 8 D10 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out +15V (2) 27 RC 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                   | 6   | Status      |

| 9 D9 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15v (2) 21 ADC in (10v) 23 Bipolar Offset Ref In 25 ACOM (2) 26 Ref Out 27 +15v (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                         |     | DII         |

| 10 D8 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (10V) 23 Bipolar Offset Ref In 25 ACOM (2) Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                 | 8   | D10         |

| 11 D7 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref in 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                 |     | D9          |

| 12 D6 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15v (2) 21 ADC in (10V) 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15v (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                       | 10  | D8          |

| 13 D5 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                   |     | D7          |

| 14 D4 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                   |     | D6          |

| 15 D3 16 D2 17 D1 18 D0 19 ADC DCOM -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref in 25 ACOM (2) 26 Ref Out +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                               |     |             |

| 16 D2 17 D1 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset Ref in 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                  |     |             |

| 17 D1 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 27 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                     |     |             |

| 18 D0 19 ADC DCOM 20 -15V (2) 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref in 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                           |     |             |

| 19 ADC DCOM 20 -15V (2) 21 ADC in (10V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                                 |     |             |

| 20                                                                                                                                                                                                                                                                    |     |             |

| 21 ADC in (20V) 22 ADC in (10V) 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                                                         |     |             |

| 22 ADC in (10V) 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                                                                         |     |             |

| 23 Bipolar Offset 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                                                                                         |     |             |

| 24 Ref In 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                                                                                                           |     |             |

| 25 ACOM (2) 26 Ref Out 27 +15V (2) 28 CE 29 R/C 30 Data Mode 31 CS 32 Byte Select                                                                                                                                                                                     |     |             |

| 26 Ref Out<br>27 +15V (2)<br>28 CE<br>29 R/C<br>30 Data Mode<br>31 CS<br>32 Byte Select                                                                                                                                                                               |     |             |

| 27 +15V (2)<br>28 CE<br>29 R/C<br>30 Data Mode<br>31 CS<br>32 Byte Select                                                                                                                                                                                             |     |             |

| 28 CE<br>29 R/C<br>30 Data Mode<br>31 CS<br>32 Byte Select                                                                                                                                                                                                            |     |             |

| 29 R/C<br>30 Data Mode<br>31 CS<br>32 Byte Select                                                                                                                                                                                                                     |     |             |

| 30 Data Mode<br>31 CS<br>32 Byte Select                                                                                                                                                                                                                               |     |             |

| 31 CS<br>32 Byte Select                                                                                                                                                                                                                                               |     |             |

| 32 Byte Select                                                                                                                                                                                                                                                        |     |             |

|                                                                                                                                                                                                                                                                       |     |             |

|                                                                                                                                                                                                                                                                       |     |             |

|                                                                                                                                                                                                                                                                       | 33  | S/H Control |

| 34 S/H Common                                                                                                                                                                                                                                                         | 34  | S/H Common  |

| PIN      | FUNCTION                    |

|----------|-----------------------------|

| 35       | S/H Out                     |

| 36       | Hold Cap                    |

| 37       | S/H Out                     |

| 38       | NC                          |

| 39       | S/H In                      |

| 40       | CH7 (CH7+)*                 |

| 41       | CH6 (CH6+)*                 |

| 42       | CH5 (CH5+)*                 |

| 43       | CH4 (CH4+)*                 |

| 44       | CH3 (CH3+)*                 |

| 45       | CH2 (CH2+)*                 |

| 46       | CH1 (CH1+)*                 |

| 47       | CH0 (CH0+)*                 |

| 48       | MUX Enable                  |

| 49       | MUX Address 0               |

| 50       | MUX Address 1               |

| 51       | MUX Address 2               |

| 52       | MUX Address 3 (NC)*         |

| 53       | ACOM (1)                    |

| 54       | CH8 (CH0-)*                 |

| 55       | CH9 (CH1-)*                 |

| 56       | CH10 (CH2-)*                |

| 57       | CH11 (CH3-)*                |

| 58       | CH12 (CH4-)*                |

| 59       | CH13 (CH5-)*                |

| 60       | CH14 (CH6-)*                |

| 61       | CH15 (CH7-)*                |

| 62       | RG (Gain Range)<br>G10      |

| 63<br>64 | G100                        |

| 65       |                             |

| 66       | MUX Out+/Amp In+<br>Amp In- |

| 67       | NC (MUX Out-)*              |

| 68       | Amp Sense                   |

| 1 00     | Tub sense                   |

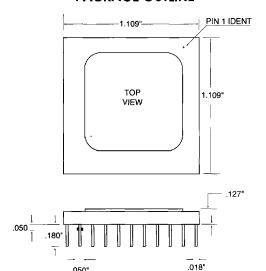

### **PACKAGE OUTLINE**

TOLERANCES ARE ±0.010"

.050"

\* Applicable to the SP9463/9473

| ORDERI   | DRDERING INFORMATION |                     |            |                     |          |       |                     |            |                     |  |  |  |

|----------|----------------------|---------------------|------------|---------------------|----------|-------|---------------------|------------|---------------------|--|--|--|

| Model    | Input                | Accuracy<br>(% FSR) | Throughput | Temp.<br>Range (°C) | Model    | Input | Accuracy<br>(% FSR) | Throughput | Temp.<br>Range (°C) |  |  |  |

| SP9462JH | 16SE                 | ±0.024              | 33KHz      | 0 to +70            | SP9463JH | 8DIF  | ±0.024              | 33KHz      | 0 to +70            |  |  |  |

| SP9462KH | 16SE                 | ±0.012              | 33KHz      | 0 to +70            | SP9463KH | 8DIF  | ±0.012              | 33KHz      | 0 to +70            |  |  |  |

| SP9462SH | 16SE                 | ±0.024              | 33KHz      | -55 to +125         | SP9463SH | 8DIF  | ±0.024              | 33KHz      | -55 to +125         |  |  |  |

| SP9462TH | 16SE                 | ±0.012              | 33KHz      | -55 to +125         | SP9463TH | 8DIF  | ±0.012              | 33KHz      | -55 to +125         |  |  |  |

| SP9472JH | 16SE                 | ±0.024              | 50KHz      | 0 to +70            | SP9473JH | 8DIF  | ±0.024              | 50KHz      | 0 to +70            |  |  |  |

| SP9472KH | 16SE                 | ±0.012              | 50KHz      | 0 to +70            | SP9473KH | 8DIF  | ±0.012              | 50KHz      | 0 to +70            |  |  |  |

| SP9472SH | 16SE                 | ±0.024              | 50KHz      | -55 to +125         | SP9473SH | 8DIF  | ±0.024              | 50KHz      | -55 to +125         |  |  |  |

| SP9472TH | 16SE                 | ±0.012              | 50KHz      | -55 to +125         | SP9473TH | 8DIF  | ±0.012              | 50KHz      | -55 to +125         |  |  |  |

This page left intentionally blank.