# Am81C471/478

**CMOS Color Palette**

# Advanced Micro Devices

## DISTINCTIVE CHARACTERISTICS

- Plug-in replacements for Bt471 and Bt478

- · VGA hardware and software compatible

- · Available in 35, 50, 66, 80 MHz versions

- Available in 44-pin PLCC package

- 256 x 18(24) Color Palette RAM

- 15 x 18(24) Overlay RAM

- · Triple 6-bit (8-bit) DACs

- · Sync on all three outputs

- RS-343A/RS-170 compatible RGB outputs

- External current or voltage reference

- Standard MPU interface

- Single +5 V power supply

## **GENERAL DESCRIPTION**

The Am81C471/478 CMOS Color Palette has been designed specifically for the VGA market. Applications include high-resolution color graphics, CAD/CAM/CAE, and desktop publishing. The Am81C471 and Am81C478 operate at speeds sufficient to support monitor sizes of 1024 X 768 pixels.

The Am81C471/478 has a 256 x 18(24) look-up table and 15 X 18(24) overlay regsiters and as such can simultaneously display 271 colors out of an available set of 65K (16.8 million) colors. The Am81C471 has triple 6-bit video DACs; the Am81C478 may be used in either 6-bit or 8-bit mode.

The Am81C471/478 also include input buffers and programmable bit-plane Read Masks. They are available in versions with pixel rates as high as 80 MHz. Proprietary

DAC decoding techniques minimize glitch energy and skew.

Both the Am81C471 and Am81C478 include programmable pedestals (0 or 7.5 IRE) and can be used with an external voltage or current reference. EGA emulation, overlaying cursors, text, grids, etc. can be implemented using the 15 overlay registers.

The Am81C471/478 generate RS-343A compatible outputs into doubly-terminated 75  $\Omega$  loads and RS-170 compatible output into a singly-terminated 75  $\Omega$  load, without external buffers.

The Am81C471 and Am81C478 are fabricated using AMD's state-of-the-art 1.2 \( \mu \) CMOS process. The devices are available in a 44-lead PLCC package.

Publication # Rev. Amendment

11447 A /0

Issue Date: October 1988

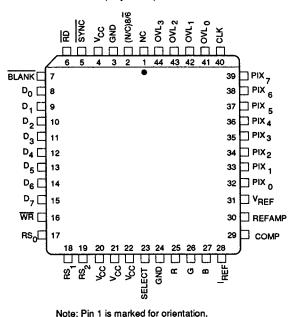

# **CONNECTION DIAGRAM**

## **PLCC**

(Top View)

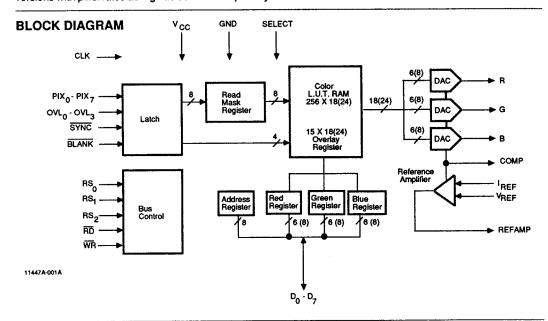

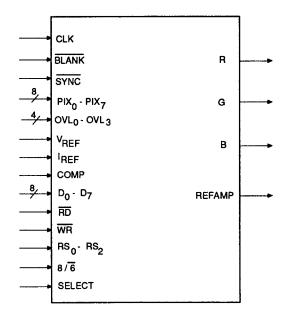

## **LOGIC DIAGRAM**

11447A-002A

1147A-003A

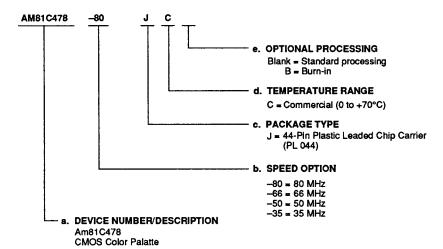

## ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Con   | Valid Combinations |  |  |  |  |  |  |  |  |  |

|-------------|--------------------|--|--|--|--|--|--|--|--|--|

| AM81C471-80 |                    |  |  |  |  |  |  |  |  |  |

| AM81C471-66 |                    |  |  |  |  |  |  |  |  |  |

| AM81C471-50 | ]                  |  |  |  |  |  |  |  |  |  |

| AM81C471-35 | JC, JCB            |  |  |  |  |  |  |  |  |  |

| AM81C478-80 |                    |  |  |  |  |  |  |  |  |  |

| AM81C478-66 |                    |  |  |  |  |  |  |  |  |  |

| AM81C478-50 | 1                  |  |  |  |  |  |  |  |  |  |

| AM81C478-35 | ]                  |  |  |  |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

\* Military or Limited Military temperature range products are "NPL" (Non-Compliant Products List) or Non-MIL-STD-883C Compliant products only.

## PIN DESCRIPTION

## **Timing Section**

## **CLK**

## Clock source pin (TTL compatible input)

This input operates at the pixel clock rate of the system. It is to be driven by a dedicated TTL buffer. The rising edge of CLK latches the SYNC, BLANK, PIX<sub>0</sub>-PIX<sub>7</sub> and OVL<sub>0</sub>-OVL<sub>3</sub> inputs.

#### BLANK

## Blank (TTL compatible input)

The BLANK input, when active, overrides the color pixel and overlay data to force the R,G, and B video outputs to their blank levels. This blank level is required during the monitor's vertical and horizontal retrace times. It is latched on the rising edge of CLK.

#### SYNC

## Sync (TTL compatible input)

The SYNC input, when active, switches off a current source on the R, G, and B video outputs. It is latched on the rising edge of CLK. Because SYNC does not override any other input or control pin, it should be asserted only during blanking intervals.

# Bit Map Interface Section

## PIX\_-PIX,

# Color Pixel Data addresses

## (TTL compatible inputs)

These 8 inputs select which of the 256 entries in the Color Palette look-up table is to be used to provide pixel color information. They are latched into the input buffer on the rising edge of CLK. PIX<sub>0</sub> is the least significant bit. Unused inputs should be grounded.

#### OVL\_OVL

# Overlay Data address (TTL compatible inputs)

These 4 inputs select which of the 15 overlay registers is to be used to provide color information. They are latched into the input buffer on the rising edge of CLK. The PIX<sub>0</sub>-PIX<sub>1</sub> inputs are ignored when the overlay palette is accessed. OVL<sub>0</sub> is the least significant bit. Unused inputs should be grounded.

## **MPU Interface Section**

## D<sub>o</sub>-D,

# Data and address bus (TTL compatible bi-directional)

These 8 pins are used to load and read back the Color look-up table and the internal control registers.  $D_0$  is the least significant bit.

## RD

## Read Control Input (TTL compatible input)

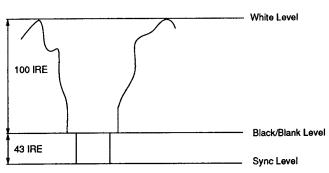

RD must be a logical zero to read data from the Color look-up table or any of the registers. During Read operations, RS\_RS, are latched on the falling edge of RD.

#### WR

## Write Control Input (TTL compatible input)

WR must be a logical zero to write data to the Color lookup table or any of the registers. During Write operations, RS\_RS\_ are latched on the falling edge of WR.

## RS,-RS,

# Register Select Inputs (TTL compatible Inputs)

RS<sub>0</sub>-RS<sub>2</sub> allow the MPU to address any location in the Color look-up tables or any of the internal control registers. These inputs determine the type of read or write operation being performed.

#### 8/6

# 8-bit/6-bit Select Input (TTL compatible input).

This pin is not used on the Am81C471 and should not be connected. For the Am81C478, this pin determines whether the MPU is reading or writing 8-bits (logical one) or 6-bits (logical zero) of information during each cycle. In 8-bit operation,  $D_{\tau}$  is the most significant bit. In 6-bit operation  $D_{s}$  is the most significant bit;  $D_{6}$  and  $D_{7}$  are ignored during write cycles and are logical zero during read cycles.

## **Analog Output Section**

R

## Red video output (Analog output)

Analog output of the red DAC. This output is capable of driving an RS-343A compatible doubly-terminated 75  $\Omega$  cable and an RS-170 compatible singly terminated 75  $\Omega$  cable.

G

## Green video output (Analog output)

Analog output of the green DAC. This output is capable of driving an RS-343A compatible doubly-terminated 75  $\Omega$  cable and an RS-170 compatible singly terminated 75  $\Omega$  cable.

В

## Blue video output (Analog output)

Analog output of the blue DAC. This output is capable of driving an RS-343A compatible doubly-terminated 75  $\Omega$  cable and an RS-170 compatible singly terminated 75  $\Omega$  cable.

VREF

## Voltage reference (Analog input).

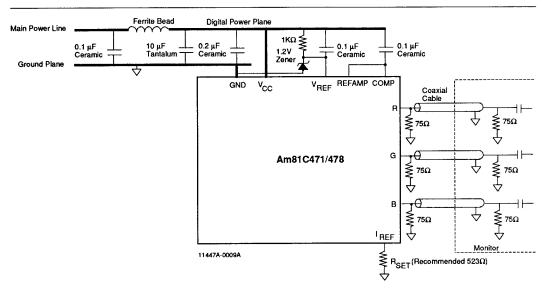

An external voltage reference circuit such as the one shown in Figure A1 must supply this input with a 1.235 volt (typical) reference.

IREF

# Current reference (Analog input).

#### Voltage Mode:

When an external voltage reference is used the  $R_{\rm SET}$  resistor connecting this pin and GND controls the magnitude of the full scale video signal according to the following relationship:

$$R_{\text{sct}}$$

(ohms) = K • 1,000 •  $V_{\text{RFF}}$  (V) /  $I_{\text{out}}$  (mA)

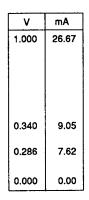

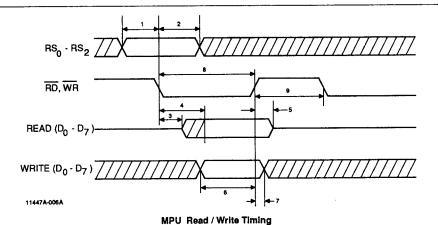

The table shown below defines K along with  $R_{\text{SET}}$  values for doubly-terminated 75  $\Omega$  loads.

| Mode  | Pedestal | K     | $R_{set}$ $(\Omega)$ |

|-------|----------|-------|----------------------|

| 6-bit | 7.5 IRE  | 3.025 | 147                  |

| 8-bit | 7.5 IRE  | 3.200 | 148                  |

| 6-bit | 0 IRE    | 3.000 | 139                  |

| 8-bit | 0 IRE    | 3.175 | 140                  |

### **Current Mode:**

When an external current reference is used, the relationship between  $\mathbf{I}_{\text{REF}}$  and the full scale output current on each video output is given by:

$$I_{REF}$$

(mA) =  $I_{out}$  (mA) / K

#### REFAMP

## Reference Amplifier Output (Analog output)

When an external voltage reference is used, this pin should be connected to COMP. When an external current reference is used this pin should be left floating.

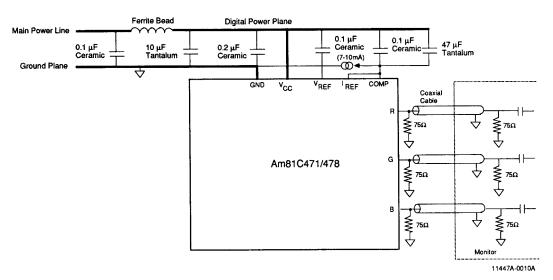

## COMP

# Compensation capacitor connection (Analog input)

A 0.1  $\mu$ F ceramic capacitor is connected between this pin and  $V_{cc}$ . This pin should be connected to REFAMP when an external voltage reference is used. When an external current reference is used this pin should be connected to  $I_{cc}$ .

# **Power Supply Section**

$\mathbf{v}_{\mathrm{cc}}$

Analog +5 volt supply

#### SELECT

## Select control input (TTL-compatible input)

This pin selects either a 0 IRE (SELECT = GND) or 7.5 IRE (SELECT =  $V_{cc}$ ) blanking pedestal.

## **FUNCTIONAL DESCRIPTION**

The Am81C471/478 CMOS Color Palette integrates all major functions required in the backend of a video system and supports pixels rates sufficient to drive most low-to-medium resolution monitors (including 1024 X 768).

A programmable look-up table maps the pixel data from a frame buffer into physical color and three Digital-to-Analog-Converters (DACs) convert the digital outputs of the look-up table into RS-343A compatible RGB analog outputs.

## Microprocessor Interface

The Am81C471/478 is designed to support a standard microprocessor bus interface with direct access to 256 look-up table (LUT) RAM locations, 15 overlay registers, and two control registers. The microprocessor interface is asynchronous with respect to pixel clock. However, data transfers between the LUT RAM or overlay registers and the Red Register, Green Register, and Blue Register as shown in the block diagram are synchronized to pixel clock. Such read and write operations take one and two pixel clock cycles, respectively.

The nature of the microprocessor operation is determined by examining the  ${\rm RS_0-RS_2}$  inputs. The  ${\rm RS_0-RS_2}$  select among the address register, the 256 LUT RAM locations, 15 overlay registers, or the Read Mask register, as shown in Table 1.

Table 1. RS<sub>0</sub>-RS<sub>2</sub> Decoding

| RS 2 | RS 1 | RS 0 | Function                                      |  |  |  |  |  |  |  |

|------|------|------|-----------------------------------------------|--|--|--|--|--|--|--|

| 0    | 0    | 0    | Write Mode RAM Look-Up-Table Address Register |  |  |  |  |  |  |  |

| 0    | 1    | 1    | Read Mode RAM Look-Up-Table Address Register  |  |  |  |  |  |  |  |

| 0    | 0    | 1    | Color Palette RAM Look-Up-Table               |  |  |  |  |  |  |  |

| 0    | 1    | 0    | Pixel Read Mask Register                      |  |  |  |  |  |  |  |

| 1    | 0    | 0    | Write Mode Overlay Address Register           |  |  |  |  |  |  |  |

| 1    | 1    | 1    | Read Mode Overlay Address Register            |  |  |  |  |  |  |  |

| 1    | 0    | 1    | Overlay Registers                             |  |  |  |  |  |  |  |

| 1    | 1    | 0    | Reserved                                      |  |  |  |  |  |  |  |

A typical color data write cycle is initiated by setting the 8-bit Address Register with the desired address of the LUT RAM (Overlay Registers) with the proper setting of RS,-RS, Next, the microprocessor performs three write cycles to the color palette: one for Red, one for Green, and one for Blue data with the RSo-RS2 selecting either the LUT RAM or RS, of the the Overlay Registers. At the end of the blue cycle the data is concatenated into a 24bit word (18 bits for the Am81C471 or for the Am81C478 with the 8/6 input set LOW) and subsequently written to the LUT RAM location (Overlay Register) pointed to by the Address Register. The Address Register is then autoincremented to point to the next LUT RAM location in the LUT RAM (to the next Overlay Register). This process may be repeated again as required by the microprocessor, See Table 2.

A typical color data read cycle is initiated by setting the 8-bit Address Register with the desired address of the LUT RAM (Overlay Registers) with the proper setting of RS<sub>0</sub>-RS<sub>2</sub>. Next, the microprocessor performs three read cycles to the color palette: one for Red, one for Green, and one for Blue data with the RS<sub>0</sub>-RS<sub>2</sub> selecting either the LUT RAM or one of the Overlay Registers. At the end of the blue cycle the Address Register is auto-incremented to point to the next LUT RAM location in the LUT RAM (to the next Overlay Register). This process may be repeated again as required by the microprocessor. See Table 2.

For the Am81C471 (and for the Am81C478 with the  $8/\overline{6}$  pin set LOW), the 6-bit color data occupies the six least significant positions of the data bus. Bits  $D_e$  and  $D_7$  are ignored during write cycles and are set to 0 during read cycles. Bit  $D_e$  is the least significant bit (LSB).

The Am81C471/478 uses one 8-bit Address Register to address both the LUT RAM and the Overlay Registers as shown in Table 3. During access to the Overlay Registers the upper four bits of the Address Registers are ignored. The Address Register resets to 0 after a blue read/write cycle to the LUT RAM address 255. A user-transparent modulo-3 counter (ARb, ARa) keeps track of the read, green, and blue cycles and auto-increments at the end of each read/write access to the LUT RAM or Overlay Registers. This counter is reset to zero after a write access to the Address Register and is unchanged following a read access to the Address Register.

The Am81C471/478 uses the 8-bit Pixel Read Mask Register to modify the address of the LUT RAM as provided by PIX<sub>o</sub>-PIX<sub>y</sub>. The eight bits of this register are ANDed with PIX<sub>o</sub>-PIX<sub>y</sub> and the result used as the address to the LUTRAM. This masking mechanism provides a quick way to after the appearance of one or more colors on the display unit with just one microprocessor access.

## **Display Memory Interface**

The color inputs,  $PIX_0$ - $PIX_7$  and  $OVL_0$ - $OVL_3$  are latched on the rising edge of CLK and are used as address to the 256 locations of the LUT RAM and the 15 Overlay Registers, respectively.

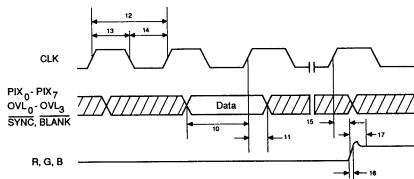

The total pipeline delay from the digital inputs  $PIX_0$ — $PIX_7$ ,  $OVL_0$ — $OVL_3$ ,  $\overline{SYNC}$ , and  $\overline{BLANK}$  to the analog R, G, and B outputs is four clock cycles.

### Video Generation

During each clock cycle, a 24-bit word (18-bits for the Am81C471 or for the Am81C478 with the  $8/\overline{6}$  input set LOW) from either the LUT RAM or the Overlay Registers is presented to the three DACs. The three DACs convert the digital color memory output into RGB RS-343A analog format.

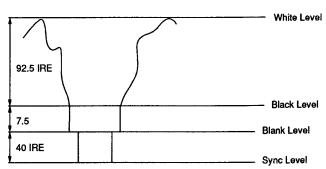

The SYNC and BLANK inputs are latched on the rising edge of CLK. These two inputs are responsible for adding weighted currents to RGB analog outputs as shown in Figures 1 and 2.

Tables 4 and 5 show how the SYNC and BLANK inputs change analog output levels.

The SYNC and BLANK inputs are routed to the three DACs after a delay equal to four clock periods, identical

to the delay incurred by the video stream.

To specify which blanking pedestal is to be applied, the SELECT input is used; if SELECT is set to logical zero, the blanking pedestal is 0.0 IRE and if SELECT is set to logical one, the blanking pedestal is 7.5 IRE.

The three analog outputs of the Am81C471/478 are each capable of driving a doubly terminated 75  $\Omega$  coaxial cable.

Table 2. Read/Write Access to the Am81C471/478

| RD | WR | RS <sub>2</sub> | RS <sub>1</sub> | RS <sub>0</sub> | ARb | ARa | FUNCTION                                                                                                                                                |

|----|----|-----------------|-----------------|-----------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 0  | 0               | 0               | 0               | Х   | Х   | Write Address Register; AR(7:0) ← D(7:0); ARb, ARa ← 0 (LUT Write)                                                                                      |

| 1  | 0  | 0               | 0               | 1               | 0   | 0   | Write Red Color; RREG(7:0) ← D(7:0); INC. ARb, ARa                                                                                                      |

| 1  | 0  | 0               | 0               | 1               | 0   | 1   | Write Green Color; GREG(7:0) ← D(7:0); INC. ARb, ARa                                                                                                    |

| 1  | 0  | 0               | 0               | 1               | 1   | 0   | Write Blue Color; BREG(7:0) $\leftarrow$ D(7:0); ARb, ARa $\leftarrow$ 0;                                                                               |

|    |    |                 |                 | •               |     |     | Write Color Look-Up-Table; R(7:0) ← RREG; G(7:0) ← GREG; B(7:0) ← BREG; INC AR(7:0)                                                                     |

| 1  | 0  | 1               | 0               | 0               | Х   | Х   | Write Address Register; AR(7:0) ← D(7:0); ARb, ARa ← 0 (Overlay Write)                                                                                  |

| 1  | 0  | 1               | 0               | 1               | 0   | 0   | Write Red Color; RREG(7:0) ← D(7:0); INC. ARb, ARa                                                                                                      |

| 1  | 0  | 1               | 0               | 1               | 0   | 1   | Write Green Color, GREG(7:0) ← D(7:0); INC. ARb, ARa                                                                                                    |

| 1  | 0  | 1               | 0               | 1               | 1   | 0   | Write Blue Color; BREG(7:0) ← D(7:0); ARb, ARa ← 0;                                                                                                     |

|    |    |                 |                 |                 |     |     | Write Overlay Register; ; R(7:0) ← RREG; G(7:0) ← GREG; B(7:0) ← BREG; INC AR(7:0)                                                                      |

| 1  | 0  | 0               | 1               | 1               | Χ   | Χ   | Write Address Register; AR(7:0) ← D(7:0); ARb, ARa ← 0;                                                                                                 |

| 0  | 1  | 0               | 0               | 1               | 0   | 0   | (LUT Read) RREG $\leftarrow$ R(7:0); GREG $\leftarrow$ G (7:0); BREG $\leftarrow$ B(7:0)<br>Read LUT Red; D (7:0) $\leftarrow$ RREG(7:0); INC. ARb, ARa |

| 0  | 1  | 0               | 0               | 1               | 0   | 1   | Read LUT Green; D(7:0) ← GREG(7:0); INC. ARb, ARa                                                                                                       |

| 0  | 1  | 0               | 0               | 1               | 1   | 0   | Read LUT Blue; D(7:0) $\leftarrow$ BREG(7:0); ARb, ARa $\leftarrow$ 0; INC AR(7:0)                                                                      |

| 1  | 0  | 1               | 1               | 1               | X   | X   | Write Address Register; AR(7:0) ← D(7:0); ARb, ARa ← 0;                                                                                                 |

| 0  | 1  | 1               | 0               | 1               | 0   | 0   | (Overlay Read) RREG ← R(7:0); GREG ← G (7:0); BREG ← B(7:0)<br>Read Overlay Red; D(7:0) ← RREG(7:0); INC. ARb, ARa                                      |

| 0  | 1  | 1               | 0               | 1               | 0   | 1   | Read Overlay Green ; D(7:0) ← GREG(7:0); INC. ARb, ARa                                                                                                  |

| 0  | 1  | 1               | 0               | 1               | 1   | 0   | Read Overlay Blue ; D(7:0) ← BREG(7:0); ARb, ARa ← 0; INC AR(7:0)                                                                                       |

Note: Refer to timing diagrams for edge information on RD and WR.

Table 3. Address Register Operation

| AR(7:0)   | RS <sub>2</sub> | RS 1 | RS 0 | Function                               |

|-----------|-----------------|------|------|----------------------------------------|

| \$00-\$FF | 0               | 0    | 1    | Color Look-Up-Table location \$00-\$FF |

| XXXX-0000 | 1               | 0    | 1    | Reserved                               |

| XXXX-0001 | 1               | 0    | 1    | Overlay Register 1                     |

| XXXX-0010 | 1               | 0    | 1    | Overlay Register 2                     |

| XXXX-0011 | 1               | 0    | 1    | Overlay Register 3                     |

| :         | :               | :    | :    | :                                      |

| XXXX-1111 | 1               | 0    | 1    | Overlay Register 15                    |

Note: 75  $\Omega$  doubly-terminated load, SELECT =  $V_{CC}$ . External voltage or current reference adjusted for 26.67 mA full scale output. RS-343A levels and tolerances assumed on all levels.

11447A-004A

Figure 1. Composite Video Output Signals (SELECT = V<sub>CC</sub>)

Table 4. Video Output Truth Table (SELECT = V<sub>cc</sub>)

| Description | SYNC | BLANK | I <sub>out</sub><br>(mA) | DAC<br>Input Data |

|-------------|------|-------|--------------------------|-------------------|

| WHITE       | 1    | 1     | 26.67                    | \$FF              |

| DATA        | 1    | 1     | data + 9.05              | data              |

| DATA-SYNC   | 0    | 1     | data + 1.44              | data              |

| BLACK       | 1    | 1     | 9.05                     | \$00              |

| BLACK-SYNC  | 0    | 1     | 1.44                     | \$00              |

| BLANK       | 1    | 0     | 7.62                     | \$xx              |

| SYNC        | 0    | 0     | 0                        | \$xx              |

|             |      |       |                          |                   |

Table 5. Video Output Truth Table (SELECT = GND)

| Description | SYNC | BLANK | l <sub>out</sub><br>(mA) | DAC<br>Input Data |

|-------------|------|-------|--------------------------|-------------------|

| WHITE       | 1    | 1     | 26.67                    | \$FF              |

| DATA        | 1    | 1     | data + 8.05              | data              |

| DATA-SYNC   | 0    | 1     | data                     | data              |

| BLACK       | 1    | 1     | 8.05                     | \$00              |

| BLACK-SYNC  | 0    | 1     | 0                        | \$00              |

| BLANK       | 1    | 0     | 8.05                     | \$xx              |

| SYNC        | 0    | 0     | 0                        | \$xx              |

Note: Typical will full scale G = 26.67 mA. SELECT = V<sub>cc</sub>.

External voltage or current reference adjusted for 26.67 mA full scale output.

Note: Typical will full scale G = 26.67 mA. SELECT = GND. External voltage or current reference adjusted for 26.67 mA full scale output.

Note:  $75\,\Omega$  doubly-terminated load, SELECT = GND. External voltage or current reference adjusted for 26.67 mA full scale output.

11447A-005A

Figure 2. Composite Video Output Signals (SELECT = GND)

| ABSO      | LUTE MA                       | AXIMUM RATINGS                                                             | OPERATI                         | NG RAN                                                               | IGES               |                      |          |  |  |  |  |  |

|-----------|-------------------------------|----------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------|--------------------|----------------------|----------|--|--|--|--|--|

| Storage ' | Temperature                   | 65 to +150                                                                 | O°C Commercial (                | C) Devices                                                           |                    |                      |          |  |  |  |  |  |

|           | Temperature                   |                                                                            |                                 |                                                                      | (T <sub>A</sub> )  | 0                    | to +70°C |  |  |  |  |  |

|           |                               | 55 to +125                                                                 | coppiy voic                     | Supply Voltage (V <sub>CC</sub> ) for 80 MHz devices+4.75 to +5.25 V |                    |                      |          |  |  |  |  |  |

|           | •                             | ture+175<br>ound Potential                                                 | 101 60 1411 12                  |                                                                      |                    |                      |          |  |  |  |  |  |

|           |                               | 0.5 to 7.0                                                                 | 0 V                             |                                                                      | /ices              |                      |          |  |  |  |  |  |

| DC Volta  | age Applied t                 | toGND-0.5 V to V <sub>CC</sub> Max+0.                                      | s v Hererence vo                | -                                                                    |                    | +1.14 to             | +1.26 V  |  |  |  |  |  |

|           | ts for HIGH                   | •                                                                          | (Voltage ne                     |                                                                      | onfiguration)      | 2.4                  | - 10 1   |  |  |  |  |  |

|           | t State                       |                                                                            | (Current De                     |                                                                      | onfiguration)      | 3 10                 | J-IU MA  |  |  |  |  |  |

|           |                               | ID0.3 to V <sub>CC</sub> +0.                                               | 0.441                           |                                                                      | yurauun)           |                      | 37.5 Q   |  |  |  |  |  |

|           |                               | se listed under ABSOLUTE MAXIM<br>e permanent device failure. Function     | IUW .                           |                                                                      | e those limits     |                      |          |  |  |  |  |  |

| at or abo | ove these lin<br>m ratings fo | nits is not implied. Exposure to abso<br>or extended periods may affect de | lute functionality of           | -                                                                    | e is guaranteed    |                      |          |  |  |  |  |  |

| DC CH     | HARACT                        | ERISTICS (Over operating rang                                              | ge)                             |                                                                      |                    |                      |          |  |  |  |  |  |

| Parm.     | Parm.                         | Parameter                                                                  | Test                            |                                                                      |                    |                      |          |  |  |  |  |  |

| Num       | Symbol                        | Description                                                                | Conditions                      | Min                                                                  | Тур                | Max                  | Unit     |  |  |  |  |  |

| Digita    | I Inputs                      | 11 - 11 - 11 - 11 - 11 - 11 - 11 - 11                                      |                                 |                                                                      |                    |                      |          |  |  |  |  |  |

|           | V <sub>IH</sub>               | Input High Voltage                                                         |                                 | 2.0                                                                  |                    | V <sub>cc</sub> +0.5 | V        |  |  |  |  |  |

|           | V <sub>IL</sub>               | Input Low Voltage                                                          |                                 | GND-0.5                                                              |                    | 0.8                  | ٧        |  |  |  |  |  |

|           | I <sub>H</sub>                | Input High Current                                                         | V <sub>in</sub> =2.4 V          |                                                                      |                    | 1                    | μА       |  |  |  |  |  |

|           | J <sub>IL</sub>               | Input Low Current                                                          | V <sub>in_</sub> 0.4 V          |                                                                      |                    | -1                   | μΑ       |  |  |  |  |  |

|           | C <sub>IN</sub>               | Input Capacitance f                                                        | =1 MHz, V <sub>in</sub> = 2.4 V |                                                                      |                    | 7                    | рF       |  |  |  |  |  |

| Digita    | Output                        | <u> </u>                                                                   |                                 |                                                                      |                    |                      |          |  |  |  |  |  |

|           | V <sub>OH</sub>               | Output High Voltage                                                        | I <sub>OH</sub> = -400 μA       | 2.4                                                                  | 18                 |                      | v        |  |  |  |  |  |

|           | V <sub>OL</sub>               | Output Low Voltage                                                         | I <sub>OL</sub> = 3.2 mA        | , 🖠                                                                  |                    | .4                   | V        |  |  |  |  |  |

|           | l <sub>oz</sub>               | 3-State Current                                                            | OL.                             | · Co                                                                 | <b>V</b> -         | 50                   | μА       |  |  |  |  |  |

|           | Cout                          | Output Capacitance                                                         |                                 | / Y                                                                  | •                  | 7                    | pF       |  |  |  |  |  |

| Analo     | g Output                      | le                                                                         |                                 | 12.                                                                  |                    |                      |          |  |  |  |  |  |

| Allaio    | g Output                      | Resolution (each DAC)                                                      | - M                             | 6 (8)                                                                | 6 (8)              | 6 (8)                | Bits     |  |  |  |  |  |

|           |                               | Accuracy (each DAC)                                                        | * & ST A.                       | <b>y</b> 0 (0)                                                       | J (J)              | - (-)                |          |  |  |  |  |  |

|           | LIN,                          | Integral Linearity Error                                                   | " MA .                          |                                                                      |                    | ±1/4(1)              | LSB      |  |  |  |  |  |

|           | LINd                          | Differential Linearity Error                                               | A A                             |                                                                      |                    | ±1/4(1)              | LSB      |  |  |  |  |  |

|           | u                             | Gray Scale Error                                                           |                                 |                                                                      |                    | ±5                   | %Gray    |  |  |  |  |  |

|           |                               | Monotonicity                                                               |                                 |                                                                      | Guaranteed         |                      |          |  |  |  |  |  |

|           |                               | Coding                                                                     | Binary                          |                                                                      |                    |                      | Binary   |  |  |  |  |  |

|           |                               | Output Current                                                             |                                 |                                                                      |                    |                      |          |  |  |  |  |  |

|           |                               | White Level Relative Blank                                                 |                                 | 17.69                                                                | 19.05              | 20.4                 | mA       |  |  |  |  |  |

|           |                               | White Level Relative to Black                                              |                                 | 16.74                                                                | 17.62              | 18.5                 | mΑ       |  |  |  |  |  |

|           |                               | Black Level Relative to Blank                                              | SELECT = V <sub>cc</sub>        | 0.95                                                                 | 1.44               | 1.9                  | mA<br>a  |  |  |  |  |  |

|           |                               | Plank t avail                                                              | SELECT = GND                    | 0<br>6.29                                                            | 5<br>7. <b>6</b> 2 | 50<br>8.96           | μA<br>mA |  |  |  |  |  |

|           |                               | Blank Level<br>Sync Level                                                  |                                 | 0.29                                                                 | 7.62<br>5          | 50                   | μА       |  |  |  |  |  |

|           |                               | LSB Size                                                                   |                                 | U                                                                    | 3                  | 30                   | μΛ       |  |  |  |  |  |

|           |                               | Am81C478 (8/6=Logical one)                                                 |                                 |                                                                      | 69.1               |                      | μА       |  |  |  |  |  |

|           |                               | Am81C471                                                                   |                                 |                                                                      | 279.68             |                      | μA       |  |  |  |  |  |

|           |                               | DAC-to-DAC Matching                                                        |                                 |                                                                      | 2                  | 5                    | %        |  |  |  |  |  |

|           | R <sub>out</sub>              | Output Impedance                                                           |                                 |                                                                      | 10                 | -                    | ΚΩ       |  |  |  |  |  |

|           | C <sub>out</sub>              | •                                                                          | f=1 MHz, I <sub>out</sub> =0 mA |                                                                      |                    | 30                   | pF       |  |  |  |  |  |

|           |                               |                                                                            |                                 |                                                                      |                    |                      |          |  |  |  |  |  |

μΑ

%/%V<sub>cc</sub>

0.5

100

COMP=0.1 pF,

f=1 KHz

I<sub>VREF</sub> PSSR Voltage Reference Input Current

Power Supply Rejection Ratio

# **SWITCHING CHARACTERISTICS** (Over operating range)

| Parm.<br>Num. | Parm.<br>Symbo                  |                                             | 80 M<br>Min Typ      |     |     | 6 <b>М</b> Н<br>Тур |     |                     | MHz<br>yp Max |                   | 5 MHz<br>Typ Ma | x Units |

|---------------|---------------------------------|---------------------------------------------|----------------------|-----|-----|---------------------|-----|---------------------|---------------|-------------------|-----------------|---------|

|               |                                 | Clock Rate                                  |                      | 80  |     |                     | 66  |                     | 50            |                   | 3               | 5 MHz   |

| 1             | ts                              | RS <sub>0</sub> -RS <sub>2</sub> Setup Time | 10                   |     | 10  |                     |     | 10                  |               | 15                |                 | ns      |

| 2             | t <sub>H</sub>                  | RS <sub>0</sub> -RS <sub>2</sub> Hold Time  | 10                   |     | 10  |                     |     | 10                  |               | 15                |                 | ns      |

| 3             | t <sub>p</sub>                  | RD Asserted to Data Bus Driven              | 5                    |     | 5   |                     |     | 5                   |               | 5                 |                 | ns      |

| 4             | t <sub>p</sub>                  | RD Asserted to Data Valid                   |                      | 40  |     |                     | 40  |                     | 40            |                   | 4               | o ns    |

| 5             | t <sub>p</sub>                  | RD Negated to Data Bus 3-stated             |                      | 20  |     |                     | 20  | 4                   | 20            |                   | 2               | o ns    |

| 6             | ts                              | Write Data Setup Time                       | 10                   |     | 10  |                     | 4   | 7                   |               | 15                |                 | ns      |

| 7             | t <sub>H</sub>                  | Write Data Hold Time                        | 10                   |     | 10  |                     |     | 10                  |               | 15                |                 | ns      |

| 8             | t <sub>w</sub>                  | RD, WR Pulse Width Low                      | 50                   |     | 50  |                     | 7   | 50                  |               | 50                |                 | กร      |

| 9             | t <sub>w</sub>                  | RD, WR Pulse Width High                     | 4 X t <sub>cyc</sub> | 4   | X   | 1                   | ~   | PX t <sub>cyc</sub> | 4             | X t <sub>cy</sub> | rc              | ns      |

| 10            | ts                              | Pixel and Overlay Setup Time                | 3                    | 4   | 3.  |                     | ) ` | 3                   |               | 4                 |                 | ns      |

| 11            | t <sub>H</sub>                  | Pixel and Overlay Hold Time                 | 3                    | 1   |     |                     |     | 3                   |               | 4                 |                 | ns      |

| 12            | t <sub>cyc</sub>                | Clock Cycle Time                            | 12.5                 |     | 5.2 |                     |     | 20                  |               | 28                |                 | ns      |

| 13            | t <sub>w</sub>                  | Clock Pulse Width High Time                 | 4                    | 1   | 5   |                     |     | 6                   |               | 7                 |                 | ns      |

| 14            | t <sub>w</sub>                  | Clock Pulse Width Low Time                  |                      | 7   | 5   |                     |     | 6                   |               | 9                 |                 | ns      |

| 15            | t <sub>o</sub>                  | Analog Output Delay                         | X)                   | 30  |     |                     | 30  |                     | 30            |                   | 3               | ) ns    |

| 16            | t <sub>R</sub> , t <sub>F</sub> | Analog Output Rise/Fall Time (Note 1)       | 3                    |     |     | 3                   |     |                     | 3             |                   | 3               | ns      |

| 17            | t <sub>s</sub>                  | Analog Output Settling Tin<br>(Note 1)      | 13                   |     |     | 16                  |     | ;                   | 20            |                   | 28              | ns      |

|               |                                 | Clock and Data Feedthrough                  | -30                  | 0   |     | -30                 |     | _                   | 30            |                   | -30             | dB      |

|               |                                 | Glitch Impulse (Note 2)                     | 75                   |     |     | 75                  |     | •                   | 75            |                   | 75              | pV-sec  |

|               |                                 | DAC to DAC Crosstalk                        | -23                  | 3   |     | -23                 |     | _                   | 23            |                   | -23             | dB      |

|               |                                 | Analog Output Skew                          |                      | 2   |     |                     | 2   |                     | 2             |                   | 2               | ns      |

|               |                                 | Pipeline Delay                              | 4                    |     |     | 4                   |     |                     | 4             |                   | 4               | clocks  |

|               | lcc                             | V <sub>cc</sub> Supply Current (Note 3)     | 160                  | 200 |     | 160                 | 200 | 1                   | 60 200        |                   | 160 20          | 0 mA    |

## Notes:

1. Clock and data feedthrough are not included

2. Included clock and data feedthrough, -3 dB bandwidth = 2 x clock frequency

3. Measured at maximum f<sub>CLK</sub>; I<sub>CC</sub>(Max.): V<sub>CC</sub> = 5.25 V, T<sub>A</sub> = 0°C I<sub>CC</sub>(Typ.): V<sub>CC</sub> = 5.0 V, T<sub>A</sub> + 25°C

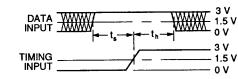

## **Test Conditions:**

TTL Input Level: 0 to 3 V with  $t_{\rm R}$ ,  $t_{\rm F}$  (10–90%)  $\leq$  3 ns  $R_{\rm set}$ =148  $\Omega$  (Am81C478);  $R_{\rm set}$ =147  $\Omega$  (Am81C471)  $V_{\rm ret}$ =1.235 V, Select =  $V_{\rm cc}$ , 8/6=Logical '1' Analog Output Load  $\leq$  10 pF,  $D_{\rm p}$ — $D_{\rm p}$  Output Load  $\leq$  50 pF

Note 1: Output delay measured from the 50% point of the rising edge of CLK to the 50 % point of the full scale transition

Note 2: Settling time measured from the 50% point of the full scale transition to the output remaining within ± LSB (Am81C478) or ± 1/4 LSB (Am81C471)

Note 3: Output rise/fall time measured between the 10% and 90% points of full scale transition

11447A-007A

## Video Input / Output Timing

11447A-012A

Notes: 1. Diagram shown for HIGH data only. Output transition may be opposite sense.

2. Cross-hatched areas are don't care condition.

## **Switching Test Waveform**

## APPENDIX A: APPLICATION NOTE FOR THE AM81C471/478

The design of a system using the Am81C471/478 should be guided by considerations similar to those used for designing precision high-speed mixed analog and digital systems. The following rules and examples are given for orientation purposes. Users may choose to design circuits, which may differ considerably from the examples given here.

The Am81C471/478 can be configured in either current or voltage reference modes. The voltage reference scheme, as shown in Figure A1, is preferred over the current source scheme because of the following features: superior power supply rejection, temperature compensation, lower power, fewer components and overall simplicity of design. The current reference mode, as shown in Figure A2, requires more components to provide adequate temperature compensation, and power supply rejection.

Power pins should be decoupled from the power lines in the rest of the system. The Am81C471/478 should have its own power plane; this plane should provide power to all its power pins and voltage/current reference circuits. This plane should be connected to the main power plane by a wire running through ferrite beads as shown in Figures A1 and A2.

If further noise reduction is required on the analog outputs then a separate analog power plane and digital power plane should be used and connected to pins (21,22) and (4,20) respectively. These two power planes should be connected to the main power plane by wires running through ferrite beads. The analog plane should not be crossed by any digital signal. Only one ground plane should be used, directly connected to the rest of the system. Tantalum capacitors, in parallel with a 0.1  $\mu\text{F}$  ceramic capacitor, should be placed between each side of the ferrite beads and the ground plane. If too much ripple exists on the lines, the use of a dedicated linear regulator is recommended.

The COMP pin should be decoupled from the power pins and the rest of the system. A 0.1  $\mu$ F ceramic capacitor should be connected in parallel between this pin and the analog power pins (21,22).

Digital lines accessible by the MPU interface should be kept far from pixel data lines. Pixel clock lines should be kept far from all other digital inputs. Analog outputs should be kept far from any other input. No digital line should run under the analog plane.

Connection to the monitor should be done through a doubly-terminated 75  $\Omega$  coaxial cable. To minimize reflections, terminating resistors on the color palette side should be placed as close as possible to the R, G, and B outputs.

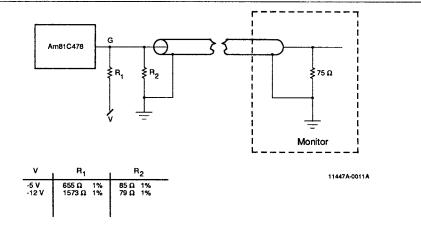

The signals produced by the Am81C471/478 are all positive currents, which when passing through the terminating resistors produce positive voltages. Since most monitors are AC-coupled, DC restoration with the proper DC level is done inside the monitor. If a negativegoing sync (-0.286V) is required, DC level shifting can be done outside the palette, prior to entering the transmission cable. The circuit that produces this level shifting is shown in Figure A3. This circuit shows two resistors, R, and R2, as the termination at the transmitting side. R, is connected between R (G, or B) outputs and ground, while R2, is connected between R (G, or B) outputs and a voltage source more negative than -0.572V. R, and R, are such that in parallel they equal 75  $\Omega$ , while their ratio is such that the voltage drop caused by the negative voltage source across R, is 0.572 V. The relationship is described by the following formulae:

$R_1 \parallel R_2 = 75 \Omega$ ;  $R_1 = V \cdot 75/(V + 0.572)$ ;  $R_2 = V \cdot 75/(-0.572)$

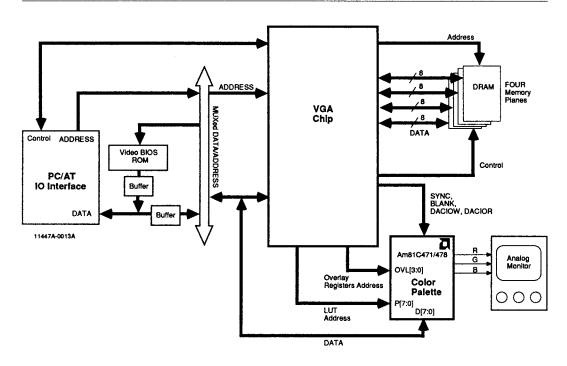

Figure A4 shows a VGA system in which a VGA graphics controller is paired with Am81C471/478 in a typical PC board design.

The Am81C471 has 6-bit  $\mu P$  interface which is compatible with existing VGA software. To accomodate 8-bit software the Am81C478 can be used. By driving the  $8/\overline{6}$  input pin from the  $\mu P$  interface the software can automatically change the DAC resolution (bits per channel) according to its own requirements.

Figure A1. Am81C471/478 Voltage Reference Connection Diagram (AC Coupling of the Monitor)

Figure A2. Am81C471/478 Current Reference connection Diagram (AC Coupling of the Monitor)

Figure A3. DC-Level Shifting Using Two Resistors in Parallel

Figure A4. Application Example: VGA system using a VGA chip and an Am81C471/478