# AM2940

# DMA Address Generator

The AM2940, a 28-pin member of AMD's AM2900 family of Low-Power Schottky bipolar LSI chips, is a high-speed, cascadable, eight-bit wide Direct Memory Access Address Generator slice. Any number of AM2940's can be cascaded to form larger addresses.

The primary function of the device is to generate sequential memory addresses for use in the sequential transfer of data to or from a memory. It also maintains a data word count and generates a DONE signal when a programmable terminal count has been reached. The device is designed for use in peripheral controllers with DMA capability or in any other system which transfers data to or from sequential locations of a memory.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Am2940

DMA Address Generator

### DISTINCTIVE CHARACTERISTICS

#### DMA Address Generation Generates memory address, word count and DONE

signal for DMA transfer operation. • Expandable Eight-bit Slice Any number of Am2940's can be cascaded to form larger memory addresses – three devices address 16 megawords.

- Repeat Data Transfer Capability Initial memory address and word count are saved so that the data transfer can be repeated.

- Programmable Control Modes

Provides four types of DMA transfer control plus

memory address increment/decrement.

- High Speed, Bipolar LSI Advanced Low-Power Schottky TTL technology provides typical CLOCK to DONE propagation delay of 50ns and 24mA output current sink capability.

- Microprogrammable Executes 8 different instructions.

### **GENERAL DESCRIPTION**

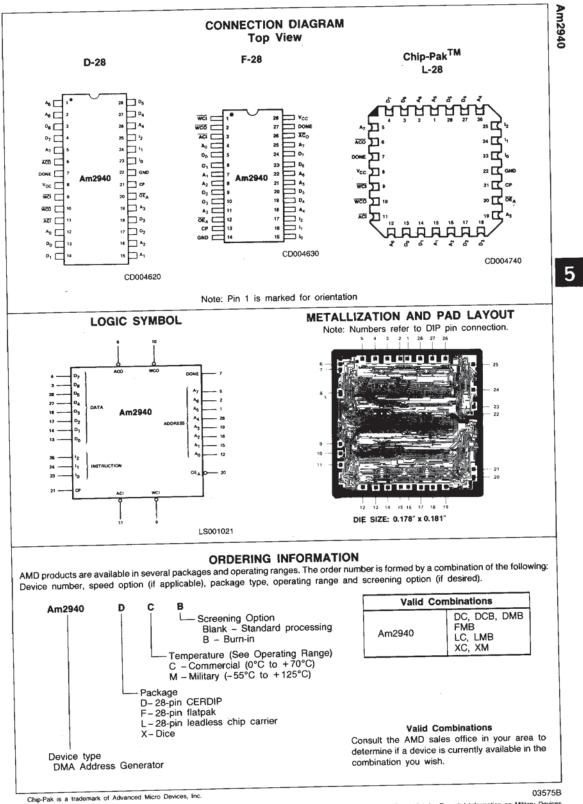

The Am2940, a 28-pin member of Advanced Micro Devices' Am2900 family of Low-Power Schottky bipolar LSI chips, is a high-speed, cascadable, eight-bit wide Direct Memory Access Address Generator slice. Any number of Am2940's can be cascaded to form larger addresses.

The primary function of the device is to generate sequential memory addresses for use in the sequential transfer of data to or from a memory. It also maintains a data word count and generates a DONE signal when a programmable terminal count has been reached. The device is designed for use in peripheral controllers with DMA capability or in any other system which transfers data to or from sequential locations of a memory.

The Am2940 can be programmed to increment or decrement the memory address in any of four control modes, and executes eight different instructions. The initial address and word count are saved internally by the Am2940 so that they can be restored later in order to repeat the data transfer operation.

5-268 Refer to Page 13-1 for Essential Information on Military Devices

5-269

Refer to Page 13-1 for Essential Information on Military Devices

Am2940

### PIN DESCRIPTION

| Pin No.    | Pin No. Name I/O Description |     |                                                                           |  |  |  |  |

|------------|------------------------------|-----|---------------------------------------------------------------------------|--|--|--|--|

| 23, 24, 25 | I <sub>0-2</sub>             | I   | Selects one of eight instructions.                                        |  |  |  |  |

| 11         | ACI                          | 1   | Carry-in to the address counter.                                          |  |  |  |  |

| 6          | ACO                          | 0   | Carry-out from the address counter.                                       |  |  |  |  |

| 9          | WCI                          | 1   | Carry-in to the word counter.                                             |  |  |  |  |

| 10         | WCO                          | 0   | Carry-out from the word counter.                                          |  |  |  |  |

|            | D <sub>0-7</sub>             | 1/0 | External data.                                                            |  |  |  |  |

|            | A <sub>0-7</sub>             | 0   | Address outputs under control of Output Enable input, OEA.                |  |  |  |  |

| 20         | OEA                          | 1   | Address output enable.                                                    |  |  |  |  |

| 7          | DONE                         | 0   | Transfer complete signal.                                                 |  |  |  |  |

| 21         | CP                           | 1   | Clock input. Registers and counters change on the LOW-to-HIGH transition. |  |  |  |  |

### Am2940 ARCHITECTURE

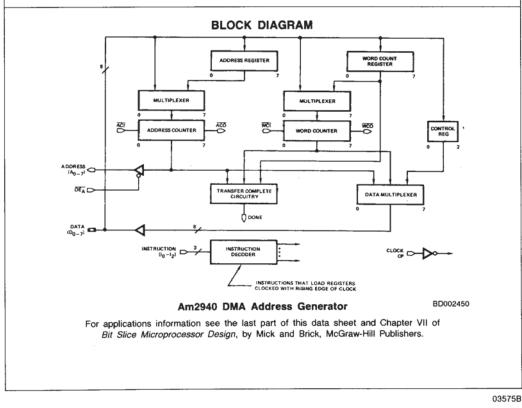

As shown in the Block Diagram, the Am2940 consists of the following:

- A three-bit Control Register

- An eight-bit Address Counter with input multiplexer

- An eight-bit Address Register

- An eight-bit Word Counter with input multiplexer

- An eight-bit Word Count Register

- Transfer complete circuitry

- An eight-bit wide data multiplexer with three-state output buffers

- Three-state address output buffers with external output enable control

- An instruction decoder

### **Control Register**

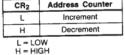

Under instruction control, the Control Register can be loaded or read from the bidirectional DATA lines  $D_0$ - $D_7$ . Control Register bits 0 and 1 determine the Am2940 Control Mode, and bit 2 determines whether the Address Counter increments or decrements. Figure 1 defines the Control Register format.

### Address Counter

The Address Counter, which provides the current memory address, is an eight-bit, binary, up/down counter with full look-ahead carry generation. The Address Carry Input ( $\overline{ACI}$ ) and Address Carry Output ( $\overline{ACO}$ ) allow cascading to accommodate larger addresses. Under instruction control, the Address Counter can be enabled, disabled, and loaded from the DATA inputs, D<sub>0</sub>-D<sub>7</sub>, or the Address Register. When enabled and the  $\overline{ACI}$  input is LOW, the Address Counter increments/decrements on the LOW-to-HIGH transition of the CLOCK input, CP. The Address Counter output can be enabled onto the three-state ADDRESS outputs A<sub>0</sub>-A<sub>7</sub> under control of the Output Enable input,  $\overline{OE_A}$ .

### Address Register

The eight-bit Address Register saves the initial address so that it can be restored later in order to repeat a transfer operation. When the LOAD ADDRESS instruction is executed, the Address Register and Address Counter are simultaneously loaded from the DATA inputs, Do-D7.

#### Word Counter and Word Count Register

The Word Counter and Word Count Register, which maintain and save a word count, are similar in structure and operation to the Address Counter and Address Register, with the exception that the Word Counter increments in Control Modes 1 and 3, decrements in Control Mode 0, and is disabled in Control Mode 2. The LOAD WORD COUNT instruction simultaneously loads the Word Counter and Word Count Register.

### **Transfer Complete Circuitry**

The Transfer Complete Circuitry is a combinational logic network which detects the completion of the data transfer operation in three Control Modes and generates the DONE output signal. The DONE signal is an open-collector output, which can be dot-anded between chips.

#### **Data Multiplexer**

The Data Multiplexer is an eight-bit wide, 3-input multiplexer which allows the Address Counter, Word Counter, and Control Register to be read at the DATA lines, D<sub>0</sub>-D<sub>7</sub>. The Data Multiplexer and three-state Data Output Buffers are instruction controlled.

### **Address Output Buffers**

The three-state Address Output Buffers allow the Address Counter output to be enabled onto the ADDRESS lines, A<sub>0</sub>-A<sub>7</sub>, under external control. When the Output Enable input,  $\overrightarrow{OE_A}$ , is LOW, the Address output buffers are enabled; when  $\overrightarrow{OE_A}$  is HIGH, the ADDRESS lines are in the high-impedance state. The Address and Data Output Buffers can sink 24mA output current over the commercial operating range.

### Instruction Decoder

The Instruction Decoder generates required internal control signals as a function of the INSTRUCTION inputs,  $I_0$ - $I_2$  and Control Register bits, CR<sub>0</sub>-CR<sub>1</sub>.

#### Clock

The CLOCK input, CP is used to clock the Address Register, Address Counter, Word Count Register, Word Counter, and Control Register, all on the LOW-to-HIGH transition of the CP signal.

|     |     |                        | Cor<br>CR <sub>2</sub> | CR1 CR0         | ] .                                                |                                                |

|-----|-----|------------------------|------------------------|-----------------|----------------------------------------------------|------------------------------------------------|

|     |     |                        |                        |                 | DONE                                               | Output Signal                                  |

| CR1 | CR0 | Control Mode<br>Number | Control<br>Mode Type   | Word<br>Counter | WCI = LOW                                          | WCI = HIGH                                     |

| L   | L   | 0                      | Word Count Equals Zero | Decrement       | HIGH when<br>Word Counter = 1                      | HIGH when<br>Word Counter = 0                  |

| L   | н   | 1                      | Word Count Compare     | Increment       | HIGH when<br>Word Counter + 1<br>= Word Count Reg. | HIGH when<br>Word Counter<br>= Word Count Reg. |

| н   |     | 2                      | Address Compare        | Hold            | HIGH when Word                                     | Counter = Address Counter                      |

| н   | н   | 3                      | Word Counter Carry Out | Increment       | At                                                 | ways LOW                                       |

## Am2940 CONTROL MODES

### Control Mode 0 - Word Count Equals Zero Mode

In this mode, the LOAD WORD COUNT instruction loads the word count into the Word Count Register and Word Counter. When the Word Counter is enabled and the Word Counter Carry-in, WCI, is LOW, the Word Counter decrements on the LOW-to-HIGH transition of the clock input, CP. Figure 1 specifies when the DONE signal is generated.

## Control Mode 1 - Word Count Compare Mode

In this mode the LOAD WORD COUNT instruction loads the word count into the Word Count Register and clears the Word Counter. When the Word Counter is enabled and the Word Counter Carry-in, WCI, is LOW, the Word Counter increments on the LOW-to-HIGH transition of the clock input, CP. Figure 1 specifies when the DONE signal is generated.

## Control Mode 2 - Address Compare Mode

In this mode, only an initial and final memory address need be specified. The initial Memory Address is loaded into the Address Register and Address Counter and the final memory address is loaded into the Word Count Register and Word Counter. The Word Counter is always disabled in this mode and serves as a holding register for the final memory address. When the Address Counter increments or decrements (depending on Control Register bit 2) on the LOW-to-HIGH transition of the CLOCK input, CP. The Transfer Complete Circuitry compares the Address Counter with the Word Counter and generates the DONE signal during the last word transfer; i.e., when the Address Counter equals the Word Counter.

.

5

### Control Mode 3 - Word Counter Carry Out Mode

For this mode of operation, the user can load the Word Count Register and Word Counter with the two's complement of the number of data words to be transferred. When the Word Counter is enabled and the  $\overline{\rm WCI}$  input is LOW, the Word Counter increments on the LOW-to-HIGH transition of the CLOCK input, CP. A Word Counter Carry Out signal,  $\overline{\rm WCO}$ , indicates the last data word is being transferred. The DONE signal is not required in this mode and, therefore, is always LOW.

> 03575B Refer to Page 13-1 for Essential Information on Military Devices

5-271

### Am2940 INSTRUCTIONS

.

The Am2940 instruction set consists of eight instructions. Six instructions load and read the Address Counter, Word Counter and Control Register; one instruction enables the Address and Word counters; and one instruction reinitializes the Address and Word Counters. The function of the REINITIALIZE COUNTERS, LOAD WORD COUNT, and ENABLE COUNTERS instructions varies with the Control Mode being utilized. Table 1 defines the Am2940 Instructions as a function of Instruction inputs I<sub>0</sub>-I<sub>2</sub> and the four Am2940 Control Modes.

The WRITE CONTROL REGISTER instruction writes DATA input  $D_0$ - $D_2$  into the Control Register; DATA inputs  $D_3$ - $D_7$  are "don't care" inputs for this instruction. The READ CONTROL REGISTER instruction gates the Control Register outputs to DATA lines,  $D_0$ - $D_2$ . DATA lines  $D_3$ - $D_7$  are in the HIGH state during this instruction.

The Word Counter can be read using the READ WORD COUNTER instruction, which gates the Word Counter outputs to DATA lines  $D_0$ - $D_7$ . The LOAD WORD COUNT instruction is Control Mode dependent. In Control Modes 0, 2, and 3, DATA inputs  $D_0$ - $D_7$  are written into both the Word Count Register and Word Counter. In Control Mode 1, DATA inputs  $D_0$ - $D_7$  are

written into the Word Count Register and the Word Counter is cleared.

The READ ADDRESS COUNTER instruction gates the Address Counter outputs to DATA lines  $D_0$ - $D_7$ , and the LOAD ADDRESS instruction writes DATA inputs  $D_0$ - $D_7$  into both the Address Register and Address Counter.

In Control Modes 0, 1, and 3, the ENABLE COUNTERS instruction enables both the Address and Word Counters; in Control Mode 2, the Address Counter is enabled and the Word Counter holds its contents. When enabled and the carry input is active, the counters increment on the LOW-to-HIGH transition of the CLOCK input, CP. Thus, with this instruction applied, counting can be controlled by the carry inputs.

The REINITIALIZE COUNTERS instruction also is Control Mode dependent. In Control Modes 0, 2, and 3, the contents of the Address Register and Word Count Register are transferred to the respective Address Counter and Word Counter; in Control Mode 1, the content of the Address Register is transferred to the Address Counter and the Word Counter is cleared. The REINITIALIZE COUNTERS instruction allows a data transfer operation to be repeated without reloading the address and word count from the DATA lines.

5-272

| 2 | 4 | 10 | Octal<br>Code | Function                     | Mnemonic | Control<br>Mode | Word<br>Reg. | Word<br>Counter | Address<br>Reg. | Address<br>Counter | Control<br>Register                 | Data<br>D <sub>0</sub> -D <sub>7</sub>          |

|---|---|----|---------------|------------------------------|----------|-----------------|--------------|-----------------|-----------------|--------------------|-------------------------------------|-------------------------------------------------|

| L | L | L  | 0             | WRITE<br>CONTROL<br>REGISTER | WRCR     | 0,1,2,3         | HOLD         | HOLD            | HOLD            | HOLD               | D <sub>0</sub> -D <sub>2</sub> → CR | INPUT                                           |

| L | L | н  | 1             | READ<br>CONTROL<br>REGISTER  | RDCR     | 0,1,2,3         | HOLD         | HOLD            | HOLD            | HOLD               | HOLD                                | CR → D <sub>0</sub> -D <sub>2</sub><br>(Note 1) |

| L | н | L  | 2             | READ<br>WORD<br>COUNTER      | RDWC     | 0,1,2,3         | HOLD         | HOLD            | HOLD            | HOLD               | HOLD                                | WC⊸D                                            |

| L | н | н  | 3             | READ<br>ADDRESS<br>COUNTER   | RDAC     | 0,1,2,3         | HOLD         | HOLD            | HOLD            | HOLD               | HOLD                                | AC→D                                            |

|   |   |    |               | REINITIALIZE                 |          | 0,2,3           | HOLD         | WCR - WC        | HOLD            | AR→AC              | HOLD                                | Z                                               |

| н | L | L  | 4             | COUNTERS                     | RE1N     | 1               | HOLD         | ZERO → WC       | HOLD            | AR→AC              | HOLD                                | Z                                               |

| н | L | н  | 5             | LOAD<br>ADDRESS              | LDAD     | 0,1,2,3         | HOLD         | HOLD            | D⊸AR            | D⊸AC               | HOLD                                | INPUT                                           |

|   |   |    | +             | LDAD                         |          | 0,2,3           | D→WR         | D→WC            | HOLD            | HOLD               | HOLD                                | INPUT                                           |

| н | н | L  | 6             | WORD<br>COUNT                | LDWC     | 1               | D.WR         | ZERO → WC       | HOLD            | HOLD               | HOLD                                | INPUT                                           |

|   |   |    |               |                              |          | 0,1,3           | HOLD         | ENABLE<br>COUNT | HOLD            | ENABLE<br>COUNT    | HOLD                                | z                                               |

| н | н | н  | 7             | ENABLE<br>COUNTERS           | ENCT     | 2               | HOLD         | HOLD            | HOLD            | ENABLE<br>COUNT    | HOLD                                | Z                                               |

CR = Control Reg. WCR = Word Count Reg. AR = Address Reg. WC = Word Counter AC = Address Counter D = Data

WCR = Word Count Reg.

L = LOW

WC = Word Counter

H = HIGH

D = Data

Z = High Impedance

Note 1: Data Bits D3-D7 are high during this instruction.

### APPLICATIONS

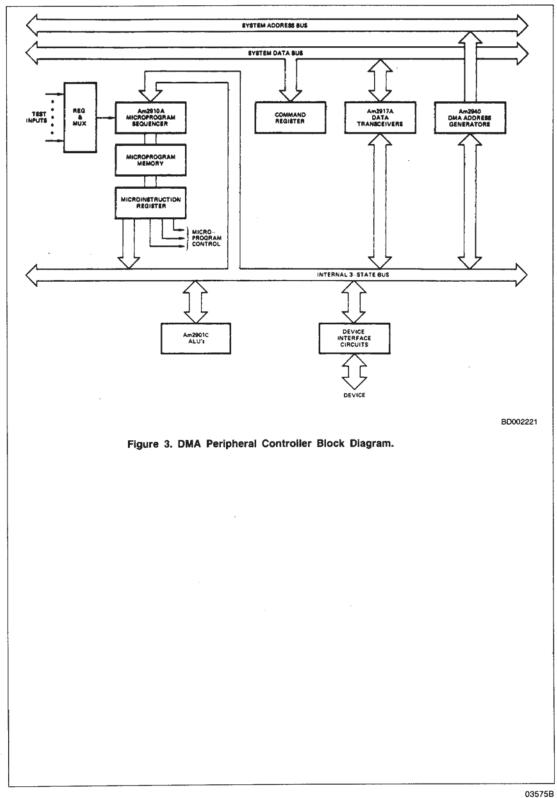

The Am2940 is designed for use in peripheral controllers with DMA capability or in any other system which transfers data to or from sequential locations of a memory. One or more Am2940's can be used in each peripheral controller of a distributed DMA system to provide the memory address and word count required for DMA operation.

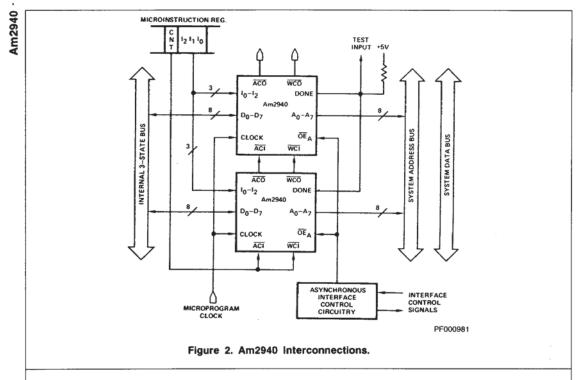

Figure 3 shows a block diagram of an example microprogrammed DMA peripheral controller. The Am2910A Microprogram Sequencer, Microprogram Memory, and the Microinstruction Register form the microprogram control portion of this peripheral controller. The Am2940 generates the memory address and maintains the word count required for DMA operation. An internal three-state bus provides the communication path between the Microinstruction Register, the Am2917 Data Transceivers, the Am2940, the Am2901C Microprocessor, and the Device Interface Circuitry. The Am2940 interconnections are shown in detail in Figure 2. Two Am2940's are cascaded to generate a sixteen-bit address. The Am2940 ADDRESS and DATA output current sink capability is 24mA over the commercial operating range. This allows the Am2940's to drive the System Address Bus and Internal Three-State Bus directly, thereby eliminating the need for separate bus drivers. Three-bits in the Microinstruction Register provide the Am2940 Instruction Inputs, I<sub>0</sub>-I<sub>2</sub>. The microprogram clock is used to clock the Am2940's and, when the ENABLE COUNTERS instruction is applied, address and word counting is controlled by the CNT bit of the Microinstruction Register. 5

Asynchronous interface control circuitry generates System Bus control signals and enables the Am2940 Address onto the System Address Bus at the appropriate time. The opencollector DONE outputs are dot-anded and used as a test input to the Am2910A Microprogram Sequencer.

5-273

## ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                | 65°C to +150°C   |

|------------------------------------|------------------|

| Ambient Temperature Under Bias     | 55°C to +125°C   |

| Supply Voltage to Ground Potential |                  |

| Centinuouo                         | -0.5V to $+7.0V$ |

| Continuous                        |                            |

|-----------------------------------|----------------------------|

| DC Voltage Applied to Outputs For |                            |

|                                   | $0.5V$ to $\pm V_{00}$ may |

| High Output State0.5V to + v    | CC max      |

|---------------------------------|-------------|

| DC Input Voltage0.5V to         | 5.5V + 5.5V |

| DC Output Current, into Outputs | 30mA        |

| DC Input Current30mA to         | + 5.0mA     |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **OPERATING RANGES**

#### Commercial (C) Devices

Temperature ...... 0°C to +70°C Supply Voltage ...... + 4.75V to + 5.25V Am2940

Military (M) Devices

Temperature .....-55°C to +125°C Supply Voltage ..... +4.5V to +5.5V Operating ranges define those limits over which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters | Description                              |                                                                          | Test Cond                                            | dition                                  | s (Note 2               | 2)                                                         | Min  | Typ<br>(Note 1) | Max   | Units |

|------------|------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|-------------------------|------------------------------------------------------------|------|-----------------|-------|-------|

|            | · · · ·                                  | V <sub>CC</sub> = MIN,                                                   | MIL I                                                | он ≖ -                                  | 1.0mA                   |                                                            |      |                 |       |       |

| VOH        | Output HIGH Voltage                      | $V_{CC} = MIN,$<br>$V_{IN} = V_{IH}$ or $V_{IL}$ COM'L $i_{OH} = -2.6mA$ |                                                      |                                         |                         | 2.4                                                        |      |                 | Volts |       |

|            |                                          | V <sub>CC</sub> = Min.,                                                  |                                                      | ACO                                     |                         | <sub>OL</sub> = 8.0mA<br>L I <sub>OL</sub> = 12mA          |      |                 | 0.5   | Volts |

| VOL        | Output LOW Voltage                       | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>I</sub><br>(Note 5)          | A0-7.                                                | A <sub>0-7</sub> , D <sub>0-7</sub>     |                         | MIL I <sub>OL</sub> = 16mA<br>COM'L I <sub>OL</sub> = 24mA |      |                 | 0.5   | Volts |

| VIH        | Input HIGH Level (Note 4)                | Guaranteed inp                                                           | Guaranteed Input Logical HIGH voltage for all inputs |                                         | 2.0                     |                                                            |      | Volts           |       |       |

| VIL        | Input LOW Level (Note 4)                 | Guaranteed Input Logical LOW voltage for all inputs                      |                                                      |                                         |                         |                                                            |      | 0.8             | Volts |       |

|            | Input Clamp Voltage                      | $V_{CC} = MIN, I_{IN} = -18mA$                                           |                                                      |                                         |                         |                                                            |      | - 1.5           | Voits |       |

| h          | Input LOW Current                        | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.5V<br>All Others              |                                                      |                                         |                         |                                                            |      | -0.15           | mA    |       |

| <u>н</u> н | Input HIGH Current                       | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7V<br>All Others              |                                                      |                                         |                         |                                                            |      | 150<br>40       | дц    |       |

| lasu       | Output Leakage on DONE                   | Vcc = MAX, V                                                             | /o = 5.5V                                            |                                         |                         |                                                            |      |                 | 250   | μA    |

| ICEX       | Input HIGH Current                       | VCC = MAX, V                                                             |                                                      |                                         |                         |                                                            |      |                 | 1.0   | mA    |

| Isc        | Output Short Circuit Current<br>(Note 3) | V <sub>CC</sub> = MAX +                                                  |                                                      | 0.5V                                    |                         |                                                            | - 30 |                 | -85   | mA    |

|            | (1010 0)                                 |                                                                          |                                                      |                                         |                         | A0-7                                                       |      |                 | - 50  |       |

| IOZL       |                                          | Vcc = MAX                                                                | Vo                                                   | UT = 0.                                 | .5V                     | D <sub>0-7</sub>                                           |      |                 | - 150 |       |

|            | Output OFF Current                       | $\overline{OE} = 2.4V$                                                   |                                                      |                                         |                         | A <sub>0-7</sub>                                           |      |                 | 50    | μΑ    |

| ЮZH        |                                          | 0E = 2.4V                                                                | Vo                                                   | V <sub>OUT</sub> = 2.4 D <sub>0-7</sub> |                         |                                                            |      | 150             |       |       |

|            |                                          |                                                                          |                                                      |                                         | $T_A = 0^{\circ}C$      | to + 70°C                                                  |      |                 | 290   |       |

|            |                                          |                                                                          | Am2940D0                                             |                                         | T <sub>A</sub> = + 70°C |                                                            |      |                 | 235   |       |

| lcc        | Power Supply Current                     | V <sub>CC</sub> = MAX                                                    |                                                      | _                                       |                         | C to + 125°C                                               |      |                 | 315   | mA    |

|            | 1                                        |                                                                          | Am2940DM, FM T <sub>C</sub> = + 125°C                |                                         | 5°C                     |                                                            |      | 225             | 1     |       |

Notes: 1.

.

Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

These input levels provide no guaranteed noise immunity and should only be static tested in a noise-free environment (not functionally tested)

tunctionally tested). 5.  $I_{OL}$  limit on A<sub>i</sub> and D<sub>i</sub> (i = 0 to 7) applies to either output individually, but not both at the same time. The sum of the loading on A<sub>i</sub> plus D<sub>i</sub> is limited to 24mA MIL or 32mA COM'L.

03575B Refer to Page 13-1 for Essential Information on Military Devices

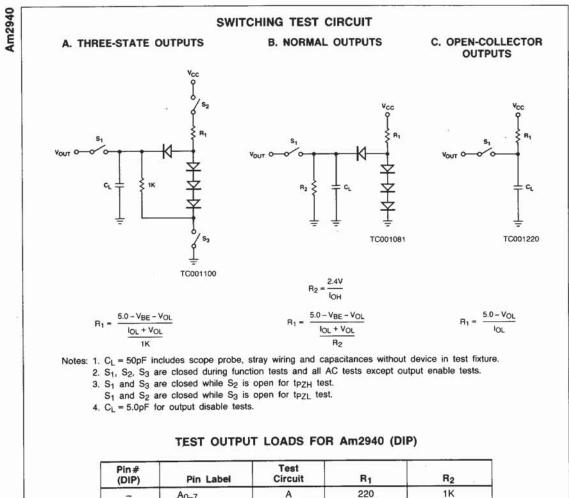

| Pin#<br>(DIP) | Pin Label        | Test<br>Circuit | R <sub>1</sub> | R <sub>2</sub> |

|---------------|------------------|-----------------|----------------|----------------|

| -             | A0-7             | A               | 220            | 1K             |

| -             | D <sub>0-7</sub> | A               | 220            | 1K             |

| 6             | ACO              | В               | 470            | 2.4K           |

| 7             | DONE             | С               | 270            | -              |

| 10            | WCO              | В               | 470            | 2.4K           |

For additonal information on testing, see section "Guidelines on Testing Am2900 Family Devices."

, 03575B Refer to Page 13-1 for Essential Information on Military Devices

### SWITCHING CHARACTERISTICS

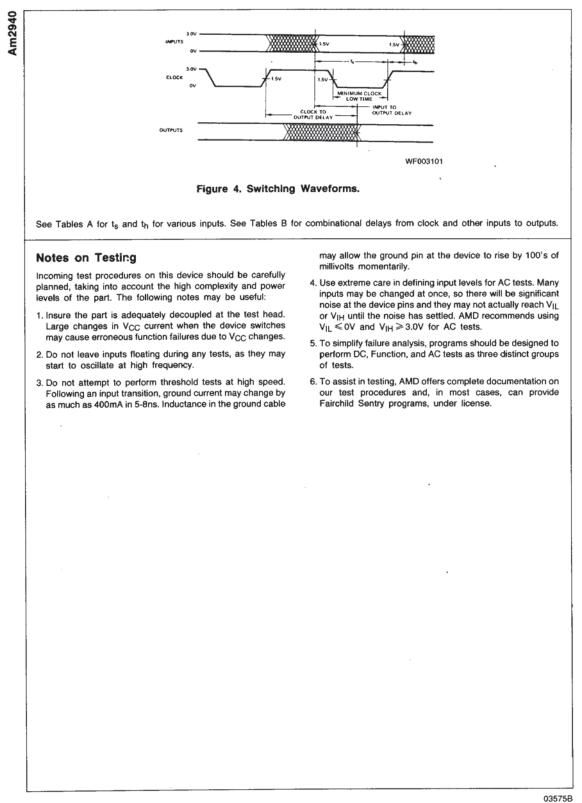

The tables below define the Am2940 switching characteristics. Tables A are set-up and hold times relative to the clock LOW-to-HIGH transition. Tables B are combinational delays. Tables C are clock requirements. All measurements are made at 1.5V with input levels at 0V or 3V. All values are in ns with  $C_L = 50$ pF except output disable times ( $\overline{OE}$  to A and I to D) which are specified or a 5pF load.

# I. GUARANTEED CHARACTERISTICS OVER COMMERCIAL OPERATING RANGE

Am2940DC (T<sub>A</sub> = 0 to +70°C, V<sub>CC</sub> = 4.75 to 5.25V, C<sub>L</sub> = 50pF)

### A. Set-up and Hold Times (Relative to clock LOW-to-HIGH transition)

| Input            | ts | t <sub>h</sub> |

|------------------|----|----------------|

| D <sub>0-7</sub> | 24 | 4              |

| l012             | 46 | 5              |

| ACI              | 30 | 4              |

| WCI<br>(Note 1)  | 30 | 3              |

| Input            | ACO | WCO | A <sub>0-7</sub> | DONE | D <sub>0-7</sub> |

|------------------|-----|-----|------------------|------|------------------|

| ACI              | 20  | -   | -                | -    | -                |

| WCI<br>(Note 2)  | -   | 20  | -                | 46   | -                |

| l <sub>0-2</sub> |     |     |                  | -    | 37               |

| CP<br>(Note 3)   | 58  | 58  | 54               | 85   | -                |

**B.** Combinational Delays

### **C. Clock Requirements**

| Minimum Clock LOW Time  | 23 | ns  |

|-------------------------|----|-----|

| Minimum Clock HIGH Time | 34 | ns  |

| Maximum Clock Frequency | 17 | MHz |

#### **D. Enable/Disbable Times**

| From             | То               | Disable | Enable |    |

|------------------|------------------|---------|--------|----|

| l <sub>012</sub> | D <sub>0-7</sub> | 35      | 35     | ns |

| ŌĒ               | A <sub>0-7</sub> | 25      | 25     | กร |

# II. GUARANTEED CHARACTERISTICS OVER MILITARY OPERATING RANGE

Am2940DM, FM (T<sub>C</sub> = -55 to + 125°C, V<sub>CC</sub> = 4.5 to 5.5V, C<sub>L</sub> = 50pF)

5-277

### A. Set-up and Hold Times (Relative to clock LOW-to-HIGH transition)

| Input            | ts | th |

|------------------|----|----|

| D <sub>0-7</sub> | 27 | 6  |

| l <sub>012</sub> | 49 | 5  |

| ACI              | 34 | 5  |

| WCI<br>(Note 1)  | 34 | 5  |

### **C. Clock Requirements**

| Minimum Clock LOW Time  | 23 | ns  |

|-------------------------|----|-----|

| Minimum Clock HIGH Time | 35 | ns  |

| Maximum Clock Frequency | 16 | MHz |

### **B.** Combinational Delays

| Input           | ACO | WCO | A <sub>0-7</sub> | DONE | D <sub>0-7</sub> |

|-----------------|-----|-----|------------------|------|------------------|

| ACI             | 21  | -   | -                | -    | -                |

| WCI<br>(Note 2) |     | 21  | -                | 54   | -                |

| I0-I2           | -   | -   | -                | -    | 41               |

| CP<br>(Note 3)  | 64  | 64  | 62               | 88   | -                |

### D. Enable/Disable Times

| From | То               | Disable | Enable |    |

|------|------------------|---------|--------|----|

| l012 | D <sub>0-7</sub> | 42      | 42     | ns |

| ŌĒ   | A <sub>0-7</sub> | 30      | 30     | ns |

Control modes 0, 1, and 3 only. Notes: 1. 2. WCI to DONE occurs only in control modes 0

and 1. 3. CP to DONE occurs only in control modes 0, 1, and 2.

03575B

Refer to Page 13-1 for Essential Information on Military Devices

Am2940

5