# silicon systems®

# SSI 32C452 Storage Controller

# **Preliminary Data**

July, 1990

#### DESCRIPTION

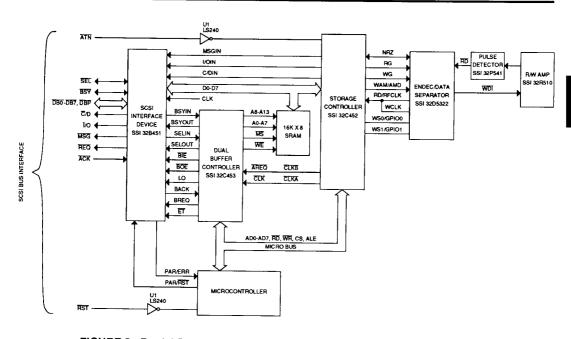

The SSI 32C452 Storage Controller is a CMOS device that provides the basis for an intelligent Winchester disk drive controller capable of non-interleaved data transfers at rates up to 20 Mbit/s. When combined with a microprocessor, memory and a buffer management device such as the SSI 32C453, the SSI 32C452 implements a powerful and cost-efficient peripheral controller solution. It also has the flexibility to be used in SCSI systems.

The SSI 32C452 includes a control sequencer with a writeable control store, and configuration/status registers which can be programmed to support standard and custom interface protocols for storage controllers. Access to the control store and registers is accomplished through the microprocessor interface which is optimized for 8 bit, multiplexed address/data bus processors such as the 8085. It also has the flexibility to interface with most standard 8-bit microprocessors. This organization allows the controller firmware to be stored in an EPROM or the host and down-loaded to the SSI 32C452, and means wide flexibility of the control functions performed by the device.

#### **FEATURES**

- Supports ST506/412, ST412HP, SA100, SMD, ESDI and custom Interfaces

- Operates with 16 MHz microprocessors

- Internal RAM-based control sequencer

- Internal user programmable ECC to 32 bits

- Non-interleaved data transfer to 20 Mbit/s

- Hard or soft sector formats

- Programmable sector lengths up to a full track

- High performance, low power CMOS device

- Plug and software compatible with AIC-010F Storage Controller

- Single 5 volt supply

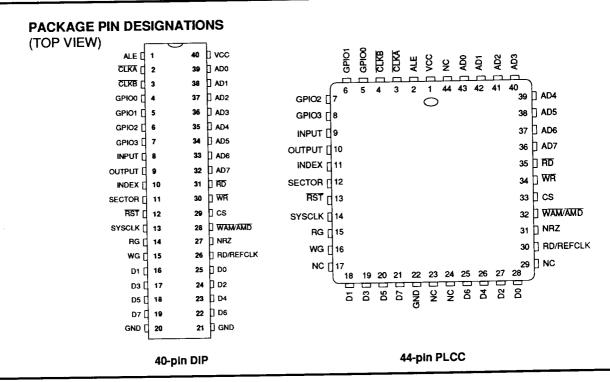

- Available in 44-pin PLCC or 40-pin DIP package

#### **BLOCK DIAGRAM**

CAUTION: Use handling procedures necessary for a static sensitive components

#### **DESCRIPTION** (Continued)

The SSI 32C452 performs all the controller functions for the peripheral device, such as serialization/deserialization, ECC generation and checking on the data stream. It also handles overhead information such as address marks, gaps and sector ID fields. If an ECC error is detected during a read, the syndrome is saved so that defects can be corrected. The ECC polynomial and register length can be programmed or bypassed entirely so that external ECC hardware can be used.

#### **FUNCTIONAL DESCRIPTION**

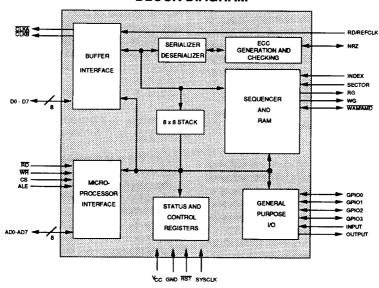

The major functional elements and data paths of the SSI 32C452 are shown in the block diagram.

The SSI 32C452 performs the functions to interface a serial data storage device such as a Winchester disk drive, to a parallel bus interface for data processing on a byte wide basis. The functions necessary to accurately make this conversion are serialization/deserialization, error detection and correction, and data path control. The SSI 32C452 also has general purpose interface lines to further facilitate control of the data storage device or parallel interface. An eight byte stack allows data to be saved and reviewed by the microprocessor for error handling purposes. The internal sequencer performs most of the operations in conjunction with the control and status registers. The sequencer program is contained in internal sequencer RAM, which is easily (re)programmed providing almost infinite flexibility in communcations protocols and control features. A microprocessor effects both initialization and control of the SSI 32C452 by writing to and reading from the internal registers, sequencer RAM, stack and general purpose I/O circuitry. The microprocessor interface block of the SSI 32C452 provides the communication and control for the SSI 32C452 to the microprocessor.

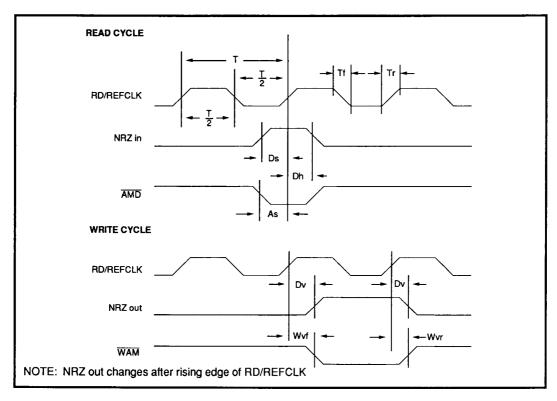

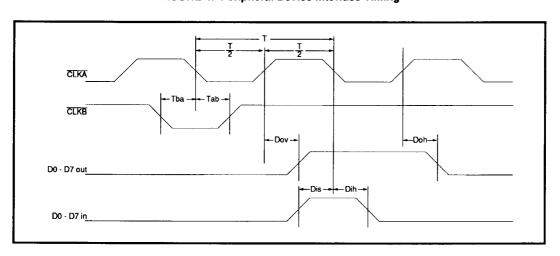

The **buffer Interface** includes a bidirectional data bus that exchanges data bytes between an external buffer memory and the serializer/deserializer. It generates two clocks, CLKA and CLKB which control all accesses to the buffer memory. All buffer memory cycles must be synchronous with CLKA, which is derived from the RD/REFCLK input during data transfers and from SYSCLK otherwise. The internal register CLKCON contains control bits which define the relationship between

these source clocks and CLKA. The CLKB signal is asserted whenever a new data byte must be transferred (ie. when the serializer/deserializer is full during a read operation or empty during a write operation). The direction of the transfer is determined from the state of the read gate (RG) and write gate (WG) lines. A CLKB cycle is used to force the buffer control device (eg. an SSI 32C453) to reserve the next buffer memory access for the SSI 32C452, since peripheral transfers take precedence over the asynchronous host transfers. In order to allow host transfers to keep up with peripheral transfers, the CLKA rate selected should be at least twice the word transfer rate of the peripheral.

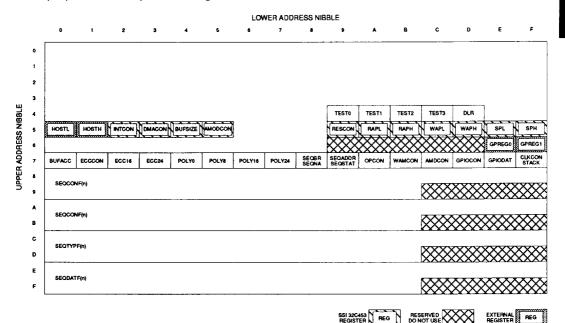

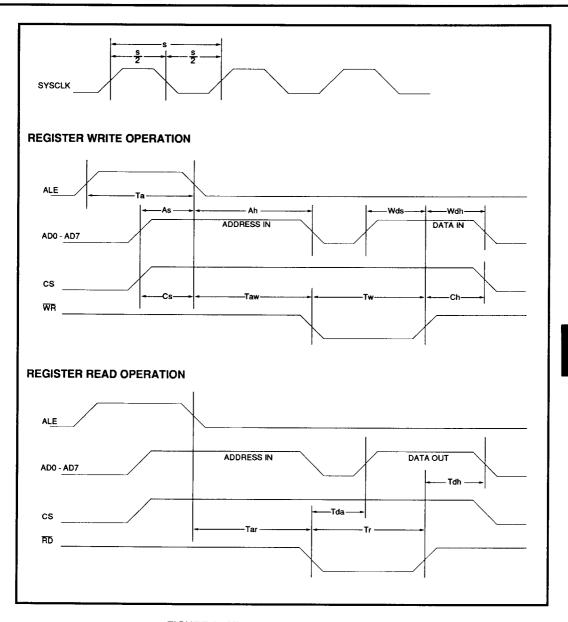

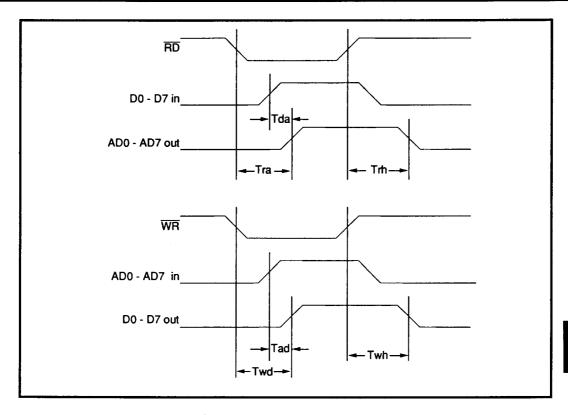

The microprocessor interface decodes microprocessor read and write requests and provides access to the appropriate register or internal memory location. Since both data and address information are carried on the multiplexed bus lines AD0-AD7, address information is latched from the bus on the falling edge of the microprocessor signal ALE (address latch enable). When  $\overline{CS}$  is asserted along with either  $\overline{RD}$  or  $\overline{WR}$ , the register whose address was previously latched is selected. The addresses and names of all the accessible registers are shown in the Register Address Map, Figure 1. The microprocessor should not read or write the sequencer RAM while the sequencer is running, since there is no circuitry to resolve conflicting accesses and incorrect sequencer operation will result.

The status and control registers make status information available to the microprocessor and allow the device to be configured for a wide variety of peripheral control applications. The microprocessor can monitor the status of transfers in progress and control the ECC register operation, the ECC polynomial, the clock generation hardware and the sequencer program execution. The microprocessor also has access to the sequencer's microprogram RAM so that it loads the microcode for all controller operations.

The serializer/deserializer circuit interfaces the parallel buffer memory bus to the serial NRZ data stream of the peripheral device. Byte synchronism is maintained with a bit ring, which is an 8 bit recirculating shift register clocked by the peripheral bit clock. During a sector write, the bit ring is initialized explicitly with a sequencer instruction. The bit ring continues to operate until the end of the field (ECC written or read) and causes CLKB to be asserted once for each data byte to be transferred. During write operations, the sequencer

may cause address marks and sync patterns to be loaded into the serializer instead of data bytes. These special patterns are contained in a sequencer instruction and are transferred to the serializer over an internal byte wide data path. During read operations, bytes of overhead information may be routed to the stack or sequencer for comparison against target values. This process is controlled by the control field (SEQCONF) in each sequencer instruction.

The eight byte recirculating **stack** may be used to capture read data for later examination by the microprocessor. Data is pushed onto the stack under sequencer control. The control bit STACKEN in the sequencer instruction field SEQCONF directly controls the stack. If more than 8 bytes are written to the stack, only the last 8 will be saved. When a data byte is read from the top of the stack by the microprocessor via the STACK register, the data is recirculated to the bottom of the stack, allowing the stack contents to be examined more than once without the use of temporary storage in the microprocessor or buffer.

Serial peripheral data is passed through a variable

length shift register with programmable exclusive OR feedback that performs ECC generation and checking. The feedback taps for the desired ECC polynomial are selected in the four registers POLY0 - POLY24 and the polynomial length is determined by the LEN bits in ECCCON. In addition, the ECC register may be operated either under sequencer or microprocessor control. During read operations, the contents of the ECC register are compared to the actual ECC field read from the peripheral. If there is a mismatch, the error syndrome is available for error correction. The ECC polynomial may be reversed to allow hardware computation of the error location, relieving the microprocessor of the burden of this lengthy calculation. During writes to the peripheral, the computed ECC word can be appended to each data or address field. The sequencer data type field (SEQDATF) indicates when ECC bytes are to be written or checked during a peripheral transfer.

The **sequencer** controls the time critical operations of the SSI 32C452. It executes programs stored in the 28 word by 32 bit sequencer RAM, and can be pro-

FIGURE 1: Register Address Map

#### FUNCTIONAL DESCRIPTION (continued)

grammed to support hard and soft sectored read, write. search and verify operations for a wide variety of Winchester disk drives and other peripherals. The sequencer RAM is loaded by writing to the sequencer instruction registers as outlined in the Sequencer Instructions section of this data sheet. Each instruction is comprised of four bytes. Each of the four bytes represents a function of the sequencer operation. They are address field, control field, data type field, and data field. The organization of these fields is shown in the Register Bit Map, Figure 2. The Sequencer Registers provide control from and status to the microprocessor and sequencer. They contain branch, next and start addresses, and sequencer status information. The SEQUENCER STATUS register provides informaton on the sequencer state such as whether an ECC error occurred, a compare equal or low occurred, if the branch condition or address mark is active, or whether the sequencer is halted.

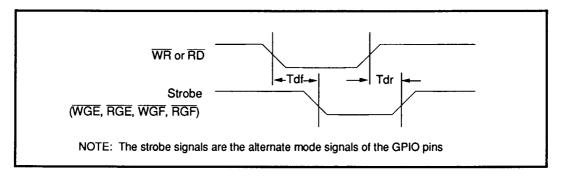

The general purpose I/O section has four general purpose I/O lines GPIO0 - GPIO3, and the INPUT pin which are accessible through the internal general purpose input/output registers. They are available for user defined functions such as Winchester disk or host interface control. The functionality of the GPIO0 -GPIO3 pins is programmed in the GPIOCON and GPIODAT registers. They can act as I/O's asserted or read through the GPIODAT register, or they can be programmed to decode microprocessor access to addresses 6EH and 6FH eliminating the need for external decode. The INPUT signal can be programmed in the SEQADRF RAM (registers) to affect sequencer operation and the state of the pin read from the GPIODAT register. The other general purpose line, OUTPUT is controlled directly by the sequencer to synchronize it with external circuitry. The OUT bit of the GPIODAT register reflects the state of the output pin.

#### PIN DESCRIPTION

#### **GENERAL**

| NAME   | DIP   | PLCC | TYPE | DESCRIPTION                                                                                                                                                                                        |

|--------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vcc    | 40    | 1    | 1    | POWER SUPPLY +5 volts                                                                                                                                                                              |

| GND    | 20-21 | 22   |      | GROUND                                                                                                                                                                                             |

| RST    | 12    | 13   | I    | RESET - Active low signal halts the sequencer, sets output pins RG, WG, WAM and NRZ low, forces the GPIO pins into a high impedance state and resets a number of the registers as described below. |

| SYSCLK | 13    | 14   | 1    | SYSTEM CLOCK - Clock input in the range of 1.5 MHz to 16 MHz                                                                                                                                       |

#### MICROPROCESSOR INTERFACE

| ALE | 1  | 2  | ı | ADDRESS LATCH ENABLE - Falling edge latches register address from AD0-7 pins.              |

|-----|----|----|---|--------------------------------------------------------------------------------------------|

| cs  | 29 | 33 | l | CHIP SELECT- Active high signal enables device to respond to microprocessor read or write. |

## PIN DESCRIPTION (continued)

| NAME    | DIP   | PLCC  | TYPE | DESCRIPTION                                                                                                                                     |

|---------|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| WR      | 30    | 34    | ı    | WRITE STROBE - Active low signal causes the data on the address/data bus to be written to the addressed register if CS is also active.          |

| RD      | 31    | 35    | ı    | READ STROBE - Active low signal causes the contents of the addressed register to be placed on the address/ data bus if CS is also active.       |

| AD0-AD7 | 39-32 | 43-36 | I/O  | ADDRESS/DATA BUS - 8 bit bus which carries register address information and bi-directional data. These pins are high impedance when not in use. |

## **GENERAL PURPOSE I/O**

| GPIO0-3 | 4-7 | 5-8 | I/O | GENERAL PURPOSE I/O LINES - These lines can be programmed as an inputs or outputs which are accessed though the GPIODAT register. They may also be programmed to serve as active low outputs which decode microprocessor accesses to the following locations: |  |  |  |

|---------|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         |     |     |     | I/O pin Alternate output decode GPIO0 Write to 6EH GPIO1 Read from 6EH GPIO2 Write to 6FH GPIO3 Read from 6FH                                                                                                                                                 |  |  |  |

| INPUT   | 8   | 9   | I   | INPUT PIN - This dedicated input line may be read through the GPIODAT register or tested directly by the control sequencer.                                                                                                                                   |  |  |  |

| OUTPUT  | 9   | 10  | 0   | OUTPUT PIN - Dedicated output line which is derived directly from the control sequencer instruction field.                                                                                                                                                    |  |  |  |

#### **DISK DRIVE INTERFACE**

| INDEX  | 10 | 11 | 1 | INDEX PULSE - Active high disk drive index pulse input, must be at least one byte time long.                                                               |

|--------|----|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTOR | 11 | 12 | ı | SECTOR PULSE - Active high sector pulse input from disk drives that are hard sectored, must be at least one byte time long.                                |

| RG     | 14 | 15 | 0 | READ GATE - Active high output from control sequencer enables external phase-locked loop (PLL) to synchronize to read data stream from the storage device. |

7-27

## PIN DESCRIPTION (continued)

## **DISK DRIVE INTERFACE** (continued)

| NAME      | DIP | PLCC | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WG        | 15  | 16   | 0    | WRITE GATE - Active high output from control sequencer indicates valid write data to the storage device.                                                                                                                                                                                                                                      |

| RD/REFCLK | 26  | 30   | l    | READ/REFERENCE CLOCK - This input must be externally multiplexed to provide the PLL clock when read gate is active and the write oscillator clock at all other times. This pin must always be driven with a clock signal, even when RST is active.                                                                                            |

| NRZ       | 27  | 31   | 1/0  | NRZ DATA - This bi-directional pin provides write data when WG is active, and must be driven with read data when RG is active. Data must be in the NRZ format.                                                                                                                                                                                |

| WAM/AMD   | 28  | 32   | 1/0  | WRITE ADDRESS MARK/ADDRESS MARK DETECT- This bi-directional pin is used to write and detect address marks. When WG is active, a low level output of one bit time on this pin indicates that an address mark must be written. When RG is active, the peripheral must provide an active low input to indicate the detection of an address mark. |

#### **BUFFER INTERFACE**

| CLKA  | 2              | 3              | 0   | CLOCK A - Clock signal which initiates host or controller accesses to the buffer memory on its falling edge. When either RG or WG is active, this output is derived from RD/REFCLK. At all other times it is derived from SYSCLK. The clock source is divided by 2 or 4 as programmed in the CLKCON register. |

|-------|----------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKB  | 3              | 4              | 0   | CLOCK B - This clock is used to reserve CLKA cycles for SSI32C452 data transfers. An active low pulse spanning a falling edge of CLKA indicates that the next falling edge on CLKA will be used by the SSI 32C452 to access the buffer memory.                                                                |

| D0-D7 | 16-19<br>22-25 | 18-21<br>25-28 | I/O | BUFFER DATA BUS - Bi-directional data bus that carries data to and from the buffer memory. Bus cycles are controlled by CLKA and CLKB. Direction of the transfer is determined by RG and WG. Note: refer to pin diagram for exact ordering of the pins.                                                       |

No connects on PLCC package: 17, 23, 24, 29, 44

| 25010752       | 4000000        | 07          | DC                              | D5       | D4         | D3     | D2      | D1       | DO      | READ<br>WRIT |  |

|----------------|----------------|-------------|---------------------------------|----------|------------|--------|---------|----------|---------|--------------|--|

| REGISTER       | ADDRESS<br>49H | D7          | D6                              |          | ENCER NEXT |        |         |          |         | R            |  |

| TEST0<br>TEST1 | 49H<br>4AH     |             | SEQUENCER CONTROL FIELD         |          |            |        |         |          |         |              |  |

| TEST2          | 4BH            |             | SEQUENCER COUNT/DATA TYPE FIELD |          |            |        |         |          |         |              |  |

| TEST3          | 40H            |             |                                 |          | SEQUENCER  |        |         |          |         | R            |  |

| DLR            | 4DH            |             |                                 |          | DATA LATCH |        |         |          |         | R            |  |

| BUFACC         | 70H            |             |                                 |          | BUFFER MEI |        |         |          |         | R/W          |  |

| ECCCON         | 71H            | LEN1        | LEN0                            | RESET    | SECTBR     | CLRECC | FEEDINH | ECCSHIFT | ECCIN   | R/W          |  |

| ECC16          | 72H            | ECC23       | ECC22                           | ECC21    | ECC20      | ECC19  | ECC18   | ECC17    | ECC0/16 | R            |  |

| ECC24          | 73H            | ECC31       | ECC30                           | ECC29    | ECC28      | ECC27  | ECC26   | ECC25    | ECC24   | R            |  |

| POLY0          | 74H            | F7          | F6                              | F5       | F4         | F3     | F2      | F1       | F0      | R/W          |  |

| POLY8          | 75H            | F15         | F14                             | F13      | F12        | F11    | F10     | F9       | F8      | R/W          |  |

| POLY16         | 76H            | F23         | F22                             | F21      | F20        | F19    | F18     | F17      | F16     | R/W          |  |

| POLY24         | 77H            | UNUSED      | F30                             | F29      | F28        | F27    | F26     | F25      | F24     | R/W          |  |

| SEQBR          | 78H            |             | UNUSED                          | L        | BRADR4     | BRADR3 | BRADR2  | BRADR1   | BRADR0  | ] w          |  |

| SEQNA          | 78H            | TEST POINTS |                                 |          | NADR4      | NADR3  | NADR2   | NADR1    | NADR0   | R            |  |

| SEQADDR        | 79H            |             | UNUSED                          |          | STADR4     | STADR3 | STADR2  | STADR1   | STADR0  | ] w          |  |

| SEQSTAT        | 79H            | AMACTIVE    | DATATRANS                       | BRACTIVE | STOPPED    | UNUSED | ECCERR  | COMPLO   | COMPEQ  | R            |  |

| OPCON          | 7AH            | CARRYINH    | UNUSED                          | TRANSINH | SEARCHOP   | SYNDET | NRZDAT  | SECTORP  | INDEXP  | R/M          |  |

| WAMCON         | 7BH            |             |                                 |          | AM7        | - AMO  |         |          |         | R/M          |  |

| AMDCON         | 7CH            |             |                                 |          | AMD7       | AMD0   |         |          |         | R/M          |  |

| GPIOCON        | 7DH            | RGFSEL      | WGFSEL                          | RGESEL   | WGESEL     | GPDIR3 | GPDIR2  | GPDIR1   | GPDIR0  | R/M          |  |

| GPIODAT        | 7EH            | UNU         | SED                             | OUT      | INP        | GP3    | GP2     | GP1      | GP0     | R/W          |  |

| CLKCON         | 7FH            | CLKF2       | CLKF1                           | UNUSED   | CLKFO      | CLKINH | SYN2    | SYN1     | SYN0    | w            |  |

| STACK          | 7FH            |             |                                 |          | TOP OF     | STACK  |         |          |         | R            |  |

| SEQADDRF       | 80H            | BRCON2      | BRCON1                          | BRCON0   | NEXT4      | NEXT3  | NEXT2   | NEXT1    | NEXT0   | ₽.W          |  |

|                | 9BH ~          | 7           |                                 |          |            |        |         |          |         | ]            |  |

| SEQCONF        | AOH            | SETWG       | SETRG                           | RESWG    | STACKEN    | NRZINH | OUTPIN  | COMPEN   | DATEN   | R/M          |  |

|                | BBH ∠          | 7           |                                 |          |            | :      |         |          |         | ]            |  |

| SEQTYPF        | СОН            | CNT7/       | CNT6/                           | CNT5/    | CNT4       | CNT3   | CNT2    | CNT1     | CNTO    | R/M          |  |

|                | DBH ∠          | DTYP2       | DTYP1                           | DTYP0    |            |        |         |          |         | ]            |  |

| SEQDATF        | ,              |             |                                 |          | DATA       | FIELD  |         |          | _       | R/M          |  |

|                | 2              |             |                                 |          |            |        |         |          |         | ]            |  |

FIGURE 2: Register Bit Map

7-29

#### REGISTER DESCRIPTION

The microprocessor which controls the system has access to all the SSI 32C452 registers and sequencer RAM through its external memory address space. The SSI 32C452 and its companion device, the SSI 32C453 Dual Port Buffer Controller, are designed to occupy a single 256 byte page. The 8 bit page address is latched from pins AD0-AD7 on a falling edge of ALE and remains valid until the next ALE falling edge.

The external registers described at the end of this section are not implemented in either the SSI 32C452 or SSI 32C453, and are assumed to be implemented in external hardware. These external registers are not required for use with the SSI 32C452, but are included as applications information.

#### **ECC REGISTERS**

The core of the ECC circuit is a 32 bit shift register whose effective length may be programmed to be 16, 24 or 32 bits. This is accomplished in hardware by directing the input data to stage 16, 8 or 0 of the ECC

shift registers, ECC16 and ECC24, while its output is always bit 31, which is bit ECC31 of register ECC24.

The ECC polynomial to be implemented is programmed by the user into the ECC feedback registers, POLY0, POLY8, POLY16 and POLY24. Each bit in these registers enables or disables exlusive OR feedback to the output of the corresponding shift register stage. The feedback signal is the exclusive OR of the serial data stream with the output of shift register stage 31. An override bit in ECCCON forces normal shift register operation, regardless of the settings of the feedback control bits.

When WG or RG are active, the ECC shift register input is the serial read or write data and the shift clock is RD/REFCLK. When an ECC word is being written, feedback is disabled and the shift register output is substituted for the data stream. At other times the microprocessor may set the ECCIN bit explicitly and cause a single shift register clocking to occur. For further information on implementing an ECC polynomial see the Applications Information Section at the end of this data sheet.

| ECC | CONTROL WORK | D                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | NAME         | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |

| 0   | ECCIN        | ECC SERIAL INPUT - When both RG and WG are inactive, this bit becomes the input bit for the ECC shift register. The RD/REFCLK must always be active for correct operation of the device.                                                                                                                                                |

| 1   | ECCSHIFT     | ECC SHIFT CONTROL - When both RG and WG are inactive, a single shift of the ECC register will occur when this bit is set. It is automatically cleared again when the shift is complete.                                                                                                                                                 |

| 2   | FEEDINH      | ECC FEEDBACK INHIBIT - When this bit is set all feedback is inhibited and the ECC register functions as a simple shift register of the selected length.                                                                                                                                                                                 |

| 3   | CLRECC       | CLEAR ECC - If this bit is set when either RG or WG are active, the ECC syndrome will be cleared at the end of the read/write operation. If both are inactive, the syndrome will be cleared immediately.                                                                                                                                |

| 4   | SECTBR       | ENABLE SECTOR BRANCH - If the sequencer "branch on index or sector" instruction is executed and SECTBR is set, the sequencer will recognize the branch condition as true if either the INDEX or the SECTOR pin is active. If SECTBR is cleared, then the sequencer will only recognize the branch condition if the INDEX pin is active. |

## **ECC REGISTERS** (continued)

| ВІТ | NAME      | DESCRI                                     | PTION               |                                                                                                                                |

|-----|-----------|--------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 5   | RESET     |                                            |                     | nen this bit is set, the SSI 32C452 will be held in its reset state.  n RST is true.                                           |

| 6-7 | LEN0-LEN1 | ECC REG<br>follows:<br>LEN1<br>0<br>0<br>1 | LENO<br>0<br>1<br>0 | _ENGTH - These two bits select the ECC register length as  16 bit register 24 bit register illegal combination 32 bit register |

| ECC16 72H Read of | only |

|-------------------|------|

|-------------------|------|

| ECC  | ECC DATA          |                                                                                                                                                                                                                                                                                   |  |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ВІТ  | NAME              | DESCRIPTION                                                                                                                                                                                                                                                                       |  |

| 0    | ECC0/16           | ECC REGISTER LEADING BITS - This bit reflects the OR of all the ECC register bits from the input stage through bit 16. For 16 bit operation, this is bit 16. For 24 bit operation this is bit $8 + bit 9 + + bit 16$ . For 32 bit operation, this is bit $0 + bit 1 + + bit 16$ . |  |

| 1-7  | ECC17-ECC23       | ECC REGISTER BITS - These bits reflect the output of ECC shift register stages 17 to 23.                                                                                                                                                                                          |  |

| Rese | et State: Unknown |                                                                                                                                                                                                                                                                                   |  |

| ECC24 | 73H | Read only |

|-------|-----|-----------|

|       |     |           |

| ECC DATA             |             |                                                                                          |

|----------------------|-------------|------------------------------------------------------------------------------------------|

| ВІТ                  | NAME        | DESCRIPTION                                                                              |

| 0-7                  | ECC24-ECC31 | ECC REGISTER BITS - These bits reflect the output of ECC shift register stages 24 to 31. |

| Reset State: Unknown |             |                                                                                          |

7-31

## **ECC REGISTERS** (continued)

| PΛ | I VN |

|----|------|

|    |      |

74H

Read/Write

| ECC POLYNOMIAL |       |                                                                                                                                                                                                                                                                                                                            |

|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВІТ            | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                |

| 0-7            | F0-F7 | ECC POLYNOMIAL FEEDBACK - These bits enable or disable exclusive OR feedback of both the shift register output (bit 31) and the serial input to the output of shift register stages 0 to 7. These settings may be overriden by the FEEDINH bit in ECCCON. For ECC register lengths of 16 or 24 bits, F0-F7 are irrelevant. |

POLY8

75H

Read/Write

| ECC POLYNOMIAL |                |                                                                                                                                                                                      |  |

|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BIT            | NAME           | DESCRIPTION                                                                                                                                                                          |  |

| 0-7            | F8-F15         | ECC POLYNOMIAL FEEDBACK - These bits enable or disable exclusive OR feedback to the output of shift register stages 8 to 15. For register lengths of 16 bits, F8-F15 are irrelevant. |  |

| Reset          | t State: POLY8 | =00H                                                                                                                                                                                 |  |

#### POLY16

76H

Read/Write

| ECC  | POLYNOMIAL      |                                                                                                                               |

|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| ВІТ  | NAME            | DESCRIPTION                                                                                                                   |

| 0-7  | F16-F23         | ECC POLYNOMIAL FEEDBACK - These bits enable or disable exclusive OR feedback to the output of shift register stages 16 to 23. |

| Rese | t State: POLY16 | =00H                                                                                                                          |

#### POLY24

77H

Read/Write

| ECC        | POLYNOMIAL |                                                                                                                               |

|------------|------------|-------------------------------------------------------------------------------------------------------------------------------|

| ВІТ        | NAME       | DESCRIPTION                                                                                                                   |

| 0-6        | F24-F30    | ECC POLYNOMIAL FEEDBACK - These bits enable or disable exclusive OR feedback to the output of shift register stages 24 to 30. |

| 7          | unused     |                                                                                                                               |

| /<br>Reset | Unused     |                                                                                                                               |

7-32 0790 - rev.

# SEQUENCER STATUS AND CONTROL REGISTERS

The sequencer controls all the time-critical interactions with the peripheral storage device being controlled by the SSI 32C452. The instructions directly control disk drive interface lines, provide data for writing or comparison, determine the number of bytes handled and control the sequence of instruction execution. It is programmed by the user for maximum capability and variability. There are 28 instructions which are 32 bits wide. They are divided in to 4 byte wide fields. These fields are sequencer address, control, data type and data fields. These may be further divided into subfields as described in detail below. Examples are shown in the Applications Information section at the end of this data sheet.

The next address field of the sequencer instruction contains address and branching information. Each instruction is executed for the duration of the number of byte times specified in its count field. The specified

count is loaded into a down counter which clocks every 8 bit times. When the counter underflows execution of that instruction is terminated. A carry inhibit feature allows the counter to wrap around to a full count for fields which are more than 256 bytes long. Execution is passed to the instruction at the specified next address, unless a branch condition is specified in the instruction (e.g., ECC error or successful data comparison). In that case, execution passes to the address specified in the SEQBR register. Sequencer operation may also be conditionally stopped. The sequencer will always stop if execution passes to address 1FH, which is outside of the 28 word instruction control store.

The control field of the sequencer instruction is used to specify the state of RG and WG, to move data to the stack and to select data transfer or data comparison operations. The count field sets the duration of each instruction in byte times and is also used to select the type of data written, such as address marks or ECC bytes.

## SEQBR 78H Write only

| SEQU | JENCER BRANC       | CH ADDRESS                                                                                                                                                                                                                         |

|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВІТ  | NAME               | DESCRIPTION                                                                                                                                                                                                                        |

| 0-4  | BRADR0<br>- BRADR4 | BRANCH ADDRESS BITS - When a sequencer instruction with a branch condition is finished (i.e., the specified number of byte times have elapsed) and the specified condition did occur, execution will resume at this 5 bit address. |

| 5-7  | unused             |                                                                                                                                                                                                                                    |

| SEQNA | 78H | Read only |

|-------|-----|-----------|

|-------|-----|-----------|

| SEQUENCER NEXT ADDRESS |                  |                                                                                                                                                                                                                                  |

|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВІТ                    | NAME             | DESCRIPTION                                                                                                                                                                                                                      |

| 0-4                    | NADR0<br>- NADR4 | NEXT ADDRESS BITS- This reflects the 5 bit next address field of the sequencer instruction currently being executed. After the specified byte count, execution will proceed at this address provided no branch conditions occur. |

| 5-7                    |                  | Internal test points                                                                                                                                                                                                             |

| Reset State: Unknown   |                  |                                                                                                                                                                                                                                  |

## SEQUENCER STATUS AND CONTROL REGISTERS (continued)

**SEQADDR**

79H

Write only

| SEQUENCER START ADDRESS |                    |                                                                                                                                                                                                                                                               |

|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВІТ                     | NAME               | DESCRIPTION                                                                                                                                                                                                                                                   |

| 0-4                     | STADR0<br>- STADR4 | SEQUENCER START ADDRESS BITS - If the sequencer is currently halted, writing this register with an address in the range 00H to 1BH will cause sequencer execution to commence at that address. If this register is written with 1FH, the sequencer will halt. |

| 5-7                     | unused             |                                                                                                                                                                                                                                                               |

| Reset                   | State: 00H         |                                                                                                                                                                                                                                                               |

| SEQSTAT | 79H | Read only |

|---------|-----|-----------|

|---------|-----|-----------|

| SEQ   | JENCER STATUS |                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| віт   | NAME          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |

| 0     | COMPEQ        | COMPARE EQUAL - When a sequencer instruction enables the comparison operation, this bit reflects the result of all the byte comparisons performed (i.e., if it is set then all bytes compared so far have been equal.) If RG is enabled, the comparisons occur between the instruction's data field and the data bytes being read (or buffer memory if the SEARCHOP bit in OPCON is true as well). |

| 1     | COMPLO        | COMPARE LOW - Similar to COMPEQ, except that it indicates that in all comparisons the data field was smaller than the compared byte.                                                                                                                                                                                                                                                               |

| 2     | ECCERR        | ECC ERROR - This bit is set during RG active, upon reading the last ECC bit, if there was an error in the data read. The error syndrome will be stored in the ECC registers.                                                                                                                                                                                                                       |

| 3     | not used      |                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4     | STOPPED       | SEQUENCER STOPPED - This bit is set when the sequencer is stopped and its instruction address is 1FH.                                                                                                                                                                                                                                                                                              |

| 5     | BRACTIVE      | BRANCH ACTIVE - This is set when the branch condition specified in the current instruction has been satisfied. This means that the next address used will be taken from the SEQBR register. This bit is reset when the microprocessor reads this register.                                                                                                                                         |

| 6     | DATATRANS     | DATA TRANSFER - This bit is set when the current sequencer instruction is causing data to be transferred between the buffer memory and the peripheral device. This distinguishes the activity from a search or verification operation.                                                                                                                                                             |

| 7     | AMACTIVE      | ADDRESS MARK ACTIVE - This bit is set when the controller reads or writes an address mark or sync byte. It is reset after the ECC bytes are read or written, or when the sequencer is halted.                                                                                                                                                                                                      |

| Reset | State: 00H    |                                                                                                                                                                                                                                                                                                                                                                                                    |

#### **SEQUENCER INSTRUCTION REGISTERS**

The 4 fields of 8 bits comprising a single sequencer instruction are detailed below. They are presented as arrays of 28 bytes each, corresponding to the 28 instructions at sequencer addresses 0 to 1BH.

#### SEQADRF(n) 80H-9BH Read/Write

| BIT | NAME              | DESCRIPTION                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-4 | NEXTO-NEXT4       | NEXT ADDRES                                                                   | SS FIELD - This 5 bit field specifies the address of the next e executed when the current instruction has continued for the er of bytes.                                                                                                                                                                                                                                                                           |

| 5-7 | BRCON0<br>-BRCON2 | for the current in<br>current instructi<br>specifed, and the<br>in SEQBR. The | TROL FIELD - This 3 bit field specifies the branch condition instruction. When a branch condition is satisfied, execution of the on is not curtailed. It continues to execute for the full byte count en the sequencer proceeds with execution of the address specified branch condition used depends on the state of RG and data type TYPF). If RG is true and ECC bytes are being read, the following ins apply: |

|     |                   | BRCON2/1/0=                                                                   | 000 No branch                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                   |                                                                               | 001 Stop on ECC error                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                   |                                                                               | 010 Stop on comparison error                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                   |                                                                               | 011 Stop on ECC or comparison error                                                                                                                                                                                                                                                                                                                                                                                |

|     |                   |                                                                               | 100 Branch on good ECC and comparison                                                                                                                                                                                                                                                                                                                                                                              |

|     |                   |                                                                               | 101 Branch on ECC error                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                   |                                                                               | 110 Branch on comparison error                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                   |                                                                               | 111 Branch on ECC or comparison error                                                                                                                                                                                                                                                                                                                                                                              |

|     |                   | Otherwise, the                                                                | branch conditions are:                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                   | BRCON2/1/0=                                                                   | 000 No branch                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                   |                                                                               | 001 Stop if INPUT pin active                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                   |                                                                               | 010 Stop if INDEX or SECTOR pin active (see SECTBR bit                                                                                                                                                                                                                                                                                                                                                             |

|     |                   |                                                                               | of register ECCCON).                                                                                                                                                                                                                                                                                                                                                                                               |

|     |                   |                                                                               | 011 Stop if comparison error                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                   |                                                                               | 100 Branch on carry (from byte counter).                                                                                                                                                                                                                                                                                                                                                                           |

|     |                   |                                                                               | 101 Branch on ECC error                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                   |                                                                               | 110 Branch if INDEX or SECTOR pin active (see SECTBR                                                                                                                                                                                                                                                                                                                                                               |

|     |                   |                                                                               | bit of register ECCCON).                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                   |                                                                               | 111 Branch on comparison error                                                                                                                                                                                                                                                                                                                                                                                     |

7-35

## SEQUENCER INSTRUCTION REGISTERS (continued)

SEQCONF(n) A0H-BBH Read/Write

| SEQ  | UENCER CONTRO       | DL FIELD ARRAY                                                                                                                                                                                                                                                                                                                                                                              |

|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT  | NAME                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |

| 0    | DATEN               | DATA TRANSFER ENABLE - When this bit is set, the SSI 32C452 will generate CLKB requests to transfer data bytes to or from buffer memory, depending on whether WG or RG is active.                                                                                                                                                                                                           |

| 1    | COMPEN              | COMPARE ENABLE - When this bit is set and RG is active, read data bytes from the peripheral will be compared with the instruction data field (SEARCHOP reset in the OPCON register) or the buffer memory data (SEARCHOP set). The results of the comparisons are OR'ed together for the duration of the instruction and can be used for a branch condition or tested by the microprocessor. |

| 2    | OUTPIN              | OUPUT PIN CONTROL - This bit appears on the OUTPUT pin and may be used to synchronize external circuitry to the sequencer.                                                                                                                                                                                                                                                                  |

| 3    | NRZINH              | NRZ DATA INHIBIT - When RG is active and this bit is set, the NRZ data input will be ignored. This is useful while external data recovery circuits start up.                                                                                                                                                                                                                                |

| 4    | STACKEN             | STACK WRITE ENABLE - While this bit is set, bytes of NRZ data are pushed onto the recirculating stack.                                                                                                                                                                                                                                                                                      |

| 5    | RESWG               | RESET WRITE GATE - This bit causes the WG line to go inactive 4 bit times after the current instruction is finished (byte counter reaches 0).                                                                                                                                                                                                                                               |

| 6    | SETRG               | SET READ GATE - Provided WG is inactive, this bit sets RG, which will remain active until the ECC information is read or the sequencer is halted.                                                                                                                                                                                                                                           |

| 7    | SETWG               | SET WRITE GATE - When this bit is set and an instruction executed, the WG line will be activated after a delay of 4 bit times. WG will remain active until cleared by the RESWG bit or the sequencer is halted. WG will not be activated if RG is already active.                                                                                                                           |

| Rese | t State: The conten | its of the sequencer RAM are unchanged.                                                                                                                                                                                                                                                                                                                                                     |

## SEQTYPF(n) C0H-DBH Read/Write

| SEQU | SEQUENCER DATA TYPE FIELD ARRAY |                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| віт  | NAME                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |

| 0-4  | CNT0-CNT4                       | COUNT FIELD - The current sequencer instruction is executed for the number of byte times specified by the count field. If the DATEN bit is set, the count is specified as an 8 bit quantity (CNT0-CNT7). If DATEN is reset, the count is specified as a 5 bit quantity (CNT0-CNT4), and the upper three bits of this instruction field are interpreted as data type bits, described below. |

#### **SEQUENCER INSTRUCTION REGISTERS (continued)**

| ВІТ | NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | CNT5/DTYP0 | COUNT BIT 5 OR DATA TYPE 0 - When this bit is interpreted as a data type bit, it is used to initialize the bit ring with a single 1. This will occur at the next CLKA cycle. This starts CLKB so that write data bytes will be fetched from buffer memory. The bit ring will be cleared after the ECC is written. |

| 6   | CNT6/DTYP1 | COUNT BIT 6 OR DATA TYPE BIT 1 - When this bit is interpreted as a data type bit, it indicates that ECC information is being read or written.                                                                                                                                                                     |

| 7   | CNT7/DTYP2 | COUNT BIT 7 OR DATA TYPE BIT 2 - When this bit is being interpreted as a data type bit it indicates that an address mark is being written.                                                                                                                                                                        |

Note: When DATEN is reset, and CNT5/DTYP0, CNT6/DTYP1 and CNT7/DTYP2 are being interpreted as data type select bits, the upper 3 bits of the byte counter are forced to 0 regardless of the settings of the data type bits. When all 3 data type bits are 0, the data field is interpreted as normal binary data.

Reset State: The contents of the sequencer RAM are unchanged

SEQDATF E0H-FBH Read/Write

| SEQUENCER DATA FIELD ARRAY |           |                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT                        | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |

| 0-7                        | DAT0-DAT7 | DATA FIELD - When RG is active, the byte in this field is used for comparison operations. If WG is active, DATATRANS is set and TRANSINH (Transfer Inhibit bit in OPCON register) is set, the write data will come from this field. This allows the sequencer to generate the necessary overhead bytes while writing a sector. |

#### **DISK DRIVE INTERFACE REGISTERS**

The disk drive interface registers provide control and status for the interface of the SSI 32C452 to the disk drive (peripheral device), and for data transfer to the buffer or host.

| OPCON 7AH | Read/Write |

|-----------|------------|

|-----------|------------|

| OPE | OPERATION CONTROL WORD |                                                                                                                                                                                                                                                             |

|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВІТ | NAME                   | DESCRIPTION                                                                                                                                                                                                                                                 |

| 0   | INDEXP                 | INDEX PULSE DETECTED - This bit is set when an index pulse is encountered and reset each time the register is read. The bit will be reset even if the INDEX pin is true during the access.                                                                  |

| 1   | SECTORP                | SECTOR PULSE DETECTED - This bit is set when a sector pulse is encountered and cleared each time the register is read. The bit will be cleared even if the SECTOR pin is true during the read access. This bit is only used with hard-sectored disk drives. |

## **DISK DRIVE INTERFACE REGISTERS** (continued)

| BIT  | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | NRZDAT           | NRZ DATA IN - This bit is set when a rising edge is detected on the NRZ pin and RG is active. It is reset when the register is read.                                                                                                                                                                                                                                               |

| 3    | SYNDET           | SERIAL DATA SYNCHRONIZATION DETECT - Indicates that the bit ring is synchronized on byte boundaries, following detection of an address mark.                                                                                                                                                                                                                                       |

| 4    | SEARCHOP         | SEARCH OPERATION - Setting this bit will cause comparisons to occur between the contents of the buffer memory and the read data bytes from the peripheral. If SEARCHOP is reset, then read data bytes will be compared to the sequencer instruction data field.                                                                                                                    |

| 5    | TRANSINH         | DATA TRANSFER INHIBIT - If WG is active and this bit is set, then the write data will come from the sequencer instruction data field instead of the buffer memory. If RG is active and this bit is set, then the read data bytes are used for comparisons only and are not written to buffer memory. Setting this bit will suppress CLKB so that no buffer memory transfers occur. |

| 6    | Unused           |                                                                                                                                                                                                                                                                                                                                                                                    |

| 7    | CARRYINH         | SEQUENCER COUNTER CARRY INHIBIT - When this bit is set, the sequencer will not detect a carry (underflow) in its byte counter. This bit is reset when a carry occurs.                                                                                                                                                                                                              |

| Rese | t State: Unknown |                                                                                                                                                                                                                                                                                                                                                                                    |

WAMCON 7BH Read/Write

| 1 1 15 15 15                                                                                  |