# T7102A-X.25/X.75 Protocol Controller

### **Features**

- 24-bit address bus to address a 16-Mbyte address space

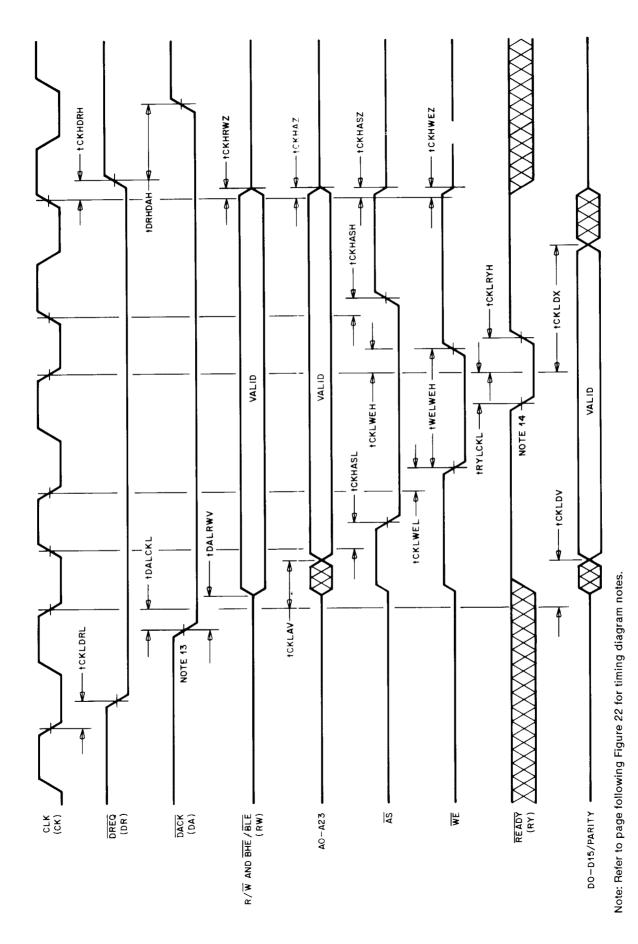

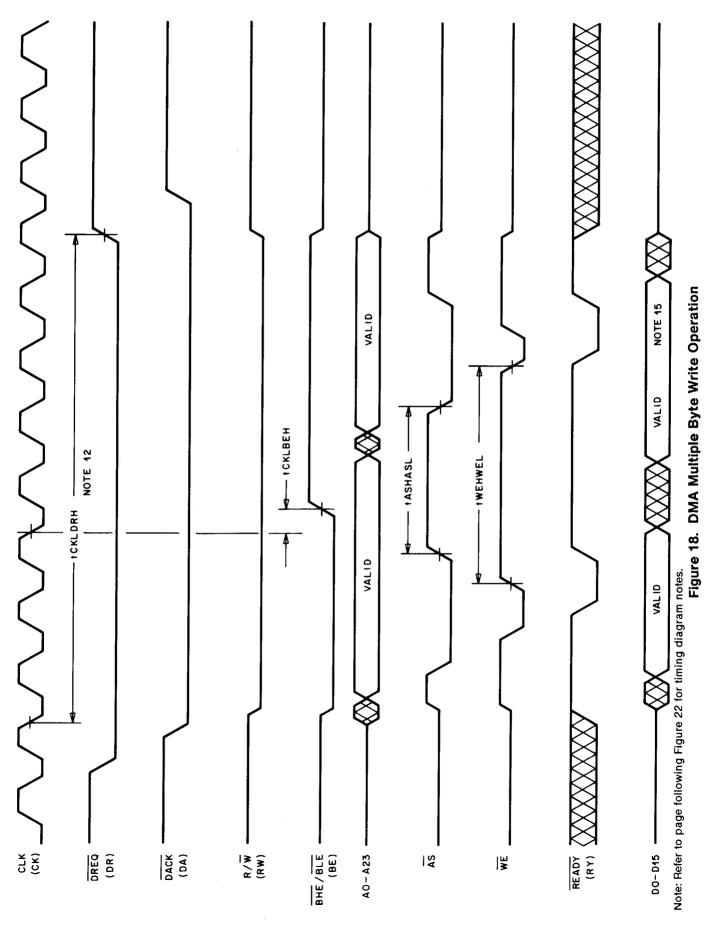

- Dual-channel DMA with standard interface, including DMA request, DMA acknowledge, DMA read, and DMA write

- Independently programmable T1 and T4 timers

- Programmable retransmission counter

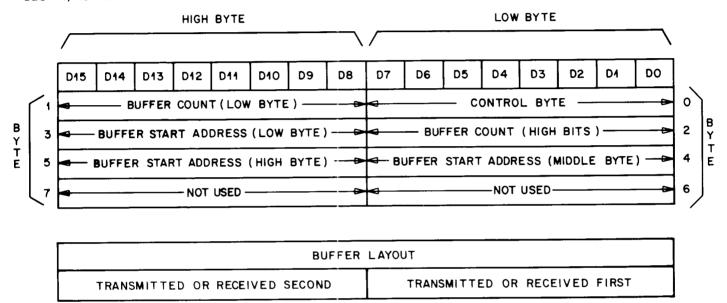

- Transmit and receive buffers accessed indirectly through a look-up table

- Programmable modulo-8 or modulo-128 frame sequence numbering

- Programmable window size (transmit and receive)

- Selectable 16-bit (CRC-CCITT) or 32-bit polynomial for frame checking sequence (FCS)

- Wait-state generator (on DMA side) for slow memory

- Programmable interframe flag fill

- Error detection and automatic recovery via packet retransmission

- Link initialization and supervision

- Independently programmable transmit and receive window size

- Password exchange mechanism for dial-up operation

- Programmable for X.25 or X.75 operation

- Supports 8-bit or 16-bit data buses

- Intel, Motorola, or WE® 32100 Microprocessor DMA interface (data bus)

- Sixteen programmable event counters, with optional interrupt capability

- Daisy-chain DMA structure for prioritycontrolled CPU interfaces

- Two independent test modes (far-end loopback and near-end loopback) to verify the XPC and its link

- Optional parity generation and checking across data bus interface on all DMA operations

- Six bidirectional address leads for accessing 51 internal XPC registers

- 2-MHz clock

- Single 5 V supply

# Description

The T7102A X.25/X.75 Protocol Controller (XPC) integrated circuit is an X.25/X.75 level 2 protocol controller. It is a single-chip LSI device available in a 70-pin pin-grid-array (PGA) package and is fabricated using N-channel silicon gate MOS technology. The T7102A XPC implements an augmented X.25 level 2 data communications standard for packet switching. The device satisfies the X.25 link level (level 2) requirements for a balanced link access procedure (LAPB) for data interchange over a synchronous full-duplex serial data link. The device also implements X.75 level 2 protocol, which is used in internetwork applications. The protocol controller is bit-oriented, with a maximum transmit and receive speed of 333 kb/s. A set of programmable registers controls and records vital events during data transmission.

# **User Information**

# **Pin Descriptions**

| -           |       |                |                 |            |

|-------------|-------|----------------|-----------------|------------|

| A4          | •60   | <u>₩</u> ₽ • € |                 | LPDREQ .   |

| A5          | 020   | 40 • Q         | <u>cs</u> •‡    | DBC • \$   |

| A6          | 024   | A1 • ₹         | c⊤s •⊈          | RD •8      |

| Α7          | 022   | A2 • 2         | DACK • 🕏        | crk •€     |

| ∨ss         | 023   | A3 • ₹         | ADD • 4         | 1c •\$     |

| <b>A8</b>   | • 024 | NC • \$        | NC • €          | RC •8      |

| <b>A1</b> 0 | 025   | A9 • €7        | RTS •₽          | INTR •8    |

| A12         | • 88  | A11 • 🛱        | TD •₹           | READY 5    |

| A14         | 027   | A13 • ₹        | PDACK • €       | R/₩ •웅     |

| σĎ          | 028   | A15 • 8        | DREQ • O        | RE •0      |

| A17         | 029   | A16 • 5        | <u>ME • 6 B</u> | HE/BLE • 8 |

| A19         | 030   | A18 • P        | ĀS • Ç          | PAR1 •0    |

| A21         | 031   | A20 • ₹        | PARO • 0        | D15 • 8    |

| A22         | 038   | D1 • ₽         | Da • €          | D14 • 8    |

| A23         | 033   | DS • th        | D8 • €          | D13 • 8    |

| Vss         | 034   | D3 • ₩         | D7 • 💆          | D12 • 8    |

| Vss         | 035   | D4 • 🛱         | De • 6          | D11 • 8    |

| DO          | 036   |                | D5 • 5          | D10 • 8    |

| Sym | Pin | Sym  | Pin | Sym    | Pin    |

|-----|-----|------|-----|--------|--------|

| A0  | 120 | A23  | 33  | D15    | 6      |

| A1  | 121 | ĀS   | 107 | DACK   | 115    |

| A2  | 122 | BHE/ | 8   | DBC    | 17     |

| A3  | 123 | BLE  |     | DREQ   | 109    |

| A4  | 19  | CD   | 28  | INTR   | 12     |

| A5  | 20  | CLK  | 15  | LPDREQ | 18     |

| A6  | 21  | CTS  | 116 | MR     | 119    |

| A7  | 22  | CS   | 117 | PAR0   | 106    |

| A8  | 24  | D0   | 36  | PAR1   | 7      |

| A9  | 125 | D1   | 132 | PDACK  | 110    |

| A10 | 25  | D2   | 133 | RC     | 13     |

| A11 | 126 | D3   | 134 | RD     | 16     |

| A12 | 26  | D4   | 135 | RE     | 9      |

| A13 | 127 | D5   | 101 | READY  | 11     |

| A14 | 27  | D6   | 102 | RTS    | 112    |

| A15 | 128 | D7   | 103 | R/W    | 10     |

| A16 | 129 | D8   | 104 | TC     | 14     |

| A17 | 29  | D9   | 105 | TD     | 111    |

| A18 | 130 | D10  | 1   | VDD    | 114    |

| A19 | 30  | D11  | 2   | Vss    | 23,34, |

| A20 | 131 | D12  | 3   |        | 35     |

| A21 | 31  | D13  | 4   | WE     | 108    |

| A22 | 32  | D14  | 5   |        |        |

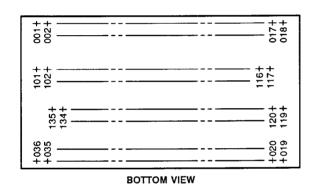

Figure 2. Pin Function Diagram and Alphabetical Listing of Symbols

Table 1. Pin Descriptions

| Pin | Symbol  | Туре | Name/Function                                                                                                                                                                                             |

|-----|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | D10     |      | Data Bus Bit 10.                                                                                                                                                                                          |

| 2   | D11     |      | Data Bus Bit 11. If DBC (pin 17) is high, a 16-bit data bus (pins 1—6,                                                                                                                                    |

| 3   | D12     | 1/0* | Data Bus Bit 12. 36, 101-105, and 132-135) is used; if DBC is low,                                                                                                                                        |

| 4   | D13     |      | Data Bus Bit 13. an 8-bit data bus (pins 36, 101—103, and 132—135)                                                                                                                                        |

| 5   | D14     |      | Data Bus Bit 14. is used.                                                                                                                                                                                 |

| 6   | D15     |      | Data Bus Bit 15.                                                                                                                                                                                          |

| 7   | PAR1    | 1/0* | Parity on High Data Byte. Parity generation and checking of high byte of data bus. Valid only during DMA operations.                                                                                      |

| 8   | BHE/BLE | O*   | Byte High Enable (Active Low). The XPC uses this line to control access to the high data byte when it has a 16-bit data bus. Access is to the low data byte in the Motorola configuration (see Table 18). |

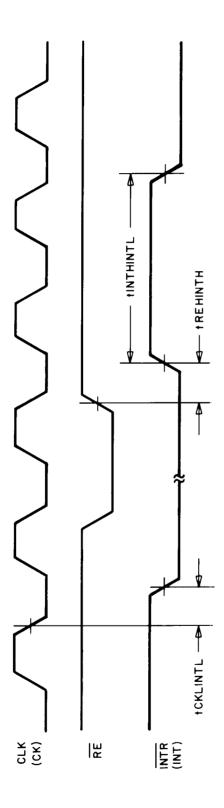

| 9   | RE      | 1/0* | Read Enable (Active Low). An input during CPU access of XPC registers; an output during DMA read cycles.                                                                                                  |

<sup>\*</sup> Indicates 3-state condition.

Table 1. Pin Descriptions (Continued)

| Pin                        | Symbol                          | Туре                       | Name/Function                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|---------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                         | R/W                             | O*                         | Read or Write (Active Low). If low, the XPC wants to write to main memory; if high, the XPC wants to read from main memory. Not used during internal XPC register read/write operations.                                                                                                                                                                                       |

| 11                         | READY                           | I/O*                       | Ready (Active Low). This signal is used as an input during DMA read and write cycles to allow slow memory to be accessed. During DMA operations, RE and WE (pins 9 and 108) remain low as long as READY is held high. During CPU read/write operations of internal XPC registers, READY is an output. It goes low to signal the CPU that the read/write operation is complete. |

| 12                         | INTR                            | 0                          | Interrupt Request (Active Low). This signal indicates that the XPC is requesting service. It returns high when the CPU reads the interrupt register.                                                                                                                                                                                                                           |

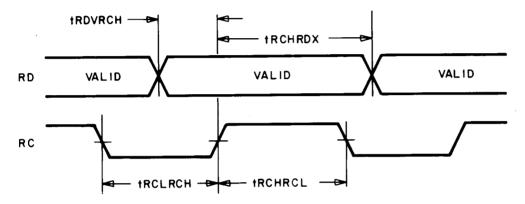

| 13                         | RC                              | 1                          | Receive Clock. Data is received at this frequency.                                                                                                                                                                                                                                                                                                                             |

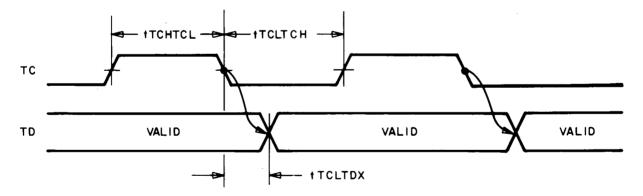

| 14                         | TC                              | ı                          | Transmit Clock. Data is transmitted at this frequency.                                                                                                                                                                                                                                                                                                                         |

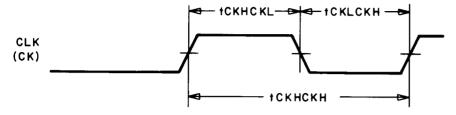

| 15                         | CLK                             | 1                          | Clock. This pin controls the internal sequencing of the chip. The clock must be a square wave with a minimum frequency of 250 kHz and a maximum frequency of 2 MHz (fCLK $\geq$ 6fRC and fCLK $\geq$ 6fTC).                                                                                                                                                                    |

| 16                         | RD                              | ı                          | Receive Data. Serial data input line.                                                                                                                                                                                                                                                                                                                                          |

| 17                         | DBC                             | I                          | Data Bus Configuration. This pin must be wired to Vss or VDD to configure the XPC data bus for 8-bit or 16-bit operation, respectively.                                                                                                                                                                                                                                        |

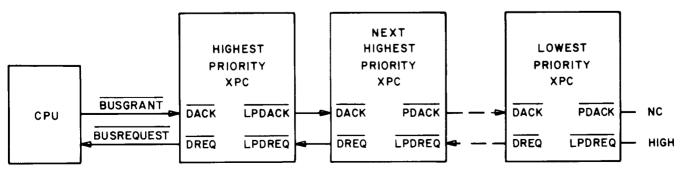

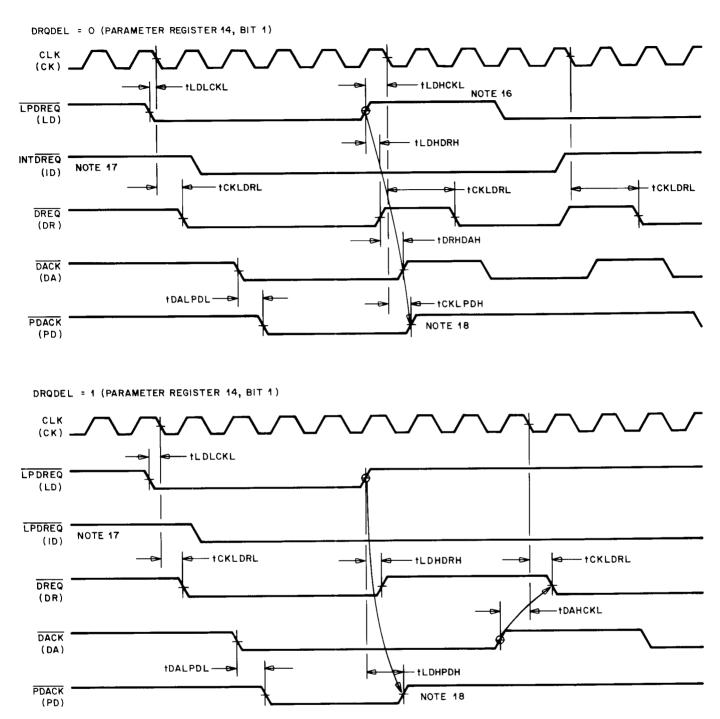

| 18                         | LPDREQ                          | I                          | Low-Priority DMA Request (Active Low). This pin is used to daisy-chain DMA requests in systems without a bus arbiter that use more than one XPC. Tie high on lowest priority XPC in the daisy chain.                                                                                                                                                                           |

| 19<br>20<br>21<br>22       | A4<br>A5<br>A6<br>A7            | 1/O*<br>1/O*<br>1/O*<br>O* | Address Bus Bit 4. If $\overline{CS}$ (pin 117) is low, A1—A6 (pins 19—21 and Address Bus Bit 5. 121—123) are inputs used to address the XPC Address Bus Bit 6. internal registers; if $\overline{CS}$ is high, all pins of the Address Bus Bit 7. 24-bit address bus (pins 19—22, 24—27, 29—33, 120—123, and 125—131) are outputs used to address system memory.              |

| 23                         | Vss                             | 0                          | Ground.                                                                                                                                                                                                                                                                                                                                                                        |

| 24<br>25<br>26<br>27       | A8<br>A10<br>A12<br>A14         | 0*                         | Address Bus Bit 8. Address Bus Bit 10. Address Bus Bit 12. Address Bus Bit 14.                                                                                                                                                                                                                                                                                                 |

| 28                         | CD                              |                            | Carrier Detect (Active Low).                                                                                                                                                                                                                                                                                                                                                   |

| 29<br>30<br>31<br>32<br>33 | A17<br>A19<br>A21<br>A22<br>A23 | 0*                         | Address Bus Bit 17. Address Bus Bit 19. Address Bus Bit 21. See description of pins 19—22. Address Bus Bit 22. Address Bus Bit 23.                                                                                                                                                                                                                                             |

| 34                         | Vss                             |                            | Ground.                                                                                                                                                                                                                                                                                                                                                                        |

<sup>\*</sup> Indicates 3-state condition.

Table 1. Pin Descriptions (Continued)

| Pin                                   | Symbol                           | Туре     | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|---------------------------------------|----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 35                                    | Vss                              |          | Ground.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 36<br>101<br>102<br>103<br>104<br>105 | D0<br>D5<br>D6<br>D7<br>D8<br>D9 | I/O*     | Data Bus Bit 0.  Data Bus Bit 5.  Data Bus Bit 6.  Data Bus Bit 7.  Data Bus Bit 8.  Data Bus Bit 9.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 106                                   | PAR0                             | I/O*     | Parity on Low Data Byte. Parity generation and checking of low byte of data bus. Valid only during DMA operations.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 107                                   | ĀS                               | O*       | Address Strobe (Active Low). The XPC uses this signal during DMA operations to indicate that it has placed a valid address on the address bus.                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 108                                   | WE                               | I/O*     | Write Enable (Active Low). Used as an input during CPU access of XPC registers. Output during DMA write cycles.                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 109                                   | DREQ                             | 0        | DMA Request (Active Low). A low on this pin indicates to the CPU that the XPC needs the address bus and the data bus for DMA cycles.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 110                                   | PDACK                            | 0        | Propagated DMA Acknowledge (Active Low). This pin is used to daisy-chain acknowledgments in systems using more than one XPC. PDACK output of one XPC connects to DACK input of the next lower priority XPC.                                                                                                                                                                                                      |  |  |  |  |  |

| 111                                   | TD                               | 0        | Transmit Data. XPC serial data output line.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 112                                   | RTS                              | 0        | Request to Send (Active Low). When asserted, this signal indicates to level 1 that the XPC is ready to transmit either data or flags over the link.  RTS remains low while the link is up.                                                                                                                                                                                                                       |  |  |  |  |  |

| 113                                   | NC                               |          | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 114                                   | VDD                              | <u> </u> | 5 V Supply.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 115                                   | DACK                             | I        | DMA Acknowledge (Active Low). When this signal is low, the CPU indicates that the XPC has been granted system buses. All floating outputs of the XPC then become TTL drivers. DACK must remain low until DREQ (pin 19) is removed.                                                                                                                                                                               |  |  |  |  |  |

| 116                                   | CTS                              | I        | Clear to Send (Active Low). Level 1 interface notifies the XPC that the data set is ready to send by asserting this signal. The link cannot come up until $\overline{\text{CTS}}$ is asserted. $\overline{\text{CTS}}$ must remain asserted when the link is up.                                                                                                                                                 |  |  |  |  |  |

| 117                                   | CS                               | ı        | Chip Select (Active Low). $\overline{CS}$ must be asserted to allow access to internal registers of the XPC. When $\overline{CS}$ is asserted, $\overline{RE}$ , $\overline{WE}$ , and A1—A6 become inputs and $\overline{READY}$ becomes an output.                                                                                                                                                             |  |  |  |  |  |

| 119                                   | MR                               | I        | Master Reset (Active Low). When this pin is asserted, all command, status, and parameter register bits are cleared (0) except for the mandatory disconnect (MDISC) and the DISCMODE bits in command register 0, which are set (1). MR must be high for at least two clock (CLK) periods after power-on. The minimum low time for reset is 1.5 CLK periods. All outputs are 3-stated when both MR and CS are low. |  |  |  |  |  |

<sup>\*</sup> Indicates 3-state condition.

Table 1. Pin Descriptions (Continued)

| Pin | Symbol | Туре | Name/Function                                      |

|-----|--------|------|----------------------------------------------------|

| 120 | A0     | 0*   | Address Bus Bit 0.                                 |

| 121 | A1     | I/O* | Address Bus Bit 1. See description of pins 19—22.  |

| 122 | A2     | 1/0* | Address Bus Bit 2. See description of pins 19—22.  |

| 123 | A3     | I/O* | Address Bus Bit 3.                                 |

| 124 | NC     |      | No Connection.                                     |

| 125 | Α9     |      | Address Bus Bit 9.                                 |

| 126 | A11    |      | Address Bus Bit 11.                                |

| 127 | A13    | :    | Address Bus Bit 13.                                |

| 128 | A15    | O*   | Address Bus Bit 15. See description of pins 19—22. |

| 129 | A16    |      | Address Bus Bit 16.                                |

| 130 | A18    |      | Address Bus Bit 18.                                |

| 131 | A20    |      | Address Bus Bit 20.                                |

| 132 | D1     |      | Data Bus Bit 1.                                    |

| 133 | D2     | 1/0* | Data Bus Bit 2. See description of pins 1—6.       |

| 134 | D3     | "    | Data Bus Bit 3. See description of pins 1—0.       |

| 135 | D4     |      | Data Bus Bit 4.                                    |

<sup>\*</sup> Indicates 3-state condition.

### Overview

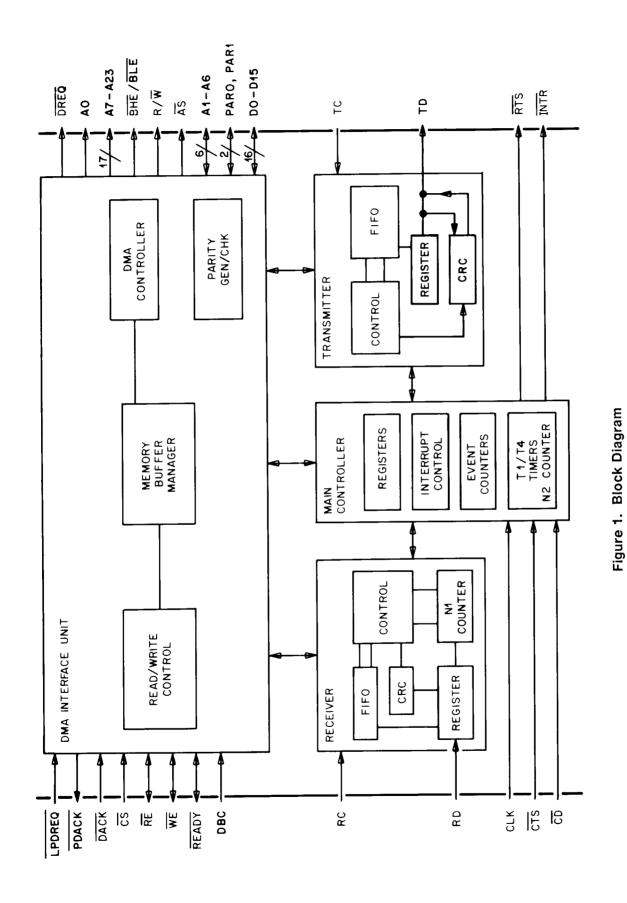

The T7102A XPC performs complete link level control according to X.25 and X.75 data communications protocols. The device generates supervisory and unnumbered frames automatically, without intervention by the host. The host must supply buffers for the data fields of received and transmitted information frames. It is notified of important events via interrupts. The XPC contains a transmitter, receiver, controller, and an interface unit, as shown in Figure 1.

### **Architecture**

### **Transmitter**

The transmitter constructs frames on command from the main controller. The transmitter contains a transmitter controller, 4-byte (first-in first-out) FIFO buffer, holding register, cyclic redundancy check (CRC) encoder, and zero inserter. The transmitter handles the transmission of continuous flags, aborts, or idle channel indications automatically. Bit stuffing is implemented to ensure data transparency.

The transmitter FIFO and the transmitter holding register control the flow of information from main memory to the data link. The transmitter FIFO is used as temporary storage for data delivered from memory to the transmitter by the DMA controller. The DMA controller can read two bytes of data at a time from main memory and place them into the transmitter FIFO. The transmitter holding register is loaded in a parallel fashion from the transmitter FIFO. The various bytes needed to construct a frame are also loaded into the holding register. When the data is ready to be transmitted, it is shifted out serially through the transmit data (TD) lead on the negative edge of the transmit clock (TC).

The CRC encoder calculates the frame check sequence (FCS) and appends it to the data field, or to the control field for frames without data. The FCS is calculated over the address, control, and data fields. The zero inserter performs bit stuffing to ensure data transparency.

#### Receiver

The receiver processes incoming data and notifies the controller of received frames and other link conditions. The receiver contains a preprocessor, receiver controller, 4-byte FIFO, receiver register, and CRC decoder. The preprocessor detects flags, aborts, and idle conditions on the data link, and deletes the 0s that were added for data transparency. Receive data (RD) is latched on the positive edge of the receive clock (RC). Frames are identified and checked for proper format by the receiver controller.

The information field of a frame is loaded into the FIFO and is DMAed to memory by the interface unit.

The frame is checked for transmission errors by means of the CRC. The XPC acts on frames received error-free and discards frames received with errors. The XPC maintains the number of link errors in the counter registers.

#### Controller

The controller interprets results from the receiver, transmitter, and internal registers, and implements the actions of the protocol. The X.25/X.75 protocol block contains the logic used to implement the entire X.25/X.75 level 2 protocol. Specific tasks of the main controller include configuring the link as specified by the parameter and command registers, maintaining the status registers, analyzing received frames and taking appropriate action, logging certain events in the bank of 16 event counters, directing the transmitter to send specific commands or responses, directing the interface unit to acquire receive and transmit data buffers, managing timing directions, and using a set of interrupts to notify the host of data link conditions.

### **DMA Interface Unit**

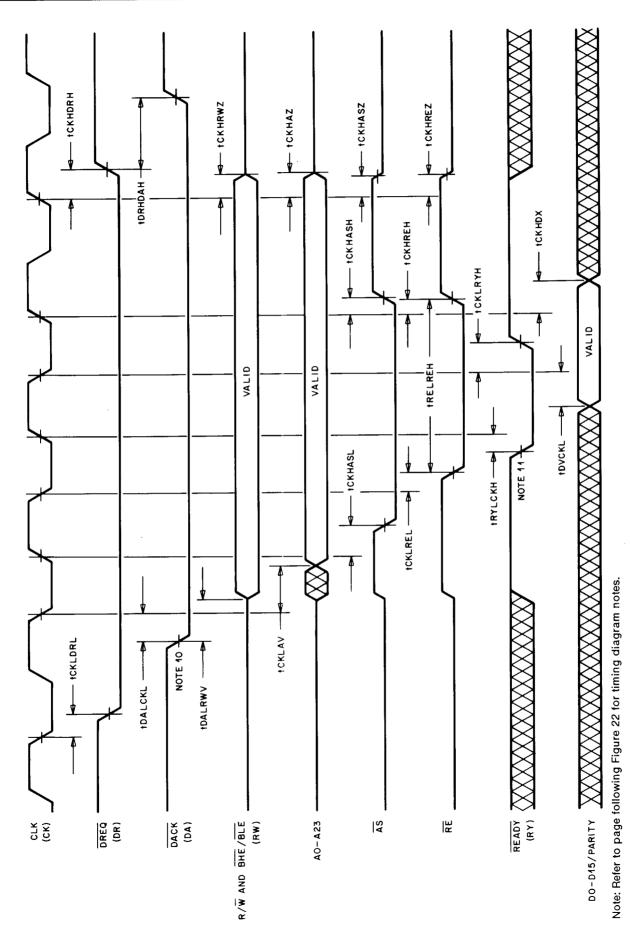

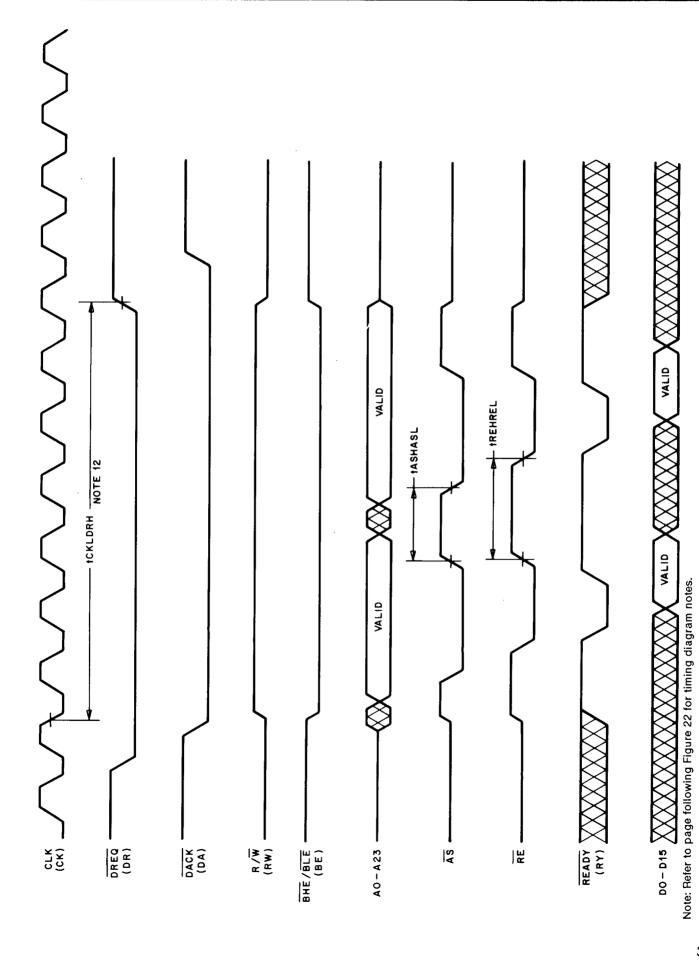

The interface unit provides the interface between main memory and the transmitter and receiver via 2-channel DMA. It consists of a data bus selector, parity generator and checker, address controller, read/write machine, data section, and DMA controller.

The data bus selector controls the width of the external data bus and data byte ordering. The external data bus can be set at either 8-or 16-bits wide by strapping DBC (pin 17) to VSS or VDD, respectively. The internal data bus is 8 bits wide. Data byte ordering is accomplished via parameter register 14, bit 0.

Parity is generated and checked for each byte of the data bus during DMA operations if parity is enabled. Parity is not checked or generated when the host accesses the XPC registers.

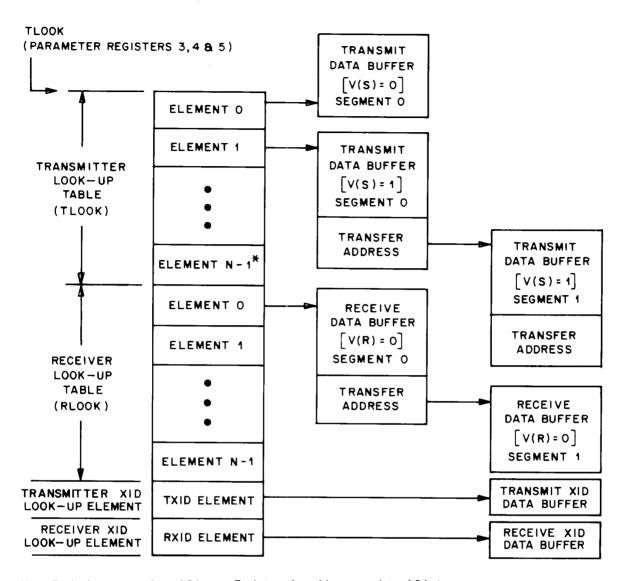

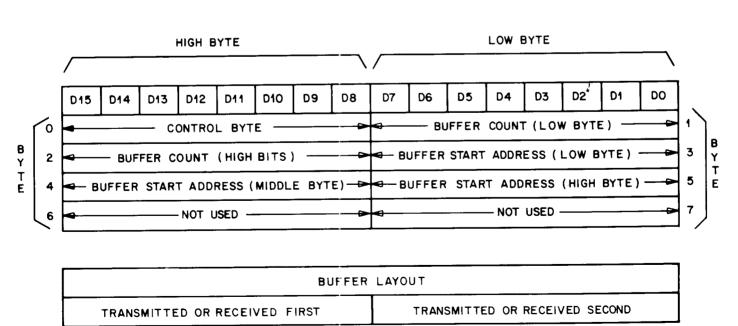

The address controller calculates and stores the addresses for the elements and buffer pointers for the transmit and receive channels.

The read/write machine generates the control signals to access data from memory, while the data section routes the data from memory to the transmit FIFO and from the receive FIFO to memory.

The DMA controller, on request from the controller, opens data buffers for the transmitter and receiver and controls the sequencing of the other sections.

A DMA priority scheme can be implemented in a daisy-chain fashion with no additional hardware for multiple XPC applications.

### Loopback Test Control

The loopback test control connects the RD and TD pins, as required by the near-end loopback test, far-end loopback test, or echo mode.

## **Principles of Operation**

### **CPU Interface**

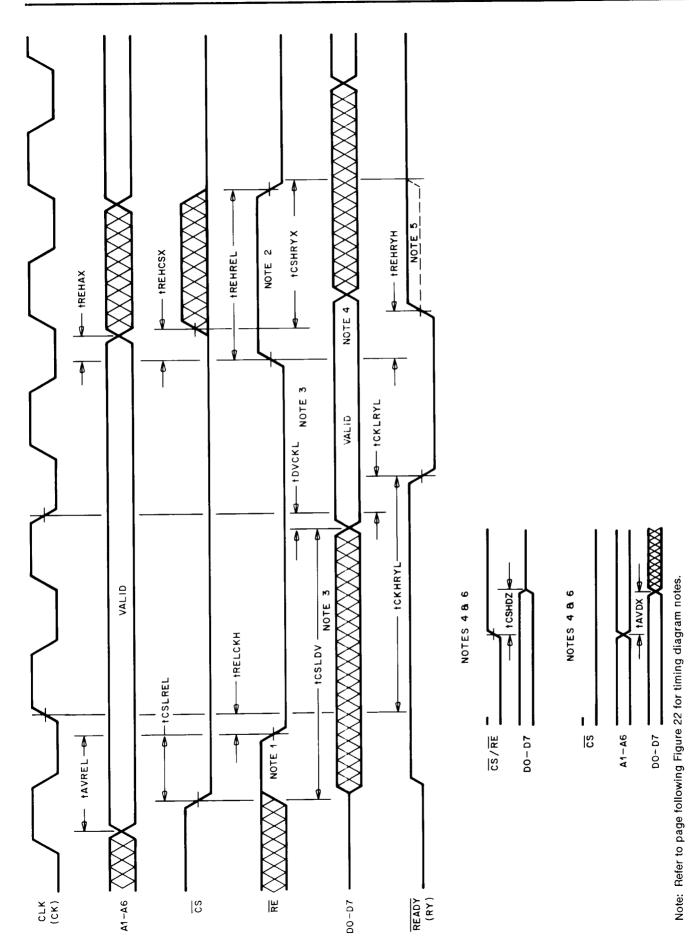

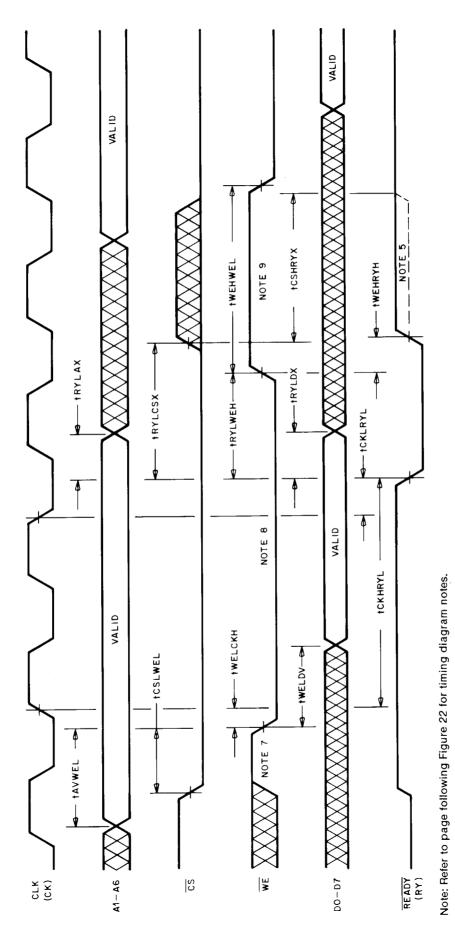

The CPU interface is used to specify commands to the XPC and to receive status information from the XPC. The XPC is a peripheral device that accepts commands from the CPU and provides interrupts and results to the CPU when necessary. Through the CPU interface, the CPU loads the command, parameter, and counter registers with the characteristics of the serial interface. The XPC provides status information and interrupts via the status and interrupt registers. The CPU accesses these registers via bits A1—A6 of the address bus. When  $\overline{\text{CS}}$  is asserted,  $\overline{\text{RE}}$ ,  $\overline{\text{WE}}$ , and A1—A6 become inputs and  $\overline{\text{READY}}$  becomes an output. Only the low-order byte of the data bus is used for register read/write operations. The XPC ignores the upper byte during write operations and forces a 3-state condition on the upper data byte during read operations. The registers always appear on D0—D7, regardless of the byte ordering that is selected. Table 2 lists the register addresses for the XPC.

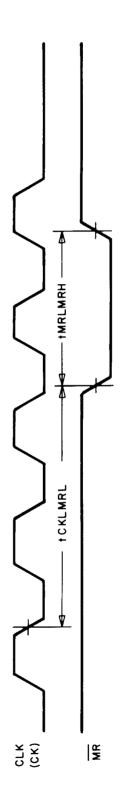

### **Master Reset**

When the master reset (MR) is asserted, the parameter registers are cleared, the command register is set to 82H (DISCMODE = 1, MDISC = 1), and the interrupt register is cleared. Status registers 9—13 and the counter registers are not initialized. MR must be high for at least two CLK periods after power-up. The minimum low time for reset is 1.5 CLK periods.

When the XPC detects a reset, it performs an internal reset sequence that requires eight CLK periods. After the reset sequence, the XPC enters a set-up state in which the CPU can configure the parameter and counter registers. While in the set-up state, the XPC transmits 1s and ignores any frames that are received. The XPC exits the set-up state and enters the operational state when the CPU clears MDISC in the command register.

In order to change parameter register values, either the XPC must be placed in the set-up state by a reset or the MDISC bit must be set while the XPC is in the operational state. An exception to this is parameter register 0, which can be configured only in the set-up state.

$\overline{\text{MR}}$  is also used with  $\overline{\text{CS}}$  to provide board isolation capabilities. If  $\overline{\text{CS}}$  is low when  $\overline{\text{MR}}$  is asserted, INTR, RTS, TD,  $\overline{\text{DREQ}}$ , and  $\overline{\text{DACK}}$  are placed in a high-impedance state; if  $\overline{\text{CS}}$  is high when  $\overline{\text{MR}}$  is asserted, these pins are not put in a high-impedance state. All other outputs are placed in a high-impedance state when  $\overline{\text{MR}}$  is asserted, regardless of the state of  $\overline{\text{CS}}$ .

## Registers

The XPC contains 51 addressable registers for controlling and observing its operational mode. The registers are divided into five types: command, status, interrupt, parameter, and counter.

Command Register. This register controls seven XPC functions: send, receive, mandatory disconnect, active or passive link initialization, password exchange, password verification, and disconnect. The command register can be written to at any time.

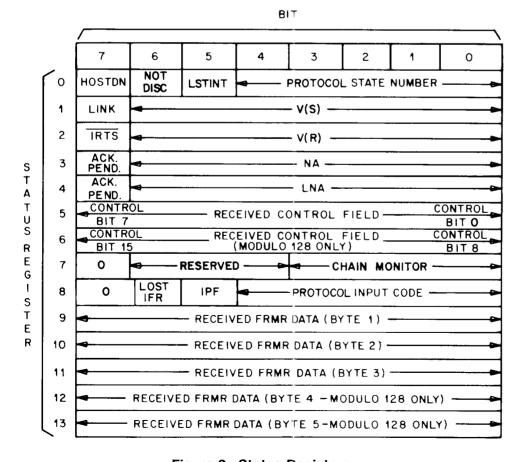

Status Registers. These 14 registers report the state of the XPC, input conditions, and other vital information regarding the XPC to the CPU; e.g., the values of the state variables V(S) and V(R).

Interrupt Register. This register's lower six bits present an encoded reason for a particular interrupt issued to the CPU; for example, packet received, parity error, idle link detected, and frame reject. This register is backed up by a 4-word FIFO, which enables several interrupts to occur before the CPU can service the XPC. Bit 7 contains a lost interrupt bit, which is independent of the LSTIN bit in status register 0 and is implicitly cleared after a read of the interrupt register. If no interrupts are pending, the interrupt register contains 00H.

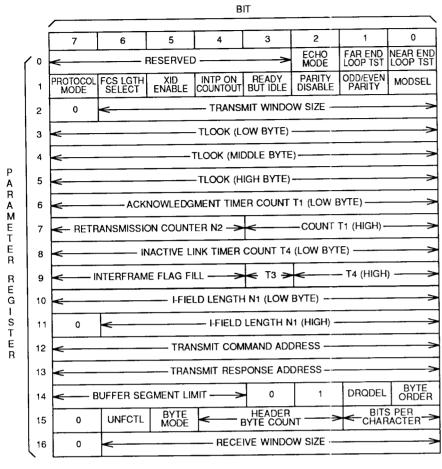

Parameter Registers. These 17 registers determine system constants and the mode of operation, for example, the period of the T1 and T4 timers and the address of the TLOOK table. The XPC can also be put into a test mode to test either itself or itself and the link. These registers can be written to only when MDISC is set. An exception to this is parameter register 0, which can be configured only in the set-up state.

Counter Registers. These 18 down-counter registers monitor 16 different events on the data link; for example, the number of rejected frames received, the number of times timer T1 expired, and the number of parity errors generated. The counter registers can be written to at any time.

Table 2. XPC Register Address Offsets

|     | Address |         |                      |     | Address |         |                       |

|-----|---------|---------|----------------------|-----|---------|---------|-----------------------|

| Hex | Dec     | Status* | Name                 | Hex | Dec     | Status* | Name                  |

| 00  | 0       | R/W     | Command register     | 34  | 52      | R/W     | Parameter register 10 |

| 02  | 2       | R       | Status register 0    | 36  | 54      | R/W     | Parameter register 11 |

| 04  | 4       | R       | Status register 1    | 38  | 56      | R/W     | Parameter register 12 |

| 06  | 6       | R       | Status register 2    | 3A  | 58      | R/W     | Parameter register 13 |

| 08  | 8       | R       | Status register 3    | 3C  | 60      | R/W     | Parameter register 14 |

| 0A  | 10      | R       | Status register 4    | 3E  | 62      | R/W     | Parameter register 15 |

| 00  | 12      | R       | Status register 5    | 40  | 64      | R/W     | Counter register 0    |

| 0E  | 14      | R       | Status register 6    | 42  | 66      | R/W     | Counter register 1    |

| 10  | 16      | R       | Status register 7    | 44  | 68      | R/W     | Counter register 2    |

| 12  | 18      | R       | Status register 8    | 46  | 70      | R/W     | Counter register 3    |

| 14  | 20      | R       | Status register 9    | 48  | 72      | R/W     | Counter register 4    |

| 16  | 22      | R       | Status register 10   | 4A  | 74      | R/W     | Counter register 5    |

| 18  | 24      | R       | Status register 11   | 4C  | 76      | R/W     | Counter register 6    |

| 1A  | 26      | R       | Status register 12   | 4E  | 78      | R/W     | Counter register 7    |

| 1C  | 28      | R       | Status register 13   | 50  | 80      | R/W     | Counter register 8    |

| 1E  | 30      | R       | Interrupt register   | 52  | 82      | R/W     | Counter register 9    |

| 20  | 32      | R       | Parameter register 0 | 54  | 84      | R/W     | Counter register 10   |

| 22  | 34      | R/W**   | Parameter register 1 | 56  | 86      | R/W     | Counter register 11   |

| 24  | 36      | R/W     | Parameter register 2 | 58  | 88      | R/W     | Counter register 12   |

| 26  | 38      | R/W     | Parameter register 3 | 5A  | 90      | R/W     | Counter register 13   |

| 28  | 40      | R/W     | Parameter register 4 | 5C  | 92      | R/W     | Counter register 14   |

| 2A  | 42      | R/W     | Parameter register 5 | 5E  | 94      | R/W     | Counter register 15   |

| 2C  | 44      | R/W     | Parameter register 6 | 60  | 96      | R/W     | Counter register 16   |

| 2E  | 46      | R/W     | Parameter register 7 | 62  | 98      | R/W     | Counter register 17   |

| 30  | 48      | R/W     | Parameter register 8 | 64  | 100     | R/W     | Parameter register 16 |

| 32  | 50      | R/W     | Parameter register 9 |     |         |         |                       |

<sup>\*</sup> Read/write (R/W) or read-only (R) status.

<sup>\*\*</sup> Parameter registers can be written only when MDISC is set.

**Table 3. Command Register Definitions**

| Γ.    |                 |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |                                                                    |                        |                        |                      |  |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------|------------------------|------------------------|----------------------|--|

|       |                 |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                           |                                                                    | ı                      | t                      | , ,                  |  |

| Bit   | 7               | 6                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                           | 3                                                                  | 2                      | 1                      | 0                    |  |

| Field | DISCMODE        | PWOK2                                                                                                                                                                                                                                                                                                                                                        | PWOK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PWXCH                       | ACT/PAS                                                            | RECR                   | MDISC                  | SEND                 |  |

|       |                 | Marie - 10                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |                                                                    |                        |                        |                      |  |

| Bit   | Symbol          |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Nam                         | e/Descriptio                                                       | n                      |                        |                      |  |

| 0     | SEND            | sending ne                                                                                                                                                                                                                                                                                                                                                   | w packets<br>bit if the li                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ; if set, ena<br>nk goes do | packets. If cl<br>bles XPC to s<br>wn or if the r<br>utomatically, | send new<br>lext trans | packets.<br>mit elemen | The XPC<br>It is not |  |

| 1     | MDISC           | remains di<br>XPC transr<br>XPC is in t<br>a DISC fra<br>generation                                                                                                                                                                                                                                                                                          | Mandatory Disconnect. Selects whether the XPC brings the link up or remains disconnected. If cleared, the XPC brings the link up; if set, the XPC transmits all 1s during fill times and remains disconnected. If the XPC is in the information transfer phase when MDISC is set, it transmits a DISC frame and exits the information transfer phase. Interrupt generation is disabled when MDISC is set and NOTDISC (status register 0) is cleared. MDISC is set during a master reset (see Table 4). |                             |                                                                    |                        |                        |                      |  |

| 2     | RECR            | receiver bu<br>available.<br>chain segr<br>not ready.                                                                                                                                                                                                                                                                                                        | Receiver Ready. Indicates availability of receiver buffers. If cleared, no receiver buffers are available. If set, receiver buffers are allocated and available. The XPC clears this bit if the receiver overruns, if the buffer chain segment is not ready, or if the receive element referenced by V(R) is not ready. If cleared while the XPC is in the information transfer phase, the XPC enters the station busy state and ignores all incoming I frames.                                        |                             |                                                                    |                        |                        |                      |  |

| 3     | ACT/PAS         | cleared, th                                                                                                                                                                                                                                                                                                                                                  | e XPC pas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | action in the<br>ts link set-up<br>).                              |                        |                        |                      |  |

| 4     | PWXCH           | Password Exchange. Determines which end of the link initiates password exchange. If cleared, the other end of link initiates password exchange; if set, the XPC initiates password exchange.                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |                                                                    |                        |                        |                      |  |

| 5, 6  | PWOK1,<br>PWOK2 | Password Verified. Enables the host to notify the XPC about the correct action to take in response to a received password. Bits 4, 5, and 6 are interpreted as:  Code  b6 b5 b4 Condition  0 1 0 Valid password command received 0 1 1 Valid password response received 1 0 0 Valid password command not received 1 0 1 Valid password response not received |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |                                                                    |                        |                        |                      |  |

| 7     | DISCMODE        | during a n                                                                                                                                                                                                                                                                                                                                                   | naster rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t. DISCMO                   | disconnected<br>DE must be s<br>d for XID ope                      | et for pa              | ssive link             |                      |  |

**Table 4. Disconnected Phase Operation**

| Protocol<br>State | XIDEN <sup>1</sup> | DISCMODE | ACT/PAS <sup>2</sup> | MDISC          | Description                                                                                                                  |

|-------------------|--------------------|----------|----------------------|----------------|------------------------------------------------------------------------------------------------------------------------------|

| S0                | 0                  | ×        | x                    | 1 <sup>3</sup> | Does not respond to received frames until MDISC is cleared. <sup>4</sup> Responds to P-bit frame with DM final. <sup>5</sup> |

| S0                | 0                  | 0        | 0                    | 0              | Responds to P-bit frame with DM final. <sup>6</sup>                                                                          |

| S1                | 0                  | 1        | 0                    | 0              | Link can be initialized by remote DXE.                                                                                       |

| х                 | 0                  | ×        | 1                    | 0              | Initiates link setup.                                                                                                        |

| S0                | 1                  | 0        | 0                    | 0              | Waits for XID transfer.                                                                                                      |

| S0                | 1                  | 0        | 1                    | 0              | Initiates XID transfer.                                                                                                      |

| S0                | 1                  | 0        | x                    | 1              | Does not respond to received frames until MDISC is cleared.                                                                  |

| х                 | 1                  | 1        | х                    | х              | Do not use.                                                                                                                  |

Note: x = don't care.

<sup>&</sup>lt;sup>6</sup> Interframe fill is flags.

Figure 3. Status Registers

<sup>&</sup>lt;sup>1</sup> Password enable bit in parameter register 1.

<sup>&</sup>lt;sup>2</sup> Use PWXCH instead of ACT/PAS if XIDEN is 1.

<sup>&</sup>lt;sup>3</sup> Interframe fill is idle (all 1s).

<sup>&</sup>lt;sup>4</sup> MDISC not yet cleared after reset.

<sup>&</sup>lt;sup>5</sup> MDISC previously cleared after reset.

Table 5. Status Registers

| Reg | Bit | Symbol  | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0-4 | PSN     | Protocol State Number. Encoding of protocol state (see Table 6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0   | 5   | LSTINT  | Lost Interrupt. Indicates if interrupts were lost. If cleared, no interrupts were lost. If set, interrupt register FIFO overflowed and interrupts were lost. This bit is implicitly cleared after a read of status register 0.                                                                                                                                                                                                                                                                                                          |

| 0   | 6   | NOTDISC | <b>Not Disconnected</b> . This bit is cleared if the XPC is disconnected or in XID phase. It is set when the device is in the link set-up or information transfer phase (protocol state $\geq$ S3). Interrupt generation is disabled when NOTDISC is cleared and MDISC (command register) is set.                                                                                                                                                                                                                                       |

| 0   | 7   | HOSTD   | Host Done (Active Low). Allows the internal host done bit to be monitored in the event that the interrupt informing the host of a link-down condition was lost. If set, the host must reassign transmit and receive buffers before link reinitialization is permitted. The XPC sets this bit when an SABM frame is received while the XPC is in the information transfer phase (LINK = 1) or when the XPC exits the information transfer phase (LINK = 0). This bit is cleared by writing to status register 0 or parameter register 1. |

| 1   | 06  | V(S)    | Send State Variable. The sequence number, N(S), of the next I frame to be transmitted and an index into the TLOOK table to access the buffer containing data for that frame.                                                                                                                                                                                                                                                                                                                                                            |

| 1   | 7   | LINK    | <b>Link.</b> Indicates the status of the transmission link. If cleared, information transfer is not possible; if set, the XPC is in the information transfer phase (protocol state $\geq$ S6).                                                                                                                                                                                                                                                                                                                                          |

| 2   | 0—6 | V(R)    | Receive State Variable. The expected value of the sequence number, N(S), of the next I frame to be received and an index into the RLOOK table for the receiver buffer associated with that packet.                                                                                                                                                                                                                                                                                                                                      |

| 2   | 7   | ĪRTS    | Internal Request to Send. Indicates that the XPC wants to acquire the link. If cleared, XPC wants link; if set, XPC does not want link.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | 0—6 | NA      | Next Acknowledgment Expected. Number of earliest unacknowledged packet. If no outstanding packets, NA = V(S).                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3   | 7   | ACKPEND | Acknowledgments Pending. This bit is set when the DMA has received acknowledgment processing to do. When all appropriate TLOOK elements have been updated, this bit is cleared. Before the host clears HOSTD or reallocates transmit buffers, it must check that this bit is cleared.                                                                                                                                                                                                                                                   |

| 4   | 0—6 | LNA     | Last Next Acknowledgment Expected. Whenever NA is updated, the old value of NA is saved here. NA and LNA can be used to determine how many transmit data buffers have been acknowledged by the remote DXE and subsequently freed by the XPC.                                                                                                                                                                                                                                                                                            |

| 4   | 7   | ACKPEND | Acknowledgment Pending. See ACKPEND description above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 5. Status Registers (Continued)

| Reg    | Bit | Symbol | Name/Description                                                                                                                                                                                                   |  |  |  |  |

|--------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5      | 0—7 | RCF    | Received Control Field. Holds the control field of the most recently received error-free frame.                                                                                                                    |  |  |  |  |

| 6      | 0—7 | RCF    | Received Control Field. Holds the second byte of the control field in modulo-128 mode only. If in modulo-8 (normal sequencing), this register is always cleared.                                                   |  |  |  |  |

| 7      | 03  | CHMON  | Chain Monitor. Indicates which chain segment of the receiver buffer is currently being used.                                                                                                                       |  |  |  |  |

| 7      | 4—6 | _      | Reserved. These bits are for internal use and should be masked when reading status register 7.                                                                                                                     |  |  |  |  |

| 7      | 7   | _      | Zero. This bit is always 0.                                                                                                                                                                                        |  |  |  |  |

| 8      | 0—4 | PIC    | Protocol Input Code. Contains an encoding of what the protocol considers to be its most recent input stimulus (see Table 7).                                                                                       |  |  |  |  |

| 8      | 5   | IPF    | Internal Poll/Final Bit. Last poll/final bit upon which the XPC has acted. This bit is used in conjunction with the protocol input code.                                                                           |  |  |  |  |

| 8      | 6   | LSTIFR | Lost I-Frame. Cleared for normal operation; set if an I frame is received but no receive buffers are available or if a receiver overrun occurs. This bit is cleared when the XPC exits the station busy condition. |  |  |  |  |

| 8      | 7   |        | Zero. This bit is always 0.                                                                                                                                                                                        |  |  |  |  |

| 9—11   | 0—7 | RFDF   | Received Frame Project (FRMR) Data Field. Holds the first, second, and third bytes of data field contained in a received FRMR frame. These registers contain random data until the first FRMR is received.         |  |  |  |  |

| 12, 13 | 0-7 | RFDF   | Received Frame Project (FRMR) Data Field. Holds the fourth and fifth byte of data field in FRMR frame (modulo-128 only). If in modulo-8 (normal sequencing), these registers always contain random data.           |  |  |  |  |

Table 6. Status Register 0 — Protocol State Number Encoding

|     | State Number |    |    |    |    |       |                        |

|-----|--------------|----|----|----|----|-------|------------------------|

| Hex | b4           | b3 | b2 | b1 | b0 | State | Description            |

| 00  | 0            | 0  | 0  | 0  | 0  | S0    | Logically disconnected |

| 01  | 0            | 0  | 0  | 0  | 1  | S1    | Logically disconnected |

| 02  | 0            | 0  | 0  | 1  | 0  | S2a   | Awaiting XID command   |

| 03  | 0            | 0  | 0  | 1  | 1  | S2b   | Awaiting XID response  |

| 04  | 0            | 0  | 1  | 0  | 0  | S3    | Link set-up initiated  |

| 07  | 0            | 0  | 1  | 1  | 1  | S4    | Frame rejected         |

| 05  | 0            | 0  | 1  | 0  | 1  | S5    | Disconnect request     |

| 06  | 0            | 0  | 1  | 1  | 0  | S6    | Information transfer   |

Table 6. Status Register 0 — Protocol State Number Encoding (Continued)

|     | St         | ate N | umbe | r  |    |       |                        |

|-----|------------|-------|------|----|----|-------|------------------------|

| Hex | <b>b</b> 4 | b3    | b2   | b1 | b0 | State | Description            |

| 08  | 0          | 1     | 0    | 0  | 0  | S7    | REJ frame sent         |

| 09  | 0          | 1     | 0    | 0  | 1  | S8    | Waiting acknowledgment |

| 11  | 1          | 0     | 0    | 0  | 1  | S9    | Station busy           |

| 0A  | 0          | 1     | 0    | 1  | 0  | S10   | Remote station busy    |

| 0F  | 0          | 1     | 1    | 1  | 1  | S11   | S9 and S10             |

| 10  | 1          | 0     | 0    | 0  | 0  | S12   | S8 and S9              |

| 0B  | 0          | 1     | 0    | 1  | 1  | S13   | S8 and S10             |

| 1A  | 1          | 1     | 0    | 1  | 0  | S14   | S8, S9, and S10        |

| 1B  | 1          | 1     | 0    | 1  | 1  | S15   | S7 and S9              |

| 0C  | 0          | 1     | 1    | 0  | 0  | S16   | S7 and S10             |

| 0D  | 0          | 1     | 1    | 0  | 1  | S17   | S7, S9, and S10        |

Table 7. Status Register 8 — Input Code

| Input Code* | Description                                  |

|-------------|----------------------------------------------|

| 0           | Local stop – disconnect link                 |

| 1           | Local start – initiate link set-up           |

| 2           | Busy condition clears                        |

| 3           | Valid XID command received                   |

| 4           | T1 expired                                   |

| 5           | T3/T4 expired                                |

| 6           | Station has become busy                      |

| 7           | I frame available (reset condition also)     |

| 8           | Invalid N(S) in last received I frame (X.75) |

| 9           | Unrecognized frame received                  |

| 10          | I frame received                             |

| 11          | RNR command received                         |

| 12          | REJ command received                         |

| 13          | RR command received                          |

| 14          | SABM received                                |

| 15          | DISC received                                |

| 16          | UA received                                  |

| 17          | FRMR received                                |

| 18          | DM received                                  |

| 19          | Valid XID response received                  |

| 20          | Idle link detected for T3                    |

| 21          | Incorrect N(S) in last received I frame      |

| 23          | N2 exceeded                                  |

| 24          | Invalid N(R) in last received I frame        |

| 26          | Initiate password exchange                   |

| 27          | RNR response received                        |

| 28          | REJ response received                        |

| 29          | RR response received                         |

| 30          | Wait for password exchange                   |

<sup>\*</sup> This code is represented as a binary number in the 5-bit protocol input code field in the status register.

Table 8. Interrupt Vector Register

|       |         | ı                                                         | ſ                    | ı                              | 1                     | ı                     | ı                     | ł                    | ſ                     |

|-------|---------|-----------------------------------------------------------|----------------------|--------------------------------|-----------------------|-----------------------|-----------------------|----------------------|-----------------------|

|       | Bit     | 7                                                         | 6                    | 5                              | 4                     | 3                     | 2                     | 1                    | 0                     |

|       | Field   | LOST<br>INTERRUPT                                         | 0                    | INT5                           | INT4                  | INT3                  | INT2                  | INT1                 | INT0                  |

| Code* | Interru | pt                                                        |                      |                                | N:                    | ame/De                | scriptio              | n                    |                       |

| 1     | SABM    | Link Res<br>received<br>is reinitia                       | whil                 | e the XF                       | I. An SA              | ABM or a              | SABME<br>formation    | comma                |                       |

| 2     | UA      | UA Rece<br>unnumbe<br>unnumbe<br>HOSTD r                  | ered<br>ered         | respons<br>comma               | se frame<br>nd neve   | was red<br>r sent.    | ceived a<br>The link  | cknowle<br>is reinit | edging a<br>ialized v |

| 3     | DM      | DM Recomode be indicatin the X.75                         | caus<br>g tha        | se it rece<br>at the fa        | eived an<br>r end of  | unsolic<br>the link   | ited, un<br>i is in a | number               | ed respo              |

| 4     | FRMRR   | Frame R<br>stored in                                      | -                    | -                              | -                     |                       | e interru             | upt is iss           | sued afte             |

| 5     | DISC    | Received<br>disconne<br>transfer                          | ct c                 | ommano                         | d is rece             | ived wh               | ile the X             | (PC is in            |                       |

| 6     | IDLINK  | Idle Link<br>starts tim<br>T3 expire<br>T1 is run         | ner T<br>es, a       | 3 if T1 is<br>n idle lir       | s not ru<br>nk is rep | nning. I<br>orted ar  | f a flag<br>nd this i | is not d<br>nterrupt | etected<br>is issue   |

| 7     | N2EXC   | N2/C2 C<br>to initiali<br>(N2) was<br>counter i           | ze th                | ie link b<br>eeded.            | ecause<br>If the XF   | the max<br>PC is in t | imum n<br>the pass    | umber c              | f retrans             |

| 8     | RF1P    | F = 1 Re<br>response<br>send a c<br>discarde<br>reset pro | frai<br>omn<br>d; in | ne with<br>nand fra<br>the X.7 | its final<br>me with  | bit set v             | vas rece<br>set. In   | eived bu<br>the X.25 | t the XP<br>mode,     |

| 9     | LK01    | Link Is U                                                 | •                    |                                | -                     |                       |                       |                      |                       |

| 10    | XIDRCV  | D XID Fran                                                |                      |                                |                       | O frame               | was rec               | eived a              | nd its da             |

| 11    | NOXIDE  | No XID F                                                  | -                    |                                |                       | omman                 | d was tr              | ansmitt              | ed and r              |

The code is represented as a binary number in the lower 6 bits of the interrupt vector register. Bit 7 of the interrupt register contains a copy of the lost interrupt bit and is implicitly cleared after the interrupt register is read. Bit 6 is always 0.

Table 8. Interrupt Vector Register (Continued)

| Code* | Interrupt | Name/Description                                                                                                                                                                                                                                                            |

|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | FRMRX-W   | Frame Reject Transmitted $-$ W = 1.** Receipt of command or response that is invalid or not implemented and cannot be corrected by retransmission.                                                                                                                          |

| 13    | FRMRX-X   | Frame Reject Transmitted $- X = 1.**$ Receipt of S or U frame with an information field that is not permitted.                                                                                                                                                              |

| 14    | FRMRX-Y   | Frame Reject Transmitted $-Y = 1.**$ Receipt of an I frame with an information field that exceeds the maximum established length, N1.                                                                                                                                       |

| 15    | FRMRX-Z   | Frame Reject Transmitted $-Z = 1.**$ Receipt of an invalid N(R).                                                                                                                                                                                                            |

| 16    | PKR       | Packet Received. This interrupt is issued after the XPC has received an I frame and stored its data field in main memory. V(R) points to the next element in the RLOOK table after this interrupt is issued.                                                                |

| 17    | XBA       | Transmitted Block Acknowledged. Issued when the XPC receives acknowledgment for one or more previously transmitted I frames.                                                                                                                                                |