# Ultra High CMR, Small Outline, 5 Lead, High Speed Optocoupler

## Technical Data

#### **Features**

- Function Compatible with HCPL-4504

- Surface Mountable

- Very Small, Low Profile JEDEC Registered Package Outline

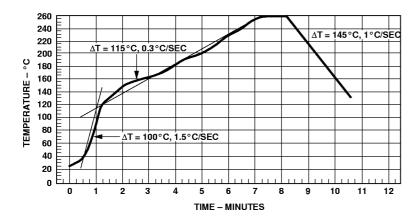

- Compatible with Infrared Vapor Phase Reflow and Wave Soldering Processes

- Short Propagation Delays for TTL and IPM Applications

- Very High Common Mode Transient Immunity: Guaranteed 15 kV/ $\mu$ s at  $V_{CM}$  = 1500 V

- High CTR: >25% at 25°C

- Guaranteed Specifications for Common IPM Applications

- TTL Compatible

- Guaranteed ac and dc Performance Over Temperature: 0°C to 70°C

- Open Collector Output

- Recognized Under the Component Program of U.L. (File No. E55361) for Dielectric Withstand Proof Test Voltage of 2500 Vac. 1 Minute

## **Applications**

- Inverter Circuits and Intelligent Power Module (IPM) Interfacing Shorter propagation delays and guaranteed (t<sub>PLH</sub> t<sub>PHL</sub>) specifications. (See Power Inverter Dead Time section).

- High Speed Logic Ground Isolation - TTL/TTL, TTL/ LTTL, TTL/CMOS, TTL/ LSTTL

#### HCPL-M454

- Line Receivers High common mode transient immunity (>15 kV/µs for a TTL load/drive) and low input-output capacitance (0.6 pF).

- Replace Pulse Transformers Save board space and weight

- Analog Signal Ground Isolation - Integrated photon detector provides improved linearity over phototransistors

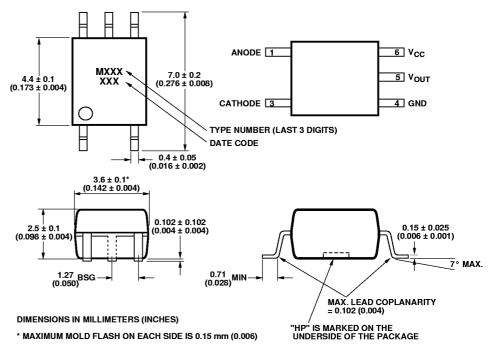

## **Outline Drawing (JEDEC MO-155)**

CAUTION: The small junction sizes inherent to the design of this bipolar component increase the component's susceptibility to damage from electrostatic discharge (ESD). It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

## **Description**

The HCPL-M454 is similar to HP's other high speed transistor output optocouplers, but with shorter propagation delays and higher CTR. The HCPL-M454 also has a guaranteed propagation delay difference ( $t_{PLH}$  -  $t_{PHL}$ ). These features make the HCPL-M454 an excellent solution to IPM inverter dead time and other switching problems.

The HCPL-M454 CTR, propagation delays, and CMR are specified both for TTL load and drive conditions and for IPM (Intelligent Power Module) load and drive conditions. Specifications and typical performance plots for both TTL and IPM conditions are provided for ease of application.

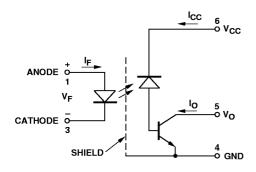

This diode-transistor optocoupler uses an insulating layer between the light emitting diode and an integrated photon detector to provide electrical insulation between input and output. Separate connections for the photodiode bias and output transistor collector increase the speed up to a hundred times over that of a conventional photo-transistor coupler by reducing the base-collector capacitance.

### **Absolute Maximum Ratings**

(No Derating Required up to 85°C)

| Storage Temperature                             | 55°C to +125°C                |

|-------------------------------------------------|-------------------------------|

| Operating Temperature                           |                               |

| Average Input Current - I <sub>F</sub>          | 25 mA <sup>[1]</sup>          |

| Peak Input Current - I <sub>F</sub>             | $50~\mathrm{mA^{[2]}}$        |

| (50%                                            | duty cycle, 1 ms pulse width) |

| Peak Transient Input Current - I <sub>F</sub>   | 1.0 A                         |

|                                                 | (≤1 µs pulse width, 300 pps)  |

| Reverse Input Voltage - $V_R$ (Pin 3-1)         | 5 V                           |

| Input Power Dissipation                         | $45 \text{ mW}^{[3]}$         |

| Average Output Current - I <sub>O</sub> (Pin 5) | 8 mA                          |

| Peak Output Current                             | 16 mA                         |

| Output Voltage - V <sub>O</sub> (Pin 5-4)       | 0.5 V to 20 V                 |

| Supply Voltage - V <sub>CC</sub> (Pin 6-4)      |                               |

| Output Power Dissipation                        | $100  \mathrm{mW^{[4]}}$      |

| Infrared and Vapor Phase Reflow Tem             |                               |

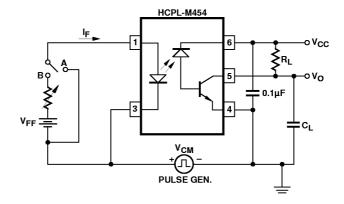

## **Schematic**

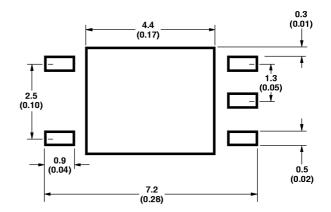

## **Pin Location**

## **Insulation Related Specifications**

| Parameter                                   | Symbol | Value | Units | Conditions                                         |

|---------------------------------------------|--------|-------|-------|----------------------------------------------------|

| Minimum External Air Gap<br>(Clearance)     | L(IO1) | ≥ 5   | mm    | Measured from input terminals to output terminals  |

| Minimum External Tracking Path (Creepage)   | L(IO2) | ≥ 5   | mm    | Measured from input terminals to output terminals  |

| Minimum Internal Plastic Gap<br>(Clearance) |        | 0.08  | mm    | Through insulation distance conductor to conductor |

| Tracking Resistance                         | CTI    | 175   | V     | DIN IEC 112/VDE 0303 Part 1                        |

| Isolation Group (per DIN VDE 0109)          |        | IIIa  |       | Material Group DIN VDE 0109                        |

DC Electrical Specifications Over recommended temperature ( $T_A = 0$ °C to 70°C) unless otherwise specified. (See note 11)

| Parameter                                                  | Symbol                            | Min. | Typ.   | Max. | Units            | Test Conditions          |                                                 |                                                |   | Note     |

|------------------------------------------------------------|-----------------------------------|------|--------|------|------------------|--------------------------|-------------------------------------------------|------------------------------------------------|---|----------|

| Current<br>Transfer                                        | CTR                               | 25   | 32     | 60   | %                |                          | $V_{\rm O} = 0.4 \text{ V}$                     | $I_F = 16 \text{ mA}$                          |   | 5        |

| Ratio                                                      | CMD                               | 21   | 34     | C.F  | 01               | m oroc                   | $V_{O} = 0.5 \text{ V}$ $V_{O} = 0.4 \text{ V}$ | $V_{CC} = 4.5 \text{ V}$ $I_F = 12 \text{ mA}$ |   | <u> </u> |

| Current<br>Transfer                                        | CTR                               | 26   | 35     | 65   | %                | $T_A = 25$ °C            |                                                 | •                                              |   | 5        |

| Ratio                                                      |                                   | 22   | 37     |      |                  |                          | $V_O = 0.5 \text{ V}$                           | $V_{\rm CC}$ = 4.5 V                           |   |          |

| Logic Low<br>Output                                        | $ m V_{OL}$                       |      | 0.2    | 0.4  | V .              | $T_A = 25$ °C            | $I_O = 3.0 \text{ mA}$                          | $I_F = 16 \text{ mA}$                          |   |          |

| Voltage                                                    | _                                 |      | 0.2    | 0.5  |                  |                          | $I_O = 2.4 \text{ mA}$                          |                                                |   |          |

| Logic High<br>Output                                       | $ m I_{OH}$                       |      | 0.003  |      | μΑ               |                          | $V_{\rm O} = V_{\rm CC} = 5.5 \text{ V}$        | $I_F = 0 \text{ mA}$                           | 5 |          |

| Current                                                    |                                   |      | 0.01   | 1.0  |                  | $I_A = 25^{\circ}C$      | $V_{\rm O} = V_{\rm CC} = 15 \text{ V}$         |                                                |   |          |

| Logic Low<br>Supply<br>Current                             | $I_{CCL}$                         |      | 50     | 200  | μA               | $I_{\mathrm{F}}$ = 16 mA | $V_{\rm CC}$ = 15 V                             | V <sub>O</sub> = open                          |   | 11       |

| Logic High<br>Supply                                       | $I_{CCH}$                         |      | 0.02   | 1    | μΑ               | $T_A = 25^{\circ}C$      | $I_F = 0 \text{ mA}$ $V_O = open$               | $V_{\rm CC}$ = 15 V                            |   | 11       |

| Current                                                    |                                   |      | 0.02   | 2    |                  |                          |                                                 |                                                |   |          |

| Input<br>Forward                                           | $ m V_F$                          |      | 1.5    | 1.7  | V                | $T_A = 25$ °C            | $I_F = 16 \text{ mA}$                           |                                                | 3 |          |

| Voltage                                                    |                                   |      | 1.5    | 1.8  |                  | T 10 A                   |                                                 |                                                |   |          |

| Input<br>Reverse<br>Breakdown<br>Current                   | $ m BV_R$                         | 5    |        |      | V                | $I_R = 10 \mu A$         |                                                 |                                                |   |          |

| Tempera-<br>ture Co-<br>efficient of<br>Forward<br>Voltage | $\Delta V_{ m F}/\Delta T_{ m A}$ |      | -1.6   |      | mV/°C            | $I_F = 16 \text{ mA}$    | Λ                                               |                                                |   |          |

| Input<br>Capacitance                                       | $\mathrm{C_{IN}}$                 |      | 60     |      | pF               | f = 1 MHz                | $V_F = 0 V$                                     |                                                |   |          |

| Input-<br>Output<br>Insulation<br>Voltage                  | $ m V_{ISO}$                      | 2500 |        |      | V <sub>RMS</sub> |                          | RH < 50%<br>$T_A = 25$ °C                       | t = 1 min                                      |   | 6,12     |

| Resistance<br>(Input-<br>Output)                           | R <sub>I-O</sub>                  |      | 10[12] |      | Ω                | $V_{\text{I-O}} = 500$   | Vdc                                             |                                                |   | 6        |

| Capacitance<br>(Input-<br>Output)                          | $\mathrm{C}_{	ext{I-O}}$          |      | 0.6    |      | рF               | f = 1 MHz                |                                                 |                                                |   | 6        |

Switching Specifications Over recommended temperature ( $T_A = 0$ °C to 70°C) unless otherwise specified

| Parameter                                                    | Sym.                        | Min. | Тур. | Max. | Units |                              | <b>Test Conditions</b>                                                                                                                                                                                                   | Fig.      | Note |

|--------------------------------------------------------------|-----------------------------|------|------|------|-------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|

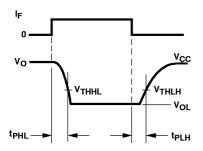

| Propagation Delay Time to Logic Low at Output                | $ m t_{PHL}$                |      | 0.2  | 0.3  | μs    | T <sub>A</sub> = 25°C        | $\begin{split} Pulse: & f = 20 \text{ kHz} \\ Duty & Cycle = 10\% \\ I_F = 16 \text{ mA} & V_{CC} = 5.0 \text{ V} \\ R_L = 1.9 \text{ k}\Omega & C_L = 15 \text{ pF} \\ V_{THHL} = 1.5 \text{ V} \end{split}$            | 8,9       | 9    |

|                                                              |                             | 0.2  | 0.5  | 0.7  |       | T <sub>A</sub> = 25°C        | $\begin{split} &Pulse: f = 10 \ kHz \\ &Duty \ Cycle = 50\% \\ &I_F = 12 \ mA \qquad V_{CC} = 15.0 \ V \\ &R_L = 20 \ k\Omega \qquad C_L = 100 \ pF \\ &V_{THHL} = 1.5 \ V \end{split}$                                  | 10-<br>14 | 10   |

| Propagation Delay Time to Logic High at Output               | $ m t_{PLH}$                |      | 0.3  | 0.5  | μs    | T <sub>A</sub> = 25°C        | $\begin{split} &Pulse: f = 20 \ kHz \\ &Duty \ Cycle = 10\% \\ &I_F = 16 \ mA \qquad V_{CC} = 5.0 \ V \\ &R_L = 1.9 \ k\Omega \qquad C_L = 15 \ pF \\ &V_{THLH} = 1.5 \ V \end{split}$                                   | 8,9       | 9    |

|                                                              |                             | 0.3  | 0.8  | 1.1  |       | T <sub>A</sub> = 25°C        | $\begin{split} & Pulse:  f = 10  kHz \\ & Duty  Cycle = 50\% \\ & I_F = 12  mA \qquad V_{CC} = 15.0  V \\ & R_L = 20  k\Omega \qquad C_L = 100  pF \\ & V_{THLH} = 2.0  V \end{split}$                                   | 10-<br>14 | 10   |

| Propagation<br>Delay<br>Difference<br>Between<br>Any 2 Parts | $ m t_{PLH}$ - $ m t_{PHL}$ | -0.4 | 0.3  | 0.9  | μs    | T <sub>A</sub> = 25°C        | $\begin{split} & Pulse: f = 10 \ kHz \\ & Duty \ Cycle = 50\% \\ & I_F = 12 \ mA \qquad V_{CC} = 15.0 \ V \\ & R_L = 20 \ k\Omega \qquad C_L = 100 \ \ pF \\ & V_{THHL} = 1.5 \ V \qquad V_{THLH} = 2.0 \ V \end{split}$ | 10-<br>14 | 13   |

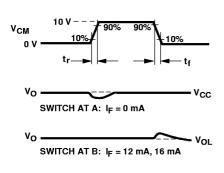

| Common<br>Mode<br>Transient<br>Immunity                      | CM <sub>H</sub>             | 15   | 30   |      | kV/μs | $T_A = 25^{\circ}C$          | $\begin{split} V_{CC} &= 5.0 \; V & R_L = 1.9 \; k\Omega \\ C_L &= 15 \; pF & I_F = 0 \; mA \\ V_{CM} &= 1500 \; V_{P\text{-}P} \end{split}$                                                                             | 7         | 7,9  |

| at Logic High Level Output                                   |                             | 15   | 30   |      |       | $T_{\rm A}=25^{\circ}{ m C}$ | $\begin{split} V_{CC} &= 15.0 \ V & R_L = 20 \ k\Omega \\ C_L &= 100 \ pF & I_F = 0 \ mA \\ V_{CM} &= 1500 \ V_{P\text{-}P} \end{split}$                                                                                 | 7         | 8,10 |

| Common Mode Transient Immunity at Logic Low Level Output     | CM <sub>L</sub>   1         | 15   | 30   |      | kV/μs | $T_A = 25^{\circ}C$          | $\begin{split} V_{CC} &= 5.0 \ V & R_L = 1.9 \ k\Omega \\ C_L &= 15 \ pF & I_F = 16 \ mA \\ V_{CM} &= 1500 \ V_{P\text{-}P} \end{split}$                                                                                 | 7         | 7,9  |

|                                                              |                             | 10   | 30   |      |       | $T_A = 25^{\circ}C$          | $\begin{split} V_{CC} &= 15.0 \ V & R_L = 20 \ k\Omega \\ C_L &= 100 \ pF & I_F = 12 \ mA \\ V_{CM} &= 1500 \ V_{P\text{-}P} \end{split}$                                                                                | 7         | 8,10 |

|                                                              |                             | 15   | 30   |      |       | $T_A = 25^{\circ}C$          | $\begin{split} V_{CC} &= 15.0 \ V & R_L = 20 \ k\Omega \\ C_L &= 100 \ pF & I_F = 16 \ mA \\ V_{CM} &= 1500 \ V_{P\text{-}P} \end{split}$                                                                                | 7         | 8,10 |

#### Notes:

- 1. Derate linearly above 70°C free-air temperature at a rate of 0.8 mA/°C.

- 2. Derate linearly above 70°C free-air temperature at a rate of 1.6mA/°C.

- 3. Derate linearly above 70°C free-air temperature at a rate of 0.9 mA/°C.

- 4. Derate linearly above 70°C free-air temperature at a rate of 2.0 mA/°C.

- 5. CURRENT TRANSFER RATIO in percent is defined as the ratio of output collector current  $(I_O)$ , to the forward LED input current  $(I_F)$ , times 100.

- Device considered a two-terminal device: Pins 1 and 3 shorted together and Pins 4, 5 and 6 shorted together.

- 7. Under TTL load and drive conditions: Common mode transient immunity in a Logic High level is the maximum tolerable (positive)  $dV_{CM}/dt$  on the leading edge of the common mode

- pulse,  $V_{CM}$ , to assure that the output will remain in a Logic High state (i.e.,  $V_O > 2.0$  V). Common mode transient immunity in a Logic Low level is the maximum tolerable (negative)  $dV_{CM}/dt$  on the trailing edge of the common mode pulse signal,  $V_{CM}$ , to assure that the output will remain in a Logic Low state (i.e.,  $V_O < 0.8$  V).

- 8. Under IPM (Intelligent Power Module) load and LED drive conditions: Common mode transient immunity in a Logic High level is the maximum tolerable  $dV_{CM}/dt$  on the leading edge of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in a Logic High state (i.e.,  $V_O > 3.0$  V). Common mode transient immunity in a Logic Low level is the maximum tolerable  $dV_{CM}/dt$  on the trailing edge of the

- common mode pulse signal,  $V_{CM}$ , to assure that the output will remain in a Logic Low state (i.e.,  $V_{O} < 1.0~V$ ).

- 9. The 1.9 k  $\Omega$  load represents 1 TTL unit load of 1.6 mA and the 5.6 k  $\Omega$  pull-up resistor.

- 10. The  $R_L=20~k\Omega,~C_L=100~pF~load$  represents an IPM (Intelligent Power Mode) load.

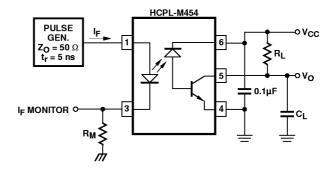

- 11. Use of a 0.1  $\mu F$  bypass capacitor connected between pins 4 and 6 is recommended.

- 12. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage  $\geq\!3000~V_{RMS}$  for 1 second (leakage detection current limit,  $I_{i-e}\leq 5~\mu A).$

- 13. The difference between  $t_{\rm PLH}$  and  $t_{\rm PHL}$ , between any two HCPL-M454 parts under the same test condition. (See Power Inverter Dead Time and Propagation Delay Specifications section).

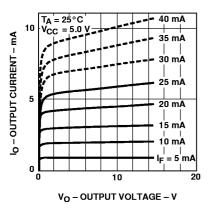

Figure 1. DC and Pulsed Transfer Characteristics.

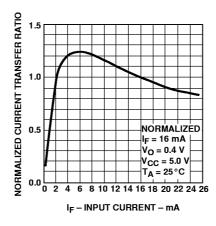

Figure 2. Current Transfer Ratio vs. Input Current.

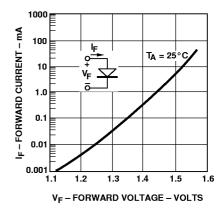

Figure 3. Input Current vs. Forward Voltage.

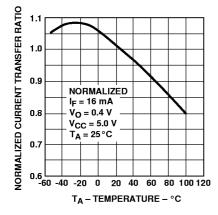

Figure 4. Current Transfer Ratio vs. Temperature.

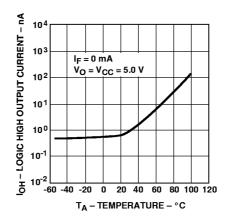

Figure 5. Logic High Output Current vs. Temperature.

Figure 6. Switching Test Circuit.

Figure 7. Test Circuit for Transient Immunity and Typical Waveforms.

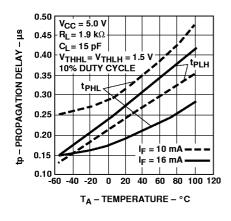

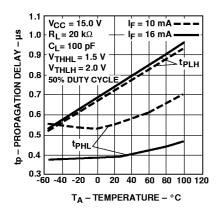

Figure 8. Propagation Delay Time vs. Temperature.

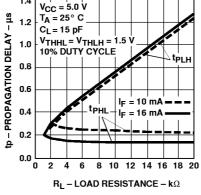

Figure 9. Propagation Delay Time vs. Load Resistance.

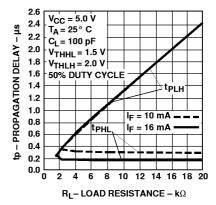

Figure 10. Propagation Delay Time vs. Load Resistance.

Figure 11. Propagation Delay Time vs. Temperature.

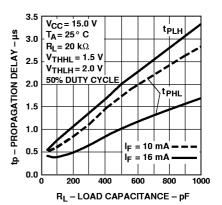

Figure 12. Propagation Delay Time vs. Load Resistance.

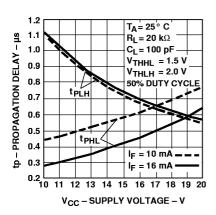

Figure 13. Propagation Delay Time vs. Load Capacitance.

Figure 14. Propagation Delay Time vs. Supply Voltage.

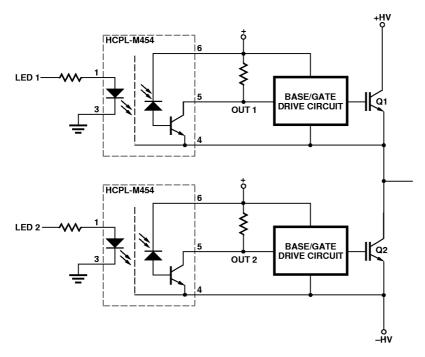

Figure 15. Typical Power Inverter.

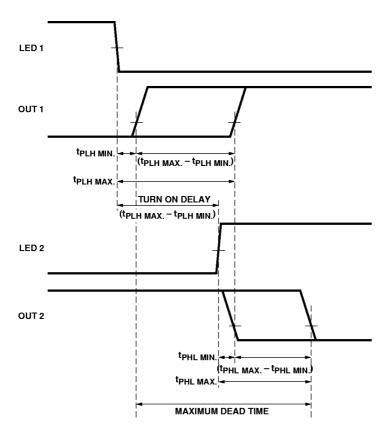

Figure 16. LED Delay and Dead Time Diagram.

### Power Inverter Dead Time and Propagation Delay Specifications

The HCPL-M454 includes a specification intended to help designers minimize "dead time" in their power inverter designs. The new "propagation delay difference" specification ( $t_{\rm PLH}$  -  $t_{\rm PHL}$ ) is useful for determining not only how much optocoupler switching delay is needed to prevent "shoot-through" current, but also for determining the best achievable wort-case dead time for a given design.

When inverter power transistors switch (Q1 and Q2 in Figure 15), it is essential that they never conduct at the same time. Extremely large currents will flow if there is any overlap in their conduction during switching transitions, potentially damaging the transistor and even the surrounding circuitry. This "shoot-through" current is eliminated by delaying the turn-on of one transistor (Q2) long enough to ensure that the opposing transistor (Q1) has completely turned off. This delay introduces a small amount of "dead time" at the output of the inverter during which both transistors are off during switching transitions. Minimizing this dead time is an important design goal for an inverter designer.

The amount of turn-on delay needed depends on the propagation delay characteristics of the optocoupler, as well as the characteristics of the transistor base/gate drive circuit. Considering only the delay characteristics of the optocoupler (the characteristics of the base/gate

drive circuit can be analyzed in the same way), it is important to know the minimum and maximum turn-on (t<sub>PHL</sub>) and  $turn-off(t_{PLH})$  propagation delay specifications, preferably over the desired operating temperature range. The importance of these specifications is illustrated in Figure 16. The waveforms labeled "LED1", "LED2", "OUT1", and "OUT2" are the input and output voltages of the optocoupler circuits driving Q1 and Q2 respectively. Most inverters are designed such that the power transistor turns on when the optocoupler LED turns on; this ensures that both power transistors will be off in the event of a power loss in the control circuit. Inverters can also be designed such that the power transistor turns off when the optocoupler LED turns on; this type of design, however, requires additional fail-safe circuitry to turn off the power transistor if an over-current condition is detected. The timing illustrated in Figure 16 assumes that the power transistor turns on when the optocoupler LED turns on.

The LED signal to turn on Q2 should be delayed enough so that an optocoupler with the very fastest turn-on propagation  $delay(t_{PHLmin})$  will never turn on before an optocoupler with the very slowest turn-off propagation delay  $(t_{PLHmax})$ turns off. To ensure this, the turn-on of the optocoupler should be delayed by an amount no less than  $(t_{PLHmax} - t_{PHLmin})$ , which also happens to be the maximum data sheet value for the propagation delay difference specification,  $(t_{PLH} - t_{PHL})$ . The

HCPL-M454 specifies a maximum ( $t_{PLH}$  -  $t_{PHL}$ ) of 1.3  $\mu s$  over an operating temperature range of 0-70°C.

Although  $(t_{PLH} - t_{PHL})_{max}$  tells the designer how much delay is needed to prevent shoot-through current, it is insufficient to tell the designer how much dead time a design will have. Assuming that the optocoupler turn-on delay is exactly equal to  $(t_{PLH} - t_{PHL})_{max}$ , the minimum dead time is zero (i.e., there is zero time between the turn-off of the very slowest optocoupler and the turn-on of the very fastest optocoupler).

Calculating the maximum dead time is slightly more complicated. Assuming that the LED turn-on delay is still exactly equal to  $(t_{PLH} - t_{PHL})_{max}$ , it can be seen in Figure 16 that the maximum dead time is the sum of the maximum difference in turn-on delay plus the maximum difference in turn-off delay,

$[(t_{PLHmax}-t_{PLHmin}) + (t_{PHLmax}-t_{PHLmin})],$

This expression can be rearranged to obtain

$[(t_{PLH_{max}}-t_{PHL_{min}}) - (t_{PHL_{min}}-t_{PHL_{max}})],$

and further rearranged to obtain

$[(t_{PLH}-t_{PHL})_{max}-(t_{PLH}-t_{PHL})_{min}],$

which is the maximum minus the minimum data sheet values of  $(t_{PLH} - t_{PHL})$ . The difference between the maximum and minimum values depends directly on the total spread of

propagation delays and sets the limit on how good the worstcase dead time can be for a given design. Therefore, optocouplers with tight propagation delay specifications (and not just shorter delays or lower pulse-width distortion) can achieve short dead times in power inverters. The HCPL-M454 specifies a minimum  $(t_{PLH} - t_{PHL})$  of -0.7  $\mu s$  over an operating temeprature range of 0-70°C, resulting in a maximum dead time of 2.0  $\mu s$  when the LED turn-on delay is equal to  $(t_{PLH} - t_{PHL})_{max},$  or 1.3  $\mu s$ .

It is important to maintain accurate LED turn-on delays because delays shorter than  $(t_{PLH} - t_{PHL})_{max}$  may allow shootthrough currents, while longer delays will increase the worst-case dead time.

www.hp.com/go/isolator

For technical assistance or the location of your nearest Hewlett-Packard sales office, distributor or representative call:

**Americas/Canada:** 1-800-235-0312 or 408-654-8675

Far East/Australasia: Call your local HP sales office.

**Japan:** (81 3) 3335-8152

Europe: Call your local HP sales office.

Data subject to change. Copyright © 1998 Hewlett-Packard Co.

Obsoletes 5962-9868E

Printed in U.S.A. 5966-4944E (5/98)