# **Advanced Analog**

a division of Intech

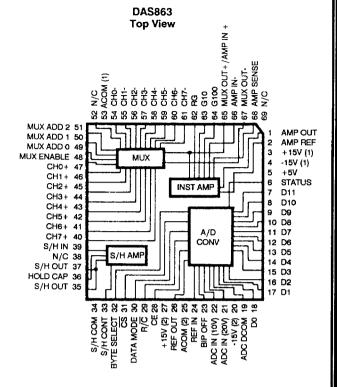

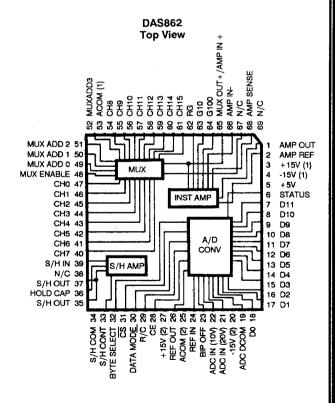

# DAS862/863

16 Single Ended 8 Differential Input 12-Bit Data Acquisition System

### **DESCRIPTION**

The DAS862/863 is a complete data acquisition subsystem packaged in a hermetically sealed 1" square leadless chip carrier or a 1.1" square pin grid array. The small size and low power consumption provide an ideal data acquisition solution when space is at a premium.

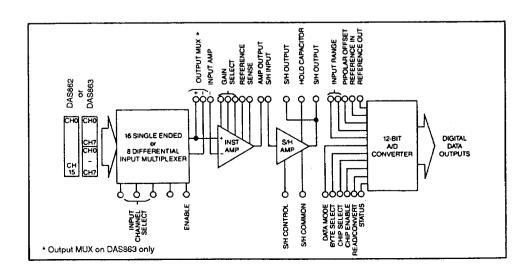

The device consists of an input multiplexer (DAS862 16 single ended inputs, DAS863 8 differential inputs), instrumentation amplifier with selectable gains, sample/hold amplifier and A/D converter with microprocessor interface and tristate buffers.

The DAS862/863 will accept unipolar or bipolar voltage inputs in the range of 0 to +10V, ±5V and ±10V. For low level signals, jumper selectable gains of 10 or 100 can be applied. The number of input channels can be expanded by the addition of multiplexers. The microprocessor interface and the facility of the sample/hold amplifier being controlled directly by the A/D converter simplifies system integration.

### **FEATURES**

- Complete 12-bit data acquisition subsystem

- Input ranges selectable for unipolar or bipolar operation

- Throughput rates

8-bit accuracy 45kHz

12-bit accuracy 33kHz

- $\ \square$  Selectable gains of 1, 10 and 100

- □ Full microprocessor compatible interface

- Guaranteed no missing codes over temperature

- Surface mount or pin grid array package options

- □ Full specification over three temperature ranges

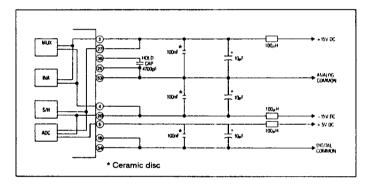

### **BLOCK DIAGRAM**

## **SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

+Vcc to ACOM -Vcc to ACOM +VDD to DCOM

-0.5V +0.5V to -16V -0.5V to +5.5V

Analog input signal range Digital input signal ACOM to DCOM

+Vcc +20V to -VCC -20V -0.5V to +Vpb  $\pm$ 1V

@ 25°C, Vcc = +15V, Vdd = +5V external sample/hold capacitor of 4700pF.

| Model                                                                                                                                                                                                                                                                                                                                 | DAS862/DAS863 J, A, R  |                                                                                        | DAS862                                         | DAS862/DAS863 K, B, S                                            |                 |                                                   |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------|-----------------|---------------------------------------------------|----------------------------------------------------------------------------------------|

| , moudi                                                                                                                                                                                                                                                                                                                               | min                    | typ                                                                                    | max                                            | min                                                              | typ             | max                                               | units                                                                                  |

| Resolution                                                                                                                                                                                                                                                                                                                            |                        |                                                                                        | 12                                             |                                                                  |                 | *                                                 | Bits                                                                                   |

| INPUT - ANALOG  Voltage Range - Bipolar  - Unipolar  Input impedance - on channel  - off channel  Input capacitance - on channel  - off channel  CMRR (20V, DC to 1kHz)  Crosstalk (20Vp-p, 1kHz)  Feedthrough (at 1kHz)  Offset (channel to channel) G = 1 <sup>2</sup> Input bias current/channel  Input voltage range <sup>3</sup> | +10                    | 10 <sup>10</sup><br>10 <sup>10</sup><br>20<br>20<br>60<br>-85<br>-85<br>30<br>1<br>+11 |                                                | ±10<br>-10<br> <br> | * * * * * * * * | * * * *                                           | V<br>V<br>Ω<br>pF<br>pF<br>dB<br>dB<br>dB<br>dB<br>v<br>V                              |

| DIGITAL Multiplexer channel select - Logic "1" (2V) - Logic "0" (0.8V)  S/H Command - Logic "1" (2V) - Logic "0" (0.8V)  ADC section - Logic "1" (2.4V) - Logic "0" (0.8V)                                                                                                                                                            |                        | 5<br>5<br>0.2<br>5                                                                     | 30<br>30<br>30<br>10                           |                                                                  | * * *           | * * * * *                                         | μΑ<br>μΑ<br>πΑ<br>μΑ<br>μΑ                                                             |

| TRANSFER CHARACTERISTICS  ACCURACY Integral linearity Differential linearity Gain error - G = 1 - G = 100 Unipolar offset error - Bipolar offset error - Noise error (measured at S/H output) G = 1 Droop rate Temperature coefficients - Unipolar offset - Bipolar offset - Full scale calibration                                   |                        | 0.7<br>0.9<br>16<br>50<br>0.5<br>50                                                    | ±0.024<br>±0.024<br>1<br>500<br>20<br>30<br>60 |                                                                  | * * * * *       | ±0.012<br>±0.012<br>*<br>*<br>*<br>15<br>25<br>35 | % of FSR<br>% of FSR<br>%<br>%<br>mV<br>mV<br>p-p<br>µV/mS<br>ppm FSR/°C<br>ppm FSR/°C |

| SYSTEM TIMINGS ADC conversion time S/H aperture delay S/H aperture uncertainty                                                                                                                                                                                                                                                        |                        | 20<br>50<br>2                                                                          | 25                                             |                                                                  | *               | *                                                 | μs<br>ns<br>ns                                                                         |

| TIMING Acquisition time (to 0.01% of final value for full scale step Throughput - serial mode - overlap mode                                                                                                                                                                                                                          |                        | 5                                                                                      | 45<br>30                                       |                                                                  | *               | *                                                 | μs<br>μs<br>μs                                                                         |

| OUTPUT - DIGITAL DATA Output codes - Unipolar - Bipolar Logic levels - Logic "0" (sink = 1.6mA) - Logic "1" (source = 500µA) Leakage (data bits only) high-Z state                                                                                                                                                                    | 2.4<br>-5              | 0.1                                                                                    |                                                | aight binary<br>ffset binary<br>*<br>*                           | *               | *                                                 | V<br>V<br>μΑ                                                                           |

| POWER SUPPLY REQUIREMENTS Rated voltage - Analog (±Vcc) - Digital (Vdd) Supply drain, +15V -15V +5V Power dissipation                                                                                                                                                                                                                 | 14.25<br>4.75          | 15<br>5<br>18<br>11<br>1<br>.44                                                        | 15.75<br>5.25<br>25<br>18<br>2                 | *                                                                | * * * * * *     | * * * * * *                                       | VDC<br>VDC<br>mA<br>mA<br>mA                                                           |

| TEMPERATURE RANGE Operating temperature range - JH, KH/JL, KL - AH, BH,AL, BL - RH, SH/RL, BL Storage temperature range                                                                                                                                                                                                               | 0<br>-25<br>-55<br>-65 |                                                                                        | 70<br>+85<br>+125<br>+150                      | *<br>*<br>*                                                      |                 | * * * *                                           | ဂံဂံဂံ                                                                                 |

#### Notes:

- 1. Measured at the sample and hold output.

- Measured with all input channels grounded.

The range of voltage on any input with respect to common over which accuracy and leakage current is guaranteed.

- 4. Applicable over full operating temperature range.

- 5. Adjustable to zero using external potentiometer or select on test resistor.

- \* Specification same as DAS862/863 J/A/R. No missing codes guaranteed over temperature.

#### **ANALOG TIMING SPECIFICATIONS**

| Parameter                         | Min    | Тур  | Max  | Units       |

|-----------------------------------|--------|------|------|-------------|

| MULTIPLEXER                       |        |      |      |             |

| Switching Time (between channels) |        | + 15 |      | μs          |

| Settling time                     |        |      |      |             |

| (10V step to 0.02%)               |        | 2.5  |      | μS          |

| Enable time ON OFF                |        | 0.25 | 0.5  | μS<br>μS    |

| INSTRUMENTATION                   |        | 0.20 | 0.0  |             |

| AMPLIFIER                         |        |      |      |             |

| Settling time to 0.01%<br>G = 1   | 1      | 5    | 12.5 | μs          |

| G = 10                            |        | 3    | 7.5  | μS          |

| G = 100                           |        | 4    | 7.5  | μs          |

| Slew rate                         | 12     | 17   |      | V/μs        |

| S/H AMPLIFIER Acquisition time    |        |      |      |             |

| (10V step to 0.01%                |        | 5    | Ì    | μs          |

| Aperture delay                    |        | 50   |      | ns          |

| Hold mode settling tir            | ne<br> | 1.5  |      | μs<br>V/μs  |

| Olow late                         | 1      | 1    |      | I <i>''</i> |

Note: Specifications are at +25°C and measured at 50% level of transition.

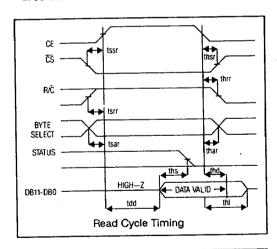

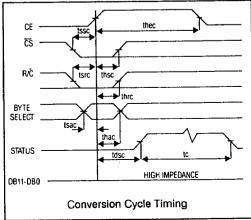

### **DIGITAL TIMING SPECIFICATIONS**

| Symbol Parameter                   | Min | Тур | Max      | Units |

|------------------------------------|-----|-----|----------|-------|

| CONVERT MODE                       |     |     |          |       |

| tdsc Status delay from CE          |     | 100 | 200      | ns    |

| thec CE pulse width                | 50  | 30  |          | ns    |

| tssc CS to CE setup                | 50  | 20  |          | ns    |

| thsc CS low during CE high         | 50  | 20  |          | ns    |

| tsrc R/C to CE setup               | 50  | 0   |          | ns    |

| thre R/C low during CE high        | 50  | 20  |          | ns    |

| tsac Byte select to CE setup       | 0   | 0   |          | ns    |

| thac Byte selected valid           |     | ļ   | <u> </u> |       |

| during CE high                     |     | 50  | 20       | ns    |

| tc Conversion time                 |     | 1   |          | '     |

| 12 bit cycle                       | 15  | 20  | 25       | μS    |

| 8 bit cycle                        | 10  | 13  | 17       | μs    |

| READ MODE                          |     |     |          |       |

| tdd Access time from CE            |     | 75  | 150      | ns    |

| thd Data valid after CE low        | 25  | 35  |          | ns    |

| thi Output float delay             |     | 100 | 150      | ns    |

| tssr CS to CE setup                |     | 50  | 0        | ns    |

| tsrr R/C to CE setup               | 0   | 0   | 1        | ns    |

| tsar Byte select to CE setup       | 50  | 25  |          | ns    |

| thsr CS valid after CE low         | 0   | 0   | 1        | ns    |

| thrr R/C high after CE low         | 0   | 0   |          | ns    |

| tharByte select valid after CE low | 50  | 25  | 1        | ns    |

| ths Status delay after data valid  | 300 | 500 | 1000     | ns    |

| CE         | <del>C</del> s | R/Ĉ | Data<br>Mode | Byte<br>Select | Operation                           |

|------------|----------------|-----|--------------|----------------|-------------------------------------|

| 0          | Х              | Х   | Х            | X              | None                                |

| ×          | 1              | Х   | Х            | Х              | None                                |

| 1 1        | 0              | 0   | X            | 0              | Initiate 12-bit conversion          |

| <b>\</b> ↑ | 0              | 0   | X            | 1              | Initiate 8-bit conversion           |

| 1          | 1              | 0   | Х            | 0              | Initiate 12-bit conversion          |

| 1          | Ĺ              | 0   | Х            | 1              | Initiate 8-bit conversion           |

| 1 1        | ŏ              | 1   | Х            | 0              | Initiate 12-bit conversion          |

| 1          | 0              | Ĭ   | Х            | 1              | Initiate 8-bit conversion           |

| 1          | 0              | i   | 1            | Χ              | Enable 12-bit output                |

| 1          | 0              | 1   | 0            | 0              | Enable 8 MSBs only                  |

| 1          | 0              | 1   | 0            | 1              | Enable 4 LSBs plus 4 trailing zeros |

Figure 1

Control Input Truth Table

| DAS862      |             |             |             |               |                     |             | Channel     |             |               |      |

|-------------|-------------|-------------|-------------|---------------|---------------------|-------------|-------------|-------------|---------------|------|

| MUX<br>ADD3 | MUX<br>ADD2 | MUX<br>ADD1 | MUX<br>ADD0 | MUX<br>Enable | Channel<br>Selected | MUX<br>ADD2 | MUX<br>ADD1 | MUX<br>ADD0 | MUX<br>Enable | Pair |

| х           | х           | ×           | х           | L.            | none                | х           | х           | х           | L             | none |

| L           | L           | L           | L           | н             | 0                   | L           | L           | L           | Н             | 0    |

| L           | L           | L           | н           | Н             | 1                   | L           | L           | н           | н             | 1    |

| L           | L           | Н           | L           | Н             | 2                   | L           | Н           | L           | н             | 2    |

| L           | L           | Н           | Н           | н             | 3                   | L           | н           | Н           | Н             | 3    |

| L           | н           | L           | L           | н             | 4                   | l H         | L           | L           | н             | 4    |

| Ĺ           | н           | L           | н           | Н             | 5                   | ļн          | L           | н           | н             | 5    |

| Ĺ           | Н           | н           | L           | н             | 6                   | Н           | Н           | L           | Н             | 6    |

| L           | н           | н           | н           | н             | 7                   | Н           | Н           | н           | н             | 7    |

| н           | L           | L           | L           | н             | 8                   |             | -           |             |               |      |

| H           | L           | L           | н           | Н             | 9                   | 1           | -           |             |               |      |

| Н           | L           | Н           | L           | н             | 10                  |             | -           |             |               |      |

| Н           | L           | Н           | н           | н             | 11                  | 1           | -           |             |               |      |

| н           | н           | L           | L           | Н             | 12                  | 1           | -           |             |               |      |

| н           | н           | L           | н           | Н             | 13                  | 1           | -           |             |               |      |

| н           | н           | Н           | L           | н             | 14                  | 1           | -           |             |               |      |

| н           | н           | н           | Н           | Н             | 15                  | 1           | -           |             |               |      |

Figure 2

Channel Select Truth Table

| RANGE   | -FS +1/2 LSB<br>000 TO 001 TRANSITION | +FS -1/2 LSB<br>FFE TO FFF TRANSITION | 1 LSB = |

|---------|---------------------------------------|---------------------------------------|---------|

| 0 - 10V | +0.0012V                              | + 9.9963V                             | 2.44mV  |

| ±5V     | -4.9988V                              | +4.9963V                              | 2.44mV  |

| ±10V    | -9.9976V                              | +9.9927V                              | 4.88mV  |

Figure 3

Code Transition Ranges

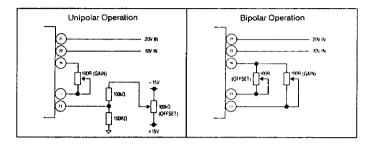

Figure 4

Calibration

Figure 5

Power Supply Connections and Recommended Decoupling

### **ORDERING INFORMATION**

| DAS862<br>16 Single Ended Inputs |     |                    |                                                          |                                                                  |        |                           |                                      |                                                                        |  |

|----------------------------------|-----|--------------------|----------------------------------------------------------|------------------------------------------------------------------|--------|---------------------------|--------------------------------------|------------------------------------------------------------------------|--|

| Grade                            | Pac | pin<br>kage<br>PGA | Accuracy<br>%FSR                                         | Temp<br>Range<br>*C                                              | Grade  | 68-pi<br>Packag<br>LCC PC | ge Accuracy                          | Temp<br>Range<br>°C                                                    |  |

| J K A B R S                      |     | H H H H            | ±0.024<br>±0.012<br>±0.024<br>±0.012<br>±0.024<br>±0.012 | 0 - 70<br>0 - 70<br>-25 +85<br>-25 +85<br>-55 +125<br>-55 - +125 | JKAARR |                           | ±0.012<br>±0.024<br>±0.024<br>±0.024 | 0 - 70<br>0 - 70<br>-25 - +85<br>-25 - +85<br>-55 - +125<br>-55 - +125 |  |

### **PIN DESIGNATIONS**

### PIN FUNCTIONS

CH0 to CH15 - Pins 40 to 47 CH0 to CH7 (+, -) - Pins 54 to 61

Channel inputs

Analog inputs, 16 total, for single ended and differential operation. Inputs that are not used must be connected to analog common.

MUX out+/AMP in+ - Pin 65

Multiplexer high output

This is the multiplexer output on the DAS862. On the DAS863, it is the output of the positive selected inputs. It is connected internally to the positive input of the instrumentation amplifier.

MUX out - Pin 67 Multiplexer low output

This pin is used on the DAS863 only. It should be connected to the negative input of the instrumentation amplifier.

AMP in - Pin 66

Negative input of instrumentation amplifier

This should be connected to the analog common on the DAS862 and to the MUX OUT (Pin 67) on the DAS863.

AMP out - Pin 1

Output of instrumentation amplifier

This should be connected to the input of the sample/hold amplifier (Pin 39).

Amp Sense - Pin 68

Output sense line of instrumentation amplifier

Normally connected directly to A input (Pin 1).

AMP Ref - Pin 2

Reference for amplifier output

This pin will normally be connected to analog common. Care should be taken to minimize tracking and contact resistance to analog common to augment system accuracy.

S/H Out - Pin 35/37 Output of sample/hold amplifier

Two pins are provided to supply a guard ring around the hold capacitor pin. These pins should be connected to either ADC in (20V) or ADC in (10V) depending on the desired range.

Hold Cap - Pin 36

Connection for hold capacitor on sample/hold amplifier

The tracking to the hold capacitor should be as short as possible and have a guard ring set up using Pins 35 and 37.

ADC in (20V) - Pin 21 ADC in (10V) - Pin 22 Inputs to A/D converter

Should be connected to S/H amplifier. Use applicable pin for desired range.

RG, G10, G100 - Pins 62 - 64 Gain setting pins on instrumentation amplifier

Gain 1 - No connection. Gain 10 - Connect G10 to RG. Gain 100 - Connect G100 to RG.

Ref Out - Pin 26 10V reference voltage Reference voltage for the A/D converter.

Ref In, BIP off - Pins 23, 24

Reference input and offset input to A/D converter

Connect trimming potentiometers (or select on test resistors) for unipolar or bipolar operation. Refer to Figure 4.

S/H in - Pin 39 Input to sample/hold amplifier Connect to pin 1, amp out.

MUX Enable - Pin 48 Multiple enable/disable

Logic "1" on this pin will enable a selected channel on the internal multiplexer. Logic "0" deselects all channels.

MUX ADD 0 to MUX ADD 3 - Pins 49 to 52 Address inputs for channel selection

These address lines select a specific channel as shown in Figure 2.

S/H Control - Pin 33

Track/hold control on S/H amplifier

Logic "1" holds an analog value for conversion by the A/D converter. This line may be controlled by the status (Pin 6) of the converter to simplify external timing control.

S/H Common - Pin 34

Reference for S/H logic control

Connect to digital common.

D0 to D11 - Pins 7 - 18 Tri-state digital outputs

The 12 or 8 bit result of a conversion that is available as output on these pins. D0 is LSB and D11 is MSB.

#### Status - Pin 6

### Status of A/D converter

During a conversion cycle, this output is at logic "1". It may be used to directly control the sample/hold amplifier.

### **CE - Pin 28**

### Chip enable

The input must be at Logic "1" to initiate a conversion or read output data. Refer Figure 1.

#### **CS - Pin 31**

### Chip select

Input must be at Logic "0" to initiate a conversion or read output data. Refer Figure 1.

### **R/C - Pin 29**

### Read/convert

Data can be read when this pin is at logic "1" or a conversion can be initiated when this pin is at logic "0". This pin is usually connected to the R/W control line of a microprocessor based system. Refer Figure 1.

### Data Mode - Pin 30

#### Select 12 or 8 bit data

Logic "1" - All 12 output data bits are enabled simultaneously.

Logic "0" - MSBs and LSBs are controlled by byte select, Pin 32.

### Byte Select - Pin 32

### Byte address, short cycle

Byte select at logic "0" enables the 8 MSBs when reading output data. Byte select at logic "1" enables the 4 LSBs. 4 LSBs can be connected to four of the MSB lines for interconnection to an 8-bit bus. In start convert mode, logic "0" enables a 12-bit conversion, while logic "1" will short cycle the conversion to 8 bits. Refer Figure 1.

### +15V (1) +15V (2) - Pins 3, 27

### **Power supply**

Connect to +15V supply using decoupling techniques as shown in Figure 5.

#### -15V (1) -15V (2) - Pins 4, 20

#### **Power Supply**

Connect to -15V supply using decoupling techniques as shown in Figure 5.

## A COM (1), A COM (2) - Pins 53, 25

#### Analog common

A common (including a digital common) should be connected together at one point close to the device.

#### +5V - Pin 5

### Logic power supply

Connect to +5V digital supply line using decoupling technique shown in Figure 5.

#### ADC DCOM - Pin 19

### Reference for A/D converter control lines

Should be connected to S/H common at one point close to device.

#### N/C - Pin 38

No internal connection

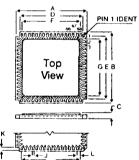

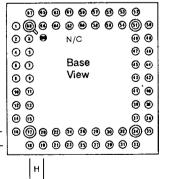

### MECHANICAL OUTLINE

#### Leadless Chip Carrier

L Package

|     | Inches     | Millimeters   |

|-----|------------|---------------|

| Dim | Min Max    | Min Max       |

| Α   | .945 .965  | 24.003 24.511 |

| В   | .945 .965  | 24.003 24.511 |

| C   | .076 .094  | 1.934 2.388   |

| D   | .841 .859  | 21.361 21.819 |

| E   | .841 .859  | 21.361 21.819 |

| F   | .755 .785  | 19.177 19.939 |

| G   | .755 .785  | 19.177 19.939 |

| н   | .800 Basic | 20.320 Basic  |

| J   | .027 .033  | .686 .838     |

| K   | .045 Basic | 1.143 Basic   |

| L   | .050 Basic | 1.270 Basic   |

Terminations: Gold plated nickel on refractory metallization. Case: White ceramic with gold plated nickel lid. Hermeticity: Gross leak test.

Weight: 4.2. grams (0.15 oz.)

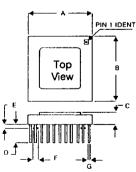

### Pin Grid Array

### H Package

Terminations: Gold plated KOVAR. Case: Black ceramic with gold plated nickel lid. Hermeticity: Gross leak test. Weight: 9 gms (0.32 oz.)

| Inches |       |       | Millimeters |        |  |

|--------|-------|-------|-------------|--------|--|

| Dim    | Min   | Max   | Min         | Мах    |  |

| A      | 1.087 | 1.109 | 27.610      | 28.169 |  |

| В      | 1.087 | 1.109 | 27.610      | 28.169 |  |

| С      | .095  | .120  | 2.413       | 3.048  |  |

| D      | .162  | .198  | 4.115       | 5.029  |  |

| Ε      | .045  | .055  | 1.143       | 1.397  |  |

| F      | .045  | .055  | 1.143       | 1.397  |  |

| G      | .016  | .020  | .406        | .508   |  |

| н      | .100  | Basic | 2.540       | Basic  |  |

| J      | .100  | Basic | 2.540       | Basic  |  |

©Advanced Analog

The information in this data sheet has been carefully checked and is believed to be accurate, however, no responsibility is assumed for possible errors. The specifications are subject to change without notice.

3-8901

Advanced Analog a division of Intech

MIL-STD-1772 Qualified 2270 Martin Avenue Santa Clara CA 95050-2781 (408) 988-4930 FAX (408) 988-2702

• 014428 X \_ X