## **T7230A Primary Access Framer/Controller**

#### **Features**

- Framing formats

- DS1 extended superframe (ESF)

- DS1 superframe (SF): D4; SLC<sup>®</sup>-96;

T1DM DDS; T1DM DDS with FDL access

- DS1 independent transmit and receive framing modes when using the ESF and D4 formats

- -- ITU-CEPT 2.048 Mbits/s basic frame

- ITU-CEPT selectable CRC-4 multiframe alignment algorithms: 100 ms timer; 400 ms interworking timer. Optional basic frame resynchronization with >915 CRC-4 checksum errors

- ITU-CEPT automatic received E-bit processing; optional detection of permanently received E bit = 0 events in a five-second interval

- Selectable automatic transmission for E bit to the line

- Line codes

- DS1: alternate mark inversion (AMI);

binary eight zero code suppression (B8ZS);

per-channel zero code suppression (ZCS)

- DS1 independent transmit and receive path line code formats when using AMI/ZCS and B8ZS coding

- TU-CEPT: AMI; high-density bipolar 3 (HDB3) encoding and decoding double bipolar violation monitoring with optional monitoring of 4-bit interval without positive or negative pulses error indication

- Signaling

- DS1: extended superframe 2-state, 4-state, and 16-state per-channel robbed bit

- DS1: D4 superframe 2-state and 4-state per-channel robbed bit

- DS1: SLC-96 superframe 2-state, 4-state, and 9-state per-channel robbed bit

- DS1: channel 24 message-oriented signaling

- ITU-CEPT: common channel signaling (CCS)

- ITU-CEPT: channel associated signaling (CAS)

- ITU-CEPT: international remote switching module (IRMS)

- Transparent (all data channels)

- Programmable elastic store buffer depth

- Two-frame (64-byte) default

- 6-byte option

- Digital phase comparator with selectable reference signal using either the system clock or the receive line clock

- Alarm reporting and performance monitoring

- ANSI and AT&T standard error checking

- Programmable ANSI yellow alarm processing

- ITU standard error checking

- Selectable interrupts enables

- Error counters: Bipolar violations

Errored frame alignment signals Errored CRC checksum block

- Errored seconds, severely errored seconds, and unavailable seconds processing

- Programmable automatic and on-demand alarm signal generation

- Multiple loopback modes

- Selectable test patterns for line transmission

- Programmable squelch and idle codes

- System interface

- One frame synchronization input signal

- One system interface clock

- Programmable clock edge for latching frame synchronization signal

- 2.048 Mbits/s, 2.048 MHz concentration highway interface (CHI) default mode

- Optional 2.048 Mbits/s, 4.096 MHz 32 time slots mode

- Optional 4.096 Mbits/s, 4.096 MHz 32 time slots mode

- Optional 4.096 Mbits/s, 8.196 MHz 32 time slots mode

- Programmable bit and byte offset

- Programmable clock edge for receive and transmit data

- Programmable CHI master mode for the generation of the CHI FS from internal logic with timing derived from the receive line clock signal

- Selectable microprocessor interface

- 16 MHz read and write access with no waitstates

- Programmable Intel\* and Motorola<sup>†</sup> interface modes

- Demultiplexed address and data bus

- Directly addressable internal registers

- Hardware reset

- Software reset

- 3-statable outputs

- \* Intel is a registered trademark of Intel Corporation.

- † Motorola is a registered trademark of Motorola, Inc.

## **Table of Contents**

| Contents                                                          | Page |

|-------------------------------------------------------------------|------|

| Features                                                          | 1    |

| Functional Description                                            |      |

| Pin Information                                                   |      |

| ISDN Primary Rate Interface                                       | 21   |

| Line Interface                                                    |      |

| Physical Interface                                                |      |

| Line Encoding                                                     | 23   |

| Single Rail                                                       |      |

| Alternate Mark Inversion (AMI)                                    |      |

| DS1 Zero Code Suppression (ZCS)                                   |      |

| T1 Binary 8 Zero Code Suppression                                 |      |

| High-Density Bipolar of Order 3 (HDB3)                            |      |

| Frame Formats                                                     |      |

| T1 Framing Structures                                             |      |

| Frame, Superframe, and Extended Superframe Definitions            |      |

| D4 Frame Format                                                   | 26   |

| Digital Data Service (DDS) Frame Format                           | 26   |

| SLC-96 Frame Format                                               | 27   |

| Extended Superframe                                               | 29   |

| T1 Loss of Frame Alignment (LFA)                                  | 30   |

| T1 Frame Recovery Alignment Algorithms                            |      |

| T1 Robbed-Bit Signaling                                           |      |

| SLC-96 9-State Signaling                                          |      |

| CEPT 2.048 Basic Frame Structure                                  |      |

| CEPT Loss of Basic Frame Alignment (LFA)                          | 33   |

| CEPT Loss of Frame Alignment Recovery Algorithm                   | 34   |

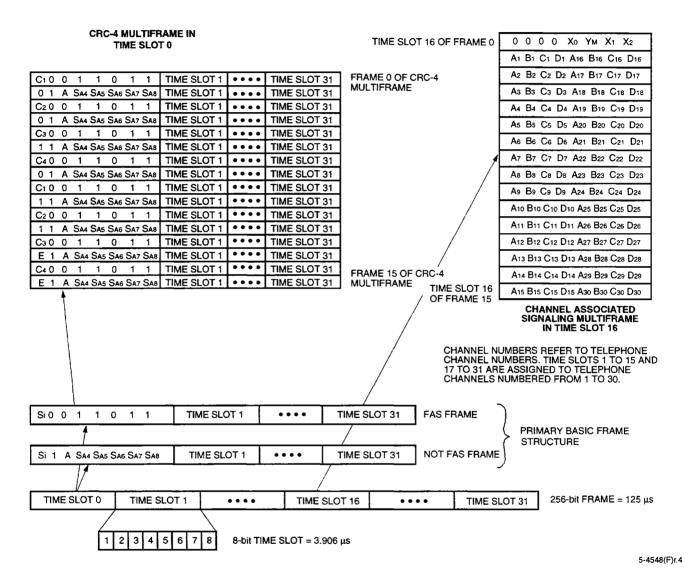

| CEPT Time Slot 0 CRC-4 Multiframe Structure                       |      |

| CEPT Loss of CRC-4 Multiframe Alignment (LTS0MFA)                 | 37   |

| CEPT Loss of CRC-4 Multiframe Alignment Recovery Algorithms       | 38   |

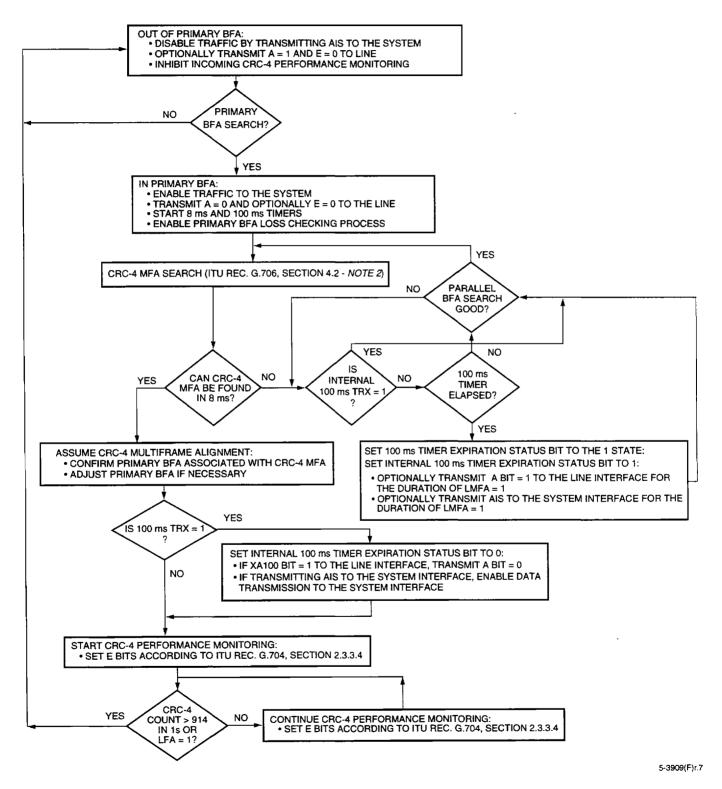

| CRC-4 Multiframe Alignment Algorithm with 8 ms Timer              | 38   |

| CRC-4 Multiframe Alignment Algorithm with 100 ms Timer            | 38   |

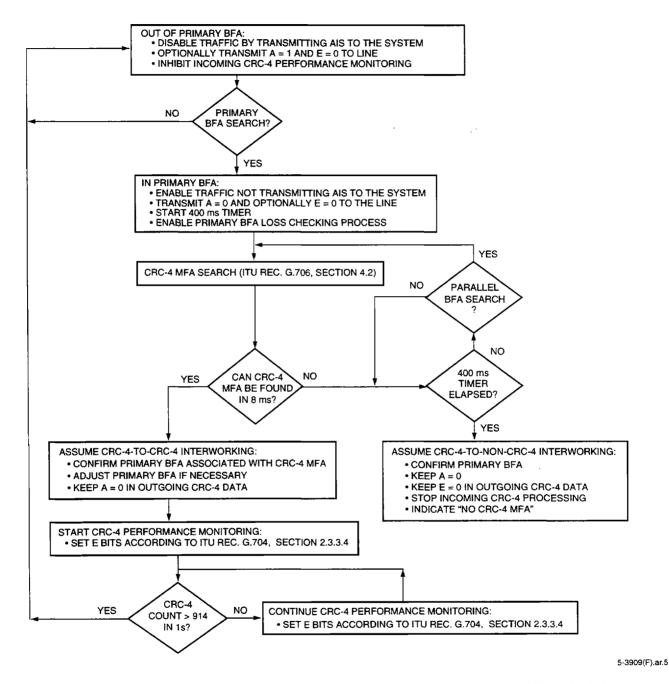

| CRC-4 Multiframe Alignment Search Algorithm with 400 ms Timer     | 40   |

| CEPT Time Slot 16 Multiframe Structure                            | 42   |

| Channel Associated Signaling                                      |      |

| IRSM Signaling                                                    | 43   |

| CEPT Loss of Time Slot 16 Multiframe Alignment (LTS16MFA)         |      |

| CEPT Loss of Time Slot 16 Multiframe Alignment Recovery Algorithm |      |

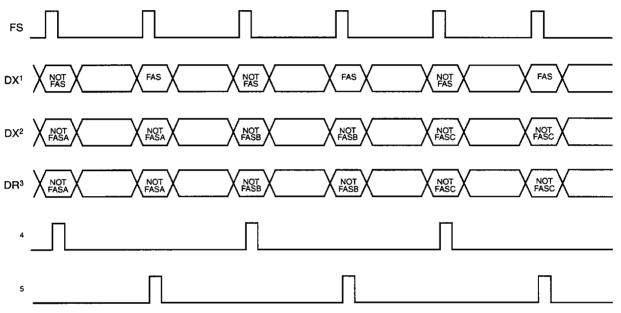

| CEPT Time Slot 0 FAS/NOT FAS Control Bits                         |      |

| FAS/NOT FAS Si- and E-Bit Source                                  |      |

| NOT FAS A-Bit Sources                                             |      |

| NOT FAS Sa-Bit Sources                                            |      |

| Sa Facility Data Link Access                                      |      |

| Microprocessor Sourcing of the Si and Sa4 to Sa8 Bits             |      |

| CEPT Time Slot 16 X0—X2 Control Bits                              |      |

| Signaling Access                                                  | 49   |

| Transparent Signaling (TSIG = 1)                                  |      |

| Microprocessor Control Registers                                  |      |

| Associated Signaling Mode                                         |      |

| Alarms and Performance Monitoring                                 |      |

| Loopback and Transmission Modes                                   |      |

| Transmit Line Test Patterns                                       |      |

| Automatic and On-Demand Commands                                  | 59   |

## Table of Contents (continued)

| Contents                                                               | Page |

|------------------------------------------------------------------------|------|

| Concentration Highway Interface (CHI)                                  | 61   |

| CHI Parameters                                                         | 62   |

| CHI Offset Programming                                                 | 63   |

| Phase-Lock Loop Circuit                                                | 65   |

| Microprocessor Interface                                               | 67   |

| Register Structure                                                     | 70   |

| Status/Counter Registers                                               | 71   |

| Interrupt Status Register (SR0)                                        | 71   |

| Facility Alarm Condition Register (SR1)                                |      |

| Remote End Alarm Register (SR2)                                        |      |

| Facility Errored Event Register (SR3)                                  |      |

| Facility Event Register 1 (SR4)                                        |      |

| Facility Event Register 2 (SR5)                                        |      |

| CRC-4 Error Counter Register (SR6—SR7)                                 |      |

| Errored Event Counter Register (SR8—SR9) — 16-Bit Counter              |      |

| Errored Seconds Counter Register (SR10—SR11)                           |      |

| Bursty Errored Seconds Counter Register (SR12—SR13)                    | 77   |

| Severely Errored Seconds Counter Register (SR14—SR15) — 16-Bit Counter |      |

| Unavailable Seconds Counter Register (SR16—SR17) — 16-Bit Counter      |      |

| Bipolar Violation Counter Register (SR18—SR19)                         |      |

| Frame Bit Error Counter Register (SR20)                                |      |

| Received Sa Register (SR21)                                            |      |

| Received Si and X Register (SR22)                                      |      |

| Received Signaling Registers: DS1 Format                               |      |

| Receive Signaling Registers: CEPT Format                               |      |

| Parameter/Control Registers                                            |      |

| Primary Interrupt Group Enable Register (PR0)                          |      |

| Framer Mode Option Register (PR1)                                      |      |

| Automatic Transmission Enable Register (PR2)                           |      |

| On-Demand Transmit Register 1 (PR3)                                    |      |

| On-Demand Transmit Register 2 (PR4)                                    |      |

| Framer Squelch Code Register (PR5)                                     |      |

| Transmit Sa Source Register (PR6)                                      |      |

| Si-Bit/X-Bit/E-Bit Source Register (PR7)                               |      |

| Framer Exercise Register (PR8)                                         |      |

| System Interface Control Register (PR9)                                | 88   |

| Signaling Mode Register (PR10)                                         |      |

| System Clock Control Register (PR11)                                   |      |

| Framer Idle Code Register (PR12)                                       |      |

| CHI Common Control Register (PR13)                                     | 91   |

| CHI Transmit Control Register (PR14)                                   | 91   |

| CHI Receive Control Register (PR15)                                    |      |

| CHI Transmit Time-Slot Enable Registers (PR16—PR19)                    |      |

| Receive Time-Slot Enable Registers (PR20—PR23)                         |      |

| CHI Transmit Highway Select Registers (PR24—PR27)                      |      |

| CHI Receive Highway Select Registers (PR28—PR31)                       |      |

| Transmit Signaling Registers: DS1 Format                               |      |

| Transmit Signaling Registers: CEPT Format                              |      |

## Table of Contents (continued)

| Contents                     | Page |

|------------------------------|------|

| Register Maps                | 95   |

| Status Registers             |      |

| Received Signaling Registers | 96   |

| Parameter Registers          | 97   |

| Transmit Signaling Registers | 98   |

| Absolute Maximum Ratings     | 99   |

| Handling Precautions         | 99   |

| Electrical Characteristics   |      |

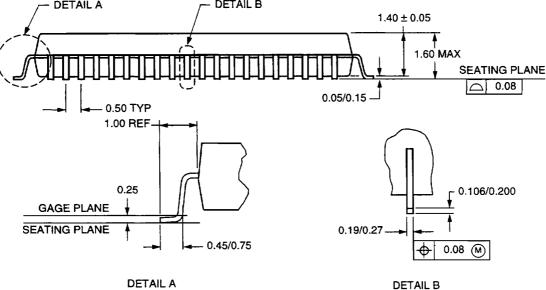

| Outline Diagrams             |      |

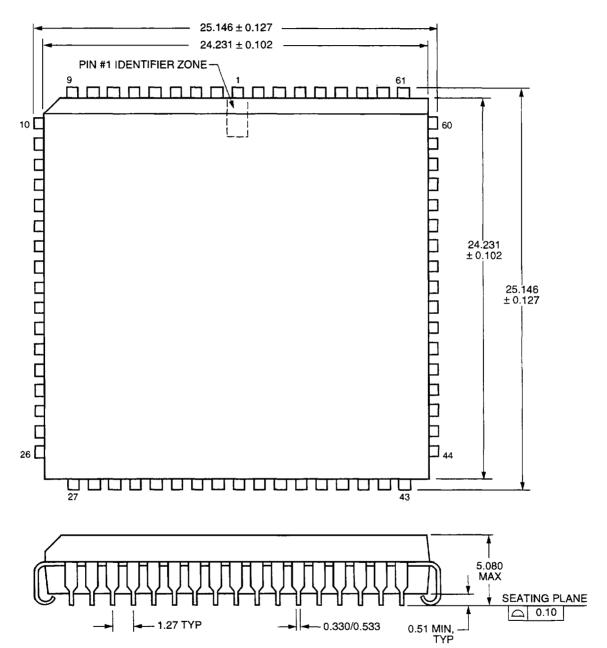

| 68-Pin PLCC                  | 101  |

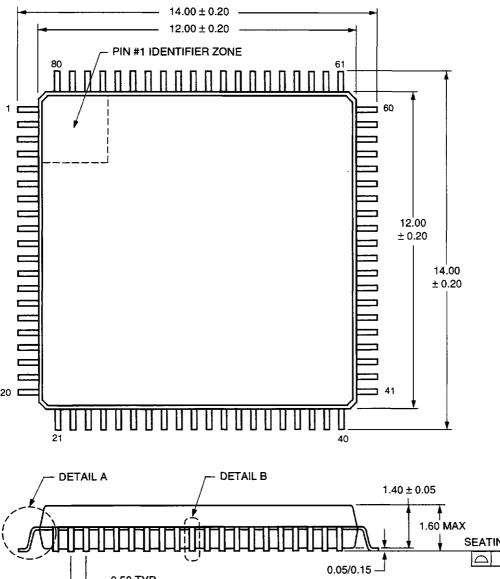

| 80-Pin TQFP                  |      |

| Ordering Information         |      |

| Index                        |      |

## **List of Tables**

| Tables                                                                                   | Page |

|------------------------------------------------------------------------------------------|------|

| Table 1. Pin Descriptions for the 68-Pin Package                                         | 13   |

| Table 2. Pin Descriptions for the 80-Pin Package                                         | 17   |

| Table 3. Single-Rail Encoding                                                            |      |

| Table 4. AMI Encoding                                                                    |      |

| Table 5. DS1 ZCS Encoding                                                                |      |

| Table 6. DS1 B8ZS Encoding                                                               |      |

| Table 7. ITU HDB3 Coding and DCPAT Binary Coding                                         | 24   |

| Table 8. T-Carrier Hierarchy                                                             |      |

| Table 9. D4 Superframe Format                                                            |      |

| Table 10. DDS Channel 24 Format                                                          | 26   |

| Table 11. SLC-96 Data Link Block Format                                                  | 28   |

| Table 12. SLC-96 Line Switch Message Codes                                               |      |

| Table 13. Extended Superframe (ESF) Structure                                            | 29   |

| Table 14. T1 Loss of Frame Alignment Criteria                                            | 30   |

| Table 15. T1 Frame Alignment Procedures                                                  |      |

| Table 16. Robbed-Bit Signaling Options                                                   | 32   |

| Table 17. SLC-96 9-State Signaling Format                                                | 32   |

| Table 18. Allocation of Bits 1 to 8 of the FAS Frame and the NOT FAS Frame               | 33   |

| Table 19. ITU CRC-4 Multiframe Structure of the T7230A                                   | 36   |

| Table 20. ITU CEPT Time Slot 16 Channel Associated Signaling Multiframe Structure        |      |

| Table 21. CEPT IRSM Signaling Multiframe Structure                                       | 43   |

| Table 22. Associated Signaling Mode CHI 2-Byte Time-Slot Format                          |      |

| Table 23. Associated Signaling Mode CHI 2-Byte Time-Slot Format for Stuffed Channels     |      |

| Table 24. Loss of Frame Alignment Alarm Conditions                                       |      |

| Table 25. Remote Frame Alarm Conditions                                                  |      |

| Table 26. Alarm Indication Signal Conditions                                             | 52   |

| Table 27. Sa6 Bit Coding Recognized by the T7230A Receive Framer                         |      |

| Table 28. Sa6 Bit Coding of NT1 Interface Events Recognized by the T7230A Receive Framer |      |

| Table 29. The T7230A Event Counters Definition                                           |      |

| Table 30. T7230A Automatic Enable Commands                                               |      |

| Table 31. T7230A On-Demand Commands                                                      |      |

| Table 32. Summary of the Concentration Highway Interface Parameter for the T7230A        |      |

| Table 33. Programming Values for XOFF[2:0] and ROFF[2:0] when CMS = 0                    |      |

| Table 34. Programming Values for XOFF[2:0] when CMS = 1                                  |      |

| Table 35. Programming Values for ROFF[2:0] when CMS = 1                                  |      |

| Table 36. T7230A Status and Control Blocks Address Range                                 |      |

| Table 37. Interrupt Status Register (SR0)                                                |      |

| Table 38. Facility Alarm Condition (SR1)                                                 | 72   |

| Table 39. Remote End Alarm Condition (SR2)                                               |      |

| Table 40. Facility Errored Event (SR3)                                                   |      |

| Table 41. Facility Event Register 1 (SR4)                                                |      |

| Table 42. Facility Event Register 2 (SR5)                                                | 76   |

| Table 43. CRC Error Counter Register (SR6—SR7)                                           |      |

| Table 44. Errored Event Counter Register (SR8—SR9)                                       |      |

| Table 45. Errored Seconds Counter Register (SR10—SR11)                                   | 77   |

| Table 46. Bursty Errored Seconds Counter Register (SR12—SR13)                            |      |

| Table 47. Severely Errored Seconds Counter Register (SR14—SR15)                          | 77   |

| Table 48. Unavailable Seconds Counter Register (SR16—SR17)                               |      |

| Table 49. Double Bipolar Violation Counter Register (SR18—SR19)                          |      |

| Table 50. Framing Bit Error Counter Register (SR20)                                      | 78   |

## List of Tables (continued)

| Tables                                                           | Page |

|------------------------------------------------------------------|------|

| Table 51. Receive Sa-Bit Register (SR21)                         | 78   |

| Table 52. Receive Sa-Bit and X-Bit Register (SR22)               | 78   |

| Table 53. Received Signaling Registers: DS1 Format (RSR0—RSR23)  | 79   |

| Table 54. Receive Signaling Registers: CEPT Format (RSR0—RSR31)  |      |

| Table 55. Primary Interrupt Group Enable Register (PR0)          |      |

| Table 56. Framer Mode Option Bits Decoding                       |      |

| Table 57. Automatic Transmission Enable Register (PR2)           | 82   |

| Table 58. On-Demand Register 1 Bits Decoding                     | 82   |

| Table 59. On-Demand Register 2 Bits Decoding                     | 83   |

| Table 60. Framer System Squelch Code Register (PR5)              | 84   |

| Table 61. Sa4—Sa8 Source Register (PR6)                          |      |

| Table 62. Si-Bit/X-Bit/E-Bit Source Register (PR7)               | 85   |

| Table 63. Framer Exercise Register (PR8)                         |      |

| Table 64. Framer Exercises, PR8, Bits 5—0                        |      |

| Table 65. Facility Alarm Interrupt Enable Register (PR9)         |      |

| Table 66. Signaling Mode Register (PR10)                         |      |

| Table 67. System Clock Control Register (PR11)                   |      |

| Table 68. Framer Line Idle Code Register (PR12)                  |      |

| Table 69. CHI Common Control Register (PR13)                     |      |

| Table 70. CHI Transmit Control Register (PR14)                   |      |

| Table 71. CHI Receive Control Register (PR15)                    |      |

| Table 72. CHI Transmit Time-Slot Enable Registers (PR16—PR19)    |      |

| Table 73. Receive Time-Slot Enable Registers (PR20—PR23)         |      |

| Table 74. CHI Transmit Highway Select Registers (PR24—PR27)      |      |

| Table 75. CHI Receive Highway Select Registers (PR28—PR31)       |      |

| Table 76. Transmit Signaling Registers: DS1 Format (TSR0—TSR23)  |      |

| Table 77. Transmit Signaling Registers: CEPT Format (TSR0—TSR31) |      |

| Table 78. Status Register Map                                    |      |

| Table 79. Receive Signaling Registers MAP                        |      |

| Table 80. Parameter Registers MAP                                |      |

| Table 81. Transmit Signaling Registers MAP                       | 98   |

| Table 82 FSD Threshold Voltage                                   | 90   |

# **List of Figures**

| Figures                                                                                         | Page |

|-------------------------------------------------------------------------------------------------|------|

| Figure 1. Basic T7230A System Interface Configuration                                           | 9    |

| Figure 2. Functional Block Diagram of the T1/E1 Primary Access Framer/Controller (PAC)          | 10   |

| Figure 3. The T7230A's 68-Pin Plastic Leaded Chip Carrier (PLCC) Package Option Pin Assignments | 11   |

| Figure 4. The T7230A's 80-Pin Thin Quad Flat Package (TQFP) Package Option Pin Assignments      | 12   |

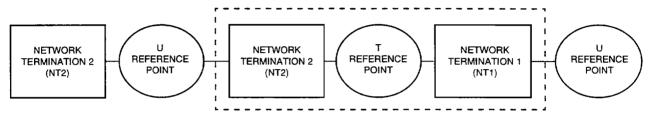

| Figure 5. ISDN Primary Rate Interface Reference Points                                          |      |

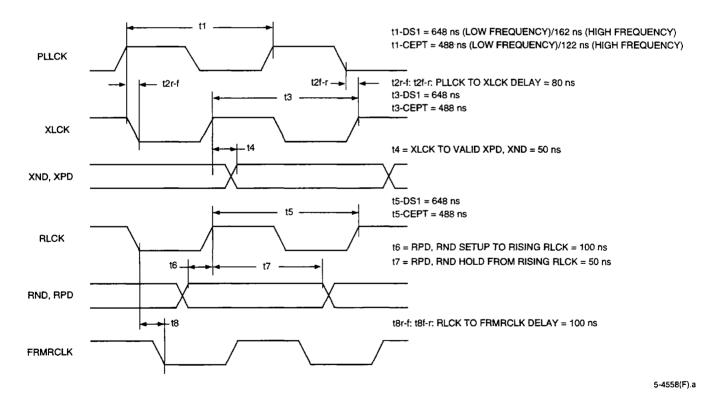

| Figure 6. Transmit Framer XLCK to XND, XPD and Receive Framer RND, RPD to RLCK Timing           | 22   |

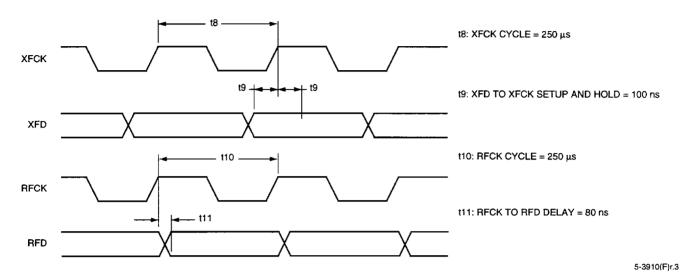

| Figure 7. T7230A Facility Data Link Timing                                                      | 23   |

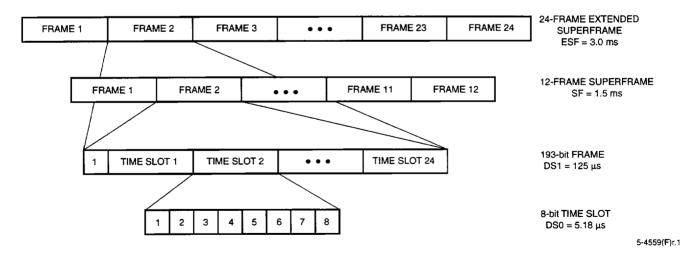

| Figure 8. T1 Frame Structure                                                                    | 25   |

| Figure 9. ITU 2.048 Basic Frame, CRC-4 Multiframe, and Channel Associated Signaling Multiframe  |      |

| Structures                                                                                      |      |

| Figure 10. Receive CRC-4 Multiframe Search Algorithm Using the 100 ms Internal Timer            | 39   |

| Figure 11. T7230A Receive CRC-4 Multiframe Search Algorithm for Automatic, CRC-4/Non-CRC-4      |      |

| Equipment Interworking as Defined by ITU (From ITU Rec. G.706, Annex B.2.2 - 1991)              |      |

| Figure 12. CEPT AFS and NOT FAS System Interface Format                                         | 47   |

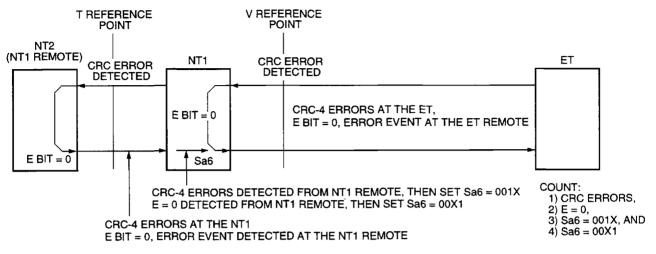

| Figure 13. The T and V Reference Points for a Typical CEPT E1 Application                       | 55   |

| Figure 14. T7230A's Loopback and Test Transmission Modes                                        |      |

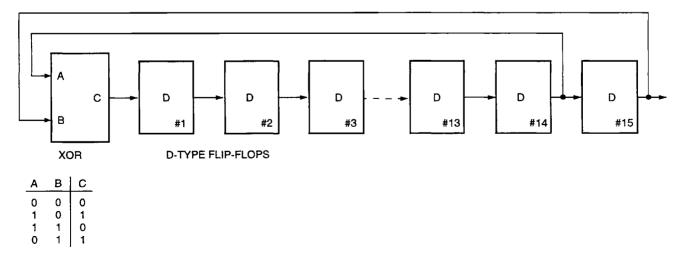

| Figure 15. 15-Stage Shift Register Used to Generate the Pseudorandom Signal                     |      |

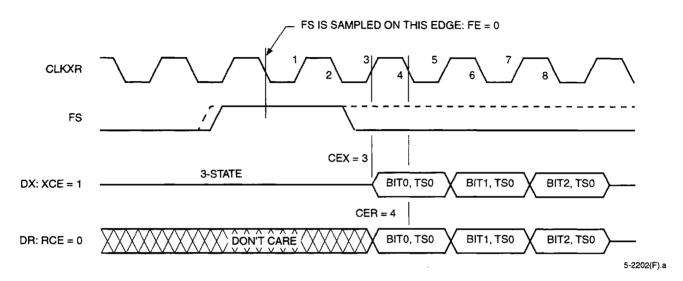

| Figure 16. CHI DX and DR to CLKXR Relationship with CMS = 0 (CEX = 3 and CER = 4, Respectively) | 64   |

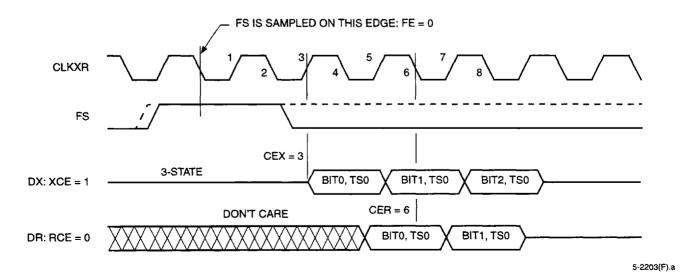

| Figure 17. CHI DX and DR to CLKXR Relationship with CMS = 1 (CEX = 3 and CER = 6, Respectively) |      |

| Figure 18. T7230A Phase Detector Circuitry                                                      | 66   |

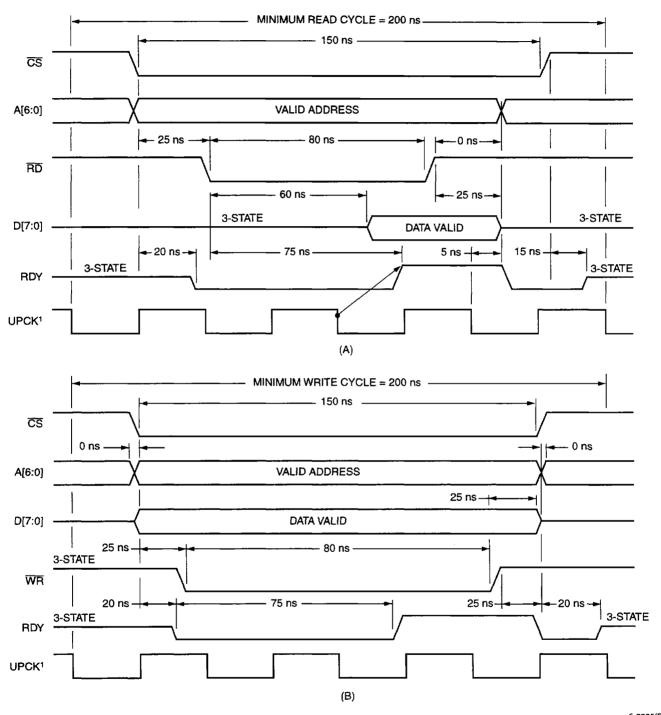

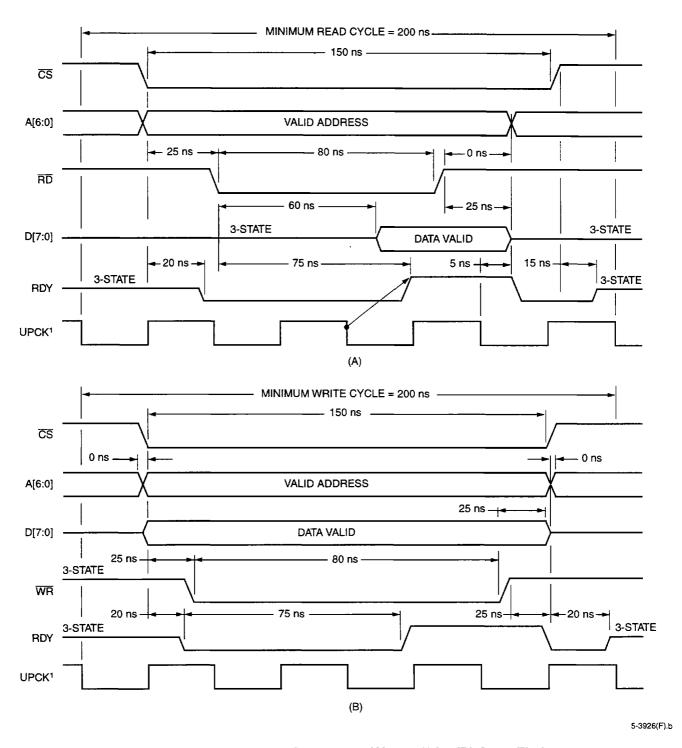

| Figure 19. Intel Interface Mode Read (A) and Write (B) Cycle Timing                             | 68   |

| Figure 20. Motorola Interface Mode Read (A) and Write (B) Cycle Timing                          | 69   |

## **Functional Description**

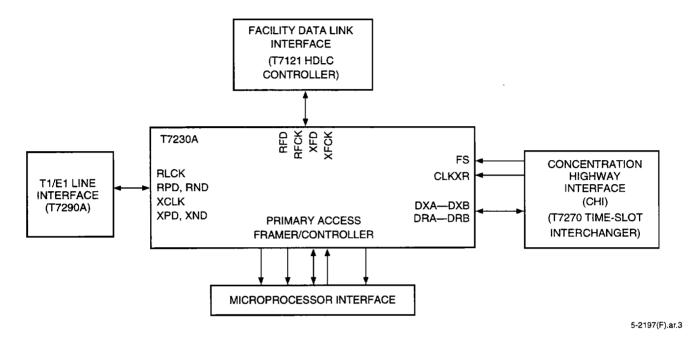

The Lucent Technologies T7230A Primary Access Controller/Framer (PAC) provides a complete T1 or E1 digital framing solution within one package. The T7230A can interface to devices using the Lucent Technologies Microelectronics Group system CHI; for example, the T7270 time-slot interchanger or T7115A synchronous protocol data formatter and DS1/T1 or ITU-CEPT line interface devices, such as the T7290A DSI/F1 line interface unit.

The line interface is a dual-rail interface that supports AMI, T1 B8ZS, per-channel T1 ZSC, and ITU-CEPT HDB3 line code formats. Optionally, the T7230A can transmit and receive single-rail line data.

Framing formats supported include T1D4, T1DM, and *SLC*-96 superframing and extended superframing; ITU-CEPT basic framing; and ITU-CEPT time slot 0 and time slot 16 multiframing.

Alarm monitoring by the receive framer includes detection of loss of receive clock, red, yellow, and blue (AIS) alarms. These alarms are detected as defined by ANSI, AT&T, and ITU standards. The transmit framer detects loss of transmit clock.

Performance monitoring as specified by AT&T, ANSI, and ITU is provided through counters monitoring frame bit errors, bipolar violation, CRC errors, errored events, errored seconds, bursty errored seconds, severely errored seconds, and unavailable or failed seconds.

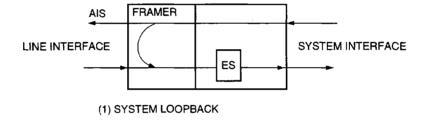

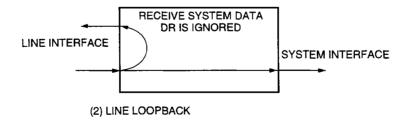

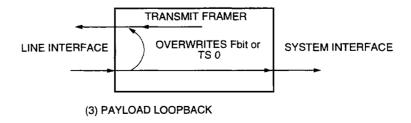

In-band loopback activation and deactivation codes can be transmitted to the line. In-band loopback activation and deactivation codes are detected.

Remote, payload, and line loopback modes are programmable.

The signaling formats supported are T1 per-channel robbed-bit signaling (RBS), channel-24 message-oriented signaling (MOS), ITU-CEPT channel-associated signaling (CAS), ITU-CEPT common channel signaling (CCS), and international remote switching module (IRMS). In the T1 RBS mode, voice and data channels are programmable. The entire payload can be forced into a no signaling, i.e., data only by programming one control bit.

Channelized data and its corresponding signaling information can be accessed through the system interface (concentration highway interface).

Extraction and insertion of the facility data link in ESF, T1DM, *SLC*-96, or ITU-CEPT modes is provided through a four-port serial interface.

A two-frame elastic store buffer for jitter attenuation performs controlled slips and provides indication of slip direction. This buffer can be programmed to operate as a function of the receive line clock and can be reduced to 11 bytes in length.

The system interface is a 2.048 Mbits/s data 2.048 MHz clock concentration highway interface (CHI) serial bus. This interface can be reconfigured into several modes: a 2.048 Mbits/s data/4.096 MHz clock; a 4.096 Mbits/s data/4.096 MHz clock; or a 4.096 Mbits/s data/8.192 MHz clock.

Accessing internal registers is done through a demultiplexed address and data bus microprocessor interface using either the *Intel* 80188 (or 80X88) interface protocol with independent read and write signals or the *Motorola* MC680X0 interface protocol with address and data strobe signals.

## Functional Description (continued)

The T7230A is manufactured using low-power CMOS technology and is packaged in an 68-pin plastic-leaded-chip-carrier (PLCC) or an 80-pin thin quad flat package (TQFP).

Figure 1. Basic T7230A System Interface Configuration

## Functional Description (continued)

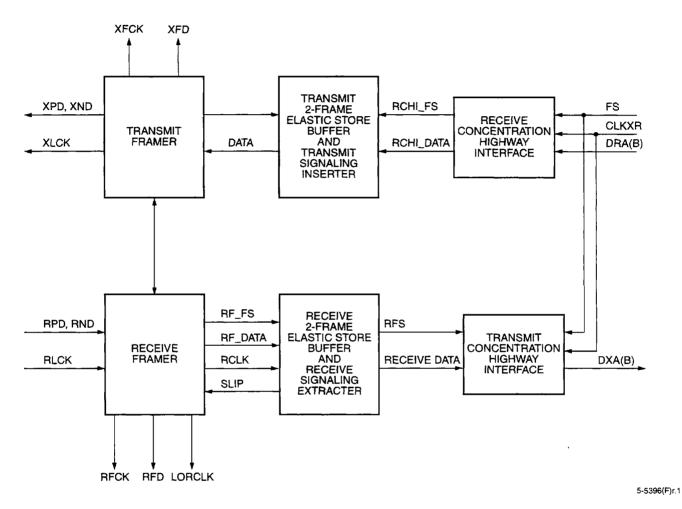

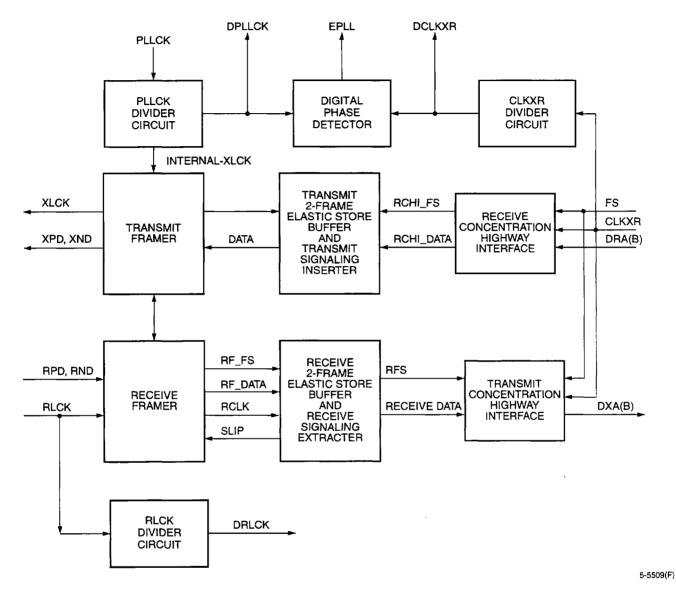

The block diagram of the T7230A is shown in Figure 2.

Figure 2. Functional Block Diagram of the T1/E1 Primary Access Framer/Controller (PAC)

#### Pin Information

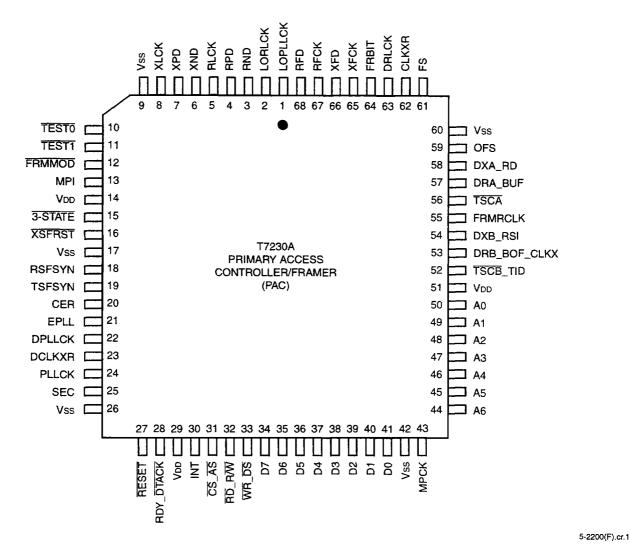

The 68-pin plastic leaded chip carrier (PLCC) package option type pin assignment for the T7230A is illustrated in Figure 3.

Figure 3. The T7230A's 68-Pin Plastic Leaded Chip Carrier (PLCC) Package Option Pin Assignments

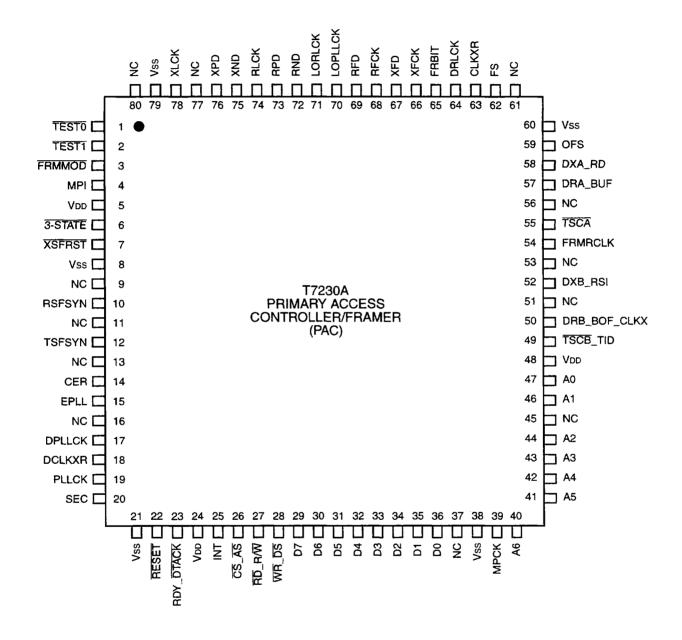

Available in an 80-pin thin quad flat package (TQFP) package option type, T7230A's pin assignment is illustrated in Figure 4.

5-5395(F)r.1

Figure 4. The T7230A's 80-Pin Thin Quad Flat Package (TQFP) Package Option Pin Assignments

Table 1 shows the list of T7230A pins and a functional description for each.

Table 1. Pin Descriptions for the 68-Pin Package

| Pin | Symbol  | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                           |

|-----|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LOPLLCK | 0                 | Loss of Transmit Clock. The T7230A drives this pin high when it detects PLLCK stuck in a 0 state or a 1 state for an interval greater than 250 µs.                                                                                                          |

| 2   | LORLCK  | 0                 | <b>Loss of Receive Clock.</b> The T7230A drives this pin high when it detects RLCK stuck in a 0 state or a 1 state for an interval greater than 250 μs.                                                                                                     |

| 3   | RND     | 1                 | Receive Negative-Rail Data. Dual-rail, non-return-to-zero serial data latched by the rising edge of RLCK. Data rates: DS1—1.544 Mbits/s; CEPT—2.048 Mbits/s. In single-rail mode, if RND = 1 at the rising edge of RLCK, the BPV counter increments by one. |

| 4   | RPD     | 1                 | Receive Positive-Rail Data. Dual-rail, non-return-to-zero serial data latched by the rising edge of RLCK. Data rates: DS1—1.544 Mbits/s; CEPT—2.048 Mbits/s. In single-rail mode, RPD is receive data.                                                      |

| 5   | RLCK    | 1                 | <b>Receive Line Interface Clock.</b> 1.544 MHz DS1 or 2.048 MHz input signal used by the receive framer.                                                                                                                                                    |

| 6   | XND     | 0                 | Transmit Negative-Rail Data. Dual-rail, non-return-to-zero serial data latched out by the rising edge of XLCK. Data rates: DS1—1.544 Mbits/s; CEPT—2.048 Mbits/s.                                                                                           |

| 7   | XPD     | 0                 | <b>Transmit Positive-Rail Data.</b> Dual-rail, non-return-to-zero serial data latched out by the rising edge of XLCK. Data rates: DS1—1.544 Mbits/s; CEPT—2.048 Mbits/s.                                                                                    |

| 8   | XLCK    | 0                 | <b>Transmit Line Interface Clock.</b> 1.544 MHz DS1 or 2.048 MHz input signal used by the transmit framer.                                                                                                                                                  |

| 9   | Vss     | _                 | Ground.                                                                                                                                                                                                                                                     |

| 10  | TEST0   | ļu                | Test 0 (Active-Low). Manufacture Testing Only.                                                                                                                                                                                                              |

| 11  | TEST1   | lπ                | Test 1 (Active-Low). Manufacture Testing Only.                                                                                                                                                                                                              |

| 12  | FRMMOD  | lu                | Framer Mode. Strap this pin to Vss (GROUND) to enable the framer mode.                                                                                                                                                                                      |

| 13  | MPI     | lα                | <b>Microprocessor Interface.</b> Strap to VDD to enable the <i>Intel</i> 80X86/88 protocol. Strap to Vss to enable the <i>Motorola</i> 680X0 protocol.                                                                                                      |

| 14  | VDD     |                   | 5 V Supply.                                                                                                                                                                                                                                                 |

| 15  | 3-STATE | ļu                | <b>3-State (Active-Low).</b> Asserting this pin low forces all outputs into a high-impedance state.                                                                                                                                                         |

| 16  | XSFRST  | ļu                | <b>Transmit Signaling Superframe Reset (Active-Low).</b> Assert this pin low to reset the DS1 signaling superframe counter and force a new signaling superframe structure.                                                                                  |

| 17  | Vss     |                   | Ground.                                                                                                                                                                                                                                                     |

| 18  | RSFSYN  | 0                 | Receive Signaling Superframe Sync. A 3 ms interval in DS1. A 2 ms interval in ITU-CEPT. Sourced from the CHI, this is an 8-bit wide pulse; sourced from the framer, this is a 1-bit wide pulse.                                                             |

| 19  | TSFSYN  | 0                 | <b>Transmit Signaling Superframe Sync.</b> A 3 ms interval in DS1. A 2 ms interval in ITU-CEPT. Sourced from the CHI, this is an 8-bit wide pulse; sourced from the framer, this is a 1-bit wide pulse.                                                     |

<sup>1.</sup> lu indicates an internal pull-up.

Table 1. Pin Descriptions for the 68-Pin Package (continued)

| Pin | Symbol    | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | CER       | 0                 | <b>Receive CRC Error.</b> Indication of a receive checksum error. In ESF, this pin is asserted at the onset of the CRC-6 error and remains asserted for the duration of the extended superframe. In CEPT, this pin is asserted once for the errored checksum block for a 1-byte interval.                                                                                                                    |

| 21  | EPLL      | 0                 | <b>Error Phase-Lock Loop Signal.</b> The error signal proportional to the phase difference between DCLKXR and DPLLCK as detected from the internal PLL circuitry.                                                                                                                                                                                                                                            |

| 22  | DPLLCK    | 0                 | <b>Divided-Down Phase-Lock Loop Clock.</b> 32 kHz or 8 kHz clock signal derived from the PLLCK input signal.                                                                                                                                                                                                                                                                                                 |

| 23  | DCLKXR    | 0                 | <b>Divided-Down CHI Clock.</b> 32 kHz or 8 kHz clock signal derived from the CLKXR input signal.                                                                                                                                                                                                                                                                                                             |

| 24  | PLLCK     |                   | Phase-Lock Loop Clock. This clock signal is used to clock the transmit framer. This signal should be phase-locked to the CLKXR clock signal.  DS1—1.544 MHz for low-frequency PLL mode.  DS1—6.167 MHz for high-frequency PLL mode.  CEPT—2.048 MHz for low-frequency PLL mode.  CEPT—8.192 MHz for high-frequency PLL mode.                                                                                 |

| 25  | SEC       | 0                 | <b>Second Pulse.</b> A one-second timer with an active-high pulse. The duration of the pulse is one RLCK cycle. Used for performance monitoring.                                                                                                                                                                                                                                                             |

| 26  | Vss       | _                 | Ground.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27  | RESET     | lu                | <b>Reset (Active-Low).</b> Asserting this pin low for at least 2.5 ms will reset the entire device; this includes all internal counters and control registers.                                                                                                                                                                                                                                               |

| 28  | RDY_DTACK | 0                 | Ready_Data Transfer Acknowledge. In the Intel interface mode, this pin is asserted high to indicate the completion of a read or write access; this pin is forced into a high-impedance state while CS is high.  In the Motorola interface mode, this pin is asserted low to indicate the completion of a read or write access; this pin is forced to a 1 state otherwise.                                    |

| 29  | VDD       |                   | 5 V Supply.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30  | INT       | 0                 | Interrupt. INT is asserted high, indicating an internal interrupt condition/ event has been generated. Otherwise, INT is in the 0 state. Interrupt events/ conditions are maskable through the control registers.                                                                                                                                                                                            |

| 31  | CS_AS     |                   | Chip Select_Address Strobe (Active-Low). In the Intel interface mode, this pin must be asserted low to initiate a read or write access and kept low for the duration of the access; asserting CS low forces RDY from its high-impedance state into a 0 state.  In the Motorola interface mode, this pin must be asserted low to initiate a read or write access and kept low for the duration of the access. |

<sup>1.</sup> I" indicates an internal pull-up.

Table 1. Pin Descriptions for the 68-Pin Package (continued)

| Pin   | Symbol       | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32    | RD_R/W       | 1                 | <b>Read_Read/Write.</b> While $\overline{\text{RD}}$ is low in the <i>Intel</i> interface mode, the T7230A drives the data bus with the contents of the addressed register. In the <i>Motorola</i> interface mode, this signal is asserted high for read accesses or asserted low for write accesses.                                                                                                                                                                                                                                                                                                    |

| 33    | WR_DS        | _                 | <b>Write_Data Strobe (Active-Low).</b> In the <i>Intel</i> mode, the value present on the data bus is latched into the addressed register on the positive edge of the signal applied to $\overline{WR}$ . In the <i>Motorola</i> mode, when $\overline{AS} = 0$ and $R/\overline{W} = 0$ (write), the value present on the data bus is latched into internal flip-flops on the positive edge of the signal applied to $\overline{DS}$ ; when $\overline{AS} = 0$ and $R/\overline{W} = 1$ (read), the T7230A drives the data bus with the contents of the addressed register while $\overline{DS} = 0$ . |

| 34—41 | D7—D0        | 1/0               | <b>Microprocessor Data Bus.</b> Bidirectional data bus used for read and write accesses. While the T7230A is not driving the data bus, the T7230A will force these pin into an high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 42    | Vss          | _                 | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 43    | MPCK         | i                 | <b>Microprocessor Clock.</b> 16 MHz microprocessor clock. Used only for timing the internal RDY signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4450  | A6A0         | I                 | <b>Microprocessor Address Bus.</b> Address bus used to access internal registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 51    | VDD          |                   | 5 V Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 52    | TSCB_TID     | I/O               | CHI Time-Slot Control for Port B. The T7230A drives this pin low to enable external bus drivers for active CHI time slots.  TID. In the framer mode (FRMMOD = 0), this is the input data signal for the transmit framer.                                                                                                                                                                                                                                                                                                                                                                                 |

| 53    | DRB_BOF_CLKX | l                 | Receive CHI Data Port B. Serial input system data at 2.048 Mbits/s or 4.096 Mbits/s.  Buffer Overflow. In framer mode (FRMMOD = 0), this may be used in performance monitoring to indicate an overflow event from an external elastic store.                                                                                                                                                                                                                                                                                                                                                             |

| 54    | DXB_RSI      | 0                 | Transmit CHI Data Port B. Serial output system data at 2.048 Mbits/s or 4.096 Mbits/s. This port is forced into a high-impedance state for all inactive time slots.  Receive Signaling Inhibit. In framer mode (FRMMOD = 0), this pin is forced to a 1-state for the duration of a loss of frame, loss of superframe (DS1), or loss of time slot 16 multiframe (CEPT) alignment state.                                                                                                                                                                                                                   |

| 55    | FRMRCLK      | 0                 | <b>Framer Receive Line Clock.</b> Framer receive line clock used in the receive framer section, derived from RLCK (same phase).                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 56    | TSCA         | 0                 | CHITime-Slot Control for Port A (Active-Low). The T7230A drives this pin low to enable external bus drivers for active CHI time slots.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

<sup>1.</sup> I' indicates an internal pull-up.

Table 1. Pin Descriptions for the 68-Pin Package (continued)

| Pin | Symbol  | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                                                                                                       |

|-----|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57  | DRA_BUF | 1                 | Receive CHI Data Port A. Serial input system data at 2.048 Mbits/s or 4.096 Mbits/s.  Buffer Underflow. In framer mode (FRMMOD = 0), this may be used in performance monitoring to indicate an underflow event from an external elastic store.                                                                                          |

| 58  | DXA_RD  | 0                 | Transmit CHI Data Port A. Serial output system data at 2.048 Mbits/s or 4.096 Mbits/s. This port is forced into a high-impedance state for all inactive time slots.  Receive Data. In framer mode (FRMMOD = 0), this is the serial uniral output data from the receive framer at 1.544 Mbits/s (DS1) or 2.048 Mbits/s (CEPT) rates.     |

| 59  | OFS     | 0                 | Output CHI Frame Sync. In the CHI master mode, the T7230A's receive CHI circuit generates an 8 kHz frame sync on this pin for use on the CHI.                                                                                                                                                                                           |

| 60  | Vss     |                   | Ground.                                                                                                                                                                                                                                                                                                                                 |

| 61  | FS      | 1                 | CHI Frame Sync. 8 kHz frame sync from a CHI master.                                                                                                                                                                                                                                                                                     |

| 62  | CLKXR   | l                 | CHI Transmit/Receive Clock. 2.048/4.096/8.192 MHz CHI clock signal. The PLLCK signal should be phase-locked to CLKXR.                                                                                                                                                                                                                   |

| 63  | DRLCK   | 0                 | <b>Divided-Down Receive Line Clock</b> . 8 kHz clock signal derived from the RLCK input signal.                                                                                                                                                                                                                                         |

| 64  | FRBIT   | 0                 | Receive Framing Bit. In DS1 framing formats, this pin outputs the value of the framing bit associated with the current CHI frame. The value is valid for the duration of the CHI frame. In CEPT mode, this pin is forced to a 1 state.                                                                                                  |

| 65  | XFCK    | 0                 | Transmit Facility Data Link Clock. In DS1-DDS with data link access, this is an 8 kHz clock signal. Otherwise, this is a 4 kHz clock signal.                                                                                                                                                                                            |

| 66  | XFD     | 1                 | Transmit Facility Data Link. Serial input facility data link bit stream for insertion into the transmit line data stream by the transmit framer. In DS1-DDS with data link access, this is an 8 kbits/s signal. Otherwise, this is a 4 kbits/s signal.                                                                                  |

| 67  | RFCK    | 0                 | Receive Facility Data Link Clock. In DS1-DDS with data link access, this is an 8 kHz clock signal. Otherwise, this is a 4 kHz clock signal.                                                                                                                                                                                             |

| 68  | RFD     | 0                 | Receive Facility Data Link. Serial output facility data link bit stream extracted from the receive line data stream by the receive framer. In DS1-DDS with data link access, this is an 8 kbits/s signal. Otherwise, this is a 4 kbits/s signal. During a loss of frame alignment, the receive framer will force this pin to a 1 state. |

<sup>1.</sup> I' indicates an internal pull-up.

Table 2. Pin Descriptions for the 80-Pin Package

| Pin | Symbol  | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                                                                                            |

|-----|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TEST0   | ļu                | TEST 0 (Active-Low). Manufacture Testing Only.                                                                                                                                                                                                                                                                               |

| 2   | TEST1   | ļu                | TEST 1 (Active-Low). Manufacture Testing Only.                                                                                                                                                                                                                                                                               |

| 3   | FRMMOD  | lu                | Framer Mode. Strap this pin to Vss (GROUND) to enable the framer mode.                                                                                                                                                                                                                                                       |

| 4   | MPI     | ļu                | <b>Microprocessor Interface.</b> Strap to VDD to enable the <i>Intel</i> 80X86/88 protocol. Strap to Vss to enable the <i>Motorola</i> 680X0 protocol.                                                                                                                                                                       |

| 5   | VDD     | _                 | 5 V Supply.                                                                                                                                                                                                                                                                                                                  |

| 6   | 3-STATE | ļu                | <b>3-State (Active-Low).</b> Asserting this pin low forces all outputs into a high-impedance state.                                                                                                                                                                                                                          |

| 7   | XSFRST  | ļu                | <b>Transmit Signaling Superframe Reset (Active-Low).</b> Assert this pin low to reset the DS1 signaling superframe counter and force a new signaling superframe structure.                                                                                                                                                   |

| 8   | Vss     |                   | Ground.                                                                                                                                                                                                                                                                                                                      |

| 9   | NC      | _                 | No Connect.                                                                                                                                                                                                                                                                                                                  |

| 10  | RSFSYN  | 0                 | Receive Signaling Superframe Sync. A 3 ms interval in DS1. A 2 ms interval in ITU-CEPT. Sourced from the CHI, this is an 8-bit wide pulse; sourced from the framer, this is a 1-bit wide pulse.                                                                                                                              |

| 12  | TSFSYN  | 0                 | Transmit Signaling Superframe Sync. A 3 ms interval in DS1. A 2 ms interval in ITU-CEPT. Sourced from the CHI, this is an 8-bit wide pulse; sourced from the framer, this is a 1-bit wide pulse.                                                                                                                             |

| 13  | NC      |                   | No Connect.                                                                                                                                                                                                                                                                                                                  |

| 14  | CER     | 0                 | Receive CRC Error. Indication of a receive checksum error. In ESF, this pin is asserted at the onset of the CRC-6 error and remains asserted for the duration of the extended superframe. In CEPT, this pin is asserted once for the errored checksum block for a 1-byte interval.                                           |

| 15  | EPLL    | 0                 | <b>Error Phase-Lock Loop Signal.</b> The error signal proportional to the phase difference between DCLKXR and DPLLCK as detected from the internal PLL circuitry.                                                                                                                                                            |

| 16  | NC      | _                 | No Connect.                                                                                                                                                                                                                                                                                                                  |

| 17  | DPLLCK  | 0                 | <b>Divided-Down Phase-Lock Loop Clock.</b> 32 kHz or 8 kHz clock signal derived from the PLLCK input signal.                                                                                                                                                                                                                 |

| 18  | DCLKXR  | 0                 | <b>Divided-Down CHI Clock.</b> 32 kHz or 8 kHz clock signal derived from the CLKXR input signal.                                                                                                                                                                                                                             |

| 19  | PLLCK   | 1                 | Phase-Lock Loop Clock. This clock signal is used to clock the transmit framer. This signal should be phase-locked to the CLKXR clock signal.  DS1—1.544 MHz for low-frequency PLL mode.  DS1—6.167 MHz for high-frequency PLL mode.  CEPT—2.048 MHz for low-frequency PLL mode.  CEPT—8.192 MHz for high-frequency PLL mode. |

| 20  | SEC     | 0                 | <b>Second Pulse.</b> A one-second timer with an active-high pulse. The duration of the pulse is one RLCK cycle. Used for performance monitoring.                                                                                                                                                                             |

<sup>1.</sup> lu indicates an internal pull-up.

Table 2. Pin Descriptions for the 80-Pin Package (continued)

| Pin            | Symbol    | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21             | Vss       |                   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22             | RESET     | Įυ                | Reset (Active-Low). Asserting this pin low for at least 2.5 ms will reset the entire device, this includes all internal counters and control registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 23             | RDY_DTACK | 0                 | <b>Ready_Data Transfer Acknowledge.</b> In the <i>Intel</i> interface mode, this pin is asserted high to indicate the completion of a read or write access; this pin is forced into a high-impedance state while $\overline{CS}$ is high. In the <i>Motorola</i> interface mode, this pin is asserted low to indicate the completion of a read or write access; this pin is forced to a 1 state otherwise.                                                                                                                                                                                               |

| 24             | VDD       |                   | 5 V Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25             | INT       | 0                 | Interrupt. INT is asserted high indicating an internal interrupt condition/ event has been generated. Otherwise, INT is in the 0 state. Interrupt events/ conditions are maskable through the control registers.                                                                                                                                                                                                                                                                                                                                                                                         |

| 26             | CS_ĀS     |                   | Chip Select_Address Strobe (Active-Low). In the <i>Intel</i> interface mode, this pin must be asserted low to initiate a read or write access and kept low for the duration of the access; asserting CS low forces RDY from its high-impedance state into a 0 state.  In the <i>Motorola</i> interface mode, this pin must be asserted low to initiate a read or write access and kept low for the duration of the access.                                                                                                                                                                               |

| 27             | RD_R/W    |                   | <b>Read_Read/Write.</b> While $\overline{\text{RD}}$ is low in the <i>Intel</i> interface mode, the T7230A drives the data bus with the contents of the addressed register. In the <i>Motorola</i> interface mode, this signal is asserted high for read accesses or asserted low for write accesses.                                                                                                                                                                                                                                                                                                    |

| 28             | WR_DS     | -                 | <b>Write_Data Strobe (Active-Low).</b> In the <i>Intel</i> mode, the value present on the data bus is latched into the addressed register on the positive edge of the signal applied to $\overline{WR}$ . In the <i>Motorola</i> mode, when $\overline{AS} = 0$ and $R/\overline{W} = 0$ (write), the value present on the data bus is latched into internal flip-flops on the positive edge of the signal applied to $\overline{DS}$ ; when $\overline{AS} = 0$ and $R/\overline{W} = 1$ (read), the T7230A drives the data bus with the contents of the addressed register while $\overline{DS} = 0$ . |

| 29—36          | D7—D0     | 1/0               | Microprocessor Data Bus. Bidirectional data bus used for read and write accesses. While the T7230A is not driving the data bus, the T7230A will force these pin into a high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 37             | NC        | _                 | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 38             | Vss       |                   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 39             | MPCK      | I                 | <b>Microprocessor Clock.</b> 16 MHz microprocessor clock. Used only for timing the internal RDY signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 40—44<br>46—47 | A6A0      | 1                 | <b>Microprocessor Address Bus.</b> Address bus used to access internal registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 45             | NC        |                   | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 48             | VDD       |                   | 5 V Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

<sup>1.</sup> I<sup>u</sup> indicates an internal pull-up.

Table 2. Pin Descriptions for the 80-Pin Package (continued)

| Pin | Symbol       | Type <sup>1</sup> | Name and Function                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49  | TSCB_TID     | I/O               | CHI Time-Slot Control for Port B. The T7230A drives this pin low to enable external bus drivers for active CHI time slots.  TID. In the framer mode (FRMMOD = 0), this is the input data signal for the transmit framer.                                                                                                                                                               |

| 50  | DRB_BOF_CLKX | 1                 | Receive CHI Data Port B. Serial input system data at 2.048 Mbits/s or 4.096 Mbits/s.  Buffer Overflow. In framer mode (FRMMOD = 0), this may be used in performance monitoring to indicate an overflow event from an external elastic store.                                                                                                                                           |

| 51  | NC           |                   | No Connect.                                                                                                                                                                                                                                                                                                                                                                            |

| 52  | DXB_RSI      | 0                 | Transmit CHI Data Port B. Serial output system data at 2.048 Mbits/s or 4.096 Mbits/s. This port is forced into a high-impedance state for all inactive time slots.  Receive Signaling Inhibit. In framer mode (FRMMOD = 0), this pin is forced to a 1 state for the duration of a loss of frame, loss of superframe (DS1), or loss of time slot 16 multiframe (CEPT) alignment state. |

| 54  | FRMRCLK      | 0                 | <b>Framer Receive Line Clock.</b> Framer receive line clock used in the receive framer section, derived from RLCK (same phase).                                                                                                                                                                                                                                                        |

| 55  | TSCA         | 0                 | CHI Time-Slot Control for Port A (Active-Low). The T7230A drives this pin low to enable external bus drivers for active CHI time slots.                                                                                                                                                                                                                                                |

| 56  | NC           | _                 | No Connect.                                                                                                                                                                                                                                                                                                                                                                            |

| 57  | DRA_BUF      | l                 | Receive CHI Data Port A. Serial input system data at 2.048 Mbits/s or 4.096 Mbits/s.  Buffer Underflow. In framer mode (FRMMOD = 0), this may be used in performance monitoring to indicate an underflow event from an external elastic store.                                                                                                                                         |

| 58  | DXA_RD       | 0                 | Transmit CHI Data Port A. Serial output system data at 2.048 Mbits/s or 4.096 Mbits/s. This port is forced into a high-impedance state for all inactive time slots.  Receive Data. In framer mode (FRMMOD = 0), this is the serial uniral output data from the receive framer at 1.544 Mbits/s (DS1) or 2.048 Mbits/s (CEPT) rates.                                                    |

| 59  | OFS          | 0                 | Output CHI Frame Sync. In the CHI master mode, the T7230A's receive CHI circuit generates an 8 kHz frame sync on this pin for use on the CHI.                                                                                                                                                                                                                                          |