**PRELIMINARY**

### BAND PASS FILTER FOR AUDIO SPECTRUM ANALYZER DISPLAY

#### **MI GENERAL DESCRIPTION**

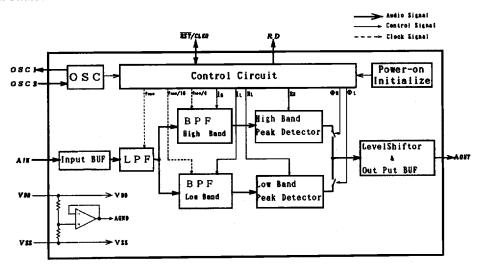

The NJU7508 is a band pass filter for audio spectrum analyzer display.

It consists of high and low band pass filters, CR oscillation circuit, control circuit and DC transfer circuit.

Each band pass filter using the switched capacitor filter technology operates at the shared time by 7 bands which filter constant is switched by the internal clock. Therefore, the audio signal shared of 7 bands is output from a serial output terminal.

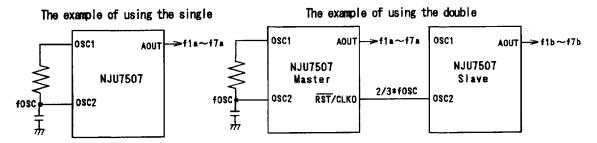

The 14 bands version using the double by the cascade connection is prepared.

#### III PACKAGE OUTLINE

NJU7508D

NJU7508M

# **FEATURES**

- BPF for the audio spectrum analyzer display

- of the 7 bands

- 14 bands extension is available by the cascade connection (Version of A: For 7 bands application by the single) (Version of B: For 14 bands application by the double)

- BPF using the switched capacitor filter technology

- CR oscillation circuit on chip (External clock input is available)

- Power-on initialization circuit on chip

(External reset input is available)

- C-MOS Technology

- Package Outline DIP8 / DMP8

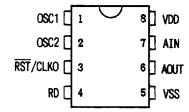

#### **III** PIN CONFIGURATION

### BLOCK DIAGRAM

#### TERMINAL DESCRIPTION

| NO. | 記号       | 機能                                                                        |

|-----|----------|---------------------------------------------------------------------------|

| 1   | OSC1     | External Resistor connecting terminal.                                    |

| 2   | OSC2     | External Resistor connecting terminal or External clock input terminal.   |

| 3   | RST/CLKO | Both as Reset input terminal and the clock of (2/3)*fosc output terminal. |

| 4   | RO       | Trigger signal for reading-out the Aout of each band output terminal.     |

| 5   | Vss      | GND 0 V                                                                   |

| 8   | Von      | Positive power supply +5.0 V                                              |

| 6   | Аоит     | Peak voltage of each band output terminal.                                |

| 7   | Ain      | Audio signal input terminal.                                              |

#### ■ VERSION LINEUP AND PEAK FREQUENCY

The NJU7507 prepares two version of A and B which are different of the peak frequency of each bands. The version of A is recommended for the 7 bands application using the single and the version of B is recommended for the 14 bands using the double by the cascade connection, however, the version of A can be used for the 14 bands using the double and the version of B can be used for the 7 bands using the single.

|      | Peak Frequency (Hz) |                  |                  |              |  |  |  |  |

|------|---------------------|------------------|------------------|--------------|--|--|--|--|

| Band | Using th            | e single         | Using the double |              |  |  |  |  |

|      | Version of A        | Version of B     | Version of A     | Version of B |  |  |  |  |

| fla  | 16k                 | 18k              | 16k              | 18k          |  |  |  |  |

| fib  |                     | _                | 10. 7k           | 12k          |  |  |  |  |

| f2a  | 6. 3k               | 8. 2k            | 6. 3k            | 8. 2k        |  |  |  |  |

| f2b  |                     |                  | 4. 2k            | 5. 5k        |  |  |  |  |

| f3a  | 2. 5k               | 3. 4k            | 2. 5k            | 3. 4k        |  |  |  |  |

| f3b  |                     | _                | 1. 7k            | 2. 3k        |  |  |  |  |

| f4a  | 1k                  | 1. 5k            | 1k               | 1. 5k        |  |  |  |  |

| f4b  |                     | _                | 670              | 1k           |  |  |  |  |

| f5a  | 400                 | 600              | 400              | 600          |  |  |  |  |

| f5b  | T                   | _                | 265              | 400          |  |  |  |  |

| f6a  | 160                 | 240              | 160              | 240          |  |  |  |  |

| f6b  |                     |                  | 107              | 160          |  |  |  |  |

| f7a  | 63                  | 95               | 63               | 95           |  |  |  |  |

| f7b  |                     | <del>-</del> 42* |                  | 63           |  |  |  |  |

Note) The bands of fla, f2a, ... f7a correspond to the master side and the bands of f1b, f2b, ... f7b correspond to the slave side at the cascade connection of the double.

Note) It may not be output along the expectation at the peak frequency of \* marking, since the sampling time is not enough.

#### **■ FUNCTIONAL DESCRIPTION**

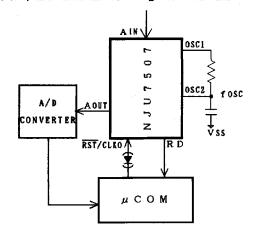

· Interface to external controller

The example of the interface between the NJU7507 and the external controller is shown below:

(1) Example of the interface to the external controller (Using the single)

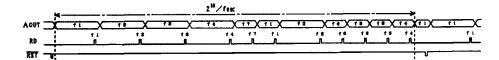

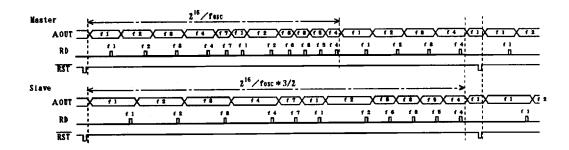

After the RST signal from the external controller is input and then the internal circuit is initialized, each band data is output as shown below timing chart;

Since the RD signal is output before each band is switched, the external controller is to count the number of the RD signal and is to recognize the status of the band and is to read the output data from the Agust terminal through the external A/D converter.

The output type of the external controller connected to the  $\overline{RST}/CLKO$  terminal as the  $\overline{RST}$  input should be the N-channel and open-drain type or the diode should be connected between the  $\overline{RST}/CLKO$  terminal and the output terminal of the external controller, so that the voltage of the  $\overline{RST}/CLKO$  terminal is not gotten over the  $V_{SS}$  level.

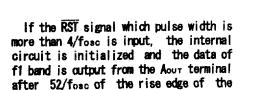

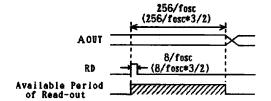

Since the RD signal is output before 256/fosc of each band switched, the output data should be read out within the limited time as shown right:

RST signal.

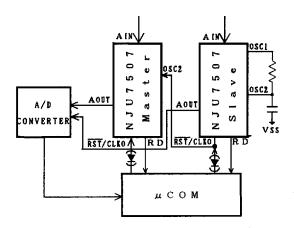

(2) Example of the interface to the external controller (Using the double)

The 14 bands application is available using the cascade connection of the double NJU7507 as shown blow.

After the RST signals from the external controller are input to each of the master and the slave of the NJU7507 and then each internal circuit is initialized, each band data is output as shown below timing chart;

Since the RD signals are output from the master and the slave before each band is switched, the external controller is to count the number of the RD signals and is to recognize the status of the band and is to read the output data from each  $A_{OUT}$  terminals through the external A/D converter.

The master clock for the slave is provided with the output signal from the  $\overline{RST}$ /CLKO terminal of the master. The master clock for the slave is stopped when the  $\overline{RST}$  signal is input from the external controller to the master, so that the  $\overline{RST}$ /CLKO terminal of the master is used both as the RST input of the master and the master clock for the slave.

The output type of the external controller connected to each  $\overline{RST}/CLKO$  terminal as the  $\overline{RST}$  input should be the N-channel and open-drain type or the diode's should be connected between each  $\overline{RST}/CLKO$  terminal and the output terminals of the external controller, so that the voltage of each  $\overline{RST}/CLKO$  terminal is not gotten over the  $V_{33}$  level.

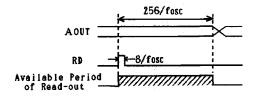

Since each RD signal of the master and the slave is output before  $256/f_{\rm osc}$  (  $256/f_{\rm osc}*2/3$  ) of each band switched, the output data should be read out within the limited time as shown right:

\* The "()" is corresponded to the slave.

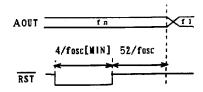

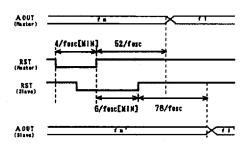

If the  $\overline{\text{RST}}$  signal which pulse width is more than 4/fosc is input to the master, the internal circuit is initialized and the data of f1 band is output from the  $A_{\text{OUT}}$  terminal of the master after 52/fosc of the rise edge of the  $\overline{\text{RST}}$  signal.

The RST signal for the slave should be set to "L" level while the RST signal for the master is "L" level and should keep "L" level more than 6/fosc. So the slave operates as same as the master after 78/fosc of the rise edge of the RST signal for the slave.

### ME ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER             | SYMBOL | RATINGS                   | UNIT | NOTE |

|-----------------------|--------|---------------------------|------|------|

| Supply Voltage        | Voo    | <b>-</b> 0. 3 <b>~→</b> 7 | TV   |      |

| Input Voltage         | VIN    | -0. 3~V₀₀+0. 3            | V    | 5    |

| Input vortage         | Vio    | -0.3~0                    | 7 '  | 3, 6 |

| Output Voltage        | Vout   | -0. 3~V₀₀+0. 3            | ٧    |      |

| Power Dissipation     | Po     | 250 (DIP) 200 (DMP)       | mW   |      |

| Operating Temperature | Topr   | -30~85                    | ာိ   |      |

| Storage Temperature   | Tata   | -55~125                   | ಌ    |      |

- Note 1) If the IC are used on condition above the absolute maximum ratings, the IC may be destroyed. Using the IC within electric characteristics conditions will cause malfunction and poor reliability.

- Note 2) All voltage values are specified as  $V_{88} = 0V$ .

- Note 3) When the voltage of the RST/CLKO terminal is gotten over the Vss level, the diode should be connected between the RST/CLKO terminal and the external

- Note 4) Decoupling capacitor should be connected between the V<sub>DD</sub> terminal and the V<sub>SS</sub> due to the stabilization of the operation.

- Note 5) Applied to the Ain or the OSC2 terminals.

- Note 6) Applied to the RST/CLKO terminal.

#### **ELECTRICAL CHARACTERISTICS**

#### DC CHARACTERISTICS

( $V_{DD}=5V$ ,  $V_{SS}=0V$ ,  $T_{a}=25^{\circ}C$ )

| PARAMETER             | SYMBOL           | CONDITI                   | TONS          | MIN     | TYP   | MAX   | UNIT     | NOTE    |

|-----------------------|------------------|---------------------------|---------------|---------|-------|-------|----------|---------|

| perating Voltage Vod  |                  | 4. 5                      | 5.0           | 6.0     | ٧ .   |       |          |         |

| Operating Current     | loo              | Dod TERMINAL              | -             | 6. 0    | 12    | mA    |          |         |

| Inner I ade Osenant 1 | liu              | AIN TERMINAL              | VILI=OV       | 0. 033  | 0.05  | 0. 1  | mA       |         |

| Input Leak Current 1  | Тінт             | ATH TEMPTRAL              | V: H:=5V      | -0. 033 | -0.05 | -0.1  |          |         |

| Input Leak Current 2  | 1162             | RST/CLKO TERMINAL V1H2=OV |               | 0.05    | 0.1   | 0. 2  | mA       |         |

| External Clock        | VILO             | OSC2 TERMINAL             |               | 0       | _     | 1.5   | V        |         |

| Input Voltage         | Vinc             |                           |               | 3. 5    | -     | 5.0   | l        |         |

| Order & Maldage 1     | Voli             | RD TERMINAL               | loL1=100 μA   | 0       | _     | 0.5   | ٧        |         |

| Output Voltage 1      | Von              | RU IERMINAL               | Іон₁≔-100 μ А | 4. 5    | ****  | 5.0   |          |         |

| Outros Valtages O     | Vol 2            | RST/CLKO                  | loL1=100 μA   | 0       | -     | 0. 5  | V        |         |

| Output Voltage 2      | V <sub>OH2</sub> | TERMINAL.                 | Іон₁=-10 μА   | 4. 25   | 4. 5  | 4. 75 | <b>\</b> |         |

| Output Offset Voltage | Vos              | AOUT TERMINAL AIN: OPEN   |               |         |       | 500   | mV       |         |

| ,                     | T ,,             | AOUT TERMINAL SIL         | ne Wave Input |         | 26. 0 |       | ď₿       | 7, 8, 9 |

| BPF Output Voltage    | Vout             | fin=f1~f7 Vii             | N=200mV p - p | 3. 5    |       |       | V        | 7, 8    |

- Note 7) This specification is tested on condition of  $f_{CLK}$ =400KHz (The external clock is input to the OSC2 terminal through the capacitor for AC coupling.

- Note 8) Each input frequency of f1 to f7 is reffered to the table of the "VERSION LINEUP AND PEAK FREQUENCY".

- Note 9) This specification is calculated from " Vout / VIN".

#### MAC CHARACTERISTICS

$(V_{00}=4.5\sim6.0V, V_{8s}=0V, Ta=25^{\circ}C)$

| PARAMETER                | SYMBOL | CONDITIONS        |                     | MIN              | ΤΥP                | MAX | UNIT | NOTE |

|--------------------------|--------|-------------------|---------------------|------------------|--------------------|-----|------|------|

| Oscillation Clock Freq.  | fosc   | RST/CLKO Terminal | Voo=5V              | 360              | 400                | 440 | KHz  | 10   |

| External Clock Frequency | folk   | RST/CLKO Terminal | Vilo=0V<br>Viho=Vod |                  | 400                | 800 | KHz  | 11   |

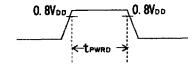

| DD D 1 W: 111            | Ī      | RD Terminal       | Master              |                  | 8/fosc<br>8/fclk   |     | με   | 12   |

| RD Pulse Width           | TPWRD  |                   | Slave               |                  | 12/fosc<br>12/folk |     |      |      |

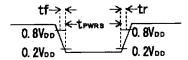

| DOT D. I W. Jul          |        | RST/CLKO Terminal | Master              | 4/fosc<br>4/fclk |                    |     | μs   | 13   |

| RST Pulse Width          | tpwas  |                   | Slave               | 6/fosc<br>6/fclk |                    |     |      |      |

| RST Rise/Fall Time       | tr, tf | RST/CLKO Terminal |                     |                  |                    | 100 | nA   | 13   |

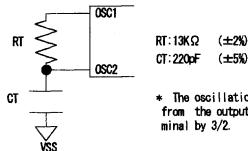

Note 10) The example for the CR Oscillation

(±5%)

\* The oscillation clock frequency is calculated from the output frequency of the RST/CLKO terminal by 3/2.

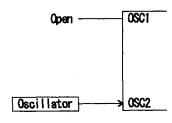

Note 11) The example for the external clock input

The input signal for the OSC2 terminal should be the condition of the pulse of DUTY50%±10%

\* The oscillation clock frequency is calculated from the output frequency of the RST/OLKO terminal by 3/2.

Note 12) The output wave form of the RD terminal.

Note 13) The input wave form of the  $\overline{\text{RST}}$  terminal.

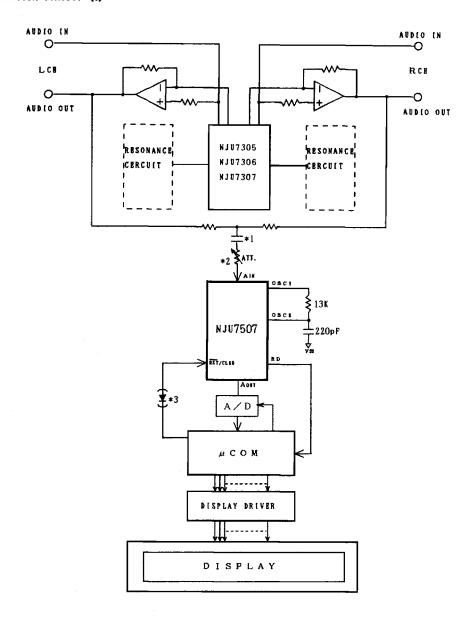

# MAPPLICATION CIRCUIT (1)

- \*1 ) The capacitor for AC coupling connected to the AIN terminal should be needed.

- \*2) Connecting the attenuator, the dynamic range of the display can be changed.

- \*3) When the voltage of the output terminal of the  $\mu$ COM gets over the V<sub>SS</sub> level, the diode should be connected between the RST/CLKO terminal and the output of the  $\mu$ COM.

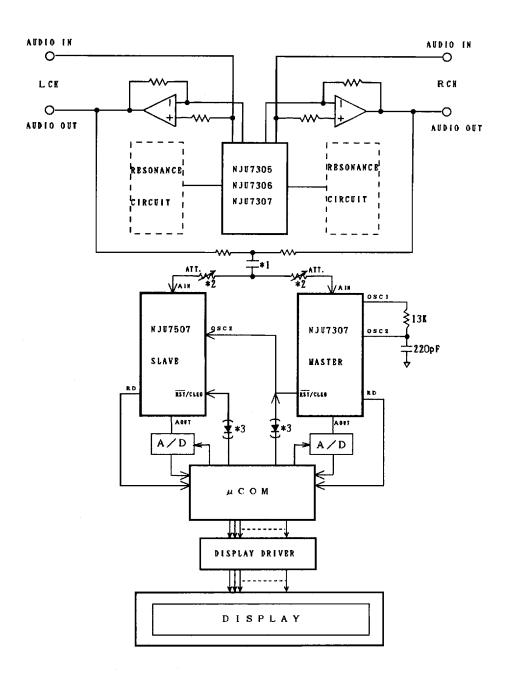

# MAPPLICATION CIRCUIT (2)

- \*1 ) The capacitor for AC coupling connected to the AIN terminal should be needed.

- \*2) Connecting the attenuator, the dynamic range of the display can be changed.

- \*3) When the voltage of the output terminal of the  $\mu$  COM gets over the V<sub>23</sub> level, the diode should be connected between the  $\overline{\rm RST}/{\rm OLKO}$  terminal and the output of the  $\mu$  COM.