D3004, JULY 1986

- Dual Circuits Capable of Driving High-Capacitance Loads at High Speeds

- Output Supply Voltage Range Up to 24 V

- Low Standby Power Dissipation

# description

The SN75372 is a dual NAND gate interface circuit designed to drive power MOSFETs from TTL inputs. It provides high current and voltage levels necessary to drive large capacitive loads at high speeds. The device operates from a VCC1 of 5 V and a VCC2 of up to 24 V.

The SN75372 is characterized for operation from 0  $^{\circ}$ C to 70  $^{\circ}$ C.

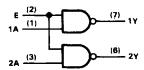

# logic symbol†

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

# logic diagram (positive logic)

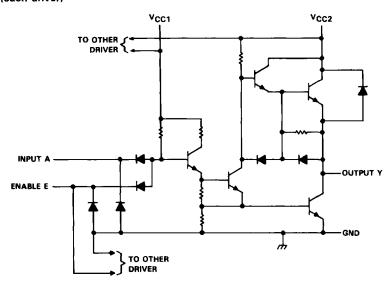

#### schematic (each driver)

PRODUCTION DATA documents cantain information current as of publication data. Products conform to specifications per the terms of Texas instruments standerd warrenty. Production processing does not necessarily include testing of all parameters.

Copyright © 1986, Texas Instruments Incorporated

# SN75372 DUAL MOSFET DRIVER

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range of VCC1 (see Note 1)                |                              |

|----------------------------------------------------------|------------------------------|

| Supply voltage range of VCC2                             | 0.5 V to 25 V                |

| Input voltage                                            | 5.5 V                        |

| Peak output current (tw < 10 ms, duty cycle < 50%): S    | ink                          |

| S                                                        | ource                        |

| Continuous total power dissipation                       | See Dissipation Rating Table |

| Operating free-air temperature range, TA                 | 0°C to 70°C                  |

| Storage temperature range                                |                              |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 sec | conds 260°C                  |

NOTE 1: Voltage values are with respect to network ground terminal.

#### DISSIPATION RATING TABLE

| PACKAGE | TA = 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE TA = 25°C | TA = 70°C<br>POWER RATING |

|---------|---------------------------|------------------------------------|---------------------------|

| D       | 725 mW                    | 5.8 mW/°C                          | 464 mW                    |

| Р       | 1000 mW                   | 8.0 mW/°C                          | 640 mW                    |

# recommended operating conditions

|                                    | MIN  | NOM | MAX  | UNIT |

|------------------------------------|------|-----|------|------|

| Supply voltage, VCC1               | 4.75 | 5   | 5.25 | V    |

| Supply voltage, VCC2               | 4.75 | 20  | 24   | V    |

| High-level input voltage, VIH      | 2    |     |      | ٧    |

| Low-level input voltage, VIL       |      |     | 0.8  | V    |

| High-level output current, IOH     |      |     | ~ 10 | mA   |

| Low-level output current, IOL      | -    |     | 40   | mA   |

| Operating free-air temperature, TA | 0    |     | 70   | °Č.  |

# electrical characteristics over recommended ranges of VCC1, VCC2, and operating free-air temperature (unless otherwise noted)

|                     | PARAMETER                                               |                | TEST CONDI                                                                            | TIONS                                           | MIN | TYP                                              | MAX          | UNIT |

|---------------------|---------------------------------------------------------|----------------|---------------------------------------------------------------------------------------|-------------------------------------------------|-----|--------------------------------------------------|--------------|------|

| VIK                 | Input clamp voltage                                     |                | I <sub>I</sub> = -12 mA                                                               |                                                 |     |                                                  | - 1.5        | V    |

| Voн                 | High-level output voltage                               | •              | $V_{ L} = 0.8 \text{ V},$ $V_{ L} = 0.8 \text{ V},$                                   | $I_{OH} = -50 \mu A$<br>$I_{OH} = -10 mA$       | 1   | V <sub>CC2</sub> - 0.8<br>V <sub>CC2</sub> - 1.8 |              | V    |

| VOL                 | Low-level output voltage                                | •              | V <sub>IH</sub> = 2 V,<br>V <sub>CC2</sub> = 15 V to 24 V,<br>I <sub>OL</sub> = 40 mA | $I_{OL} = 10 \text{ mA}$ $V_{IH} = 2 \text{ V}$ |     | 0.15<br>0.25                                     | 0.3          | V    |

| VF                  | Output clamp diode forward voltage                      |                | V <sub>1</sub> = 0,                                                                   | 1 <sub>F</sub> = 20 mA                          |     |                                                  | 1.5          | V    |

| ų                   | Input current at maximu input voltage                   | m              | V <sub>I</sub> = 5.5 V                                                                |                                                 |     |                                                  | 1            | mA   |

| ΉΗ                  | High-level input current                                | Any A<br>Any E | V <sub>I</sub> = 2.4 V                                                                |                                                 |     |                                                  | 40<br>80     | μА   |

| ΉL                  | Low-level input current                                 | Any A          | V <sub>I</sub> = 0.4 V                                                                |                                                 |     | - 1<br>- 2                                       | -1.6<br>-3.2 | mA   |

| ICC1(H)             | Supply current from Vo                                  | C1,            | V <sub>CC1</sub> = 5.25 V, V <sub>CC2</sub> = 24 V,                                   | V <sub>CC2</sub> = 24 V,                        |     | 2                                                | 4            | mA   |

| ICC2(H)             | Supply current from V <sub>C</sub><br>both outputs high | C2,            | All inputs at 0 V,                                                                    | No load                                         |     |                                                  | 0.5          | mA   |

| ICC1(L)             | Supply current from V <sub>C</sub><br>both outputs low  | C1,            | V <sub>CC1</sub> = 5.25 V,                                                            | V <sub>CC2</sub> = 24 V,                        |     | 16                                               | 24           | mA   |

| ICC2(L)             | Supply current from V <sub>C</sub> both outputs low     | C2,            | All inputs at 5 V,                                                                    | No load                                         |     | 7                                                | 13           | mA   |

| I <sub>CC2(S)</sub> | Supply current from V <sub>C</sub> standby condition    | C2,            | VCC1 = 0,<br>All inputs at 5 V,                                                       | V <sub>CC2</sub> = 24 V,<br>No load             |     |                                                  | 0.5          | mA   |

$<sup>^{\</sup>dagger}$  All typical values are at VCC1 = 5 V, VCC2 = 20 V, and TA = 25 °C.

# switching characteristics, $V_{CC1} = 5 \text{ V}$ , $V_{CC2} = 20 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$

| PARAMETER                                                  | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------|---------------------|-----|-----|-----|------|

| tDLH Delay time, low-to-high-level output                  |                     |     | 20  | 35  | ns   |

| tDHL Delay time, high-to-low-level output                  | $C_1 = 390 pF$      |     | 10  | 20  | ns   |

| t <sub>TLH</sub> Transition time, low-to-high-level output | $R_D = 10 \Omega$ , |     | 20  | 30  | ns   |

| t <sub>THL</sub> Transition time, high-to-low-level output | See Figure 1        |     | 20  | 30  | ns   |

| tpLH Propagation delay time, low-to-high-level output      | See Figure 1        | 10  | 40  | 65  | กร   |

| tpHL Propagation delay time, high-to-low-level output      |                     | 10  | 30  | 50  | ns   |

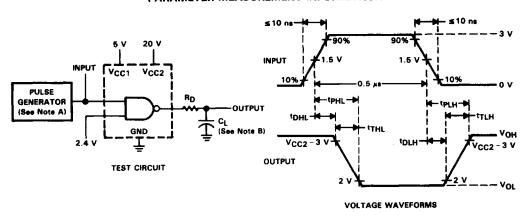

# PARAMETER MEASUREMENT INFORMATION

NOTES: A. The pulse generator has the following characteristics: PRR = 1 MHz,  $Z_{out}$  = 50  $\Omega$ .

B. CL includes probe and jig capacitance.

FIGURE 1. SWITCHING TIMES, EACH DRIVER

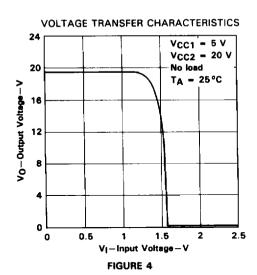

#### TYPICAL CHARACTERISTICS LOW-LEVEL OUTPUT VOLTAGE HIGH-LEVEL OUTPUT VOLTAGE **OUTPUT CURRENT OUTPUT CURRENT** 0.5 V<sub>C</sub>C<sub>2</sub> V<sub>CC1</sub> = 5 V VCC1 - 5 V VCC2 - 20 V VCC2 - 20 V VOH -- High-Level Output Voltage -- V VOL -- Low-Level Output Voltage -- V VCC2 - 0.5 V1 - 2 V 0.4 TA - 70°C VCC2-1.0 25°C 0.3 VCC2-1.5 0.2 VCC2-2.0 - 0°C 0.1 VCC2-2.5 0 V<sub>CC2</sub> - 3.0 - 10 0 20 60 80 100 -0.01-0.1 - 100 40 IOH-High-Level Output Current-mA IOL-Low-Level Output Current-mA FIGURE 2 FIGURE 3

# TYPICAL CHARACTERISTICS

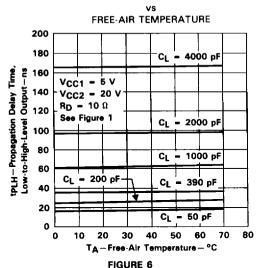

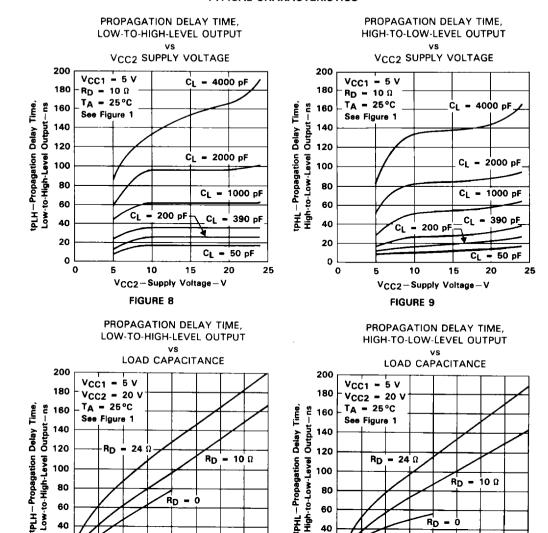

PROPAGATION DELAY TIME, LOW-TO-HIGH-LEVEL OUTPUT

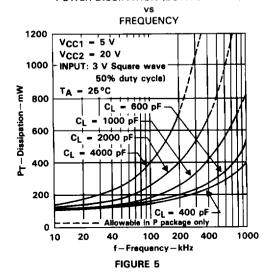

POWER DISSIPATION (BOTH DRIVERS)

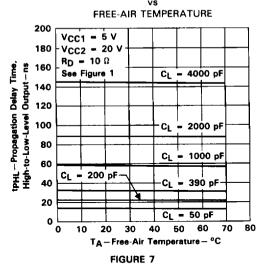

PROPAGATION DELAY TIME, HIGH-TO-LOW-LEVEL OUTPUT

#### TYPICAL CHARACTERISTICS

NOTE: For  $R_D = 0$ , operation with  $C_L > 2000$  pF violates absolute maximum current rating.

3000

4000

2000

CL-Load Capacitance-pF

FIGURE 10

20

٥

0

1000

RD = 0

4000

2000

CL - Load Capacitance - pF

FIGURE 11

60

40 20

0

0

1000

#### APPLICATIONS INFORMATION

#### driving power MOSFETs

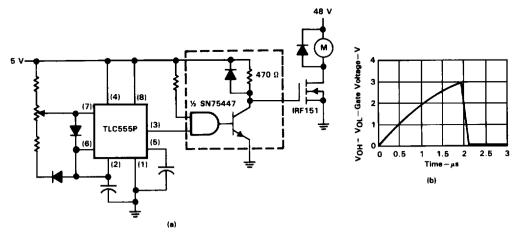

The drive requirements of power MOSFETs are much lower than comparable bipolar power transistors. The input impedance of a FET consists of a reverse biased PN junction that can be described as a large capacitance in parallel with a very high resistance. For this reason, the commonly used open-collector driver with a pull-up resistor is not satisfactory for high-speed applications. In Figure 12(a), an IRF151 power MOSFET switching an inductive load is driven by an open-collector transistor driver with a 470- $\Omega$  pull-up resistor. The input capacitance ( $C_{\rm iss}$ ) specification for an IRF151 is 4000 pF maximum. The resulting long turn-on time due to the combination of  $C_{\rm iss}$  and the pull-up resistor is shown in Figure 12(b).

FIGURE 12. POWER MOSFET DRIVE USING SN75447

# **APPLICATIONS INFORMATION**

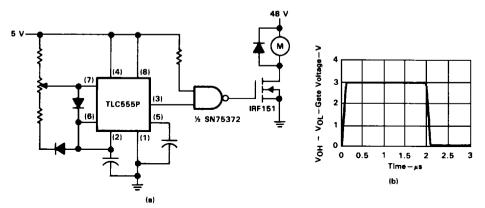

A faster, more efficient drive circuit uses an active pull-up as well as an active pull-down output configuration, referred to as a totem-pole output. The SN75372 driver provides the high speed, totem-pole drive desired in an application of this type, see Figure 13(a). The resulting faster switching speeds are shown in Figure 13(b).

FIGURE 13. POWER MOSFET DRIVE USING SN75372

Power MOSFET drivers must be capable of supplying high peak currents to achieve fast switching speeds as shown by the equation

$$I_{pk} = \frac{VC}{t_r}$$

where C is the capacitive load, and  $t_r$  is the desired rise time. V is the voltage that the capacitance is charged to. In the circuit shown in Figure 13(a), V is found by the equation

$$V = V_{OH} - V_{OL}$$

Peak current required to maintain a rise time of 100 ns in the circuit of Figure 13(a) is

$$I_{PK} = \frac{(3-0)4(10-9)}{100(10-9)} = 120 \text{ mA}$$

Circuit capacitance can be ignored because it is very small compared to the input capacitance of the IRF151. With a  $V_{CC}$  of 5 V, and assuming worst-cast conditions, the gate drive voltage is 3 V.

For applications in which the full voltage of V<sub>CC2</sub> must be supplied to the MOSFET gate, the SN75374 QUAD MOSFET driver should be used.

# THERMAL INFORMATION

#### power dissipation precautions

Significant power may be dissipated in the SN75372 driver when charging and discharging high-capacitance loads over a wide voltage range at high frequencies. Figure 5 shows the power dissipated in a typical SN75372 as a function of load capacitance and frequency. Average power dissipated by this driver is derived from the equation

$$PT(AV) = PDC(AV) + PC(AV) + PS(AV)$$

where  $P_{DC(AV)}$  is the steady-state power dissipation with the output high or low,  $P_{C(AV)}$  is the power level during charging or discharging of the load capacitance, and  $P_{S(AV)}$  is the power dissipation during switching between the low and high levels. None of these include energy transferred to the load and all are averaged over a full cycle.

The power components per driver channel are

$$P_{DC(AV)} = \frac{P_{H}t_{H} + P_{L}t_{L}}{T}$$

$$P_{C(AV)} \approx C V_{C}^{2} f$$

$$P_{S(AV)} = \frac{P_{L}H^{t}L_{H} + P_{L}t_{H}L_{L}}{T}$$

where the times are as defined in Figure 14.

$P_L$ ,  $P_H$ ,  $P_{LH}$ , and  $P_{HL}$  are the respective instantaneous levels of power dissipation, C is the load capacitance.  $V_C$  is the voltage across the load capacitance during the charge cycle shown by the equation

FIGURE 14. OUTPUT VOLTAGE WAVEFORM

$$V_C = V_{OH} - V_{OL}$$

PS(AV) may be ignored for power calculations at low frequencies.

# THERMAL INFORMATION

In the following power calculation, both channels are operating under identical conditions:  $V_{OH}$  = 19.2 V and  $V_{OL}$  = 0.15 V with  $V_{CC1}$  = 5 V,  $V_{CC2}$  = 20 V,  $V_{C}$  = 19.05 V, C = 1000 pF, and the duty cycle = 60%. At 0.5 MHz,  $P_{S(AV)}$  is negligible and can be ignored. When the output voltage is high, ICC2 is negligible and can be ignored.

On a per-channel basis using data sheet values

$$P_{DC(AV)} = \left[ (5 \text{ V}) \left( \frac{2 \text{ mA}}{2} \right) + (20 \text{ V}) \left( \frac{0 \text{ mA}}{2} \right) \right] (0.6) + \left[ (5 \text{ V}) \left( \frac{16 \text{ mA}}{2} \right) + (20 \text{ V}) \left( \frac{7 \text{ mA}}{2} \right) \right] (0.4)$$

PDC(AV = 47 mW per channel

Power during the charging time of the load capacitance is

$$PC(AV) = (1000 pF) (19.05 V)^2 (0.5 MHz) = 182 mW per channel$$

Total power for each driver is

$$PT(AV) = 47 \text{ mW} + 182 \text{ mW} = 229 \text{ mW}$$

and total package power is

PT(AV) = (229)(2) = 458 mW.