# MOTOROLA SEMICONDUCTOR! TECHNICAL DATA

# Advance Information

# **Geometry Correction Waveform Generator**

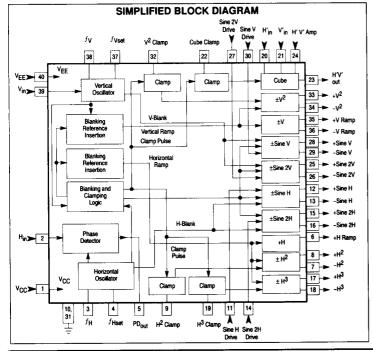

The MC1388 is a bipolar integrated circuit designed to be used with the control circuitry for geometry correction in monitors and HDTV receivers. The function of the integrated circuit is to generate the required voltage waveforms that will be applied to the control circuitry. The control circuitry will apply them in the proper amplitude and combination for use in modulating the horizontal and vertical scan currents.

#### Features

- Multistandard Operation Capable (10 kHz  $\leq f_H \leq$  63 kHz)(45  $\leq f_V \leq$  120 Hz)

- Constant Amplitude Outputs, Independent of Frequency

- Complementary Output Waveforms (Horizontal Parabola, Horizontal Cubic, Vertical Ramp, Vertical Parabola and Sine Functions)

- Three Input Multiplier

- Minimum of External Components Necessary

- Standard Supplies (±5 Vdc)

#### Functions (Ten Waveforms):

- Horizontal Ramp and Vertical Ramp

- Horizontal Parabola and Vertical Parabola

- Horizontal Cube and Cube with Accessible Inputs (H'in, V'in)

- ± Sine H

- ± Sine 2 H

- ± Sine V

- ± Sine 2 V

# MC1388

# WAVEFORM GENERATOR IC FOR MONITOR APPLICATIONS

## **ORDERING INFORMATION**

| Device  | Temperature<br>Range | Package     |

|---------|----------------------|-------------|

| MC1388P | 0° to +70°C          | Plastic DIP |

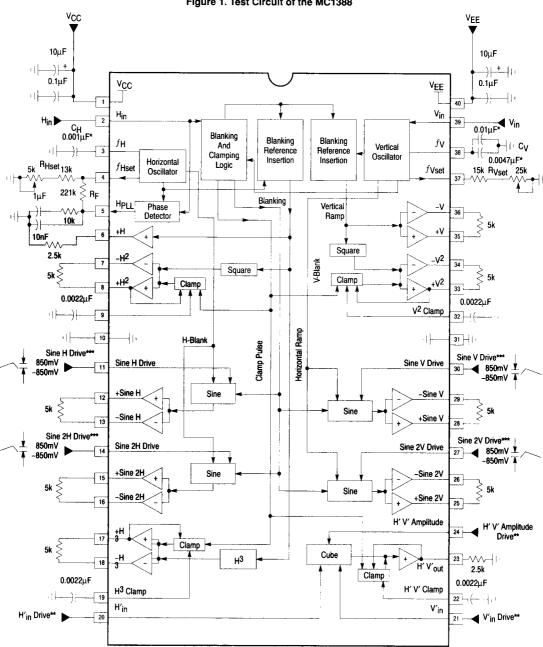

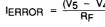

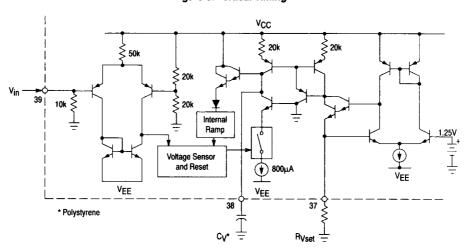

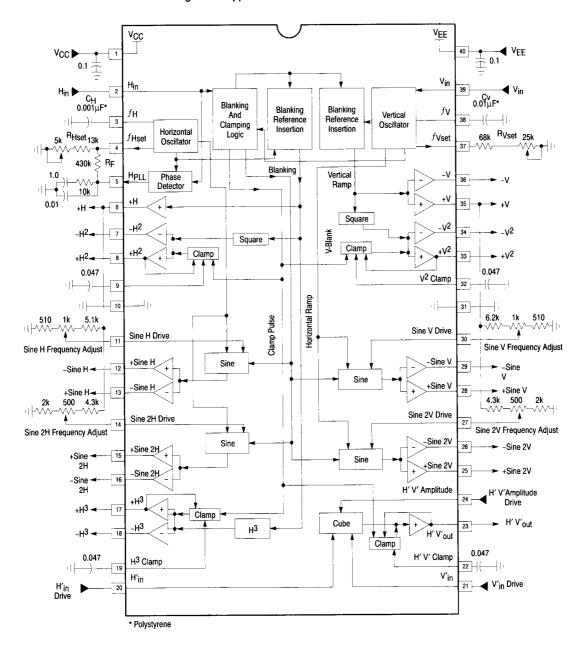

Figure 1. Test Circuit of the MC1388

Polystyrene

The three input multiplier was tested by applying a DC voltage to two of the inputs while applying a 1.25 Vp-p ramp input to the third.

The inputs applied to the Sine Drive Inputs is a voltage ramped from -850 mV to +850 mV in 10 mV steps.

# MAXIMUM OPERATING CONDITIONS

| Rating                              | Symbol                                                                                          | Value                                        | Unit |

|-------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------|------|

| Power Supply Voltage                | V <sub>CC</sub><br>V <sub>EE</sub>                                                              | +6.0<br>-6.0                                 | Vdc  |

| Input Voltage<br>Maximum<br>Minimum | V <sub>in</sub> , H <sub>in</sub> , H' <sub>in</sub> ,<br>V' <sub>in</sub> , H' V'<br>Amplitude | V <sub>CC</sub> +0.5<br>V <sub>EE</sub> -0.5 | Vdc  |

| Storage Temperature                 | T <sub>stg</sub>                                                                                | -65 to +150                                  | °C   |

| Junction Temperature                | TJ                                                                                              | +150                                         | °C   |

## RECOMMENDED OPERATING CONDITIONS

| Characteristics                                                                                                                                                                         | Pins(s)                                                                         | Symbol                                                                     | Value                                                                               | Unit              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------|

| Power Supply Voltage                                                                                                                                                                    | 1<br>40                                                                         | V <sub>CC</sub><br>VEE                                                     | +4.5 to +5.5<br>-5.5 to -4.5                                                        | Vdc               |

| Horizontal Sync Frequency (see Figure 8) Maximum Minimum Pulse Width: Maximum Minimum Pulse Amplitude: Maximum Voltage (Tip) Minimum Voltage (Baseline) Minimum Threshold: Tip Baseline | 2                                                                               | H <sub>in</sub>                                                            | 63<br>10<br><1.0/(2.0fH)<br>2.0<br>VCC<br>VEE +0.5<br>VCC/2.0 +0.2<br>VCC/2.0 +0.2  | k Hz<br>μs<br>Vdc |

| Vertical Sync Frequency (see Figure 8) Maximum Minimum Pulse Width: Maximum Minimum Pulse Amplitude: Maximum Voltage (Tip) Minimum Voltage (Baseline) Minimum Threshold: Tip Baseline   | 39                                                                              | Vin                                                                        | 120<br>45<br><1.0/(2.0fy)<br>2.0<br>VCC<br>VEE +0.5<br>VCC/2.0 +0.2<br>VCC/2.0 +0.2 | Hz<br>μs<br>Vdc   |

| Sine H Drive<br>Sine 2H Drive<br>Sine V Drive<br>Sine 2V Drive                                                                                                                          | 11<br>14<br>30<br>27                                                            | Sine H Drive<br>Sine 2H Drive<br>Sine V Drive<br>Sine 2V Drive             | -0.85 to +0.85                                                                      | Vdc               |

| H′ <sub>in</sub><br>V′in<br>H′ <sub>in</sub> V′ <sub>in</sub> Amplitude                                                                                                                 | 20<br>21<br>24                                                                  | H' <sub>in</sub><br>V'in<br>H' <sub>in</sub> V' <sub>in</sub><br>Amplitude | -1.25 to +1.25                                                                      | Vdc               |

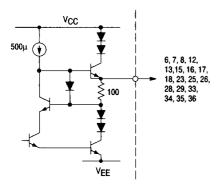

| Peak Load Current                                                                                                                                                                       | 6, 7, 8, 12,<br>13, 15, 16<br>17, 18, 23,<br>25, 26, 28<br>29, 33, 34<br>35, 36 | IL.                                                                        | 5.0                                                                                 | mA                |

| Ambient Temperature                                                                                                                                                                     |                                                                                 | TA                                                                         | 0 to +70                                                                            | °C                |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = +5.0 \text{ V}$ ,  $V_{EE} = -5.0 \text{ V}$ ,  $R_L = 2.5 \text{ k}\Omega$ ,  $T_A = 25^{\circ}\text{C}$ ,  $f_H = 31,250 \text{ Hz}$ ,  $f_V = 1562.5 \text{ Hz}$ , see Figure 1, unless otherwise noted.)

| Characteristics                                                                                            | Pin(s)                                                                          | Symbol                                                  | Min          | Тур       | Max        | Unit        |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------|--------------|-----------|------------|-------------|

| Supply Current $V_{CC} = +5.0 \text{ Vdc}$<br>$V_{EE} = -5.0 \text{ Vdc}$                                  | 1<br>40                                                                         | ICC<br>IEE                                              | 29<br>–50    | 33<br>-42 | 41<br>-38  | mA          |

| Output DC Offset, (All outputs when blanked)                                                               | 6, 7, 8, 12,<br>13, 15, 16<br>17, 18, 23,<br>25, 26, 28<br>29, 33, 34<br>35, 36 |                                                         | -100         | ±8        | 100        | mV          |

| Pull-In Range<br>Hold In Range<br>( $C_H = 1.0$ nF, $R_F = 221$ k $\Omega$ , $H_{PLL}$ filter shown)       | 5                                                                               | H <sub>PLL</sub>                                        | ±1.5<br>±1.5 | <br>±4.5  | _          | kHz         |

| Horizontal Ramp — Amplitude — Non-Symmetry                                                                 | 6                                                                               | +H                                                      | 4.4          | 5.0       | 5.3<br>2.0 | Vp-p<br>%   |

| Horizontal Parabola — Amplitude — Non-Symmetry                                                             | 7,8                                                                             | ±H2                                                     | 2.2<br>—     | 2.6<br>—  | 3.1<br>12  | Vp-p<br>%   |

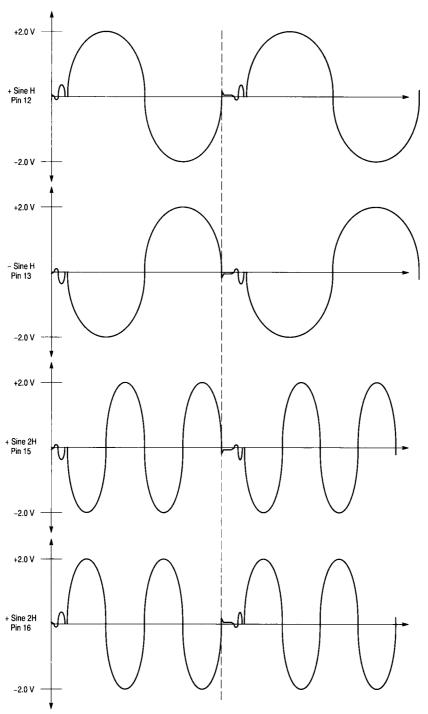

| ±Sine H — Amplitude (No DC Offset Input)  — Zero Crossing Phase Error  (Pin 11 Drive as shown in Figure 1) | 12, 13                                                                          | ±Sine H                                                 | 2.8<br>—     | 4.0       | 5.6<br>25  | Vp-p<br>Deg |

| ±Sine 2H — Amplitude (No DC Offset Input) — Zero Crossing Phase Error (Pin 14 Drive as shown in Figure 1)  | 15, 16                                                                          | ±Sine 2H                                                | 2.8          | 4.0<br>—  | 5.6<br>25  | Vp-p<br>Deg |

| Horizontal Cubic — Amplitude<br>— Non-Symmetry                                                             | 17, 18                                                                          | ±Н3                                                     | 4.1<br>—     | 5.0       | 5.9<br>12  | Vp-p<br>%   |

| ±Sine 2V — Amplitude (No DC Offset Input) — Zero Crossing Phase Error (Pin 27 Drive as shown in Figure 1)  | 25, 26                                                                          | ±Sine 2V                                                | 2.8<br>—     | 4.0<br>—  | 5.6<br>25  | Vp-p<br>Deg |

| ±Sine V — Amplitude (No DC Offset Input) — Zero Crossing Phase Error (Pin 30 Drive as shown in Figure 1)   | 28, 29                                                                          | ±Sine V                                                 | 2.8          | 4.0<br>—  | 5.6<br>25  | Vp-p<br>Deg |

| Vertical Parabola — Amplitude<br>— Non-Symmetry                                                            | 33, 34                                                                          | ±V2                                                     | 2.2          | 2.5<br>   | 3.1<br>12  | Vp-p<br>%   |

| Vertical Ramp — Amplitude — Non-Linearity                                                                  | 35, 36                                                                          | ±V                                                      | 4.4          | 5.0<br>—  | 5.3<br>2.0 | Vp-p<br>%   |

| H' V' <sub>out</sub> — Amplitude<br>— Non-Linearity                                                        | 23                                                                              | H' V'out                                                | 4.2<br>—     | 4.8<br>—  | 5.4<br>12  | Vp-p<br>%   |

| H'in V'in H' V' — Amplitude<br>— Multiplication Factor                                                     | 20, 21, 24                                                                      | H' <sub>in</sub> V' <sub>in</sub><br>H' V'<br>Amplitude | _            | 1.0       | _          | V/V         |

| Pin | Symbol | Internal Equivalent<br>Circuit          | Description                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc    |                                         | Positive Rail Voltage. Requires 33 mA at +4.5 < Vdc < +5.5                                                                                                                                                                                                           |

| 2   | Hin    | 25k 25k 25k 25k VEE                     | Positive Horizontal Flyback input. Input impedance is nominally 10 kΩ. Threshold is at V <sub>CC</sub> /2. See Figure 2.                                                                                                                                             |

| 3   | fн     | CH LIMA VEE                             | Horizontal Oscillator Capacitor (C <sub>H</sub> ). The charge and discharge rate of the capacitor voltage determines the horizontal frequency. Charging current set predominantly by R <sub>Hset</sub> (Pin 4).                                                      |

| 4   | fHset  | VCC<br>10µA                             | Horizontal Charge Current Set. An internally regulated 1.25 Vdc, and the external resistance (R <sub>Hset</sub> ) at this pin determines the horizontal free run charging current. Also, the feedback current from the Hp <sub>LL</sub> filter is input at this pin. |

| 5   | Нрц    | 10n + 10k + 600 + 600 Filter + 2.2V VEE | Horizontal Phase Detector output pin. An external filter circuit between this pin and Pin 5 determines the selectivity of the phase detector and provides the feedback path for the horizontal phase locked loop.                                                    |

<sup>\*</sup> All pins except (V $_{CC}$  and V $_{EE}$ ) have ESD diodes between V $_{CC}$  and V $_{EE}$ .

| Positive horizontal ramp.  Horizontal Parabola Clamping pin. An external capacit works to cancel DC offset. Typically coupled to ground with a 0.047 μF capacitor.  Ground Connection.  Sine H Drive  VCC  Sine H Drive. A ramp waveform input here will produce sine wave output (at Pins 12 and 13) with frequency varying with input ramp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ.  12 +Sine H  (See Pin 6)  +Sine H output. The sine wave output developed from the input at Pin 11.  -Sine H output. A 180° phase shifted version of +Sine H.  Sine 2H  Drive  Positive horizontal ramp.  Horizontal Parabola Clamping pin. An external capacit works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically coupled to ground works to cancel DC offset. Typically capacity.  Sine H Drive. A ramp waveform input here will produce a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying w ramp DC offset. Typically coupled to ground works to cancel DC offset. Typically capacity.                                                                                                                                                                                                                                                                                                                              | Pin | Symbol               | Internal Equivalent<br>Circuit              | Description                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Horizontal Parabola output. The squared result of the positive horizontal ramp.  Horizontal Parabola Clamping pin. An external capacit works to cancel DC offset. Typically coupled to ground with a 0.047 µF capacitor.  Ground Connection.  Sine H Drive. A ramp waveform input here will produce sine wave output (at Pins 12 and 13) with frequency varying with input ramp amplitude, and phase varying with ramp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ.  Here I (See Pin 6)  Sine H output. The sine wave output developed from the input at Pins 12 and 13).  Sine H output. A 180° phase shifted version of +Sine H.  Sine 2H Drive. A ramp waveform input here will produce sine wave output developed from the input at Pins 15 and 16) with frequency varying with input arm parabilitude and phase varying warm pDC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6   | +H                   | 50µA () () () () () () () () () () () () () | Horizontal Ramp output.                                                                                                                                                                                                                         |

| Positive horizontal ramp.  Horizontal Parabola Clamping pin. An external capacit works to cancel DC offset. Typically coupled to ground with a 0.047 μF capacitor.  Ground Connection.  Sine H Drive  VCC  Sine H Drive. A ramp waveform input here will produce sine wave output (at Pins 12 and 13) with frequency varying with input ramp amplitude, and phase varying with ramp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ.  +Sine H output. The sine wave output developed from the input at Pin 11.  -Sine H output. A 180° phase shifted version of +Sine H.  Sine 2H Drive  Sine 2H Drive. A ramp waveform input here will produce is no manually greater than 1.0 MΩ.  **Sine H output. The sine wave output developed from the input at Pin 11.  -Sine H output. A 180° phase shifted version of +Sine H.  Sine 2H Drive. A ramp waveform input here will produce a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying warmp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7   | _H2                  | (See Pin 6)                                 | Complement Horizontal Parabola output.                                                                                                                                                                                                          |

| works to cancel DC offset. Typically coupled to ground with a 0.047 μF capacitor.  10 Gnd  11 Sine H Drive  VCC  Sine H Drive. A ramp waveform input here will produce sine wave output (at Pins 12 and 13) with frequency varying with input ramp amplitude, and phase varying with framp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ.  12 +Sine H  (See Pin 6)  +Sine H output. The sine wave output developed from the input at Pin 11.  Sine BH output. A 180° phase shifted version of +Sine H.  Sine 2H Drive. A ramp waveform input here will produce as ine wave output the pin put at Pin 11.  Sine BH output. A 180° phase shifted version of +Sine H.  Sine 2H Drive. A ramp waveform input here will produce as ine wave output the Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying wramp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8   | +H2                  |                                             | Horizontal Parabola output. The squared result of the positive horizontal ramp.                                                                                                                                                                 |

| Sine H Drive  Sine H Drive  Sine H Drive. A ramp waveform input here will product sine wave output (at Pins 12 and 13) with frequency varying with input ramp amplitude, and phase varying with ramp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ  +Sine H  (See Pin 6)  +Sine H output. The sine wave output developed from the input at Pin 11.  -Sine H output. A 180° phase shifted version of +Sine H.  Sine 2H  Drive  Sine 2H Drive. A ramp waveform input here will product a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying warmp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ  +Sine 2H output. The sine wave output developed from the input at Pin 11.  Sine 2H Drive. A ramp waveform input here will product a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying warmp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ  +Sine 2H output. The sine wave output developed from the input at Pin 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9   | H <sup>2</sup> clamp | 0.047 1k 20k                                | Horizontal Parabola Clamping pin. An external capacitor works to cancel DC offset. Typically coupled to ground with a 0.047 μF capacitor.                                                                                                       |

| Sine wave output (at Pins 12 and 13) with frequency varying with input ramp amplitude, and phase varying with ramp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ.  12 +Sine H (See Pin 6)  +Sine H output. The sine wave output developed from the input at Pin 11.  -Sine H output. A 180° phase shifted version of +Sine H.  Sine 2H Drive. A ramp waveform input here will produ a sine wave output (at Pins 12 and 13) with frequency varying with input ramp amplitude and phase varying w ramp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.  15 +Sine 2H (See Pin 6)  +Sine 2H output. The sine wave output developed from the input arm pamplitude and phase varying w ramp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10  | Gnd                  |                                             | Ground Connection.                                                                                                                                                                                                                              |

| the input at Pin 11.    Sine H   Sine 2H   Drive   Sine 2H   Drive   Sine 2H   Drive   Sine 2H   Sine 2H | 11  |                      | 0.5pF<br>11 0√5k<br>⊕ 63µA                  | varying with input ramp amplitude, and phase varying with ramp DC offset. Dynamic input impedance is                                                                                                                                            |

| +Sine H.  Sine 2H Drive  Sine 2H Drive. A ramp waveform input here will produ a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying w ramp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.  +Sine 2H  (See Pin 6)  +Sine 2H output. The sine wave output developed from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12  | +Sine H              | (See Pin 6)                                 | +Sine H output. The sine wave output developed from the input at Pin 11.                                                                                                                                                                        |

| Drive a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying w ramp DC offset. Dynamic input impedance is nominall greater than 1.0 MΩ.  15 +Sine 2H (See Pin 6) +Sine 2H output. The sine wave output developed from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13  | -Sine H              |                                             |                                                                                                                                                                                                                                                 |

| (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14  | 1 1                  | (See Pin 11)                                | Sine 2H Drive. A ramp waveform input here will produce a sine wave output (at Pins 15 and 16) with frequency varying with input ramp amplitude and phase varying with ramp DC offset. Dynamic input impedance is nominally greater than 1.0 MΩ. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15  | +Sine 2H             | (See Pin 6)                                 | +Sine 2H output. The sine wave output developed from the input at Pin 14.                                                                                                                                                                       |

| Pin | Symbol               | Internal Equivalent<br>Circuit | Description                                                                                                                                                                                                                                      |

|-----|----------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | -Sine 2H             | (See Pin 6)                    | -Sine 2H output. A 180° phase shifted version of +Sine 2H.                                                                                                                                                                                       |

| 17  | +H3                  |                                | Horizontal Cubic output.                                                                                                                                                                                                                         |

| 18  | _H3                  |                                | Complement Horizontal Cubic output.                                                                                                                                                                                                              |

| 19  | H <sup>3</sup> clamp | (See Pin 9)                    | Cubic Clamping pin. An external capacitor works to cancel DC offset. Typically coupled to ground with a 0.047 µF capacitor.                                                                                                                      |

| 20  | H'in                 | 20 20k 20k 20k 20k VEE         | H' Input. Dynamic input impedance in excess of 1.0 M $\Omega$ . Valid input voltage range is between VEE and VCC.                                                                                                                                |

| 21  | V'in                 | (See Pin 20)                   | $V'$ Input. Dynamic input impedance in excess of 1.0 $M\Omega_{\cdot}$ Valid input voltage range is between VEE and VCC.                                                                                                                         |

| 22  | H' V'<br>Clamp       | (See Pin 9)                    | $H'_{in}$ , $V'_{in}$ and $H'$ $V'$ Amplitude Product Clamping pin. An external capacitor works to cancel DC offset. Typically coupled to ground with a 0.047 $\mu F$ capacitor.                                                                 |

| 23  | H' V' out            | (See Pin 6)                    | H' V' Output Pin. The product of $H'_{in}$ , $V'_{in}$ , $H'$ V' amplitude must be less than 1.9 Vp-p.                                                                                                                                           |

| 24  | H' V'<br>Amplitude   | (See Pin 20)                   | $H'$ V' Amplitude. Dynamic input impedance in excess of 1.0 $M\Omega_{\cdot}$ Valid input voltage range is between VEE and VCC.                                                                                                                  |

| 25  | +Sine 2V             | (See Pin 6)                    | +Sine 2V output. The sine wave output developed from the input at Pin 27.                                                                                                                                                                        |

| 26  | -Sine 2V             |                                | -Sine 2V output. A 180° phase shifted version of +Sine 2V.                                                                                                                                                                                       |

| 27  | Sine 2V<br>Drive     | (See Pin 11)                   | Sine 2V Drive. A ramp waveform input here will produce a sine wave output (at Pins 25 and 26) with frequency varying with input ramp amplitude, and phase varying with ramp DC offset. Input impedance is nominally greater than 1.0 $M\Omega$ . |

| 28  | +Sine V              | (See Pin 6)                    | +Sine V output. The sine wave output developed from the input at Pin 30.                                                                                                                                                                         |

| 29  | -Sine V              |                                | -Sine V output. A 180° phase shifted version of +Sine V.                                                                                                                                                                                         |

| 30  | Sine V<br>Drive      | (See Pin 11)                   | Sine V Drive. A ramp waveform input here will produce a sine wave output (at Pins 28 and 29) with frequency varying with input ramp amplitude, and phase varying with ramp DC offset. Input impedance is nominally greater than 1.0 $M\Omega$ .  |

| Pin | Symbol               | Internal Equivalent<br>Circuit        | Description                                                                                                                                                                                                          |

|-----|----------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | Gnd                  |                                       | Ground connection.                                                                                                                                                                                                   |

| 32  | V <sup>2</sup> clamp | (See Pin 9)                           | Vertical Parabola Clamp pin. An external capacitor works to cancel DC offset. Typically coupled to ground with a 0.047 $\mu F$ capacitor.                                                                            |

| 33  | +V2                  | (See Pin 6)                           | Vertical Parabola.                                                                                                                                                                                                   |

| 34  | _V2                  |                                       | Complement Vertical Parabola.                                                                                                                                                                                        |

| 35  | +V                   |                                       | Vertical Ramp.                                                                                                                                                                                                       |

| 36  | -V                   |                                       | Complement Vertical Ramp.                                                                                                                                                                                            |

| 37  | fVset                | 37 N <sub>Vset</sub> Σ 10μΑ ψ Σ 1.25V | Vertical Charge Current Set. An internally regulated 1.25 Vdc, and the external resistance (R <sub>Vset</sub> ) at this pin determines the charging current for the capacitor, C <sub>V</sub> , connected to Pin 38. |

| 38  | fy                   | VCC                                   | Vertical Ramp Generator Capacitor (C <sub>V</sub> ). The charge and discharge rate of the capacitor at this pin determines the vertical ramp rate.                                                                   |

| 39  | Vin                  | 39 - 20k 20k 20k VEE                  | Positive Vertical Flyback input pin. Presents 10 kΩ to input waveform. (See Figure 3). Threshold is at V <sub>CC</sub> /2.                                                                                           |

| 40  | VEE                  |                                       | Negative Supply pin. Requires 43 mA at -5.5 < Vdc < -4.5.                                                                                                                                                            |

#### **FUNCTIONAL DESCRIPTION**

#### Introduction

The MC1388 is a multi-frequency capable integrated circuit used for geometry correction in monitors and HDTV receivers. With a few inputs the MC1388 will provide ten functions, eight with complements, as output waveforms. These waveforms can then be used by the control circuitry in any combination to modulate the horizontal and vertical deflection currents for geometry correction.

The MC1388 accomplishes multi-frequency operation by allowing external components to determine the nominal frequency of operation. This is done by choosing resistor-capacitor pairs for the desired horizontal and vertical oscillator frequencies. The horizontal and vertical sync inputs then provide the timing reference to which the output waveforms of the MC1388 adhere.

## **Horizontal Timing**

To ensure proper horizontal timing, the MC1388 uses a phase-locked-loop to provide a reliable time base. The loop is externally accessible at the current controlled oscillator (ICO), Pins 3, 4, and at the output of the phase detector, Pin 5. Figure 2 shows relevant internal circuitry and pin connections. This allows the system designer to tailor the timing and performance of the MC1388.

The ICO is an RC type in which the horizontal frequency is determined by the charge and discharge rate of the capacitor at Pin 3. During charging, the voltage on the capacitor (CH) is increased until it reaches an internally determined trip level. At this trip level the direction of the current at Pin 3 is reversed and the discharge process begins. During discharge, circuitry diverts the current available at Pin 3 internally and the capacitor discharges quickly to the bottom trip level where control circuitry switches the direction of Pin 3 current and the cycle begins again.

The charging current at Pin 3 is determined by the current out of Pin 4, which is mirrored at Pin 3. The current out of Pin 4 is set by a nominal 1.25 V stable reference and the external resistance at this node (RHset). This also provides a means of modulating the charging current at Pin 3 by injecting the error current from the phase detector (Pin 5).

At Pin 5(Hpi I ) are the filter components of the horizontal phase-locked-loop. These components were chosen to ensure fast tracking over the possible horizontal operating frequencies and a capture range equal to the lock range over these operating frequencies. (Refer to application notes AN553 and AN535 for information regarding design of the filter). The feedback resistor RF, and the frequency setting capacitor CH, are also components of the the horizontal phase-locked-loop. RF serves two purposes, it provides the feedback path for the error current to Pin 4, and is a factor in the phase detector sensitivity which sets the amount of feedback. CH influences the characteristics of the loop by being a factor in the oscillator sensitivity.

The error current from the phase detector is determined by the static phase error between the free running frequency and the frequency of the horizontal input at Pin 2, and the value of feedback resistance (RF) between Pins 4 and 5. The output of the phase detector. Pin 5, will develop a voltage as a result of the phase detector error current acting on the HPLI filter. This voltage difference will appear between Pins 5 and 4 and produce the error current provided to the horizontal oscillator. This error current is:

$$I_{ERROR} = \frac{(V_5 - V_4)}{R_F}$$

Figure 2. Horizontal Timing

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

The average voltage difference (V $_5$  – V $_4$ ) is capable of approximately  $\pm 2.5$  V. The changing current is then defined by:

$$I_3 = I_4 = \frac{1.25 \text{ V}}{R_{\text{Hset}}} - I_{\text{ERROR}}$$

#### **Vertical Timing**

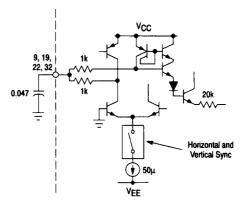

Vertical timing for the MC1388 is determined by the frequency of the input at Pin 39 and the charging rate of the capacitor at Pin 38. Representative circuitry for relevant pins is shown in Figure 3. The vertical timing is set by an injection oscillator, with the frequency of the generated ramp being determined by the current drawn out of Pin 37. That current is also set with a stable 1.25 Vdc reference and the resistance (R<sub>Vset</sub>) at this pin. At the beginning of a vertical cycle, the current sourced by Pin 37 is mirrored out of Pin 38 charging the capacitor at Pin 38 with a constant current resulting in a linear ramp. The charging current of the capacitor (C<sub>V</sub>) must be set so the +V output (Pin 35) reaches 2.5 V just before the next vertical sync pulse arrives to trigger the discharge of the capacitor. The current sourced by Pin 37 is then again provided to the capacitor and the cycle repeats.

#### **WAVEFORMS**

#### Sine Waveforms

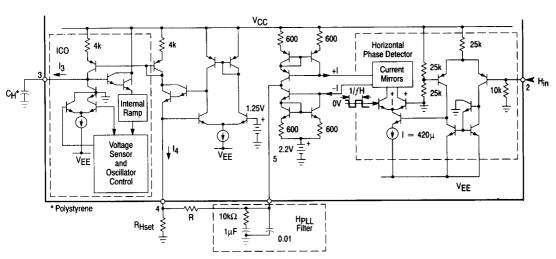

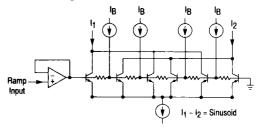

The MC1388 has on board circuitry which is capable of producing sine wave like waveforms. Relevant circuitry is shown in Figure 4. A total of four subcircuits are available and each has a 0° and 180° phase shifted output. The sine wave generators require a ramp input which can be provided by the horizontal and vertical ramp outputs of the MC1388.

By modifying the input ramp, the output sine wave can be tailored to meet particular requirements for geometry correction. Figure 5 illustrates an example of geometry errors and the waveforms needed to correct the top to bottom geometry errors. The ramp amplitude affects the number of sine wave cycles and the ramp offset affects the phase. By doubling the peak-to-peak amplitude of an input ramp which created one complete period, a sine wave of two complete periods is produced. By adding DC offset to the input ramp, phase advance or delay is produced. Input ramps to the sine wave generators, which should be DC coupled to provide bias current, are presented to transistor bases with high dynamic impedances in excess of 1.0 M $\Omega$ . A means of applying an adjustable ramp is shown in the application section.

Figure 4. Sine Wave Generator

Figure 5. Sine Wave Adjustments

Figure 3. Vertical Timing

## Three Input Multiplier (H'in, V'in and H' V' Amplitude)

Pins 20, 21 and 24, are the inputs to a multiplier with the output at Pin 23. All three inputs, although named differently, are the same internally and can be combined in any means to provide the desired output. However, the product of the three inputs is restricted to less than 1.9 Vp-p or the output waveform will experience current limiting. Input bias current must be provide and therefore the input waveforms require DC coupling. The output is clamped and blanked during the appropriate intervals.

#### Internally Generated Waveforms

Within the MC1388, operations are performed on the horizontal and vertical ramps to produce several waveforms before being provided as outputs through buffers.

Of the internally generated waveforms resulting from operations on the horizontal ramp are a blanked version of the horizontal ramp (+H, Pin 6). A blanked, clamped and squared version of the horizontal ramp (±H<sup>2</sup>, Pins 7 and 8), and a blanked, clamped and cubed version of the horizontal ramp(±H<sup>3</sup>, Pins 17 and 18).

The vertical ramp is blanked and provided at Pins 35 and 36 ( $\pm$ V). Also, a squared, clamped, and blanked version of the vertical ramp is provided at Pins 33 and 34 ( $\pm$ V<sup>2</sup>).

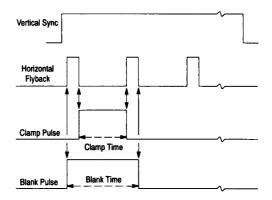

Blanking of the waveforms occurs once every vertical retrace. Clamping occurs during this blanked interval.

## **Outputs Buffers and Clamps**

The 18 output waveforms are buffered and made available at the output pins. The output buffers are capable of supplying 5.0 mA. A simplified schematic of the output stage is shown in Figure 6.

Figure 6. Output Circuitry

Although all outputs are blanked once each vertical period, not all of them are clamped. Clamping is performed only on the horizontal and vertical parabola outputs  $(\pm H^2, \pm V^2)$ , the horizontal cubic outputs  $(\pm H^3)$ , and the three-input multiplier

output (H' V'out). Clamping occurs after the leading edge of a vertical sync pulse. Blanking logic zeros the outputs for the time spanned by the first two horizontal pulses during the vertical sync period (see Figure 7B). Clamping circuitry works for the line period between the first two horizontal blanking intervals. Clamping is done by storing a voltage on the clamp capacitor that is proportional to the current required to force the output voltage of the buffer to zero. This provides a sustained current for the next vertical period that is capable of cancelling the DC offset in the waveform. Internal circuitry present at the clamp pins is shown in Figure 7A, and a diagram showing relative timing is shown in Figure 7B.

Figure 7A. Clamp Circuitry for Output Waveforms

Figure 7B. Blanking and Clamping Diagram

# APPLICATION INFORMATION

The following information is provided to assist designing in the MC1388.

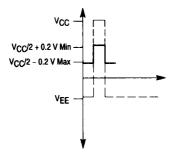

#### Horizontal and Vertical Flyback Inputs

Waveforms to the horizontal and vertical flyback inputs (Pins 2 and 39) must meet similar requirements except for the frequencies involved. The requirements can be described as follows:

- 1) VCC/2.0 + 0.2 V < Vin Peak < VCC

- 2) VEE + 0.5 < Vin Baseline ≤ VCC/2 0.2 V

- 3) 2.0 μs ≤ Pulse Width < 1/(2 f<sub>H</sub>) (Horizontal Input)

2.0 μs ≤ Pulse Width < 1/(2 f<sub>V</sub>) (Vertical Input)

and the allowable frequencies of operation are:

- A) 10 kHz  $\leq f_{\rm H} \leq 63$  kHz

- B) 45 Hz  $\leq f_{V} \leq$  120 Hz

Figure 8 shows the restrictions on the voltage levels for the flyback inputs.

Figure 8. Valid Input Levels for Both the Horizontal (Pin 2) and the Vertical (Pin 39) Inputs.

Since the input pins are equipped with ESD diodes, voltages on these pins should never exceed V<sub>CC</sub> or V<sub>EE</sub> by more than 0.5 V.

## Horizontal Oscillator and Phase-Locked-Loop

Since the charge and discharge of the capacitor at Pin 3 (C<sub>H</sub>) is done with constant currents, the voltage waveform of the capacitor voltage is:

$$\pm \Delta V = \pm \frac{1 \Delta t}{C}$$

,where  $\Delta t$  is the trace or retrace time.

The horizontal frequency is then the inverse of the sum of the charge time and the discharge time,

$$f$$

horizontal =  $\frac{1}{(t_{charge} + t_{discharge})}$

where, t<sub>charge</sub> = trace time and t<sub>discharge</sub> = retrace time. This relates the trace and retrace time to element values, internal quantities and a design variable, I<sub>charge</sub>. So,

$$t_{charge} = \frac{C_{H} \Delta V_{p-p}}{I_{charge}}$$

and  $t_{discharge} = \frac{C_{H} \Delta V_{p-p}}{I_{discharge}}$

$\Delta Vp\text{-p}$  and ldischarge are fixed (ldischarge is typically 1.0 mA and  $\Delta Vp\text{-p}$  is  $\simeq$  2.5  $\Delta Vp\text{-p}). If <math display="inline">C_H$  is chosen to meet the requirements of retrace time and,

If C<sub>H</sub> is chosen to meet the requirements of retrace time and, trace time >> retrace time, then t<sub>charge</sub> >> t<sub>discharge</sub>.

then

$$f_{\text{horizontal}} \simeq \frac{1}{\text{tcharge}}$$

or,  $f_{\text{horizontal}} \simeq \frac{\text{Icharge}}{\text{CH } \Delta V_{p-p}}$

By choosing  $C_H$  and determining  $I_{charge}$  the horizontal frequency can be set, since  $\Delta Vp$ -p is known. Referring to Figure 2, the current out of Pin 4 is the current  $I_{charge}$  and is composed of,

$$I_{charge} = \frac{1.25}{RHset} - I_{ERROR}$$

where IERROR is the current from the phase detector when the loop is locked and was determined in the FUNCTIONAL DESCRIPTION to be,

$$IERROR = \frac{(V_5 - V_4)}{R_F}$$

The horizontal frequency is now defined and is.

$$f_{\text{horizontal}} = \left\{ \frac{1.25}{\text{RHset}} \ \pm \ \frac{(\text{V}_5 \ - \ \text{V}_4)}{\text{R}_F} \right\} \left( \frac{1}{\text{C}_H \ \Delta \text{V}_{\text{p-p}}} \right) \, \text{or},$$

fhorizontal = ffree run  $\pm \Delta f$ ,

where  $\Delta f$  is the frequency difference between the horizontal free run frequency and the frequency of the input signal, R<sub>Hset</sub> is the resistance from Pin 4 to ground, R<sub>F</sub> is the resistor between Pins 4 and 5, and C<sub>H</sub> is the capacitor from Pin 3 to ground. It is to be emphasized that this equation holds true only when the loop is locked.

The phase detector sensitivity, Kpp, is determined from the slope of the curve which describes the average current output from the phase detector and the phase error related to that current. It is defined by.

$$\mathsf{KPD} \simeq \frac{2 \; \mathsf{IPDmax}}{\mathsf{SW} \; 2\pi f \, \mathsf{H}} \; (\mathsf{A/rad}) \; \mathsf{or}, \; \frac{900 \; \bullet \; 10^{-6}}{\mathsf{SW} \; 2\pi f \, \mathsf{H}} (\mathsf{A/rad}).$$

IpD $_{\rm max}$  is the maximum current that can be sourced or sinked from the phase detector and SW is the width of the horizontal flyback input pulse in seconds.  $f_{\rm H}$  is the frequency of the horizontal flyback input.

The oscillator sensitivity, K<sub>O</sub>, defined by  $\partial f_H/\partial I$  is,

$$K_O \simeq \frac{1}{2.5 \text{ CH}} (Hz/A)$$

Since the maximum average voltage difference between Pins 4 and 5 is capable of about ±2.5 V, the maximum error current transfer from Pin 5 to Pin 4 is.

$$|ERRORmax| \le \frac{\pm 2.5 \text{ V}}{R_F}.$$

And also redefines the phase detector sensitivity as,

$$KpD' \simeq \frac{2.5 \text{ V}}{\text{Re } \pi \text{ SW} f_{H}}$$

The product of the phase detector sensitivity, the oscillator sensitivity and the maximum phase error then defines maximum possible deviation from the free run frequency. The maximum possible phase error is the phase error corresponding to one half the width of the horizontal flyback input pulse or, (SW/2),  $2\pi f_H$ , so the maximum deviation from the free run frequency is one half the lock range and is,

$$\pm \frac{f_{\text{Flock}}}{2} \simeq \frac{1}{\text{CH RF}}$$

(The value of  $f_{Flock}$  should be kept small enough to prevent loop lock on harmonics. A general rule of thumb is  $f_{lock} < 10\%$  of the desired horizontal frequency.) Then IERROR is less than 10% of I<sub>charge</sub>, and the horizontal frequency is almost entirely determined by,

$$f$$

horizontal  $\simeq \frac{1.25}{\text{RHset CH }\Delta\text{V p-p}}$ ,  $\Delta\text{V p-p}\simeq 2.5$ ,

so this becomes,

$$f_{\text{horizontal}} \approx \frac{1}{2 \text{ R}_{\text{Hset CH}}}$$

which is also the horizontal free run frequency. The horizontal free run frequency should be set at or very near the desired horizontal frequency since the lock range is centered about this frequency.

Calculating the external components is then based on the following requirements:

- 1) The value of C<sub>H</sub> satisfies the requirements for retrace time, or C<sub>H</sub>  $\leq 5.6 \cdot 10^{-4}$  tdischarge.

- The value of the resistance from Pin 5 to ground is given by,

RHset

$$\approx \frac{1}{2 f_{\text{horizontal}} C_{\text{H}}}$$

(The value of the resistor calculated for  $R_{HSet}$  should be considered approximate. The 5.0 k $\Omega$  pot shown in the application circuit of Figure 12 is recommended for optimization).

The resistor RF is such that the lock range is a reasonable choice (fH/10) given by,

$$R_F \simeq \frac{2}{C_H (\pm \int_{lock})}$$

For 15,625 Hz, recommended values are,  $C_H$  = 0.001  $\mu$ F,  $R_{Hset}$  = 30  $k\Omega$  + 5.0  $k\Omega$  variable, and  $R_F$   $\geq$  620  $k\Omega$ . For 31,250 Hz, recommended values are,  $C_H$  = 0.001  $\mu$ F,  $R_{Hset}$  = 13  $k\Omega$  + 5.0  $k\Omega$  variable, and  $R_F$   $\geq$  300  $k\Omega$ .

## **Vertical Timing**

To set the vertical timing a capacitor-resistor pair must be chosen (refer to Figure 3). The vertical timing section is similar to the horizontal section in that the frequency is determined by the charge and discharge rate of a capacitor at Pin 38. However, the vertical ramp oscillator is an injection type and the proper peak-to-peak voltage must be set with Ryset.

The basic equation,

$$\pm \Delta V = \pm \frac{1 \Delta t}{C V}$$

describes the capacitor voltage for the charge and discharge currents made available at Pin 38. Further, if tretrace << trace then,

$$f$$

vertical =  $f$ V  $\simeq \frac{1}{\Delta t_{trace}} = \frac{1}{\Delta t_{charge}}$

and the vertical frequency is determined by the charging current,  $\Delta V$  and the capacitor value.

The reference voltage for developing the charging current is present at Pin 37 and is nominally 1.25 V. The charging current is then defined by the resistance at this node,

The resistance required can be determined for a particular frequency and capacitor combination. The capacitor voltage,  $\Delta V$ , must be nominally 2.5 Vp-p for the specified full scale vertical outputs. Using this value, the proper combination Ryset and Cy, can be calculated.

The current available to discharge C $_V$  is approximately 800  $\mu$ A. So, a practical C $_V$  value is described by, C $_V \le 3.2$  • 10<sup>-4</sup>  $\Delta t$ , where  $\Delta t$  is required retrace time.

This value of Cy is next used to calculate the value Ryset considering the vertical frequency desired,

Icharge =

$$\frac{1.25}{\text{RVset}}$$

=  $\frac{\text{C}_{V} \Delta \text{V}}{\Delta \text{t}}$  =  $\text{C}_{V} \Delta \text{V}$  fy or,

$$R_{Vset} \simeq \frac{1.25}{C_V \Delta V f_V} = \frac{1.25}{C_V 2.5 f_V} \simeq \frac{1}{2 C_V f_V}$$

(The equation given for  $RV_{Set}$  is approximate and should be used only as a starting point. The 25  $k\Omega$  pot in the applications circuit of Figure 12 is used to optimize this value.)

#### Sine Wave Generation

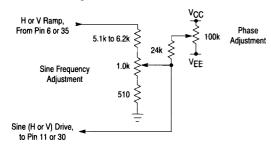

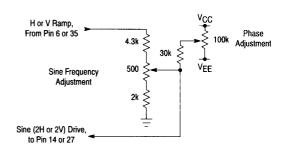

Shown in Figure 9 and 10 are two circuits which can be used to provide drive to the sine generator circuits. These circuits DC couple to the sine drive inputs providing the necessary base drive. The circuit in Figure 9 will provide

Figure 9. Sine H or V Driver

An approximate relation between the number of cycles and peak-to-peak input voltage is,

Vinp-p

$$\approx \frac{\text{number of cycles} + 0.2}{1.25}$$

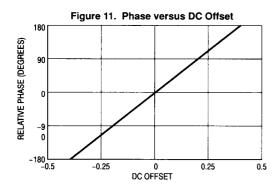

The phase of the output sine wave is a function of the input ramp DC offset. Figure 11 shows the relationship between the phase and the offset.

If a phase change is desired, it should be remembered that the input windows for the sine generators are between -850 mV and +850 mV centered about zero, therefore, a DC offset will reduce the allowable input ramp peak-to-peak amplitude.

adequate ramp amplitude for a single cycle of a sine wave at the horizontal or vertical frequency and the circuit in Figure 10 will provide adequate ramp amplitude for two cycles of a sine wave.

Figure 10. Sine 2H or 2V Driver

## **Multiplier Circuit**

The multiplier is made up of three inputs, H'<sub>in</sub>, V'<sub>in</sub> and H'V' Amplitude (Pins 20, 21 and 24 respectively), which are internally equivalent. The voltage output on Pin 23 is the product of the voltage on the input pins and is restricted to a maximum output voltage of 1.9 Vp-p, or current limiting will occur. Any combination of the three inputs can be used, provided that the product of all the inputs is less than 5.0 Vp-p.

## **Application Circuit**

Figure 12 shows an application circuit with component values applicable for,

fhorizontal = 31.25 kHz fvertical = 60 Hz  $\pm f$ lock = 2.3 kHz  $\pm f$ pull-in = 2.3 kHz

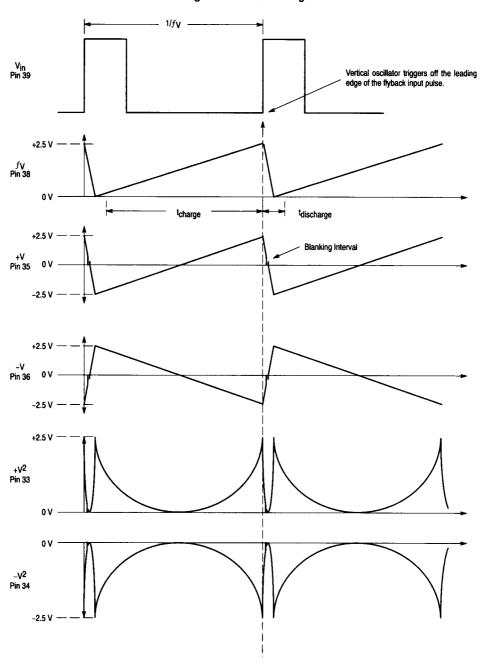

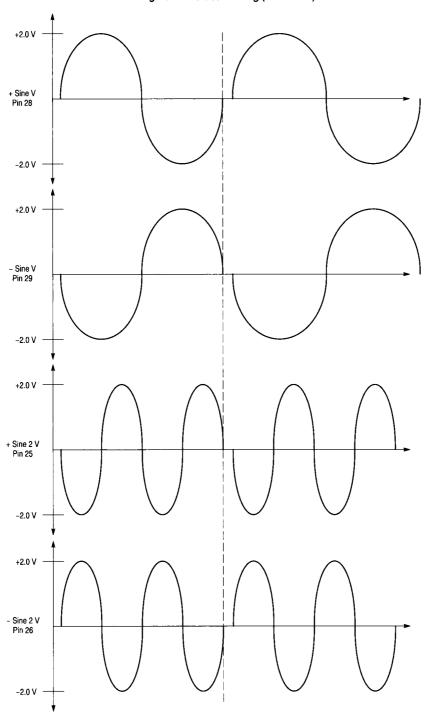

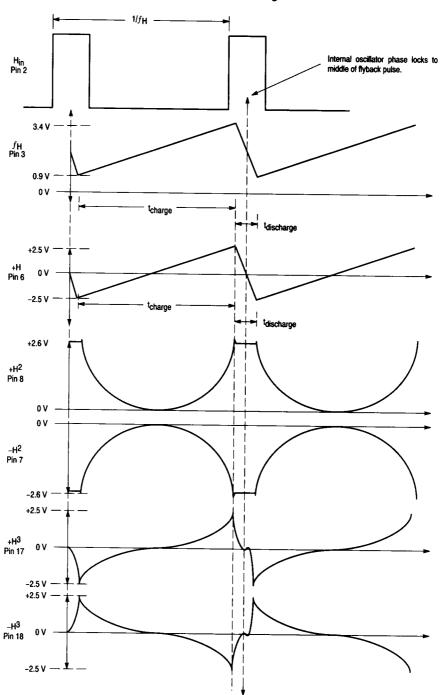

Figure 13 shows the timing of all the vertical waveforms for the application circuit. Figure 14 shows the timing of all the horizontal waveforms for the application circuit.

Figure 12. Application Circuit of the MC1388

Figure 13. Vertical Timing

Figure 13. Vertical Timing (continued)

Figure 14. Horizontal Timing

Figure 14. Horizontal Timing (continued)