# Color LCD Interface Engine (CLINE)

# HITACHI

#### Description

The HD66850F CLINE interface controller converts multi-color video signals for CRT display into color or monochrome LCD data.

This device enables an LCD system to replace a CRT display system without any changes to the original display system. It automatically adapts to display modes of the IBM-VGA (Video Graphics Array<sup>TM</sup>) system, facilitating the configuration of an LCD system.

The CLINE can control TN-type (Twisted Nematic) color and monochrome LCDs and can display a maximum of 4096 color levels or 16 gray levels.

Note: Video Graphics Array is a trademark of International Business Machines Corporation, U.S.A.

#### Features

- Various LCD panel sizes supported — 640 or 720 dots wide

- -32 to 512 lines high

- Programmable display size — 32 to 720 dots wide

- -32 to 512 lines high

- Easy-to-see display

- Centering

- Stretching (display stretched to fill out the panel)

- Improved gradation display quality using the pulse width modulation method

- Desired gradation levels assignable to each display color through the use of internal gradation level palettes

- Changeable LCD frame frequency

- Through the use of a multi-port RAM frame buffer

- Within the range of 1/2 to 2 times of CRT display dot clock frequency

- High-speed operating frequency: 32 MHz (CRT display dot clock)

- Recommended LCD drivers: HD66110ST (column) and HD66115T (common)

- Single power supply: +5 V

#### **Ordering Information**

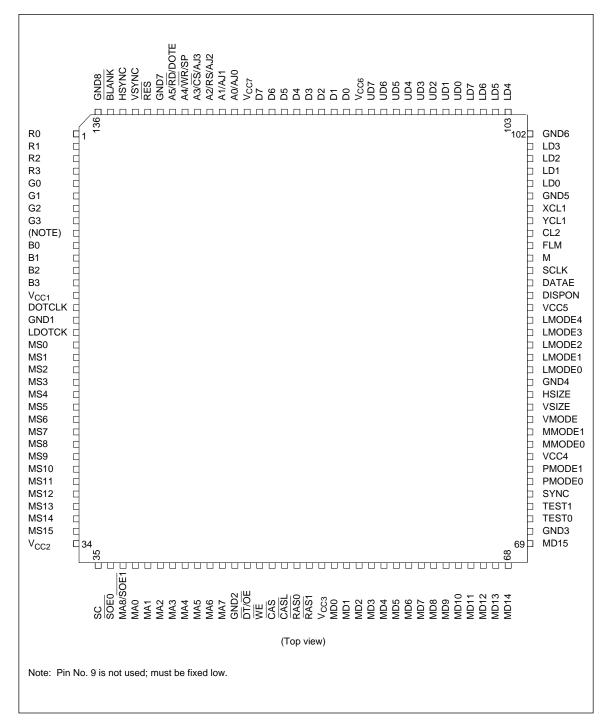

Type No.PackageHD66850F136-pin plastic QFP (FP-136)

#### **Pin Arrangement**

| Туре            | Symbol                                   | Pin No.                              | Pin Name                   | I/O | Function                                                                                                                                                 |

|-----------------|------------------------------------------|--------------------------------------|----------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>supply | V <sub>CC</sub> 1 –<br>V <sub>CC</sub> 7 | 14, 34, 53, 76,<br>88, 115, 124      | $V_{CC1} - V_{CC7}$        | —   | All of these pins must beAll<br>connected to a +5V supply                                                                                                |

| MPU/ROM         | GND1 –<br>GND8                           | 16, 46, 70, 82,<br>97, 102, 131, 136 | GND1 – GND7                | —   | All of these pins must be grounded.                                                                                                                      |

| or program      | D0 – D7*1                                | (M) 116 – 123                        | Data 0 – 7                 | I/O | Transfer data between internal registers and MPU                                                                                                         |

| interface       | D0 – D7*1                                | (R) 116 – 123                        | Data 0 – 7                 | I   | Input data to internal registers from external ROM                                                                                                       |

|                 | DOTE                                     | (P) 130                              | Dot clock edge<br>change   | I   | Switches RGB data latch timing<br>High: Data latched at the rising<br>edge of DOTCLK pulses<br>Low: Data latched at the falling<br>edge of DOTCLK pulses |

|                 | RD                                       | (M) 130                              | Read                       | I   | Inputs a read signal for reading data from internal registers                                                                                            |

|                 | A5                                       | (R) 130                              | Address 5                  | 0   | Outputs external ROM address 5                                                                                                                           |

|                 | SP                                       | (P) 129                              | Spread display<br>select I | I   | Selects either of the following<br>display size modes<br>High: Double – width display<br>Low: Normal display                                             |

|                 | WR                                       | (M) 129                              | Write                      | I   | Inputs a write signal for writing data to internal registers                                                                                             |

|                 | A4                                       | (R) 129                              | Address 4                  | 0   | Outputs external ROM address 4                                                                                                                           |

|                 | AJ3                                      | (P) 128                              | Adjust 3                   | I   | Adjusts the display timing signal (table 1)                                                                                                              |

|                 | CS                                       | (M) 128                              | Chip select                | I   | Inputs a chip select signal to select<br>the CLINE<br>High: The CLINE not selected<br>Low: The CLINE selected                                            |

|                 | A3                                       | (R) 128                              | Address 3                  | 0   | Outputs external ROM address 3                                                                                                                           |

|                 | AJ2                                      | (P) 127                              | Adjust 2                   | I   | Adjusts the display timing signal (table 1)                                                                                                              |

|                 | RS                                       | (M) 127                              | Register select            | I   | Inputs a register select signal to<br>select either CLINE data registers<br>or index register<br>High: Data registers<br>Low: The index register         |

|                 | A2                                       | (R) 127                              | Address 2                  | 0   | Outputs external ROM address 2                                                                                                                           |

|                 | AJ0, AJ1*2                               | (P) 125, 126                         | Adjust 0, 1                | Ι   | Adjust the display timing signal (table 1)                                                                                                               |

|                 | A0, A1* <sup>2</sup>                     | (R) 125, 126                         | Address 0, 1               | 0   | Output external ROM addresses 0<br>and 1, respectively                                                                                                   |

# Pin Description

(M): For MPU programming method (R): For ROM programming method (P): For pin programming method I/O: Input/Output

| Туре                     | Symbol                     | Pin No.   | Pin Name                      | I/O | Function                                                                                                                                                                                                                                                                                                |

|--------------------------|----------------------------|-----------|-------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | R0 – R3*3                  | 1 – 4     | Red serial data 0 – 3         | Ι   | Input CRT display R data                                                                                                                                                                                                                                                                                |

| interface                | G0 – G3*3                  | 5 – 8     | Green serial data 0 – 3       | Ι   | Input CRT display G data or<br>monochrome data                                                                                                                                                                                                                                                          |

| Type<br>CRT<br>interface | B0 – B3* <sup>3</sup>      | 10 – 13   | Blue serial data 0 – 3        | I   | Input CRT display B data: For<br>monochrome display, B1 selects 16-<br>gray-scale display and B0 indicates<br>the type of CRT display data input.<br>B1 = high: Prohibited<br>B1 = low: 16-level gray scale<br>display<br>B0 = high: 64-color data input<br>B0 = low: 16-level gray scale<br>data input |

|                          | DOTCLK                     | 15        | Dot clock                     | Ι   | Inputs the dot clock pulses for CRT display                                                                                                                                                                                                                                                             |

|                          | HSYNC                      | 134       | Horizontal synchronization    | Ι   | Inputs the CRT horizontal synchro-<br>nization signal                                                                                                                                                                                                                                                   |

|                          | VSYNC                      | 133       | Vertical synchronization      | Ι   | Inputs the CRT vertical synchroniza-<br>tion signal                                                                                                                                                                                                                                                     |

|                          | BLANK                      | 135       | Blanking                      | I   | Inputs a display timing siganl<br>indicating horizontal or vertical<br>display period, or a blank signal<br>indicating the display period with<br>border area period                                                                                                                                    |

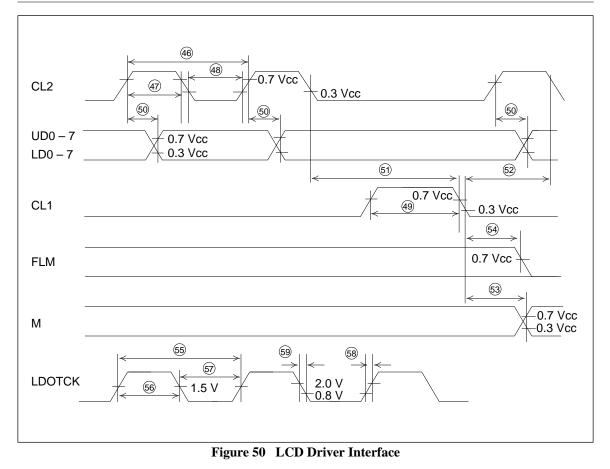

| -                        | UD4 –<br>UD7* <sup>4</sup> | 111 – 114 | LCD upper panel data<br>4 – 7 | 0   | Output LCD upper panel data or R data                                                                                                                                                                                                                                                                   |

|                          | UD0 –<br>UD3*4             | 107 – 110 | LCD upper panel data<br>0 – 3 | 0   | Output LCD upper panel data or G data                                                                                                                                                                                                                                                                   |

|                          | LD4 –<br>LD7*4             | 103 – 106 | LCD lower panel data<br>4 – 7 | 0   | Output LCD lower panel data or<br>B data                                                                                                                                                                                                                                                                |

|                          | LD0 –<br>LD3*4             | 98 – 101  | LCD lower panel data<br>0 – 3 | 0   | Output LCD lower panel data or I data                                                                                                                                                                                                                                                                   |

|                          | XCL1*4                     | 96        | X-driver latch clock          | 0   | Outputs the LCD data latch clock<br>pulses for X-drivers                                                                                                                                                                                                                                                |

|                          | YCL1                       | 95        | Y-driver shift clock          | 0   | Outputs the LCD data line shift<br>clock pulses for Y-drivers                                                                                                                                                                                                                                           |

|                          | CL2                        | 94        | X-driver shift clock          | 0   | Outputs the LCD data line shift<br>clock pulses for X-drivers                                                                                                                                                                                                                                           |

|                          | FLM                        | 93        | First line maker              | 0   | Outputs the first line maker for<br>Y-drivers                                                                                                                                                                                                                                                           |

I/O: Input/Output

| Туре             | Symbol                      | Pin No. | Pin Name                                    | I/O | Function                                                                                                                                     |

|------------------|-----------------------------|---------|---------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| LCD<br>interface | М                           | 92      | Μ                                           | 0   | Outputs a signal for converting LCD drive signals to AC                                                                                      |

|                  | SCLK                        | 91      | Shift clock                                 | 0   | Outputs clock pulse with a<br>frequency identical to CL2 but<br>without a retrace period                                                     |

|                  | DATAE*4                     | 90      | Data enable                                 | 0   | Indicates LCD data display period                                                                                                            |

|                  | DISPON*4                    | 89      | Display on                                  | 0   | Controls LCD on/off                                                                                                                          |

|                  | LDOTCK                      | 17      | LCD dot clock                               | I   | Inputs LCD dot clock pulses                                                                                                                  |

| Buffer<br>memory | MD0 –<br>MD15 <sup>*5</sup> | 54 – 69 | Memory data 0 – 15                          | 0   | Output data to be written to buffer memory                                                                                                   |

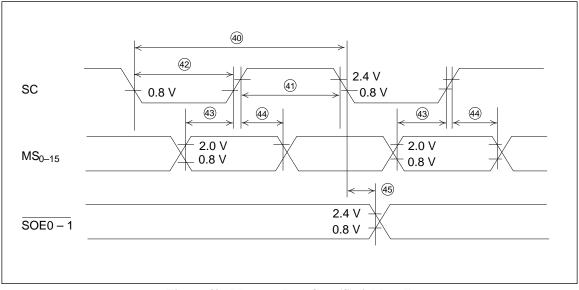

| interface        | MS0 –<br>MS15 <sup>*6</sup> | 18 – 33 | Memory serial data<br>0 – 15                | Ι   | Input data read from buffer memory                                                                                                           |

|                  | MA0 –<br>MA7* <sup>5</sup>  | 38 – 45 | Memory address<br>0 – 7                     | 0   | Output buffer memory addresses<br>0 – 7                                                                                                      |

|                  | MA8/<br>SOE1*5              | 37      | Memory address 8/<br>serial output enable 1 | Ο   | Outputs buffer memory address 8<br>when 1-Mbit RAMs are used or<br>outputs a serial data output enable<br>signal when 256-kbit RAMs are used |

|                  | SOE0 <sup>*5</sup>          | 36      | Serial output enable 0                      | 0   | Output a serial data output enable signal for buffer memory                                                                                  |

|                  | WE <sup>*5</sup>            | 48      | Write enable                                | 0   | Outputs a write enable signal for<br>buffer memory                                                                                           |

|                  | DT/OE <sup>*5</sup>         | 47      | Data transfer/output<br>enable              | 0   | Outputs a data transfer signal or<br>an output enable signal for buffer<br>memory                                                            |

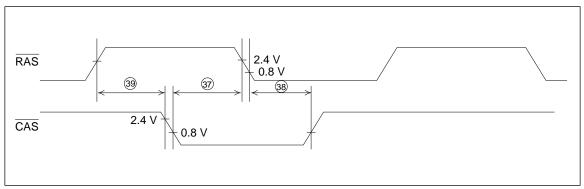

|                  | RAS0,<br>RAS1* <sup>5</sup> | 51, 52  | Row address strobe 0, row address strobe 1  | 0   | Outputs a row address strobe signal<br>for buffer memory                                                                                     |

|                  | CAS,<br>CASL <sup>*5</sup>  | 49, 50  | Column address<br>strobe                    | 0   | Outputs a column address strobe signal for buffer memory                                                                                     |

|                  | SC*5                        | 35      | Serial clock                                | 0   | Outputs serial read clock pulses for<br>buffer memory                                                                                        |

| Mode<br>control  | PMODE0,<br>PMODE1           | 74, 75  | Program mode 0,<br>Program mode 1           | Ι   | Select a CLINE programming<br>method (table 2)                                                                                               |

|                  | LMODE0 –<br>LMODE4          | 83 – 87 | LCD mode 0 – 4                              | Ι   | Select a display mode (table 9)                                                                                                              |

|                  | MMODE0,<br>MMODE1           | 77, 78  | Memory mode 0, 1                            | I   | Select a memory configuration (table 3)                                                                                                      |

|                  | SYNC                        | 73      | Synchronization                             | Ι   | Select a basic clock for LCD<br>High: DOTCLK<br>Low: LDOTCK                                                                                  |

I/O: Input/Output

| Туре                      | Symbol          | Pin No. | Pin Name            | I/O | Function                                                                             |

|---------------------------|-----------------|---------|---------------------|-----|--------------------------------------------------------------------------------------|

| Mode<br>control<br>(cont) | VMODE           | 79      | VGA mode            | I   | Specifies a CRT display system<br>High: Non-VGA system<br>Low: VGA system            |

|                           | VSIZE           | 80      | LCD vertical size   | I   | Specifies the vertical size of the<br>LCD panel<br>High: 480 lines<br>Low: 400 lines |

|                           | HSIZE           | 81      | LCD horizontal size | I   | Specifies the horizontal size of the<br>LCD panel<br>High: 720 dots<br>Low: 640 dots |

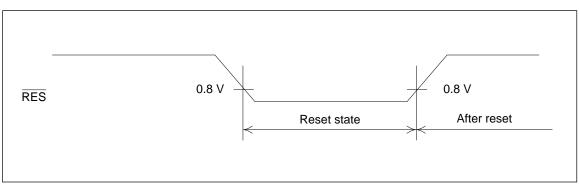

|                           | RES             | 132     | Reset               | I   | Inputs an external reset signal                                                      |

|                           | TEST0,<br>TEST1 | 71, 72  | Test 0, 1           | I   | Used for tests; Must be grounded                                                     |

I/O: Input/Output

Notes: 1. Must be fixed low for pin programming method.

- 2. Must be fixed low for MPU programming method.

- 3. Must be fixed low when not used.

- 4. Must be left disconnected when not used.

- 5. Must be left disconnected when buffer memory is not used.

- 6. Must be fixed low when buffer memory is not used.

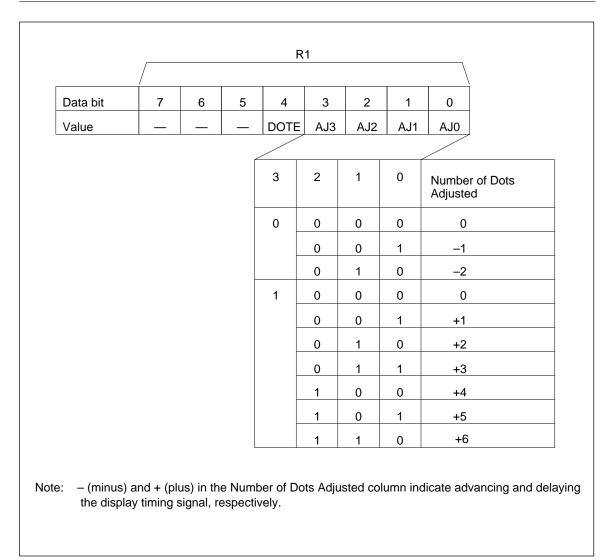

#### Table 1Display Timing Signal Fine Adjustment

|     |     | Pin |     | _ Number of Dots |  |

|-----|-----|-----|-----|------------------|--|

| AJ3 | AJ2 | AJ1 | AJ0 | Adjusted         |  |

| 0   | 0   | 0   | 0   | 0                |  |

| 0   | 0   | 0   | 1   | -1               |  |

| 0   | 0   | 1   | 0   | -2               |  |

| 1   | 0   | 0   | 0   | 0                |  |

| 1   | 0   | 0   | 1   | +1               |  |

| 1   | 0   | 1   | 0   | +2               |  |

| 1   | 0   | 1   | 1   | +3               |  |

| 1   | 1   | 0   | 0   | +4               |  |

| 1   | 1   | 0   | 1   | +5               |  |

| 1   | 1   | 1   | 0   | +6               |  |

Note: - (minus) indicates advancing the phase of the display timing signal,

+ (plus) indicates delaying the phase of the display timing signal.

#### Table 2 Programming Method Selection

|        | Pin    | _                        |

|--------|--------|--------------------------|

| PMODE1 | PMODE0 | Programming Method       |

| 0      | 0      | Pin                      |

| 0      | 1      | Internal registers (MPU) |

| 1      | 0      | Internal registers (ROM) |

| 1      | 1      | Prohibited               |

#### Table 3Memory Configuration Selection

|        | Pin    | _                                                                |

|--------|--------|------------------------------------------------------------------|

| MMODE1 | MMODE0 | Memory Configuration                                             |

| 0      | 0      | 1-Mbit RAM                                                       |

| 0      | 1      | 256-kbit RAM                                                     |

| 1      | 0      | No memory                                                        |

| 1      | 1      | No memory (when the CRT controller supports dual screen display) |

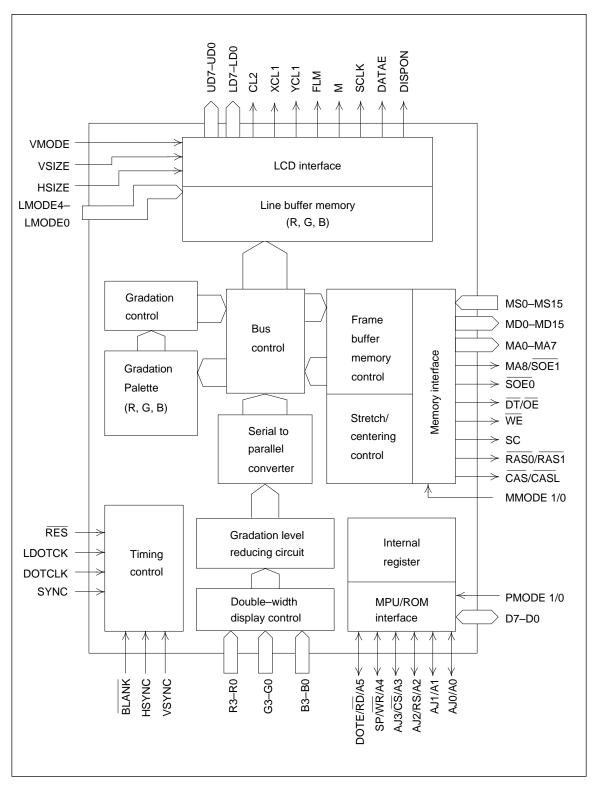

#### **Block Diagram**

**Register List** Table 4

|           |    |             |              | )            |                |                  |                |                                                                                                                                                 |                     |              |      |      |      |      |           |

|-----------|----|-------------|--------------|--------------|----------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|------|------|------|------|-----------|

|           |    |             |              | Inde         | Index Reg      | ō                | . Rea.         |                                                                                                                                                 | Program             | Read/        |      |      |      | Dat  | Data Bit: |

|           | CS | RS          | 3            | 2            | -              | 0                | No.            | Register Name                                                                                                                                   | Units               | Write        | 7    | 6    | 5    | 4    | 3         |

|           | -  |             | I            |              | I              | Ι                | I              | 1                                                                                                                                               | I                   | I            | *    | *    | *    | *    | *         |

|           | 0  | 0           | 0            | 0            | 0              | 0                | ≝              | Index                                                                                                                                           |                     | N            |      | I    |      |      | IA3       |

|           | 0  | -           | 0            | 0            | 0              | 0                | RO             | Control                                                                                                                                         | 1                   | RW           | I    | I    | I    | STE  | CRE       |

|           | 0  | -           | 0            | 0            | 0              | -                | R1             | Input timing control                                                                                                                            | Dot                 | R/W          |      |      |      | DOTE | AJ3       |

|           | 0  | -           | 0            | 0            | -              | 0                | R2             | Horizontal display size                                                                                                                         | Character           | R/W          |      | DHG  | DH5  | DH4  | DH3       |

|           | 0  | -           | 0            | 0            | ۲              | ٢                | R3             | Vertical display size (high-order)                                                                                                              | Line                | R/W          | I    | I    | I    | I    | Ι         |

|           | 0  | -           | 0            | -            | 0              | 0                | R4             | Vertical display size (low-order)                                                                                                               | Line                | RM           | DV7  | DV6  | DV5  | DV4  | DV3       |

| Н         | 0  | ~           | 0            | -            | 0              | -                | R5             | Centering raster                                                                                                                                | Line<br>(Raster)    | R/W          | CR7  | CR6  | CR5  | CR4  | CR3       |

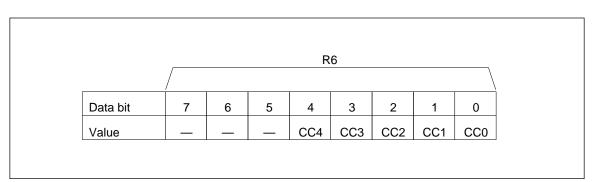

| IT/       | 0  | -           | 0            | ~            | ~              | 0                | R6             | Centering character                                                                                                                             | Character           | R/W          | I    | I    | I    | CC4  | CC3       |

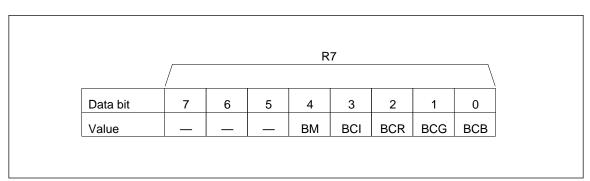

| <b>4C</b> | 0  | -           | 0            | -            | -              | -                | R7             | Border color control                                                                                                                            |                     | R/W          | I    |      |      | BM   | BCI       |

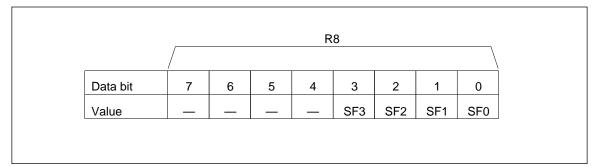

| H         | 0  | -           | ٢            | 0            | 0              | 0                | R8             | Stretching control                                                                                                                              | Line                | R/W          | I    | I    | I    | I    | SF3       |

|           | 0  | -           | ٢            | 0            | 0              | ٢                | R9             | Stretching index (high-order)                                                                                                                   | Line                | RM           | SI15 | SI14 | SI13 | SI12 | SI11      |

|           | 0  | -           | -            | 0            | -              | 0                | R10            | Stretching index (low-order)                                                                                                                    | Line                | R/W          | SI7  | SIG  | SI5  | SI4  | SI3       |

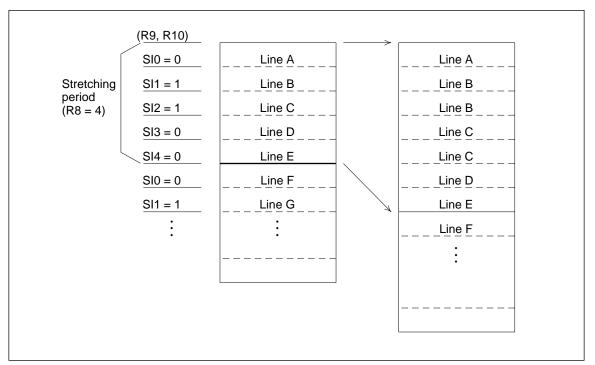

|           | 0  | -           | -            | 0            | -              | -                | R11            | Gradation level palette address                                                                                                                 | I                   | M            | I    | I    | PS1  | PS0  | PA3       |

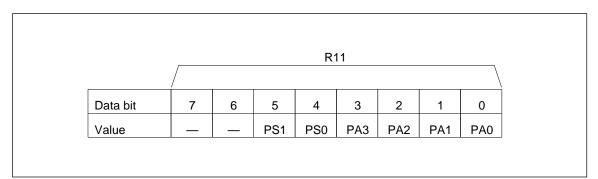

|           | 0  | ٦           | ٢            | ٢            | 0              | 0                | R12            | Gradation level palette data                                                                                                                    | I                   | R/W          | I    | I    | PD5  | PD4  | PD3       |

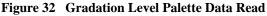

|           | 0  | <del></del> | <del></del>  | <del></del>  | 0              | -                | R13            | Gradation display clock period (high-order)                                                                                                     | Dot                 | R/W          | I    | Ι    | I    | I    | I         |

|           | 0  | -           | <del>.</del> | <del>.</del> | -              | 0                | R14            | Gradation display clock period (low-order)                                                                                                      | Dot                 | R/W          | GC7  | GC6  | GC5  | GC4  | GC3       |

|           | 0  | ٦           | ٦            | 1            | ٦              | 1                | R15            | Reserved                                                                                                                                        | Ι                   | Ι            | Ι    | I    | Ι    | I    |           |

|           | ۶  | Notes:      | 1.<br>В В    | lits m       | arkec<br>arkec | d with<br>d with | * can<br>– are | Bits marked with $st$ cannot either read from or written to. Bits marked with – are invalid and must be initialized to 0s; they cannot be read. | ).<br>D Os; they ca | innot be rea | jd.  |      |      |      |           |

BCB

BCG S

SF0

SF1

SF2

SI8

SI9 S<u>1</u>

SI10

SI2 PA2

ö

CC CC CC BCR

ო

# **Register List**

0 -<del>X-</del>

~ -<del>X</del>-

2

ß

-<del>X</del>-

CLINE registers are summarized in table 4.

DISP ON

Ъ

ССЕ

ш

AO

Ā

IA2

θНΟ DV8

DH1

DH2

AJO

٩J

AJ2

\_\_\_ ო DVO CR0

D 7 CR1

DV2

ო

CR2

ო

# HD66850F

GC8

I

I

PDO

PD1

PD2

e

PA0 SIO

PA1

СO

GC1

GC2

ო

I

#### **System Description**

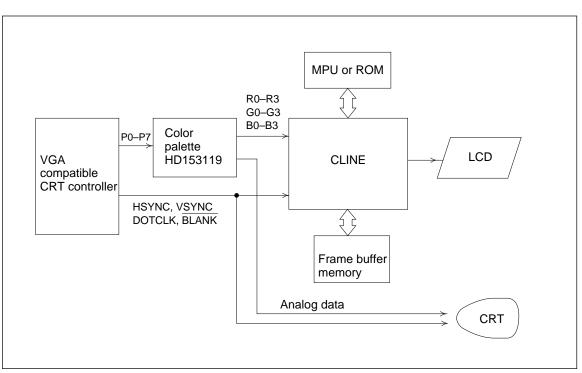

Figure 1 shows an example of a VGA-compatible display system implemented with the CLINE. In this system, a color palette HD153119 (Hitachi), which is capable of digital output, is used with a VGA-compatible CRT controller. The CLINE receives digital color data and display sychronization signals from the color pallette and the CRT controller, respectively, and displays 4096-color images on a color LCD, or 16-level grayscale images on a monochrome LCD. With minor modification of the existing CRT display system, simultaneous LCD and CRT display is possible.

Addition of an external frame buffer memory (dual-port RAM) allows the LCD frame frequency to be increased above that of a CRT. This enables easy-to-see gradation display and the control of LCDs having a dual screen configuration.

CLINE operation may be controlled by internal registers through the 80-family MPU bus or an external ROM (as shown in the figure), or simply by pins.

Figure 1 System Block Diagram

### **Functional Description**

#### **Programming Methods**

To control CLINE functions, set the appropriate pins and/or internal registers according to the functions used. Controlling methods include pin and internal register programming methods. Internal register programming includes the MPU and ROM programming methods. Any of the three methods can be selected by the combined setting of pins PMODE0 and PMODE1 (table 2).

The pin programming method uses pins to control CLINE functions, and the internal register programming method uses data written to the internal registers to control the functions.

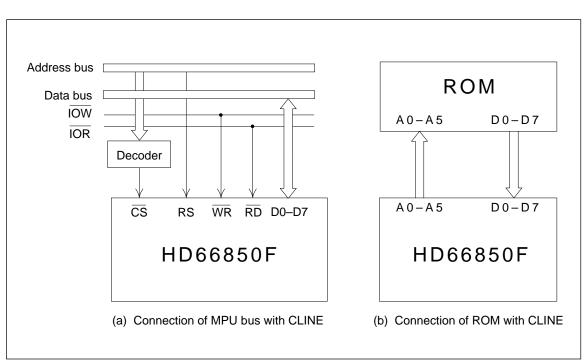

Figure 2 (a) shows a connection example of the CLINE and MPU buses for the MPU programming method. The CLINE bus, which is compatible with the 80-family microprocessor bus, can be directly connected to the host MPU bus.

Figure 2 (b) shows a connection example of the CLINE and ROM for the ROM programming method. In this case, data is automatically loaded into internal registers from the external ROM attached for this purpose. Note that with the ROM programming method, the reset signal must be applied before rewriting the internal registers or gradation level palettes.

Figure 2 Connection of MPU Bus or ROM with CLINE

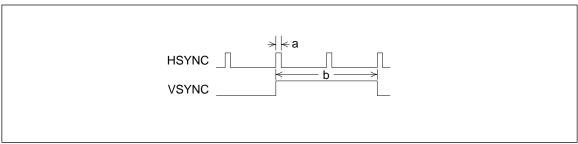

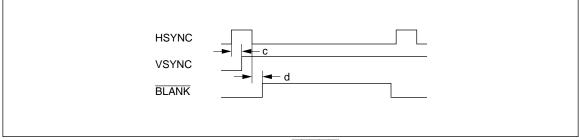

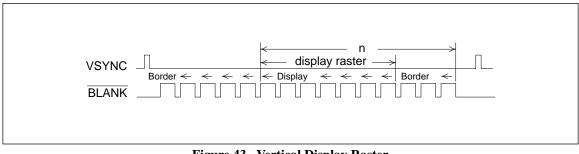

#### Automatic Adaptation to VGA Display Modes

VGA CRT display system display size varies depending on the display mode. (VGA display sizes are: 320, 360, 640, or 720 dots wide and 350, 400, or 480 lines high.) The CLINE identifies the current display mode from VSYNC and HSYNC signal polarities and the display period length, and changes the display size automatically (tables 5 and 6). This function is enabled by setting the VMODE pin low. The CLINE, based on this function, automatically sets the necessary registers (R0, R2, R3, R4, R5, R6, R8, R9, and/or R10) corresponding to the parameters of the display size, double-width display, gradation display clock, and stretching/centering display functions. (In MPU or ROM programming method, selection of vertical centering (bit 3 of R0) or stretching (bit 4 of R0) is

not automatic.) Consequently, in VGA display modes, rewriting these registers is disabled.

Note that display stretching and centering are unavailable when buffer memory is not used in the system, even in VGA display modes. In these cases, a display of different vertical size would be placed in the upper section of the LCD panel, resulting in a blank area in the lower section. Centering the display in a system without memory requires external circuits or BIOS tuning.

When displaying an image 720 dots wide (9 dots  $\times$  80 characters) on an LCD panel 640 dots wide, the CLINE removes the ninth horizontal dot of each character to prevent losing the far-right portion of the image.

| Table 5  | Automatic Vertical Display Size Settings for VGA Display Modes      |

|----------|---------------------------------------------------------------------|

| I WOIC C | Thatomatic vertical Display Size Settings for v Gir Display filoaes |

| VSYNC    | HSYNC    | Display Size | Border Rasters | Displayed Rasters |

|----------|----------|--------------|----------------|-------------------|

| Negative | Positive | 350 lines    | 1-6            | 7-356             |

| Positive | Negative | 400 lines    | 1-7            | 8-407             |

| Negative | Negative | 480 lines    | 1-8            | 9-488             |

#### Table 6 Automatic Horizontal Display Size Settings for VGA Display Modes

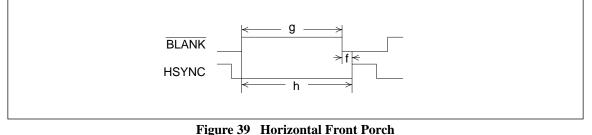

#### **BLANK Signal High Level**

| Pulse Width  | Display Size         | Border Dots | Displayed Dots |  |

|--------------|----------------------|-------------|----------------|--|

| 256-335 dots | 320 dots (256-color) | 1-5         | 6-325          |  |

| 336-359 dots | 320 dots (16-color)  | 1-8         | 9-328          |  |

| 360-511 dots | 360 dots             | 1-9         | 10-369         |  |

| 640-703 dots | 640 dots             | 1-8         | 9-648          |  |

| 704-767 dots | 720 dots             | 1-9         | 10-729         |  |

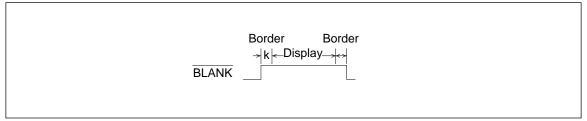

#### LCD Panel Size

LCD panel size is specified by either pins or internal registers.

For VGA modes, vertical panel size of 400 or 480 lines can be selected by the VSIZE pin and horizontal panel size of 640 or 720 lines by the HSIZE pin.

For non-VGA modes, the panel size is also specified by the VSIZE and HSIZE pins in pin programming method. In internal register programming method, vertical display size is specified by the vertical display size register (R3 and R4), within the range of 2 to 512 lines. Here, note that the vertical display size specified by R3 and R4 is the CRT display vertical size. When this size differs from the LCD panel vertical size. centering or stretching function must be used. Refer to the following equations for calculating the number of centering rasters and the stretching ratio. For the definition of the centering rasters, see figure 23, Centering Rasters,

• For centering

LCD panel vertical size (line) = CRT display vertical size (line) + centering rasters (lines)  $\times 2$

• For stretching

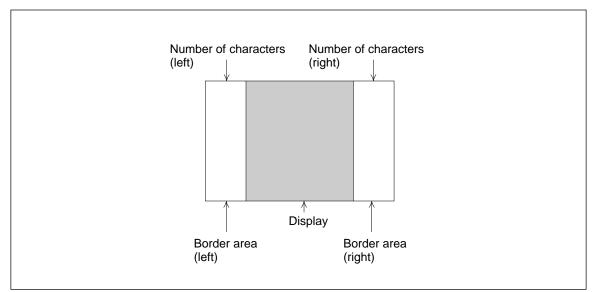

LCD panel vertical size (line) = CRT display vertical size (line) × stretching ratio Since LCD panel horizontal size is limited to 640 or 720 dots even in internal register programming method, centering function must be used as well so that the total number of horizontal dots including the CRT display area and border areas become 640 or 720. Refer to the following equation to calculate the number of centering characters. For the definition of the border areas and centering characters, see figure 25, Centering Characters.

LCD panel horizontal size (dot) = {number of horizontal display characters + (number of centering characters  $\times$  2)}  $\times$  8

#### **Double-Width Display**

Some CRT display systems have a low-resolution display mode of 320 horizontal dots in addition to a high-resolution display mode of 640 horizontal dots. In this case, the CRT display system lowers the dot clock frequency to reduce one line of data to 320 dots. If such data is supplied to the LCD system of 640 horizontal dots as-is, the entire display will be placed on the left section of the panel with the right half blank. To accommodate this situation, the CLINE doubles the width of the low-resolution display. This function is enabled by the SP/WR/A4 pin in pin programming method or the SP bit (bit 1) of the control register (R0) in internal register programming method (table 7). In either method, for VGA display systems, the CLINE detects low-resolution display mode and automatically enables double-width display.

| Programming Method                 | CRT System Mode | Setting                 |

|------------------------------------|-----------------|-------------------------|

| Pin: SP                            | VGA             | Automatic               |

|                                    | Non-VGA         | 0: Normal display       |

|                                    |                 | 1: Double-width display |

| Internal register:                 | VGA             | Automatic               |

| Control register bit 1<br>(SP bit) | Non-VGA         | 0: Normal display       |

|                                    |                 | 1: Double-width display |

#### Table 7Double-Width Display Usage

#### Stretching and Centering Display

When the display size differs from the LCD panel size, data will be displayed on the upper-left section of the LCD panel with blank space to the right and/or below if no countermeasures are taken. To provide a user-friendly display, the CLINE can stretch a display to fill out the panel or center a display. Both stretching and centering functions are enabled by control register (R0) bits 2, 3, and 4.

Note that stretching and centering functions are available only in a system where buffer memory is used. This is because these functions are realized through adjustment of memory access. Similarly, stretching and centering functions are unavailable in non-VGA modes when the CLINE is controlled by the pin programming method. Simultaneous use of the vertical centering and stretching functions is also impossible.

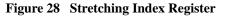

In the internal register programming method, horizontal centering function is controlled by the centering character register (R6) within the range of 1 to 32 characters (8 to 256 dots), while vertical centering function is controlled by the centering raster register (R5) within the range of 1 to 256 lines. Stretching function is controlled by the stretching control register (R8) and the stretching index register (R9 and R10) so as to double the vertical display size at most.

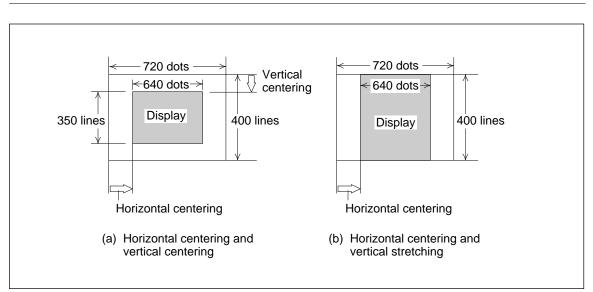

Figure 3 shows display examples using stretching/ centering functions. In these examples, a display of  $640 \text{ dots} \times 350 \text{ lines}$  is displayed on an LCD panel of  $720 \text{ dots} \times 400 \text{ lines}$ , using stretching/centering functions.

For VGA modes, in both internal register programming and pin programming methods, necessary parameters are automatically calculated from the relationship between display size and the LCD panel size and set in the appropriate registers. Consequently, there is no need to account for display size.

However, the vertical centering or stretching function can be selected in the internal register programming method. (In pin programming method, the stretching function is automatically selected.) Table 8 describes the use of the stretching and centering function.

Figure 3 Display Examples Using Stretching/Centering Functions

| Table 8    | Stretching and Ce     | ntering Function U | Jsage                      |              |

|------------|-----------------------|--------------------|----------------------------|--------------|

| Direction  | Programming<br>Method | CRT System<br>Mode | Display Arranging Function | Setting      |

| Vertical   | Pin                   | VGA                | Stretching                 | Automatic    |

|            |                       | Non-VGA            | None                       | *1           |

|            | Internal register     | VGA                | Stretching or centering    | Automatic *2 |

|            |                       | Non-VGA            | Stretching or centering    | Necessary    |

| Horizontal | Pin                   | VGA                | Centering                  | Automatic    |

|            |                       | Non-VGA            | None                       | *1           |

|            | Internal register     | VGA                | Centering                  | Automatic    |

|            |                       | Non-VGA            | Centering                  | Necessary    |

Notes: 1. Display size must be LCD panel size.

2. Either stretching or centering function must be selected by the internal register.

#### **Display Modes**

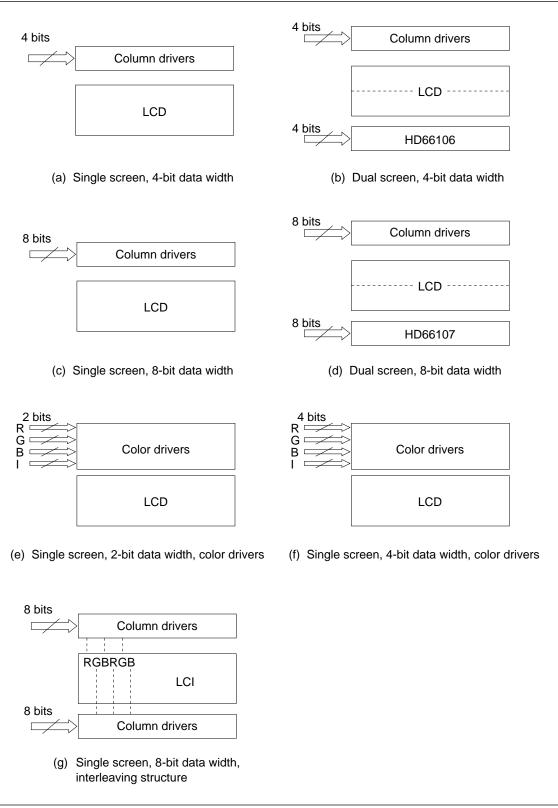

**Display Mode Settings and LCD Module Configurations:** The CLINE supports 20 display modes, depending on the settings of the LMODE4 to LMODE0 pins. The display mode includes display color mode (color or monochrome), screen configuration (single or dual), gradation display method, and width of data transfer to LCD drivers. Table 9 lists the display modes and figures 4 (a) to 4 (g) show the corresponding LCD module configurations.

#### Table 9 Display Modes and LCD Module Configurations

| Mode |   | Pi | n: LN | IODE |   | Display Color Mode           | Screen  | Data  | LCD Module |

|------|---|----|-------|------|---|------------------------------|---------|-------|------------|

| No.  | 4 | 3  | 2     | 1    | 0 | (Gradation Display Method)   | Config. | Width | Config.    |

| 1    | 0 | 0  | 0     | 0    | 0 | Monochrome: black and white  | Single  | 4     | Fig. 4 (a) |

| 2    | 0 | 0  | 0     | 0    | 1 |                              | Dual    | 4     | Fig. 4 (b) |

| 3    | 0 | 0  | 0     | 1    | 0 |                              | Single  | 8     | Fig. 4 (c) |

| 4    | 0 | 0  | 0     | 1    | 1 |                              | Dual    | 8     | Fig. 4 (d) |

| 5    | 0 | 0  | 1     | 0    | 0 | Monochrome: 16 gray levels   | Single  | 4     | Fig. 4 (a) |

| 6    | 0 | 0  | 1     | 0    | 1 | (Frame-based data thinning)  | Dual    | 4     | Fig. 4 (b) |

| 7    | 0 | 0  | 1     | 1    | 0 |                              | Single  | 8     | Fig. 4 (c) |

| 8    | 0 | 0  | 1     | 1    | 1 |                              | Dual    | 8     | Fig. 4 (d) |

| 9    | 0 | 1  | 0     | 0    | 0 | Monochrome: 16 gray levels   | Single  | 4     | Fig. 4 (a) |

| 10   | 0 | 1  | 0     | 0    | 1 | (1/2 pulse width modulation) | Dual    | 4     | Fig. 4 (b) |

| 11   | 0 | 1  | 0     | 1    | 0 |                              | Single  | 8     | Fig. 4 (c) |

| 12   | 0 | 1  | 0     | 1    | 1 |                              | Dual    | 8     | Fig. 4 (d) |

| 13   | 1 | 0  | 0     | 0    | 0 | 16 colors                    | Single  | 2     | Fig. 4 (e) |

| 14   | 1 | 0  | 0     | 1    | 0 |                              | Single  | 4     | Fig. 4 (f) |

| 15   | 1 | 0  | 0     | 1    | 1 | 8 colors                     | Single  | 8     | Fig. 4 (g) |

| 16   | 1 | 0  | 1     | 0    | 0 | 4096 color                   | Single  | 2     | Fig. 4 (e) |

| 17   | 1 | 0  | 1     | 1    | 0 | (Frame-based data thinning)  | Single  | 4     | Fig. 4 (f) |

| 18   | 1 | 0  | 1     | 1    | 1 |                              | Single  | 8     | Fig. 4 (g) |

| 19   | 1 | 1  | 0     | 1    | 0 | 4096 color                   | Single  | 4     | Fig. 4 (f) |

| 20   | 1 | 1  | 0     | 1    | 1 | (1/2 pulse width modulation) | Single  | 8     | Fig. 4 (g) |

Note: Modes 15, 18, and 20 are interleaving structure modes.

Figure 4 LCD Module Configurations by Display Modes

**Gradation Level Reduction**: Although a CRT display system can represent information for over 100,000 color levels, an LCD cannot handle so much information.

Consequently, CRT color or gradation level information must be reduced in order for the CLINE to display it. Reduction methods vary depending on the input color or gradation level information, the LCD panel (color or monochrome), and other factors. Table 10 lists gradation level reduction for CLINE modes, where "Input Bits" indicates CRT display color data and "Reduced Data" indicates input to the gradation level palettes.

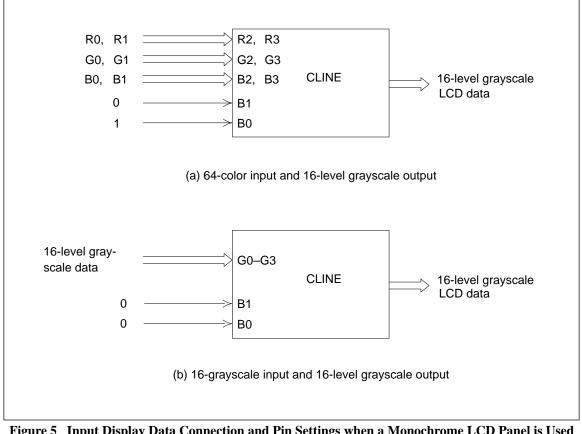

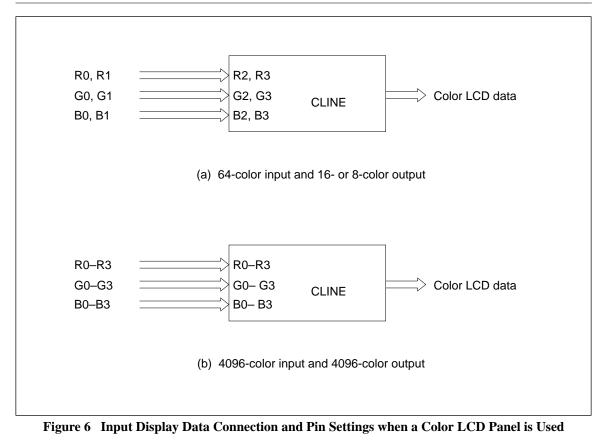

**Input Display Data Connection**: Input display data connection and pin settings depend on the CRT input mode (color or gradation level information) and the LCD panel used.

- When monochrome LCD panel is used (LMODE4 = 0)

- 64-color input and 16-level grayscale output (modes 5-12)

The B0 pin must be set to 1, and the B1 pin to 0. Unused display data input pins must be fixed to 0. See figure 5 (a).

16-level grayscale input and 16-level grayscale output (modes 5-12)

Both B0 and B1 pins must be set to 0. Unused display data input pins must be fixed to 0. See figure 5 (b).

- When color LCD panel is used (LMODE4 = 1)

- 64-color input and 16- or 8-color output (modes13-15)

Two-bit R, G, and B data must be input to the R2-R3, G2-G3, and B2-B3 pins, respectively. Unused display data input pins must be fixed to 0). See figure 6 (a).

— 4096-color input and 4096-color output (modes 16-20)

Four-bit R, G, and B data must be input to the R0-R3, G0-G3, and B0-B3 pins, respectively. If the input has more than 4096 colors, use the high-order four bits of each color. See figure 6 (b).

#### Table 10 Gradation Level Reduction for CLINE Display Modes

| Input             | In | put E | Bits | CLINE Display                 | Re    | educe  | d Da  | ta | LCD        | Gradation Level     |

|-------------------|----|-------|------|-------------------------------|-------|--------|-------|----|------------|---------------------|

| Mode              | R  | G     | В    | Mode                          | 3     | 2      | 1     | 0  | Panel      | Reduction (Bits)    |

| 4096<br>colors    | 4  | 4     | 4    | 4096 color<br>levels          | D3    | D2     | D1    | D0 | Color      | $12 \rightarrow 12$ |

| 64<br>colors      | 2  | 2     | 2    | 16 colors                     | R     | G      | В     | I  | Color      | $6 \rightarrow 4$   |

| 64<br>colors      | 2  | 2     | 2    | 16 gray levels                | D3    | D2     | D1    | D0 | Monochrome | $6 \rightarrow 4$   |

| 16 gray<br>levels | _  | 4     | —    | 16 gray levels                | D3    | D2     | D1    | D0 | Monochrome | $4 \rightarrow 4$   |

| 16 gray<br>levels | —  | 4     | —    | Monochrome<br>(black & white) | All 0 | s or a | ll 1s |    | Monochrome | $4 \rightarrow 1$   |

Figure 5 Input Display Data Connection and Pin Settings when a Monochrome LCD Panel is Used

B5

G4

R3

B3

G2

R1

B1

G0

R4

B4

G3

R2

B2

G1

R0

B0

R6

B6

G5

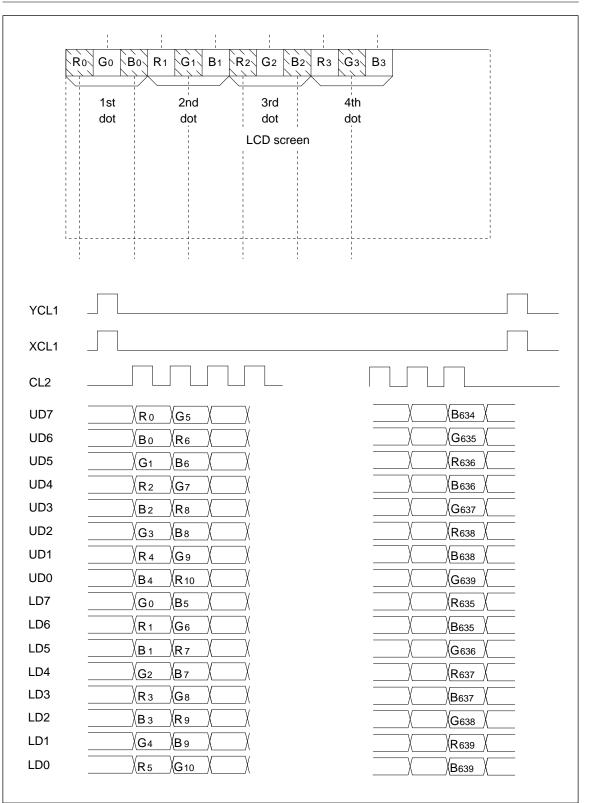

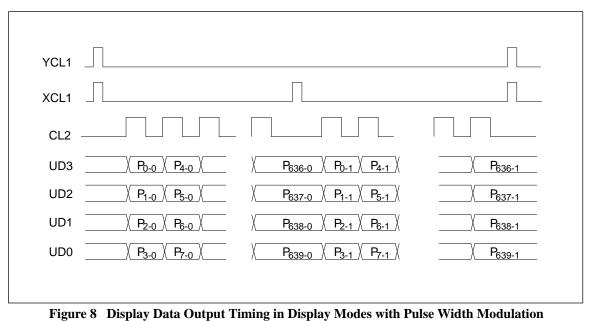

LCD Data Output: The CLINE uses pins UD7-UD0 and LD7-LD0 for display data output. Output data from these pins depend on the display mode, as shown in table 11. However, data output timings are basically the same in all display modes. Display data output timing for modes 15 and 18 (8bit color data transfer, bidirectional connection, without pulse width modulation) is shown in figure 7. Display data output timing for the LCD display

modes with pulse width modulation is slightly different. This type of example is shown in figure 8. Figure 8 shows the display data output timing in mode 10 (1/2 pulse width modulation, 4-bit monochrome data transfer, and dual screen configuration).

However, LCD lower panel data LD3-LD0 are not shown in the figure.

#### **Monochrome Modes** 4-Bit/ 4-Bit/ 8-Bit/ 8-Bit/ **Color Modes** Single Dual Single Dual Pin Screen Screen Screen Screen 4-Bit 8-Bit 2-Bit UD7 D7 UD7 R3 R15 G10 UD6 D6 UD6 R2 B15 R9 \_ \_\_\_\_ UD5 D5 UD5 R1 R1 G14 B9 UD4 R13 UD4 D4 R0 G8 **R**0 UD3 D3 UD3 D3 UD3 \_\_\_\_ G3 B13 R7 G2 G12 UD2 D2 UD2 D2 UD2 B7 UD1 D1 UD1 D1 UD1 G1 G1 R11 G6 UD0 UD0 D0 UD0 D0 G0 G0 B11 R5 LD7 LD7 B3 G15 B10 B2 LD6 R14 G9 LD6 LD5 LD5 B1 Β1 B14 R8 \_ \_ \_ LD4 LD4 B0 B0 G13 B8 LD3 LD3 LD3 (13)R12 G7

#### Table 11 LCD Data Output Pins and Display Data by Display Modes

LD0 Notes: 1. The left bit corresponds to MSB.

LD2

LD1

LD2

LD1

LD0

\_

\_\_\_\_

2. U and L indicate upper panel and lower panel data, respectively.

LD2

LD1

LD0

3. Data in parentheses are for 16-color display.

\_\_\_\_

\_\_\_\_

4. — indicates that the corresponding pins are not used; must be left disconnected.

\_\_\_\_

(11)

(10)

(12)

(11)

(10)

B12

G11

R10

Figure 7 Display Data Output Timing in Display Modes without Pulse Width Modulation (Modes 15 and 18)

In figure 8, data P0–0, P4–0, ... P636–0 make up the first set of data for one line to be output to LCD drivers via pin UD3. Likewise, data P0–1, P4–1, ... P636–1 make up the second set of data. The combination of the first and second sets of data

determines the display status as follows: (first data, second data) = (0, 0): display off; (1, 0): 1/2 pulse width modulation; and (1, 1): display on. For more details, refer to the Gradation Display Methods section.

(Mode 10)

#### **Gradation Display Methods**

The CLINE supports the frame-based data thinning method and pulse width modulation method for gradation display.

**Frame-Based Data Thinning Method**: In the frame-based data thinning method, the CLINE thins out the display data in line or dot units in the specified frames.

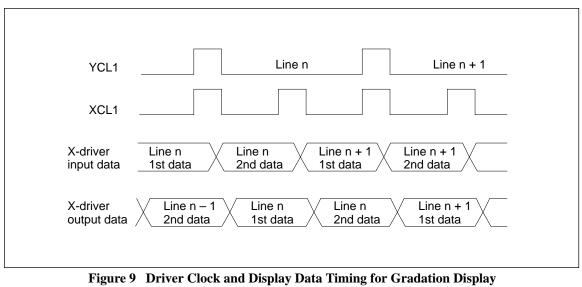

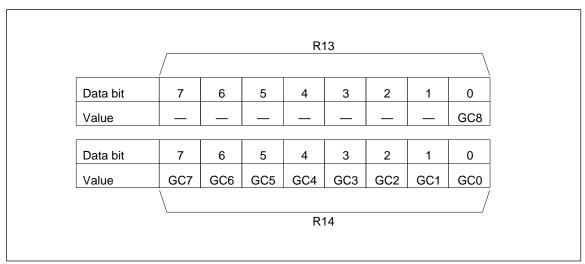

**Pulse Width Modulation Method**: In the pulse width modulation method, the CLINE combines 1/2 pulse width modulation and frame-based data thinning. In this case, data is output from X-drivers twice in one line-selection period (figure 9).

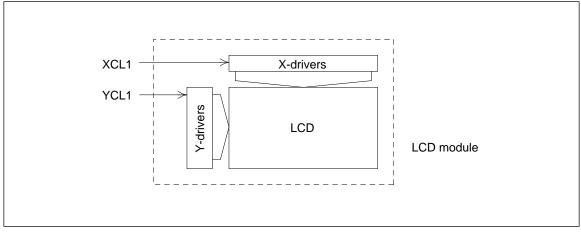

Consequently, the X-driver latch clock must be different from the Y-driver shift clock, and a conventional LCD module configuration cannot be used. Therefore, clock XCL1 must be supplied to X-drivers and clock YCL1 to Y-drivers (figure 10).

The XCL1 period is specified by the gradation display clock period register (R13 and R14) when no buffer memory is used in non-VGA modes and in the internal register programming method. (Pulse width modulation is unavailable when buffer memory is not used in non-VGA modes, pin programming method.) In the other cases, the register is automatically set, since the YCL1 period is fixed (table 12).

with 1/2 Pulse Width Modulation

#### XCL1 Period **Memory Mode** Setting Automatic With-memory Half of YCL1 period for 1/2 pulse with modulation method VGA Half of YCL1 period for 1/2 pulse width Without-memory Automatic modulation method (See note below) Non-VGA Internal register Conforms to gradation display clock Required (R13, R14) register (R13, R14) settings programming Pin programming

Table 12

**XCL1 Period Setting**

Note: Total number of horizontal dots must be 400, 450, 800, or 900 for displaying 320, 360, 640, or 720 dots, respectively.

Figure 10 X- and Y-Driver Clock Connection for Pulse Width Modulation Method

#### **Gradation Level Palettes**

Gradation display quality depends greatly on LCD panel characteristics.

Consequently, uniform gradation display may be impossible for some panels. To accommodate this situation, the CLINE incorporates a set of gradation level palettes that can assign any gradation level to any CRT display color as desired.

16 levels are available for gradation display using the frame-based data thinning method and 31 levels using 1/2 pulse width modulation method. Appropriate levels can be selected for the LCD panel used.

The R-, G-, and B-palettes are used for color level display modes, while only the R-palette is used for 16-level grayscale display modes.

In pin programming and MPU programming methods, these palettes are automatically loaded after reset with appropriate data for frame-based data thinning modes and 1/2 pulse width modulation modes. The automatically set data cannot be rewritten in the pin programming method, but can be rewritten, any time after 100 µs have elapsed after reset, in MPU programming method.

By contrast, in the ROM programming method, these palettes are not automatically set. Thus writing the necessary data to the palettes is always required.

Table 13 shows the relationship between the values set in the palettes (through R12) and gradation levels. Values other than those shown here disable correct display.

#### Table 13 Relationship between Gradation Levels and Palette (R12) Values

#### (a) Frame-based data thinning modes

| Grada-<br>tion |          |             |              |            |            |           | Grada-        |

|----------------|----------|-------------|--------------|------------|------------|-----------|---------------|

| Level<br>No.   | Pal<br>5 | ette D<br>4 | )ata (l<br>3 | R12 D<br>2 | ata B<br>1 | its)<br>0 | tion<br>Level |

| 0              | 1        | 0           | 0            | 0          | 0          | 0         | 0.00          |

| 1              | 1        | 0           | 0            | 0          | 0          | 1         | 0.14          |

| 2              | 1        | 0           | 0            | 0          | 1          | 0         | 0.20          |

| 3              | 1        | 0           | 0            | 0          | 1          | 1         | 0.29          |

| 4              | 1        | 0           | 0            | 1          | 0          | 0         | 0.33          |

| 5              | 1        | 0           | 0            | 1          | 0          | 1         | 0.40          |

| 6              | 1        | 0           | 0            | 1          | 1          | 0         | 0.43          |

| 7              | 1        | 0           | 0            | 1          | 1          | 1         | 0.50          |

| 8              | 1        | 0           | 1            | 0          | 0          | 0         | 0.57          |

| 9              | 1        | 0           | 1            | 0          | 0          | 1         | 0.60          |

| 10             | 1        | 0           | 1            | 0          | 1          | 0         | 0.66          |

| 11             | 1        | 0           | 1            | 0          | 1          | 1         | 0.71          |

| 12             | 1        | 0           | 1            | 1          | 0          | 0         | 0.75          |

| 13             | 1        | 0           | 1            | 1          | 0          | 1         | 0.80          |

| 14             | 1        | 0           | 1            | 1          | 1          | 0         | 0.86          |

| 15             | 1        | 0           | 1            | 1          | 1          | 1         | 1.00          |

#### (b) 1/2 pulse width modulation modes

| Grada-<br>tion<br>Level<br>No. | Pal<br>5 | ette D | Data (I<br>3 | R12 D<br>2 | ata B | its)<br>0 | Grada-<br>tion<br>Level |

|--------------------------------|----------|--------|--------------|------------|-------|-----------|-------------------------|

| 0                              | 0        | 1      | 0            | 0          | 0     | 0         | 0.00                    |

| 1                              | 0        | 1      | 0            | 0          | 0     | 1         | 0.07                    |

| 2                              | 0        | 1      | 0            | 0          | 1     | 0         | 0.10                    |

| 3                              | 0        | 1      | 0            | 0          | 1     | 1         | 0.14                    |

| 4                              | 0        | 1      | 0            | 1          | 0     | 0         | 0.17                    |

| 5                              | 0        | 1      | 0            | 1          | 0     | 1         | 0.20                    |

| 6                              | 0        | 1      | 0            | 1          | 1     | 0         | 0.21                    |

| 7                              | 0        | 1      | 0            | 1          | 1     | 1         | 0.25                    |

| 8                              | 0        | 1      | 1            | 0          | 0     | 0         | 0.29                    |

| 9                              | 0        | 1      | 1            | 0          | 0     | 1         | 0.30                    |

| 10                             | 0        | 1      | 1            | 0          | 1     | 0         | 0.33                    |

| 11                             | 0        | 1      | 1            | 0          | 1     | 1         | 0.36                    |

| 12                             | 0        | 1      | 1            | 1          | 0     | 0         | 0.38                    |

| 13                             | 0        | 1      | 1            | 1          | 0     | 1         | 0.40                    |

| 14                             | 0        | 1      | 1            | 1          | 1     | 0         | 0.43                    |

| 15                             | 0        | 1      | 1            | 1          | 1     | 1         | 0.50                    |

| 16                             | 1        | 1      | 0            | 0          | 0     | 0         | 0.50                    |

| 17                             | 1        | 1      | 0            | 0          | 0     | 1         | 0.57                    |

| 18                             | 1        | 1      | 0            | 0          | 1     | 0         | 0.60                    |

| 19                             | 1        | 1      | 0            | 0          | 1     | 1         | 0.64                    |

| 20                             | 1        | 1      | 0            | 1          | 0     | 0         | 0.67                    |

| 21                             | 1        | 1      | 0            | 1          | 0     | 1         | 0.70                    |

| 22                             | 1        | 1      | 0            | 1          | 1     | 0         | 0.71                    |

| 23                             | 1        | 1      | 0            | 1          | 1     | 1         | 0.75                    |

| 24                             | 1        | 1      | 1            | 0          | 0     | 0         | 0.79                    |

| 25                             | 1        | 1      | 1            | 0          | 0     | 1         | 0.80                    |

| 26                             | 1        | 1      | 1            | 0          | 1     | 0         | 0.83                    |

| 27                             | 1        | 1      | 1            | 0          | 1     | 1         | 0.86                    |

| 28                             | 1        | 1      | 1            | 1          | 0     | 0         | 0.88                    |

| 29                             | 1        | 1      | 1            | 1          | 0     | 1         | 0.90                    |

| 30                             | 1        | 1      | 1            | 1          | 1     | 0         | 0.93                    |

| 31                             | 1        | 1      | 1            | 1          | 1     | 1         | 1.00                    |

|                                |          |        |              |            |       |           |                         |

#### **Display On/Off Control**

When the LCD drivers used have an LCD on/off control pin, display can be controlled with the CLINE DISPON signal. When the LCD drivers used do not have an LCD on/off control pin, the CLINE can turn off display by transferring all-0 display data to the drivers.

Display will be turned on with the DISPON pin = 1, turns the display off while DISPON = 0. The DISPON pin is equivalent to the DISPON bit (bit 0) of the control register.

In the pin programming method, display is on except for four frames after reset. The four frame display-off time period prevents random display at power-on. In the MPU programming method, display is turned off at reset, but can be freely turned on or off after four frames after reset by rewriting the corresponding register bit. In the ROM programming method, a 1 must be written to the DISPON bit to turn on display. Like in other programming methods, display is off for four frames after reset.

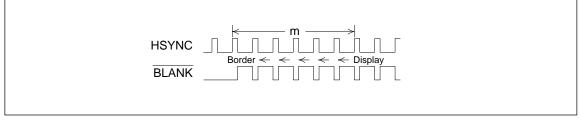

#### LDOTCK Frequency and Data Transfer Rate

The LDOTCK frequency  $(f_{LDOTCK})$  for asynchronous mode is calculated from the following equation:

$f_{LDOTCK} = (Nhd + 48) \times Nvd \times f_F$

- Nhd: Number of dots contained in one horizontal line of the LCD panel

- Nvd: Number of horizontal lines from the LCD panel top to bottom

- f<sub>F</sub>: Frame frequency

In this case, the following relationship must hold true:

$1/2 \times f_{DOTCLK} < f_{LDOTCK} < 2 \times f_{DOTCLK}$

f<sub>DOTCLK</sub>: Dot clock frequency

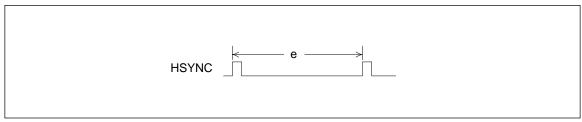

The data transfer rate to LCD drivers depends on the mode in which the CLINE is used. Specifically, the rate depends on screen configura-tion (single or dual), data transfer width (bit count), and gradation display methods. For example, the data transfer rate will be doubled for 1/2 pulse width gradation display. This is because data must be transferred two times during one line-selection period. The data transfer rate ( $f_{CL2}$ : CL2 frequency) is calculated from the following equation ( $f_{LDOTCK} = f_{DOTCLK}$  for synchronous mode):

$$f_{CL2} = \frac{f_{LDOTCK} \times I}{n \times m}$$

- n: Number of panels composing one screen

- 1 for modes 1, 3, 5, 7, 9, 11, 13-20

- 2 for modes 2, 4, 6, 8, 10, 12

m: Number of bits transferred at one time

- 2 for modes 13, 16

- 4 for modes 1, 2, 5, 6, 9, 10, 14, 15, 17-20

1: Constant for each gradation display

- 1 for modes 1-8, 13-18

- 2 for modes 9-12, 19, 20

# Synchronous/Asynchronous Modes and Memory

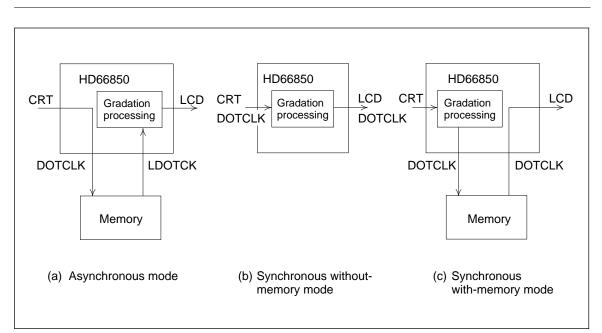

The CLINE has two timing modes: asynchronous and synchronous.

In asynchronous mode, dot clock pulses for the CRT system (DOTCLK) are different from those for the LCD system (LDOTCK) in frequency to accommodate frame frequency conversion. This requires buffer memory as shown in figure 11 (a). In this mode, dual screen LCD panels can be used.

In synchronous mode, dot clock pulses for the CRT system are identical to those for the LCD system, thus requiring no buffer memory in principle (synchronous without-memory mode (figure 11 (b)). However, synchronous without-memory mode cannot support dual screen LCD panels. The CLINE has another mode in which dual screen LCD panels can be used and fewer memory devices are required. This is called "synchronous with-memory mode" (figure 11 (c)). In this mode, the number of memory devices can be reduced to a half or a third that of asynchronous mode. This is because RGB data sent from the CRT system is processed for gradation display before being written into buffer memory. (In asynchronous mode, on the other hand, R, G, and B data sent from the CRT system is separately written into the G-plane, B-plane R-plane, and memories, respectively.)

Table 14 summarizes these modes.

Figure 11 Signal Flow for Synchronous/Asynchronous With-/Without-Memory Modes

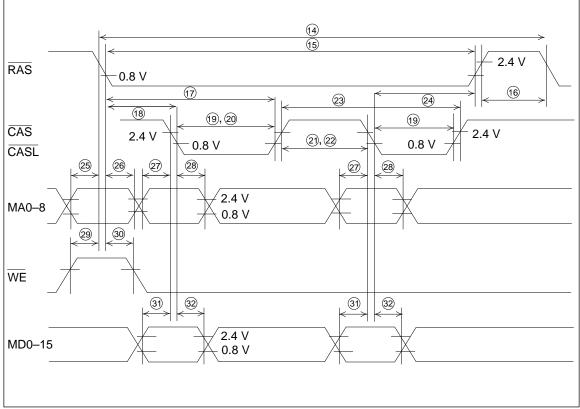

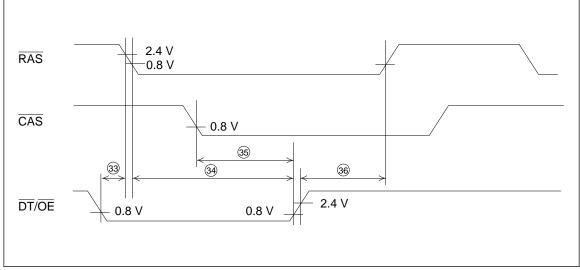

The CLINE uses dual port RAMs for buffer memory, enabling high-speed display and independent use of an LCD dot clock and a CRT dot clock.

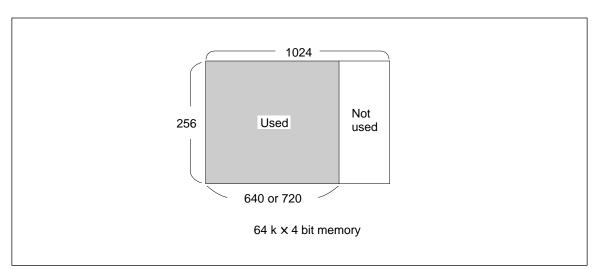

The CLINE supports three types of memory configurations:  $64 \text{ k} \times 4$  bits (256 k), 256 k  $\times 4$  bits (1 M), and 128 k  $\times 8$  bits (1 M), any of which can be selected with the MMODE0 and MMODE1 pins (table 3).

The number of memory devices required depends on the LCD panel size and the display mode. However, it depends only on LCD panel vertical size and not on horizontal size since the CLINE uses memory as shown in figure 12. For example, one 256-kbit memory device is required for the panel having 256 or less lines and two for that having 257 to 512 lines. Table 15 lists the number of memory devices required for each mode.

|                             | Asynchronous With-<br>Memory Mode | Synchronous With-<br>Memory Mode | Synchronous Without<br>Memory Mode |

|-----------------------------|-----------------------------------|----------------------------------|------------------------------------|

| Centering/stretching        | Possible                          | Possible                         | Impossible                         |

| Max number of gray levels   | 16                                | 16                               | 16                                 |

| Max number of color levels  | 16                                | 4096 (frame-based data thinning) | 4096 (pulse width modulation)      |

| Dual screen                 | Possible                          | Possible                         | Impossible                         |

| Max number of display lines | 512                               | 512                              | 1024                               |

| Frame frequency conversion  | Possible                          | Impossible                       | Impossible                         |

#### Table 14Memory Mode Summary

Figure 12 Display Sizes and Memory Area Used

|                                                       |          | N          | umber of Me | mory Devices | s Required |           |

|-------------------------------------------------------|----------|------------|-------------|--------------|------------|-----------|

|                                                       |          | Asynchrono | us          |              | Synchrono  | us        |

| Display Mode                                          | 64 k × 4 | 256 k × 4  | 128 k × 8   | 64 k × 4     | 256 k × 4  | 128 k × 8 |

| Monochrome<br>Modes 1–4                               | 2        | 1          | 1           | 2            | 1          | 1         |

| 16-level grayscale<br>(frame-based)<br>Modes 5–8      | 8        | 4          | 2           | 2            | 1          | 1         |

| 16-level grayscale<br>(1/2 pulse width)<br>Modes 9–12 | 8        | 4          | 2           | 4            | 2          | 1         |

| 8-color Mode 15                                       | 6        | 3          | 2           | 6            | 3          | 2         |

| 16-color Modes 13, 14                                 | 8        | 4          | 2           | 8            | 4          | 2         |

| 4096-color-scale<br>(frame-based)<br>Modes 16–18      | _        | _          | _           | 6            | 3          | 2         |

#### Table 15 Number of Memory Devices for Different Display modes

Number of Memory Devices Required

Frame-based: Frame-based data thinning method 1/2 pulse width: 1/2 pulse width modulation method

Note: With-memory mode does not support color level display using the pulse width modulation method.

#### **Display Timing Signal Fine Adjustment**

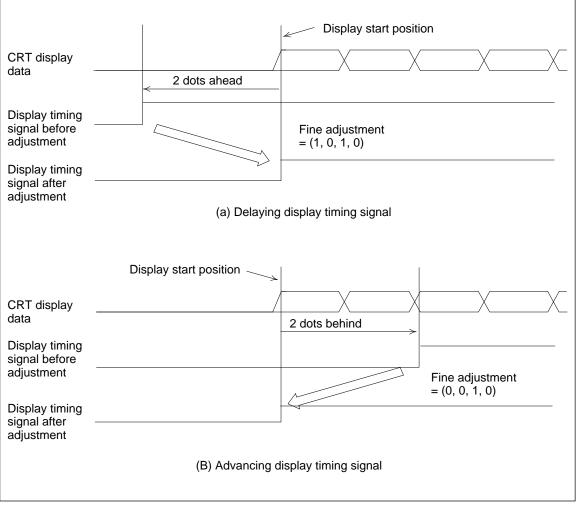

When the display timing signal is supplied externally, a phase shift may appear between CRT data and the display timing signal, since each signal has its own peculiar lag. The CLINE can adjust the display timing signal with pins AJ3–AJ0 (in pin programming method) or with the input timing control register (R1) (in internal register programming method) to compensate the phase shift (table 1).

Figure 13 (a) shows an example of adjusting a display timing signal that is two dots ahead of the display start position. In this case, pins (AJ3, AJ2, AJ1, AJ0) or data bits (3, 2, 1, 0) of R1 must be set

to (1, 0, 1, 0) to delay the signal for two dots. Conversely, they must be set to (0, 0, 1, 0) to advance the signal for two dots for the case of figure 13 (b), where the display timing signal is two dots behind.

When there is no need to adjust the signal, a setting of either (0, 0, 0, 0) or (1, 0, 0, 0) will work.

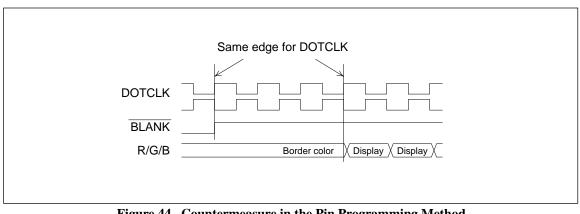

It should be noted that the VGA CRT system applies the BLANK signal, which includes the border area period, as the display timing signal, and that the CLINE removes the border area period. Consequently, the border area period must be considered for adjusting the display timing signal.

Figure 13 Display Timing Signal Fine Adjustment

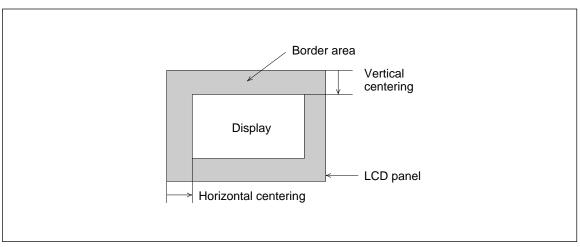

#### **Border Color Control**

In the internal register programming method, the CLINE can specify the color of a blank area that is left on a centered display (figure 14). Any of 16 colors or the color of the dot immediately before the valid display data can be specified by the

border color control register (R7). However, the desired color can be specified only in asynchronous mode.

In the pin programming method, the specified color is always the same color as the dot immediately before the valid display data.

Figure 14 Border Area and an LCD Panel

#### **Internal Registers**

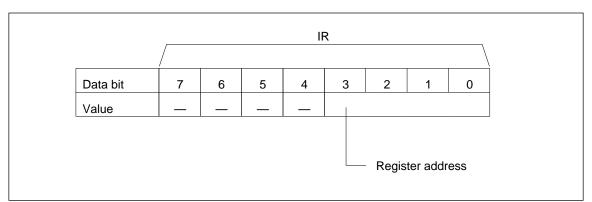

The CLINE has one index register (IR) and 15 data registers (R0–R14). In the MPU programming method, the desired register address must be written in one cycle into the index register before writing or reading data to/from the register in the following cycle. By contrast, in the ROM programming method, the index register is not used; the CLINE automatically reads data from the ROM, in which data has been written to the ROM addresses corresponding to the desired data registers, and writes it to the data register.

Registers are valid only for the internal register programming method and are invalid (don't care) for the pin programming method. Since all data registers are reset to 0s, they must be rewritten after reset.

#### **Register Access for MPU Programming Method**

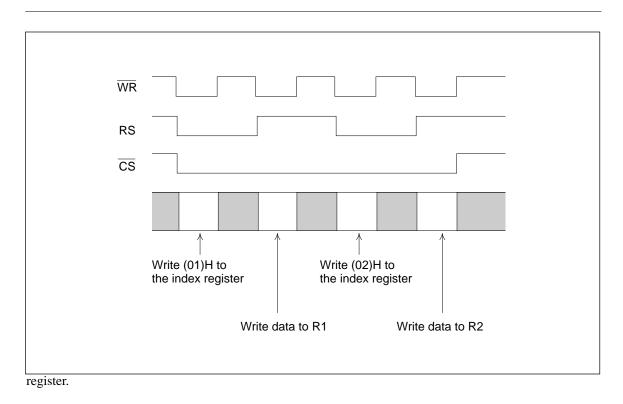

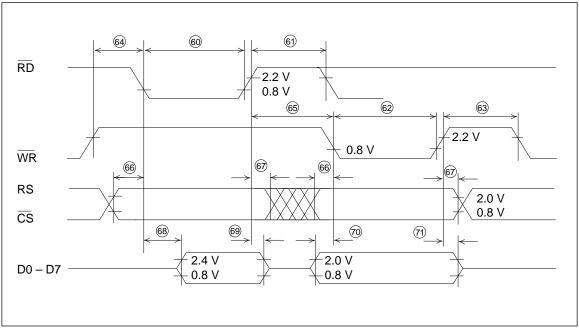

First write the desired data register address into the index register with  $\overline{CS} = 0$ , RS = 0, and  $\overline{WR} = 0$ , then write/read data to/from the register with  $\overline{CS} = 0$ , RS = 1, and  $\overline{WR} = 0$  or  $\overline{RD} = 0$ . Figure 15 shows the timing for writing data into an internal

Figure 15 Internal Register Write by MPU

# ROM Data Setting for ROM Programming Method

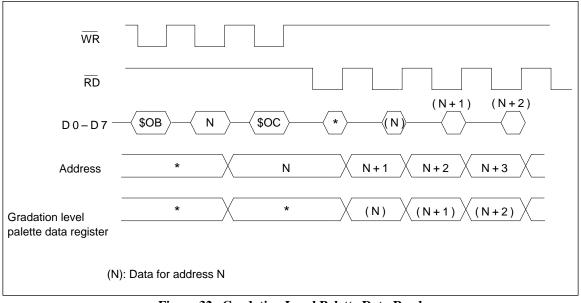

The desired data must have been previously written to the ROM addresses corresponding to the data register addresses; that is, to ROM addresses \$0000–\$000F. Data for the gradation level palettes must have been written to ROM addresses \$0010-\$003F. Consequently, data written for internal registers R11 and R12 are invalid. Figure 16 shows the ROM address map.

| \$0000 | Data for R0          | Internal registers |

|--------|----------------------|--------------------|

| \$0001 | Data for R1          |                    |

| \$0002 | Data for R2          | _                  |

|        | :                    |                    |

| \$0010 | Data for R-palette 0 | R-palettes         |

| \$0011 | Data for R-palette 1 | _                  |

|        | ÷                    |                    |

| \$0020 | Data for G-palette 0 | G-palettes         |

| \$0021 | Data for G-palette 1 |                    |

|        | ÷                    |                    |

| \$0030 | Data for B-palette 0 | B-palettes         |

| \$0031 | Data for B-palette 1 |                    |

|        | ÷                    |                    |

| \$0040 |                      | Not used           |

|        |                      |                    |

| \$FFFF |                      |                    |

#### **Register Function**

Index Register (IR): The index register (figure 17), composed of four valid bits, selects one of the 15 data registers. The index register itself is selected by the MPU while the RS signal is low and selects a data register with the register address written.

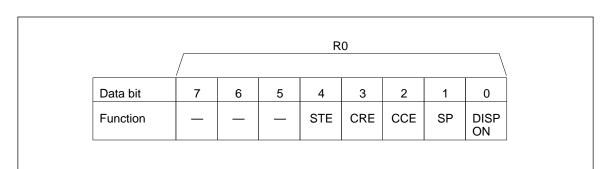

Control Register (R0): The control register (figure 18) is composed of five valid bits, each with a particular function.

- STE bit

- STE = 1: Stretching function enabled

- STE = 0: Stretching function disabled

- CRE bit

- CRE = 1: Vertical centering function enabled

- CRE = 0: Vertical centering function disabled

Simultaneous use of stretching and vertical centering functions is impossible; if both the CRE and STE bits are set to 1 at the same time, correct display will be disabled.

- CCE bit

- CCE = 1: Horizontal centering function enabled

- CCE = 0: Horizontal entering function disabled

- SP bit

- SP = 1: Double-width display

- SP = 0: Normal display

- DISPON bit

- DISPON = 1: Display on

- DISPON = 0: Display off

DISPON is always cleared at reset. In the MPU programming method, rewriting this bit can always be rewritten. However, display will be off for four frames after reset, regardless of the status of this bit.

Figure 18 Control Register

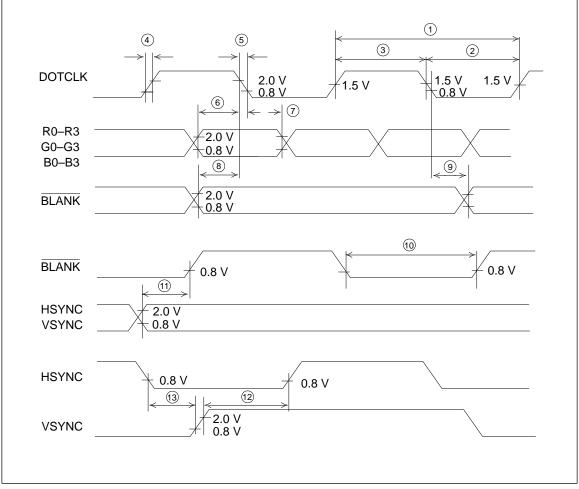

**Input Timing Control Register:** The input timing control register (figure 19) has five valid bits, having two different functions.

- DOTE bit : Switches RGB data latch timing.

- DOTE = 1: Latches data at the rising edge of the dot clock pulses

- DOTE = 0: Latches data at the falling edge of the dot clock pulses

- AJ3-AJ0 bits: Adjust the externally supplied display timing signal to synchronize its phase with that of LCD data. Write the shift, represented in dots, between the display timing signal and the display start position to these bits. The absolute value of the number of dots to be shifted must be written to the AJ2-AJ0 bits and shift polarity to the AJ3 bit. If there is no need to adjust the display timing signal, these bits may be set to either (1, 0, 0, 0) or (0, 0, 0, 0).

Figure 19 Input Timing Control Register

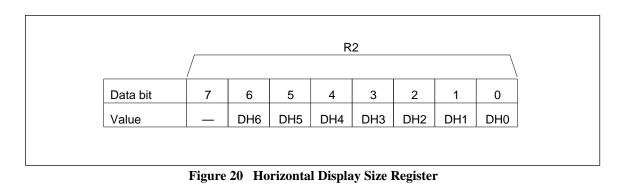

**Horizontal Display Size Register:** The horizontal display size register (figure 20), composed of seven valid bits, specifies the horizontal display size in units of characters (eight dots). The value to write to this register is "number of characters displayed on one horizontal line – 1." A maximum of 90 characters (720 dots) can be specified.

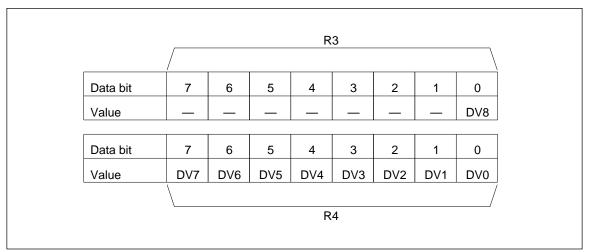

**Vertical Display Size Register:** The vertical display size register (figure 21), composed of nine valid bits, specifies the vertical display size in units of lines. The value to write to this register is "number of lines displayed from display screen top to bottom -1." A maximum of 512 lines can be specified.

This register is set automatically in VGA mode.

Figure 21 Vertical Display Size Register

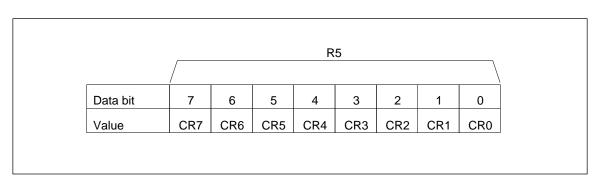

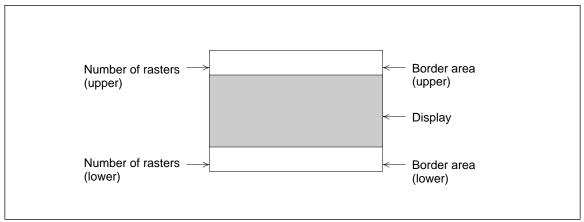

**Centering Raster Register:** The centering raster register (figure 22), composed of eight bits, specifies the number of rasters for vertically centering the display within the range of 1 to 256. The value to write to this register is "number of rasters for centering -1." As shown in figure 23, the number here indicates the number of rasters in either the upper border area or lower border area, not