### 54F/74F384 8-Bit Serial/Parallel Twos Complement Multiplier

#### **General Description**

The 'F384 is an 8-bit by 1-bit sequential logic element that multiplies two numbers represented in twos complement notation. The device implements Booth's algorithm internally to produce a twos complement product that needs no subsequent correction. Parallel inputs accept and store an 8-bit multiplicand ( $X_0-X_7$ ). The multiplier word is then applied to the Y input in a serial bit stream, least significant bit first. The product is clocked out at the SP output, least significant bit first.

The K input is used for expansion to longer X words, using two or more 'F384 devices by connecting the output (SP) of one device to the K input of the other device. The Mode Control (M) input is used to establish the most significant

device. An asynchronous Parallel Load ( $\overline{PL}$ ) input clears the internal flip-flops to the start condition and enables the X latches to accept new multiplicand data. The Parallel Load ( $\overline{PL}$ ) also clears the output (SP).

#### **Features**

- Twos complement multiplication

- 8-bit by 1-bit sequential logic element

- Parallel inputs accept and store an 8-bit multiplicand (X<sub>0</sub>-X<sub>7</sub>)

- K input is used for expansion to longer X words

- Functionally and pin compatible to the Am25LS14A

#### Ordering Code: See Section 5

#### **Logic Symbol**

# Y PL X<sub>7</sub> X<sub>6</sub> X<sub>5</sub> X<sub>4</sub> X<sub>3</sub> X<sub>2</sub> X<sub>1</sub> X<sub>0</sub> K CP SP

TL/F/10217-1

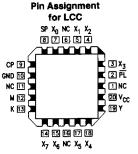

#### **Connection Diagrams**

TL/F/10217-3

#### Input Loading/Fan-Out: See Section 2 For U.L. Definitions

| Pin<br>Names | Description                                   | 54F/74F (U.L.)<br>High/Low | I <sub>IH</sub> /I <sub>IL</sub><br>I <sub>OH</sub> /I <sub>OL</sub> |

|--------------|-----------------------------------------------|----------------------------|----------------------------------------------------------------------|

| СР           | Clock Pulse Input (Active Rising Edge)        | 1.0/1.0                    | 20 μA/ - 0.6 mA                                                      |

| K            | Serial Expansion Input                        | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |

| М            | Mode Control Input                            | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |

| PL           | Asynchronous Parallel Load Input (Active LOW) | 1.0/2.0                    | 20 μA/ – 1.2 mA                                                      |

| $X_0-X_7$    | Multiplicand Data Inputs                      | 1.0/1.0                    | 20 μA/ – 0.6 mA                                                      |

| Ϋ́           | Serial Multiplier Input                       | 1.0/1.0                    | 20 μA/-0.6 mA                                                        |

| SP           | Serial X•Y Product Output                     | 50/33.3                    | -1 mA/20 mA                                                          |

#### **Functional Description**

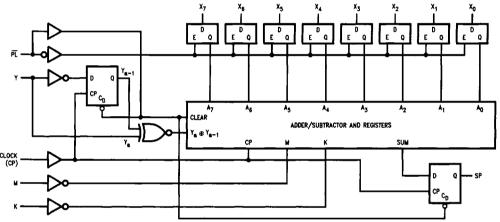

Referring to the Logic Diagram and Figure A, the multiplicand (X<sub>0</sub>-X<sub>7</sub>) latches are enabled to receive new data when PL is LOW. Data that meet the setup/hold time requirements are stored when PL goes HIGH. The LOW signal on PL clears the output (SP) as well as the internal flip-flops.

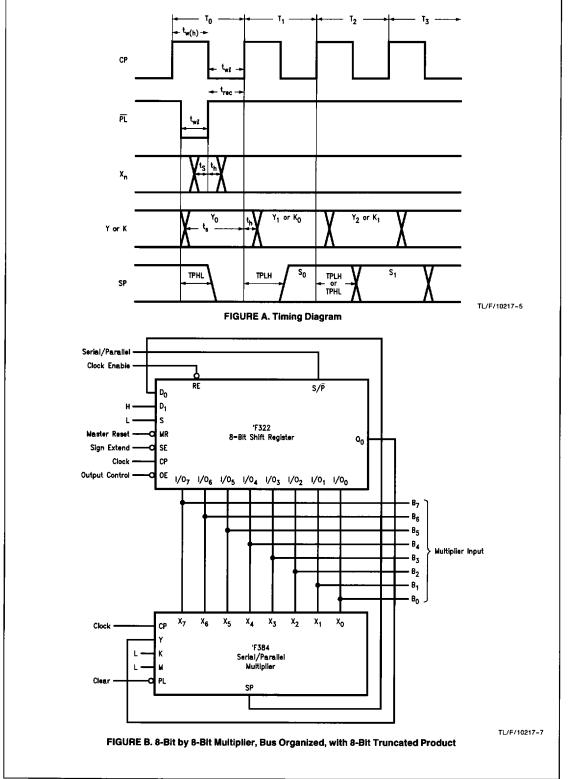

New multiplicand data enter the X latches during bit time To. It is assumed that PL goes LOW shortly after the CP rising edge that marks the beginning of To and goes HIGH again one recovery time before the beginning of T<sub>1</sub>. The LSB (Y<sub>0</sub>) of the multiplier is applied to the Y input during To and must be held one hold time after the beginning of T<sub>1</sub>. One propagation delay after the beginning of T1, the LSB (S0) of the product appears at the output (SP). This multiplication process is continued by applying Y1-Y6 to the Y input causing S<sub>1</sub>-S<sub>6</sub> of the product to appear at the output (SP).

The MSB Y7 (the sign bit) of the multiplier is first applied to the Y input during T<sub>7</sub> and must be held through T<sub>16</sub> causing S7-S15 of the product to appear at the output (SP). This extension of the sign bit is a necessary adjunct to the implementation of Booth's algorithm. This is a built-in feature of the 'F322 Shift Register (See Figure B).

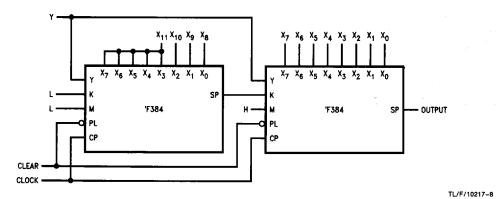

Figure C shows the method of using two F384's to perform a 12 x n bit multiplication. Notice that the sign of X is effectively extended by connecting X<sub>11</sub> to X<sub>4</sub>-X<sub>7</sub> of the most significant package. Whereas the 8 x 8 multiplication required 17 clock periods (m + n to form the product terms plus To to clear the multiplier), the arrangement of Figure C requires 12 + n + 1 bits to form the product terms.

#### **Logic Diagram**

TL/F/10217-4

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### **Function Table**

|    |          | Inpu | ıts |    | Output | Function |    |                                                                     |  |  |  |

|----|----------|------|-----|----|--------|----------|----|---------------------------------------------------------------------|--|--|--|

| PL | СР       | K    | М   | Χı | γ      | Ya-1     | SP | . a.louon                                                           |  |  |  |

| Х  | X        | L    | L   | Х  | Х      | Х        | х  | Most Significant Multiplier Device                                  |  |  |  |

| X  |          | CS   | Н   | ×  | Х      | Х        | Х  | Devices Cascaded in Multiplier String                               |  |  |  |

| L  | х        | ×    | X   | OP | Х      | L        | L  | Load New Multiplicand and Clear<br>Internal Sum and Carry Registers |  |  |  |

| Н  | Х        | Х    | Х   | Х  | Х      | Х        | Х  | Device Enabled                                                      |  |  |  |

| Н  | <u></u>  | Х    | ×   | Х  | L      | Ļ        | AR | Shift Sum Register                                                  |  |  |  |

| Н  | 1        | Х    | Х   | Х  | L      | н        | AR | Add Multiplicand to Sum<br>Register and Shift                       |  |  |  |

| Н  | 1        | ×    | Х   | Х  | Н      | L        | AR | Subtract Multiplicand from Sum<br>Register and Shift                |  |  |  |

| Н  | <b>↑</b> | Х    | Х   | Х  | Н      | н        | AR | Shift Sum Register                                                  |  |  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

<sup>=</sup> LOW-to-HIGH Transition

CS = Connected to SP output of high order device

$OP = X_i$  latches open for new data (i = 0-7)

AR = Output as required per Booth's algorithm

X = Immeterial

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature -65°C to +150°C

Ambient Temperature under Bias -55°C to +125°C

Junction Temperature under Bias −55°C to +175°C

V<sub>CC</sub> Pin Potential

to Ground Pin -0.5V to +7.0V

Input Voltage (Note 2) -0.5V to +7.0V Input Current (Note 2) -30 mA to +5.0 mA

Input Current (Note 2)

Voltage Applied to Output

in HIGH State (with V<sub>CC</sub> = 0V)

Current Applied to Output

in LOW State (Max) twice the rated IOL (mA)

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

Free Air Ambient Temperature

Military

−55°C to +125°C

Commercial

0°C to +70°C

Supply Voltage

Military +4.5V to +5.5V Commercial +4.5V to +5.5V

#### **DC Electrical Characteristics**

| Symbol           | Darama                               | Parameter                                                                    |                   | 54F/74F |              |          | Vcc        | Conditions                                                                                                                        |  |  |

|------------------|--------------------------------------|------------------------------------------------------------------------------|-------------------|---------|--------------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Эунион           | Farameter                            |                                                                              | Min               | Тур     | Max          | Units    | *CC        |                                                                                                                                   |  |  |

| V <sub>IH</sub>  | Input HIGH Voltage                   |                                                                              | 2.0               |         |              | ٧        |            | Recognized as a HIGH Signal                                                                                                       |  |  |

| V <sub>iL</sub>  | Input LOW Voltage                    |                                                                              |                   |         | 8.0          | >        |            | Recognized as a LOW Signal                                                                                                        |  |  |

| V <sub>CD</sub>  | Input Clamp Diode Vo                 | ltage                                                                        |                   |         | -1.2         | _<br>V   | Min        | I <sub>IN</sub> = -18 mA                                                                                                          |  |  |

| V <sub>OH</sub>  | Output HIGH<br>Voltage               | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 5% V <sub>CC</sub> | 2.5<br>2.5<br>2.7 |         |              | ٧        | Min        | $I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$                                                  |  |  |

| V <sub>OL</sub>  | Output LOW<br>Voltage                | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub>                           |                   |         | 0.5<br>0.5   | ٧        | Min        | I <sub>OL</sub> = 20 mA<br>I <sub>OL</sub> = 20 mA                                                                                |  |  |

| I <sub>1H</sub>  | Output HIGH<br>Current               | 54F<br>74F                                                                   |                   |         | 20.0<br>5.0  | μΑ       | Max        | V <sub>IN</sub> = 2.7 V                                                                                                           |  |  |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test | 54F<br>74F                                                                   |                   |         | 100<br>7.0   | μА       | Max        | V <sub>IN</sub> = 7.0 V                                                                                                           |  |  |

| I <sub>CEX</sub> | Output HIGH<br>Leakage Current       | 54F<br>74F                                                                   |                   |         | 250<br>50    | μΑ       | Max        | V <sub>OUT</sub> = V <sub>CC</sub>                                                                                                |  |  |

| V <sub>ID</sub>  | Input Leakage<br>Test                | 74F                                                                          | 4.75              |         |              | V,       | 0.0        | I <sub>ID</sub> = 1.9 μA<br>All Other Pins Grounded                                                                               |  |  |

| IOD              | Output Leakage<br>Circuit Current    | 74F                                                                          |                   |         | 3.75         | μΑ       | 0.0        | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded                                                                              |  |  |

| I <sub>IL</sub>  | Input LOW Current                    |                                                                              |                   |         | -0.6<br>-1.2 | mA<br>mA | Max<br>Max | $V_{\text{IN}} = 0.5V \text{ (Except } \overline{\text{PL}}\text{)}$ $V_{\text{IN}} = 0.5V \text{ (}\overline{\text{PL}}\text{)}$ |  |  |

| los              | Output Short-Circuit (               | Current                                                                      | -60               |         | 150          | mA       | Max        | V <sub>OUT</sub> = 0V                                                                                                             |  |  |

| Icc              | Power Supply Curren                  | t                                                                            |                   | 60      | 90           | mA       | Max        | V <sub>O</sub> = HIGH                                                                                                             |  |  |

# AC Electrical Characteristics : See Section 2 for Waveforms and Load Configurations

| Symbol                               | Parameter                     | 54F/74F  T <sub>A</sub> = +25°C  V <sub>CC</sub> = +5.0V  C <sub>L</sub> = 50 pF |            |            | 54F  T <sub>A</sub> , V <sub>CC</sub> =  Mil  C <sub>L</sub> = 50 pF |     | 74F  T <sub>A</sub> , V <sub>CC</sub> =  Com  C <sub>L</sub> = 50 pF |              | Units | Fig.<br>No. |

|--------------------------------------|-------------------------------|----------------------------------------------------------------------------------|------------|------------|----------------------------------------------------------------------|-----|----------------------------------------------------------------------|--------------|-------|-------------|

|                                      |                               | Min                                                                              | Тур        | Max        | Min                                                                  | Max | Min                                                                  | Max          |       |             |

| f <sub>max</sub>                     | Maximum Clock Frequency       | 50                                                                               |            |            |                                                                      |     | 50                                                                   |              | MHz   | 2-1         |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to SP | 3.5<br>3.5                                                                       | 6.5<br>6.5 | 9.0<br>9.0 |                                                                      |     | 3.5<br>3.5                                                           | 10.0<br>10.0 | ns    | 2-3         |

| t <sub>PHL</sub>                     | Propagation Delay PL to SP    | 6.0                                                                              | 10.0       | 13.0       |                                                                      |     | 6.0                                                                  | 14.0         | ns    | 2-3         |

# AC Operating Requirements : See Section 2 for Waveforms

| Symbol                                   |                                                 | 54F/74F<br>T <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5.0V |     | 5                                         | 4F  | 74                                        | \$F |       |             |

|------------------------------------------|-------------------------------------------------|--------------------------------------------------------------|-----|-------------------------------------------|-----|-------------------------------------------|-----|-------|-------------|

|                                          | Parameter                                       |                                                              |     | T <sub>A</sub> , V <sub>CC</sub> =<br>Mil |     | T <sub>A</sub> , V <sub>CC</sub> =<br>Com |     | Units | Fig.<br>No. |

|                                          |                                                 | Min                                                          | Max | Min                                       | Max | Min                                       | Max |       | L           |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>K to CP              | 9.0<br>9.0                                                   |     |                                           |     | 10.0<br>10.0                              |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>K to CP               | 2.0<br>2.0                                                   |     |                                           |     | 2.0<br>2.0                                |     | 113   | 2-6         |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>Y to CP              | 15.0<br>15.0                                                 |     |                                           |     | 15.0<br>15.0                              |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>Y to CP               | 2.0<br>2.0                                                   |     |                                           |     | 2.0<br>2.0                                |     | 1 115 |             |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>X <sub>n</sub> to PL | 3.0<br>6.0                                                   |     |                                           |     | 4.0<br>7.0                                |     | ns    | 2-6         |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW                          | 2.0<br>4.0                                                   |     |                                           |     | 2.0<br>4.0                                |     | 113   | 2-6         |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse Width<br>HIGH or LOW                   | 7.0<br>7.0                                                   |     |                                           |     | 7.0<br>7.0                                |     | ns    | 2-4         |

| t <sub>w</sub> (L)                       | PL Pulse Width, LOW                             | 6.5                                                          |     |                                           |     | 7.0                                       |     | ns    | 2-4         |

| t <sub>rec</sub>                         | Recovery Time<br>PL to CP                       | 6.0                                                          | _   |                                           |     | 10.0                                      |     | ns    | 2-6         |

FIGURE C. 12-Bit by n-Bit Twos Complement Multiplier