# 54F/74F146

# Priority Interrupt/DMA Request Controller

Descrition

prity Interrupt/DMA Request Controller is used to control the and output units to the processing unit. The 'F146 can neous or multiple requests according to their priority. Both a signal indicati n int runt/DMA request and 3-bit binary coded vector of the the highest level, re generated. Interrupt input and vector output latches are provided exibility to the interrupt scheme. The mask latch provides masking cap omany level interrupt before prioritization. The I/O ports and conto ow direct bus interfacing. The acknowledge outputs generate the bu dge signals for DMA controlling or multi-processor environments.

Ordering Code: See Section 5

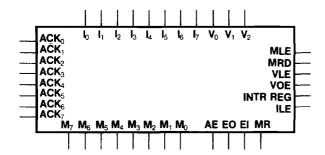

### **Logic Symbol**

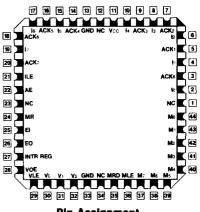

### **Connection Diagrams**

Pin Assignment for DIP

Pin Assignment for LCC and PCC

Input Loading/Fan-Out: See Section 3 for U.L. definitions

| Pin Names                                                            | Description                        | <b>54F/74F(U.L.)</b><br>HIGH/LOW |

|----------------------------------------------------------------------|------------------------------------|----------------------------------|

| I <sub>0</sub> -I <sub>7</sub><br>ACK <sub>0</sub> -ACK <sub>7</sub> | Interrupt Pins                     | 0.5/0.375                        |

| ACK <sub>0</sub> -ACK <sub>7</sub>                                   | Acknowledge Outputs                | 25/12.5                          |

| ILE                                                                  | Interrupt Latch Enable             | 0.5/0.375                        |

| ĀĒ                                                                   | Acknowledge Enable (Active LOW)    | 0.5/0.375                        |

| MR                                                                   | Master Reset                       | 0.5/0.375                        |

| INRQ                                                                 | Interrupt Request                  | 25/12.5                          |

| М <sub>0</sub> -М <sub>7</sub>                                       | Mask Inputs                        | 0.5/0.375                        |

| CŠ                                                                   | Mask Latch Address Select Line     | 0.5/0.375                        |

| R/W                                                                  | Mask Latch Read/Write Control Line | 0.5/0.375                        |

| $\overline{V}_0$ - $\overline{V}_2$                                  | Priority Vector                    | 25/12.5                          |

| <b>VLE</b>                                                           | Vector Latch Enable                | 0.5/0.375                        |

| VOE                                                                  | Vector Output Enable (Active LOW)  | 0.5/0.375                        |

| ĒŌ                                                                   | Expansion Output (Active LOW)      | 25/12.5                          |

| ĒĪ                                                                   | Expansion Input (Active LOW)       | 0.5/0.375                        |

### **Functional Description**

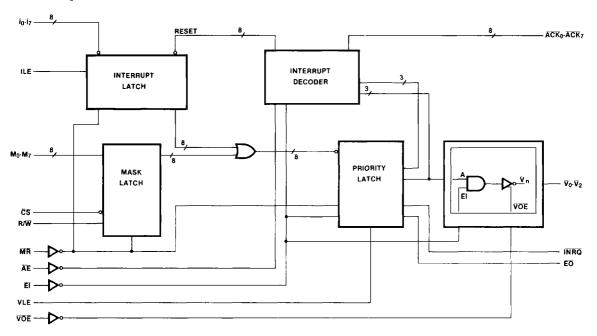

The basic function of the 'F146 Priority Interrupt/DMA Controller is as follows. The receipt of an interrupt signal from the Interrupting Peripheral generates an Interrupt Request signal, stopping the processor after the current instruction or bus cycle. The processor will respond by enabling the vector data generated by the 'F146 to be read on the data bus and generating an acknowledge enable signal. This Acknowledge signal is used by the 'F146 to generate the Peripheral Acknowledge signal and reset the Interrupt Request. The 'F146 consists of four major sections as described below:

#### Interrupt Latch

The interrupt latch is organized as eight SR latches. The Set input is used to catch negative transitions on the Interrupt ( $\overline{I}_n$ ) inputs. Latch Enable (ILE) latches the current interrupt status and inhibits further changes. The Reset ( $\overline{MR}$ ) input to each latch is fully overriding, resetting the latch regardless of the state of the ILE input. If both S and R are HIGH, the previous state of the Latch is held.

#### Mask Latch

The Mask Latch is an Octal Latched Transceiver. This latch allows changes to the interrupt scheme to be made dynamically by masking out chosen interrupts before prioritizing. The Address Select

Line ( $\overline{CS}$ ) selects the mask latch on the negative transition and the Latch Read/Write Control Line (R/ $\overline{W}$ ) controls the Read/Write status of the mask latch. The Mask (M) I/O ports add the freedom of storing the current mask word for retrieval at a later time, thus requiring no register overhead.

#### **Priority Latch**

The Priority Encoder  $(\overline{V}_n)$  and Vector Latch (VLE) can be integrated into one functional block. The Priority Latch encodes the eight interrupt lines (and the complements) providing a 3-bit binary vector. A priority is assigned to each input so that when two or more inputs are active, the one with the highest priority is represented by the vector output. The Expansion Input (EI) and the Expansion Output (EO) signals are provided for cascade expansion, with the EO being the more significant Priority Encoder driving the EI which is less significant. The latch is employed to prevent erroneous vector outputs during reading and peripheral acknowledge cycles. The Group Signal (INRQ) provides direct detection of an interupt before vector generation is complete.

#### Interrupt Decoder

A 3-to-8 line decoder decodes the vector address generating the peripheral acknowledge outputs (ACK<sub>n</sub>) and the Interrupt Latch Reset (MR) signals.

## **Block Diagram**

## DC Characteristics over Operating Temperature Range (unless otherwise specified)

|                 | 54F/74F              |     |     |     |       |                       |

|-----------------|----------------------|-----|-----|-----|-------|-----------------------|

| Symbol          | Parameter            | Min | Тур | Max | Units | Conditions            |

| I <sub>cc</sub> | Power Supply Current |     | 100 | 150 | mA    | V <sub>CC</sub> = Max |

AC Characteristics: See Section 3 for waveforms and load configurations

| Symbol                               | Parameter                                                                | 54F/74F                                              | 54F                                                              | 74F                                                                 | Units |

|--------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|-------|

|                                      |                                                                          | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V<br>$C_L = 50$ pF | T <sub>A</sub> , V <sub>CC</sub> = Mil<br>C <sub>L</sub> = 50 pF | T <sub>A</sub> , V <sub>CC</sub> =<br>Com<br>C <sub>L</sub> = 50 pF |       |

|                                      |                                                                          | Min Typ Max                                          | Min Max                                                          | Min Max                                                             |       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay ī to ĪNRQ                                              | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>EI to EO, ACK <sub>n</sub> , V <sub>n</sub> or INRQ | 8.0<br>8.0                                           |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CS to INRQ or V <sub>n</sub>                           | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{I}_n$ to $\overline{V}_n$                   | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay ILE to $\overline{V}_n$                                | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>ILE to INRQ                                         | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>R/W to INRQ or V <sub>n</sub>                       | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay MR to V <sub>n</sub>                                   | 10.0<br>10.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay VLE to $\overline{V}_n$                                | 11.5<br>11.5                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay AE to ACK <sub>n</sub>                                 | 8.0<br>8.0                                           |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay MR to INRQ                                             | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay M <sub>n</sub> to INRQ or V <sub>n</sub>               | 14.0<br>14.0                                         |                                                                  |                                                                     | ns    |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Enable Time<br>VOE to V <sub>n</sub>                              | 8.0<br>8.0                                           |                                                                  |                                                                     | ns    |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output Disable Time<br>VOE to V <sub>n</sub>                             | 8.0<br>8.0                                           |                                                                  |                                                                     | ns    |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Enable Time<br>CS or R/W to M <sub>n</sub>                        | 8.0<br>8.0                                           |                                                                  |                                                                     | ns    |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Propagation Delay CS or R/W to Mn                                        | 8.0<br>8.0                                           |                                                                  |                                                                     | ns    |

## AC Operating Requirements: See Section 3 for waveforms

| Symbol                                   | Parameter                                                | 54F/74F                             | 54F                                | 74F                                       | Units |  |

|------------------------------------------|----------------------------------------------------------|-------------------------------------|------------------------------------|-------------------------------------------|-------|--|

|                                          |                                                          | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V | T <sub>A</sub> , V <sub>CC</sub> = | T <sub>A</sub> , V <sub>CC</sub> =<br>Com |       |  |

|                                          |                                                          | Min Typ Max                         | Min Max                            | Min Max                                   |       |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW In to ILE                        | 4.0<br>4.0                          |                                    |                                           | ns    |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW $\overline{I}_n$ to ILE           | 3.0<br>3.0                          |                                    |                                           |       |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW M <sub>n</sub> to CS or R/W      | 4.0<br>4.0                          |                                    |                                           | ns    |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW M <sub>n</sub> to CS or R/W       | 3.0<br>3.0                          |                                    |                                           |       |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW $M_n$ or $\overline{I}_n$ to VLE | 7.0<br>7.0                          |                                    |                                           |       |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW $M_n$ or $\overline{I}_n$ to VLE  | 3.0<br>3.0                          |                                    |                                           | ns    |  |

| t <sub>w</sub> (L)                       | MR Pulse Width, LOW                                      | 6.0                                 |                                    |                                           | ns    |  |

| t <sub>w</sub> (L)                       | ILE or VLE Pulse Width, LOW                              | 6.0                                 |                                    |                                           | ns    |  |

| t <sub>rec</sub>                         | Recovery Time<br>MR to ILE                               | 6.0                                 |                                    |                                           | ns    |  |

| t <sub>rec</sub>                         | Recovery Time<br>MR to CS or R/W                         | 6.0                                 |                                    |                                           | ns    |  |