# MB81C4251-10/-12/-15

## 1,048,576 BIT DUAL PORT CMOS DYNAMIC RAM

## 262,144 X 4 Bit Dual Port CMOS Dynamic RAM

The Fujitsu MB81C4251 is a fully decoded dual port CMOS Dynamic RAM(DRAM) organized as 262,144 words by 4 bits dynamic RAM port and 512 words by 4 bits serial access memory (SAM) port.

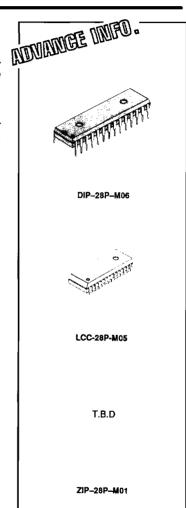

The MB81C4251 is ideally suited for mainframes, video imaging equipment, and other memory applications where very low power dissipation and high bandwidth are basic requirements of the design. Multiplexed row and column address inputs permit the MB81C4251 to behoused in 400mil wide 28 pin DIP, SOJ and ZIP. Pin outs conformed to the JEDEC approved pinout. The MB81C4251 features a Bit Masked Write operation whereby the user can inhibit writing to particular bits.

The MB81C4251 is fabricated using silicon gate CMOS and Fujitsu's advanced triple-layer polysilicon process. This process, coupled with three-dimensional stacked capacitor memory cells, reduces the possibility of soft errors and extends the time interval between memory refreshes.

### **PRODUCT LINE & FEATURES**

| Paramete <del>r</del> |                                 | MB81C425110 | MB81C4251-12 | MB81C425115 |            |

|-----------------------|---------------------------------|-------------|--------------|-------------|------------|

|                       |                                 | DRAM        | 100ns max.   | 120ns max.  | 150ns max. |

| Access Time           | •                               | SAM         | 30ns max.    | 40ns max.   | 60ns max.  |

|                       |                                 | DRAM        | 180ns min.   | 210ns min.  | 260ns min. |

| Cycle Time            | Cycle Time                      |             | 30ns min.    | 40ns min.   | 60ns min.  |

| Power<br>Dissipation  | DRAM ; Active<br>SAM ; Standby  |             | 450mW max.   | 400mW max.  | 350mW max. |

|                       | DRAM ; Standby<br>SAM ; Active  |             | 330mW max.   | 280mW max.  | 250mW max. |

|                       | DRAM ; Standby<br>SAM ; Standby |             | 22mW max.    |             |            |

- Dual port organization

262,144 words x 4 bits (DRAM port)

512 words x 4 bits (SAM port)

- Silicon gate, CMOS, 1 transistor cell

- Single +5V power supply, + / 0.5 V tolerance

- · All inputs and outputs are TTL compatible

- 512 refresh cycles every 8.2 ms

- Bi-directional data transfer capability

- Fast serial access asynchronous to DRAM expect transfer operation

- Addressable start location(TAP) on serial shift register

- Realtime Read Transfer capability

- Bit Masked Write Mode capability

- I/O switch by transfer cycle

- Fast page Mode, Read-Modify-Write capability

- RAS only, CAS-before-RAS, or Hidden

Refresh

#### **ABSOLUTE MAXIMUM RATINGS (see NOTE)**

| Parameter                                         | Symbol                             | Value       | Unit |

|---------------------------------------------------|------------------------------------|-------------|------|

| Voltage at any pin relative to VSS                | V <sub>IN</sub> , V <sub>OUT</sub> | -1 to +7    | >    |

| Voltage of V <sub>CC</sub> supply relative to VSS | Vcc                                | -1 to +7    | >    |

| Power Dissipation                                 | PD                                 | 1.0         | W    |

| Short Circuit Output Current                      | lout                               | 50          | mA   |

| Storage Temperature                               | T <sub>STG</sub>                   | -55 to +125 | °c   |

NOTE: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric liefs. However, it is advised that normal precutions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Copyright © 1989 by FUJITSU LIMITED