# WD2511A X.25 Packet Network Interface (LAPB)

## **FEATURES**

# Handles The Entire Link Level Communication Protocol

- International standard CCIT X.25 LAPB protocol for packet switching

- Programmable link level timer (T1) and retransmission counter (N2)

- Automatic framing, appending and testing of FCS, and zero bit insertion and deletion

- · Automatic error detection and retransmission

- Automatic flow control when buffers are not available

- Certified by Telenet, Transpac, and other major packet switching networks

# **Custom Communications Architecture Provides Top Performance**

- Full-duplex transmission speeds to 1.1 Mbps

- Dual-channel direct memory access (DMA) capability unburdens your CPU

- Bus-oriented control for easy computer interface

- · Synchronous modem interface built in

- 5 Volt NMOS technology in 48-pin DIP and 68-pin CLCC

- · TTL compatible on all inputs and outputs

## X.25 Feature Extensions For Broader Applications

- Half-Duplex communication option

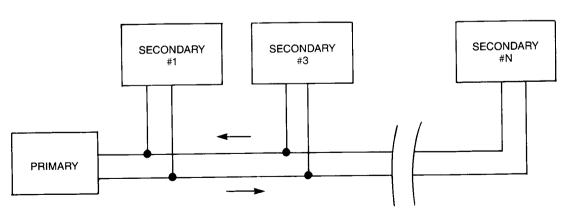

- Programmable address field for multipoint operation and any point-to-point application where throughput and data integrity are required

- · Built-in loopback testing

## DESCRIPTION

Western Digital is the first company to offer a complete implementation of the CCITT Recommendation X.25 LAPB protocol in a chip. The WD2511A provides an error free communication capability while offloading the Host from the responsibility of meeting the realtime requirements of the communication channel.

The WD2511A consists of a 48-pin DIP and 68-pin CLCC. These NMOS LSI devices provide a unique solution for point-to-point communication requirements. The WD2511A offloads the Host by implementing the full link layer protocol of the International Standard Recommendation X.25 using the two DMA channels.

This bit oriented serial link controller automatically handles the transmission and reception of packets of data, acknowledges the receipt of error free packets, and requests that lost or erroneous packets be retransmitted.

The WD2511A interrupts the Host after receiving an error free packet, acknowledgement of a transmitted packet, and after detecting certain error or abnormal conditions on the link.

#### **APPLICATIONS**

The WD2511A can be used on dedicated or switched lines whenever reliable error free communication is needed. In fact, any point-to-point application concerned with high integrity and throughput will benefit from the WD2511A's integrated solution.

Examples of equipment using this chip include modems, PADs, switching nodes, statistical multiplexers, gateways from one network to another and equipment connecting computers or terminals to public or private networks.

| TAB        | LE OF CONTENTS                                     |            |                                       | _        |

|------------|----------------------------------------------------|------------|---------------------------------------|----------|

| 1.0        | Organization of WD2511A                            |            |                                       | <u>ح</u> |

|            | Structure of X.25                                  |            |                                       | 5        |

| - 2        | 2.1 Frame Format                                   |            |                                       | 7        |

|            | 2.3 Control Field Formats                          |            |                                       | /        |

| _          | 2.4 Supervisory Commands and Responses             | <i>.</i> . |                                       | 7        |

| _          | 2.5 Unnumbered Commands and Responses              |            |                                       | /        |

|            | 2.6 Exception Condition Reporting and Recovery     |            |                                       | 9        |

| _          | 2.8 Use of Poll Bit                                |            |                                       | 9        |

|            | 2.9 Transmission of Abort                          |            |                                       | 9        |

| :          | 2.10 LAPB Procedure                                |            |                                       | 9        |

| :          | 2.11 The Difference Between LAP and LAPB           |            |                                       | 10       |

|            | Register Description                               |            |                                       | 11       |

|            | 3.1 Control Registers                              |            |                                       | 12       |

|            | 3.3 Error Register                                 | <b></b> .  |                                       | 14       |

| ;          | 3.4 Received Control Field Register                |            |                                       | 15       |

|            | 3.5 Timer/Counter Register                         |            | · · · · · · · · · · · · · · · · · · · | 15<br>15 |

|            |                                                    |            |                                       |          |

|            | Memory Access Method                               |            |                                       | 16       |

|            | 4.2 Receive (RLOOK)                                | <b>.</b> . |                                       | 1/       |

|            | 4.3 Deadly Embrace Prevention                      |            |                                       | 19       |

|            | 4.4 SEND Bit Contention                            |            |                                       | 19<br>20 |

|            | 4.5 Buffer Size/Chaining Register                  |            |                                       | 20       |

|            | 4.7 Variable Bit Length and Residual Bits          |            |                                       | 21       |

|            | 4.8 Error Counters                                 |            |                                       | 21       |

| 5.0        | Self Tests                                         |            |                                       | 21       |

|            | 5.1 Internal RAM Register Test 5.2 Loop-Back Test  |            |                                       | 21<br>21 |

|            | Electrical Specifications                          |            |                                       | 21       |

| 6.0        | Electrical Specifications                          |            |                                       | 24       |

| 7.0        | Ordering Information                               |            |                                       | 25       |

| App        | pendix A - Transparent Modes                       |            |                                       | 20       |

| App        | pendix B - Half-Duplex Option                      |            |                                       | 21       |

| App        | pendix C - Operating in a Multipoint Configuration |            |                                       | 28       |

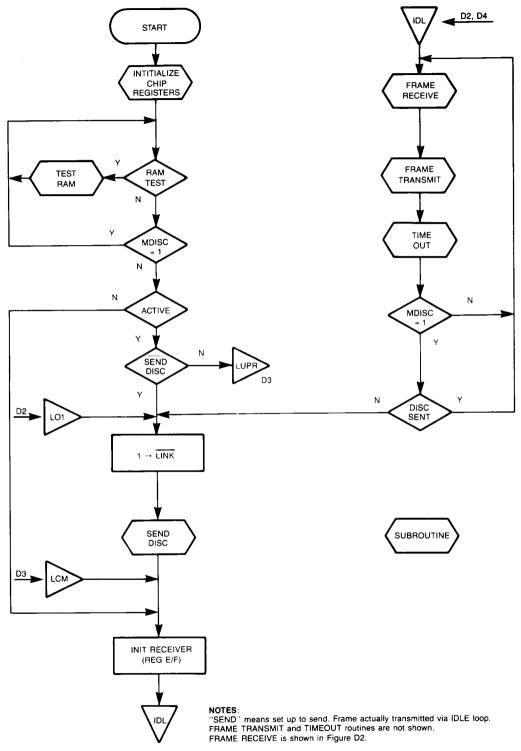

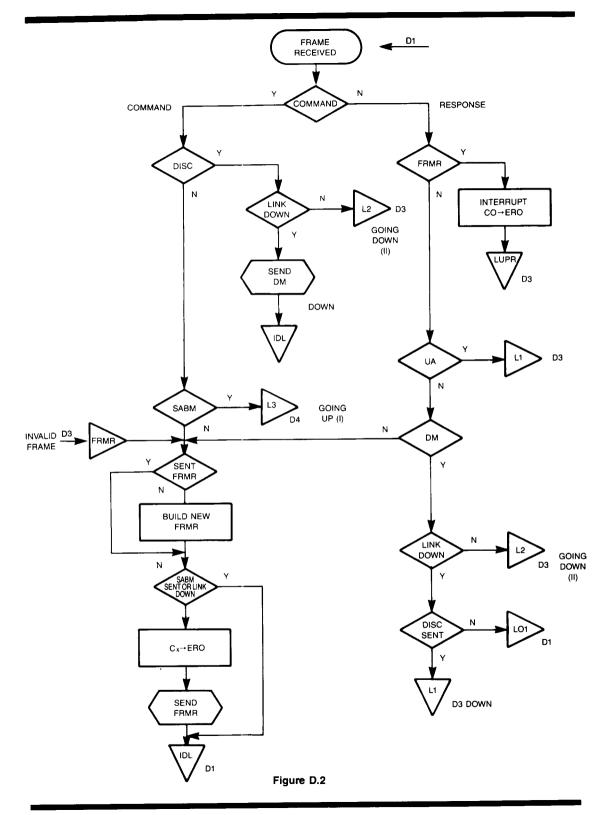

| App        | pendix D - State Description                       |            |                                       | 29       |

| App        | pendix E - Software Application Notes              |            |                                       | 38       |

| App        | pendix F - Hardware Application Notes              |            |                                       | 63       |

| Glo        | ssary                                              |            |                                       | 64       |

| FIG        | URES                                               | TAB        | LES                                   |          |

| 1.         | 48-Pin Designation 1                               | 1.         | 48-Pin and 68-Pin                     | _        |

|            | 68-Pin Designation                                 |            | Interface Signals Description         |          |

| 2.         | WD2511A Block Diagram 5 LAPB Frame Format 6        | 2.<br>3.   | Frame Types                           |          |

| 3.<br>4.   | FRMR Information Field 8                           | 4.         | Control, Status, Error Registers      | 11       |

| 5.         | System Connection Interface10                      | 5.         | Control Register 0                    | 11       |

| 6.         | Time Out Conditions                                | 6.<br>7.   | Control Register 1                    |          |

| 7.<br>8.   | Memory Access Scheme                               | 7.<br>8.   | STATUS Register 1                     |          |

| o.<br>9.   | TLOOK Segment                                      | 9.         | STATUS Register 2                     | 13       |

| 10.        | TLOOK Segment State Flow                           | 10.        | Error Register 0                      | 14       |

| 11.        | RLOOK Segment                                      | 11.        | DC Operating Characteristics          | 12<br>22 |

| 12.<br>13. | RLOOK Segment State Flow                           | 12.        | AO THIIIING CHARACTERISTICS           |          |

| ıJ.        | rining Diagrams                                    |            |                                       |          |

## 1.0 ORGANIZATION

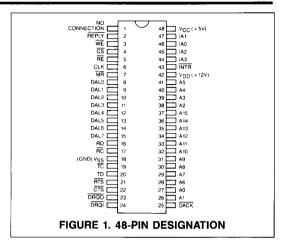

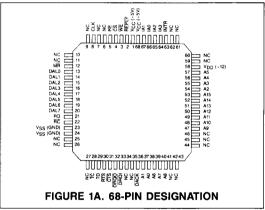

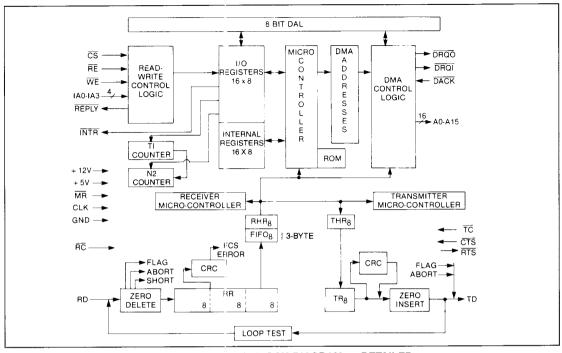

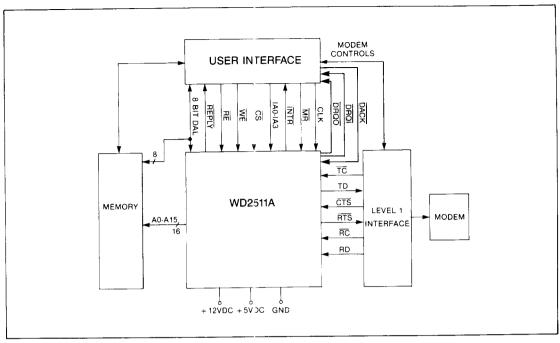

Figures 1 and 1A illustrate the Pin Designations and Table 1 describes the interface signals of the WD2511A. A detailed block diagram of the WD2511A is shown in Figure 2. A glossary of terms used throughout this document appears at the end of the Data Sheet.

Mode control and monitor of status by the user's CPU is performed through the Read/Write Control circuit which reads from or writes into I/O registers addressed by IAO-IA3.

Transmit and receive data are accessed through the DMA control. Serial data is generated and received by the bitoriented controllers.

Internal Control of the WD2511A is by means of three internal microcontrollers: one for transmit, one for receive, and one for overall control.

Parallel transmit data are entered into the Transmitter Holding Register (THR) and then presented to the Transmitter Register (TR) which converts the data to a serial bit stream. The Cyclic Redundancy Check (CRC) is computed in the 16-bit CRC register and the result becomes the transmitted Frame Check Sequence (FCS).

Parallel receive data enters the Receiver Holding Register (RHR) from the 24-bit serial Receiver Register (RR). The 24-bit length of RR permits stripping of the FCS prior to transfer into the RHR. The receiver CRC register is used to test the validity of the received FCS. A 3-Byte FIFO is included in the receiver to decouple the speed of the user from the receiver.

Table 1, 48-PIN AND 68-PIN INTERFACE SIGNALS DESCRIPTION (All signals are TTL compatible.)

| 48-PIN<br>NUMBER | 68-PIN<br>NUMBER | SYMBOL        | PIN NAME             | FUNCTION                                                                                                                                                           |

|------------------|------------------|---------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | -                | NO CONNECTION | No Connection        | Leave pin open.                                                                                                                                                    |

| 2                | 2                | REPLY         | Reply                | An active low output indicates the WD2511A has either a CS∙RE or a CS•WE condition.                                                                                |

| 3                | 3                | WE            | Write Enable         | The data on the DAL are written into the selected register when $\overline{CS}$ and $\overline{WE}$ are low.                                                       |

| 4                | 4                | CS            | Chip Select          | Active low chip select for user control of I/O registers.                                                                                                          |

| 5                | 5                | RE            | Read Enable          | The contents of the selected register is placed on DAL when $\overline{\text{CS}}$ and $\overline{\text{RE}}$ are low.                                             |

| 6                | 8                | CLK           | Clock                | Clock input used for internal timing. Must be square wave and should be 2MHZ $\pm$ 5%. For operation at less than 2MHZ, contact the factory.                       |

| 7                | 12               | MR            | Master Reset         | Active low initializes the chip. All registers reset to zero, except control bits MDISC and LINK which are set to 1. DACK must be stable high before MR goes high. |

| 8-15             | 13-20            | DAL0-DAL7     | Data Access<br>Lines | An 8-bit bi-directional three-state data bus for user and DMA controller transfers.                                                                                |

| 16               | 21               | RD            | Receive Date         | Receive serial data input.                                                                                                                                         |

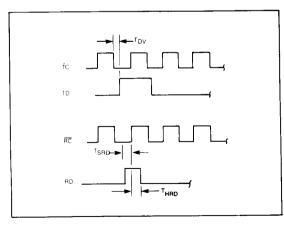

| 17               | 22               | RC            | Receive Clock        | This is a 1x clock input. RD is sampled on the rising edge of RC.                                                                                                  |

| 18               | 23,24            | $V_{SS}$      | Ground               | Ground.                                                                                                                                                            |

| 19               | 28               | TC            | Transmit Clock       | A 1x clock input. TD changes on the falling edge of TC.                                                                                                            |

| 20               | 29               | TD            | Transmit Data        | Transmit serial data output.                                                                                                                                       |

| 21               | 30               | RTS           | Request-To-Send      | An open collector (drain) output which goes low when the WD2511A is ready to transmit either flags or data.                                                        |

| 22               | 31               | стѕ           | Clear-To-Send        | An active low output signals the WD2511A that transmission may begin. If high, the TD output is forced high. May be hard-wired to ground.                          |

Table 1. 48-PIN AND 68-PIN INTERFACE SIGNALS DESCRIPTION (continued) (All signals are TTL compatible.)

| 48-PIN<br>NUMBER         | 68-PIN<br>NUMBER                                     | SYMBOL          | PIN NAME             | FUNCTION                                                                                                                                                                                                                                            |

|--------------------------|------------------------------------------------------|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23                       | 32                                                   | DRQO            | DMA Request<br>Out   | An active low output signal which initiates user bus request so the WD2511A can output data onto the bus.                                                                                                                                           |

| 24                       | 33                                                   | DRQI            | DMA Request In       | An active low output signal which initiates user bus request so that data may be input to the WD2511A.                                                                                                                                              |

| 25                       | 36                                                   | DACK            | DMA<br>Acknowledge   | An active low input from the user in response to DRQI or DRQO. DACK must not be low if CS and RE are low or if CS and WE are low.                                                                                                                   |

| 27,26<br>38-41,<br>28-37 | 38,37,<br>54-57,<br>39-41,<br>47-53                  | A0-A15          | Address Lines<br>Out | Sixteen address outputs from the WD2511A for DMA operation. If the control bit ADRV is 1, the outputs are TTL drives at all times. If ADRV is 0, the outputs are three-state, and are HI-Z whenever DACK is high. (ADRV is in Control Register #1.) |

| 42                       | 58                                                   | $V_{DD}$        | Power Supply         | +12VDC power supply input.                                                                                                                                                                                                                          |

| 43                       | 63                                                   | INTR            | Interrupt Request    | An active low interrupt service request output. Returns to high when Status Register #1 is read.                                                                                                                                                    |

| 46,47,<br>45,44          | 64,65,<br>66,67                                      | IAO-IA3         | Address Lines In     | Four address inputs for user controlled read/<br>write operation of the I/O registers in the<br>WD2511A. If ADRV = 0, these may be tied to<br>A0-A3. (ADRV is in Control Register = 1.)                                                             |

| 48                       | 1,68                                                 | V <sub>cc</sub> | Power Supply         | +5VDC power supply input.                                                                                                                                                                                                                           |

| -                        | 6,7,<br>9-11,<br>25-27,<br>34,35,<br>42-46,<br>59-62 | NC              | No Connection        | Leave pins open.                                                                                                                                                                                                                                    |

Figure 2. WD2511A BLOCK DIAGRAM — DETAILED

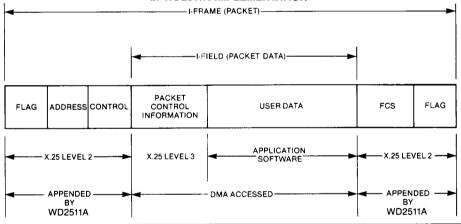

## 2.0 THE STRUCTURE OF X.25

CCITT Recommendation X.25 is an international standard for connecting computer equipment to a Public Data Network (PDN). Its uses, however, go far beyond PDN'S. X.25 is used for connecting dissimilar computer equipment together, as a gateway from one Local Area Network (LAN) to another, and in many private Wide Area Networks (WAN).

## THE WD2511A AND THE ISO MODEL

The CCITT X.25 recommendation comprises three levels of protocols (Level 1 to 3).

LEVEL 3 PÄCKET LAYER SOFTWARE

LEVEL 2 DATA LINK LAYER LAPB (WD2511A)

LEVEL 1 PHYSICAL LAYER RS232, X.21

Level 1 is the physical level, which concerns the actual means of bit transmission across a physical medium.

Level 2 is the link level which includes frame formatting, error control and link control.

Level 3 is the packet (network) level which controls the traffic of the different virtual calls and multiplexes these for passage over the physical line.

These three levels are completely independent of each other, which allows changes to be made to one level without disrupting the operation of any other level. An adjacent level is affected only if the changes affect the interface to that level.

Each level performs one well defined set of functions, using only a well defined set of services provided by the

level below. These functions implement a set of service that can be accessed only from the level above. Each level is strictly controlled by the systems engineer according to formal functional and interface specifications.

The WD2511A implements level 2. Without additional logic, it generates the frame, performs error checking, performs link management (set up/disconnect) and ensures reliable data transmission by evaluating the sequence number associated with each I-frame. The device automatically acknowledges received I-frames and fully supports up to 7 outstanding (unacknowledged) frames, including retransmission if required.

## 2.1 FRAME FORMAT

The WD2511A performs LAPB, which is a "bit oriented" data communications protocol. According to the general format for bit-oriented procedures (HDLC, SDLC, ADCCP) each serial block of data is called a frame. Figure 3 shows the frame format.

Each frame starts and ends with a FLAG (01111110). A single FLAG may be used both as the closing flag of one frame and the opening flag of the next frame. The WD2511A can detect this shared flag if it receives one. However, the WD2511A generates at least three flags inbetween each frame it transmits with the exception of ABOHT frames. In this case the WD2511A could generate a single flag after an aborted frame.

In between flags, data transparency to easily distinguish flags from data is provided by the insertion of a 0 bit after

all sequences of 5 contiguous 1 bits. The receiver will strip 0 these inserted 0 bits to reconstruct the original data.

Each frame begins with an address field followed by a control field (the A and C fields). The last 16-bits before the closing flag make up the Frame Check Sequence (FCS.)

The Address field consists of one byte.

The Control field consists of one byte. The content of this field is described below.

The Information field of a frame is unrestricted with respect to code or grouping of bits. The maximum length of an I-field is a system parameter.

| a. FRAME | FORMATS |

|----------|---------|

|----------|---------|

Bit order of transmission

|   | 12345678 | 12345678 | 12345678 | 16 to 1 | 12345078 |

|---|----------|----------|----------|---------|----------|

| ſ | Flag     | Address  | Control  | FCS     | Flag     |

| Ī | F        | Α        | С        | FCS     | F        |

|   | 01111110 | 8-bits   | 8-bits   | 16-bits | 01111110 |

Bit order of transmission

12345678 12345678 12345678

16 to 1 12345678

40045070

| Flag     | Address | Control | Information | FCS     | Flag     |

|----------|---------|---------|-------------|---------|----------|

| F        | A       | C       | I           | FCS     | F        |

| 01111110 | 8-bits  | 8-bits  | N-bits      | 16-bits | 01111110 |

FCS Frame Checking Sequence

## b. WD2511A IMPLEMENTATION

Figure 3. LAPB FRAME FORMAT

The FCS calculation includes all data between the opening flag and the first bit of the FCS, except for 0's inserted for transparency. The 16-bit FCS has the following characteristics:

$= X^{16} + X^{12} + X^{5} + 1$ Polynomial

Transmitted Polarity - Inverted Transmitted Order - High Order Bit First

Preset Value - All 1's

After the frame is received, if there were no errors, the remainder in the CRC register (internal in the WD2511A)

will be:

1111000010111000 (FOB8).

The WD2511A generates and tests the opening and closing Flag, FCS, A-Field, and C-Field and performs zero bit insertion and deletion.

According to the X.25 protocol, there are three types of frames: supervisory (S-frame), un-numbered (U-frame), and information (I-frame). The WD2511A performs datalink layer access control. All S- and U-frames are automatically generated and tested by the WD2511A. The user need only be concerned with the I-frames, (i.e. packets).

The WD2511A will transmit contiguous flags for interframe time fill in full duplex mode.

Addresses, commands, responses and sequence numbers are transmitted with the low order bit first. The order of transmitting bits within the information field is not specified in X.25. The WD2511A transmitts the low order bit first. The FCS is transmitted to the line commencing with the coefficient of the highest term. (*Note* – The low order bit is defined as bit 1, as depicted in Figure 3.)

A frame not properly bounded by two flags, or having fewer than 32 bits between flags, is an invalid frame.

Aborting a frame is performed by transmitting at least seven contiguous 1s (with no inserted 0s).

Interframe time fill is accomplished by transmitting contiguous flags between frames.

#### 2.2 LINK STATES

The Link is in an ACTIVE condition when a station is actively transmitting a frame, an abort sequence, or interframe time fill.

The Link is defined to be in an IDLE condition when a contiguous 1s state is detected that persists for at least 15 bit times.

#### 2.3 CONTROL FIELD FORMATS

The control field contains a command or a response, and sequence numbers where applicable.

Three types of control field formats (see Table 2.) are used to perform the LAPB protocol: numbered information transfer (I frames), numbered supervisory functions (S frames) and unnumbered control functions (U frames).

The I format is used to perform an information transfer. The functions of N(S), N(R) and P/F are independent; i.e., each I frame has an N(S), an N(R) which may or may not acknowledge additional I frames received by the DTE or DCE, and a P/F bit.

The S format is used to perform link supervisory control functions such as to acknowledge I frames, to request retransmission of I frames, and to request a temporary suspension of transmission of I frames.

The U format is used to provide additional link control functions. This format contains no sequence numbers.

## Modulus

Each I frame is sequentially numbered and may have the value 0 through modulus minus 1 (where "modulus" is the modulus of the sequence numbers). The modulus equals 8 and the sequence numbers cycle through the range of 0 to 7.

## Frame variables and sequence numbers

The send state variable denotes the sequence number of the next in-sequence I frame to be transmitted. The send state variable can take on the value 0 through 7. The value of the send state variable is incremented by 1 with each successive I frame transmission, but cannot exceed N(R) of the last received I or S frame by more than the maximum number of outstanding I frames (7). Only I frames contain N(S), the send sequence number of transmitted frames. Prior to transmission of an in-

sequence I frame, the value of N(S) is set equal to the value of the send state variable.

The receive state variable denotes the sequence number of the next in-sequence I frame to be received. The receive state variable can take on the value 0 through 7. The value of the receive state variable is incremented by one with the receipt of an error free, in-sequence I frame whose send sequence number N(S) equals the receive state variable. All I frames and S frames contain N(R), the expected sequence number of the next received I frame. Prior to transmission of a frame of the above types, the value of N(R) is set equal to the current value of the receive state variable. N(R) indicates that the DTE or DCE transmitting the N(R) has received correctly all I frames numbered up to and including N(R) – 1.

## 2.4 SUPERVISORY COMMANDS AND RESPONSES

The Receive Ready (RR) supervisory frame is used to indicate it is ready to receive an I frame or to acknowledge previously received I frames numbered up to and including N(R) - 1. RR may be used to clear a busy condition that was initiated by the transmision of an RNR.

The Reject (REJ) supervisory frame is used to request retransmission of I frames starting with the frame numbered N(R). I frames numbered N(R) – 1 and below are acknowledged. Additional I frames pending initial transmission may be transmitted following the retransmitted I frame(s).

Only one REJ exception condition for a given direction of information transfer may be established at any time. The REJ exception condition is cleared (reset) upon the receipt of an I frame with an N(S) equal to the N(R) of the REJ.

The Receive Not Ready (RNR) supervisory frame is used to indicate a busy condition: i.e., temporary inability to accept additional incoming I frames. I frames numbered up to and including N(R) – 1 are acknowledged. I frame N(R) and subsequent I frames received, if any, are not acknowledged; the acceptance status of these I frames will be indicated in subsequent exchanges. An indication that the busy condition has cleared is communicated by the transmission of a UA, RR, REJ or SABM. The RNR, REJ or RR command with the P bit set to 1 may be used to ask for the status of the remote device.

## 2.5 UNNUMBERED COMMANDS AND RESPONSES

The SABM unnumbered command is used to place the addressed station in the asynchronous balanced mode (ABM) information transfer phase. No information field is permitted with the SABM command. A station confirms acceptance of SABM by the transmission at the first opportunity of a UA response. Upon acceptance of this command the send state variable and receive state variable are set to 0. Previously transmitted I frames that are unacknowledged when this command is actioned remain unacknowledged and must be resent after the Link has been brought back up.

The DISC unnumbered command is used to terminate the mode previously set. It is used to inform the station

receiving the DISC that the sender is suspending operation. No information field is permitted with the DISC command. The receiving station confirms the acceptance of DISC by the transmission of a UA response. Previously transmitted I frames that are unacknowledged when this command is actioned remain unacknowledged.

The UA unnumbered response is used to acknowledge the receipt and acceptance of the U format commands. No information field is permitted with the UA response.

The DM unnumbered response is used to report a status where a station is logically disconnected from the link, and is in the disconnected phase. The DM response may be sent in this phase to request a set mode command, or, if sent in response to the reception of a set mode command, to say that the station is still in the disconnected phase and cannot action the set mode command. No information field is permitted with the DM response.

The FRMR response is used to report an error condition not recoverable by retransmission of the identical frame; i.e., one of the following conditions, which results from the receipt of a frame without FCS error:

- the receipt of a command or response that is invalid or not implemented;

- the receipt of an I-frame with an information field which exceeds the maximum established length:

- 3) the receipt of an invalid N(R);

- the receipt of a frame with an information field which is not permitted or the receipt of an S or U frame with incorrect length.

An invalid N(R) is defined as one which points to an I-frame which has previously been transmitted and acknowledged or to an I-frame which has not been transmitted and is not the next sequential I-frame pending transmission.

An information field which immediately follows the control field, and consists of 3 octets, is returned with this response and provides the reason for the FRMR response. This format is given in Figure 4 below.

Figure 4: FRMR information field format Information field bits

| 1234567                               | 89 | 10 11 12 | 2 13 -     | 14 15 16 | 3 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

|---------------------------------------|----|----------|------------|----------|------|----|----|----|----|----|----|----|

| Rejected<br>frame<br>control<br>field | 0  | V(S)     | (See Note) | V(R)     | w    | x  | Υ  | z  | 0  | 0  | 0  | 0  |

- Rejected frame control field is the control field of the received frame which caused the command (frame) reject.

- V(S) is the current send state variable value at the station reporting the rejection condition (bit 10 = low order bit).

- V(R) is the current receive state variable value at the station reporting the rejection condition (bit 14 = low order bit).

- W set to 1 indicates that the control field received and returned in bits 1 through 8 was invalid or not implemented.

- X set to 1 indicates that the control field received and returned in bits 1 through 8 was considered invalid because the frame contained an information field which is not permitted or is an S or U frame with incorrect length. Bit W must be set to 1 in conjunction with this bit.

- Y set to 1 indicates that the information field received exceeded the maximum established capacity of the station reporting the rejection condition.

- Z set to 1 indicates that the control field received and returned in bits 1 through 8 contained an invalid N(R).

Note - For FRMR, bits 9 and 21 to 24 shall be set to 0. Bit 13 shall be set to 1 if the frame rejected was a response, and set to 0 if the frame rejected was a command.

## 2.6 EXCEPTION CONDITION REPORTING AND RECOVERY

The error recovery procedures which are available to effect recovery following the detection/occurrence of an exception condition at the link level are described below. Exception conditions described are those situations which may occur as the result of transmission errors, device malfunction or operational situations.

A busy condition results when a station is temporarily unable to continue to receive I-frames due to internal constraints, e.g., receive buffering limitations. In this case an RNR frame is transmitted from the busy station. I-frames pending transmission may be transmitted from a busy station.

An N(S) sequence exception condition occurs in the receiver when an I-frame received error-free (no FCS error) contains an N(S) which is not equal to the receive state variable at the receiver. The receiver does not acknowledge (increment its receive state variable) the I-frame causing the sequence error, or any I-frames which may follow, until an I-frame with the correct N(S) is received. The information field of all I-frames whose N(S) does not equal the receive state variable will be discarded.

A station receiving one or more I-frames having sequence errors but otherwise error free accepts the control information contained in the N(R) field and the P bit to perform link control functions; e.g., to receive acknowledgement of previously transmitted I-frames. Therefore, the retransmitted I-frame may contain an N(R) field and P bit that are updated from, and therefore different from, the ones contained in the originally transmitted I-frame.

The REJ is used to initiate an exception recovery (retransmission) following the detection of a sequence error. Only one "sent REJ" exception condition from a station is established at a time. A sent REJ exception condition is cleared when the requested I-frame is received. A station receiving REJ initiates sequential (re-) transmission of I-frames starting with the I-frame indicated by the N(R) obtained in the REJ frame.

If a station, due to a transmission error, does not receive (or receives and discards) a single I-frame or the last I-frame in a sequence of I-frames, it will not detect an out-of-sequence exception condition and therefore will not transmit REJ. The station that transmitted the unacknowledged I-frame(s), following the completion of a system specified time-out period, takes recovery action as described in section 2.8 to determine at which I-frame retransmission must begin.

## 2.7 LINK SET UP AND DISCONNECTION

Should a station wish to set up the link, it sends an SABM command to which it expects a UA response.

Should a station wish to disconnect for any reason, it sends a DISC command, to which it expects a UA or DM response.

## 2.8 USE OF POLL BIT

One use of the Poll bit (P) is in conjunction with Time-Out Recovery. Timer T1 is started at the beginning of a transmitted command provided it has not been previously started. If T1 runs out, the command will be retransmitted with P=1. If T1 runs out again, the command will again be retransmitted, with P=1 up to N2 times. At N2 + 1, an error interrupt will occur. If the command was an S-frame, the WD2511A will reset the link by transmitting a SABM. If the command was a SABM, the WD2511A will send a DISC. If a DISC, the WD2511A will continue to send a DISC indefinitely until the remote station responds.

## 2.9 TRANSMISSION OF ABORT

An Abort (seven contiguous 1's) is transmitted to terminate a frame in such a manner that the receiving station will ignore the frame. There are two conditions which will cause the WD2511A to transmit an ABORT.

- 1. Transmitter Under-Run

- 2. While transmitting a packet, a REJ is received.

## 2.10 LAPB PROCEDURE

The Link Access Procedure Balanced (LAPB) is described in CCITT Recommendation X.25 as the Level

2 protocol for the Asynchronous Balanced Mode (ABM).

The DTE is the Data Terminal Equipment and the DCE is the Data Circuit Termination Equipment (the network side of the DTE-DCE connection).

Unlike the earlier Master/Slave Protocols, the DTE and DCE are each "combined" stations in that each can transmit and receive commands and responses. Whether a particular frame is to be taken as a Command or a Response is determined by the contents of the address field. Commands from the DCE and the associated responses from the DTE use address A (hex 03). Commands from the DTE and the associated responses from the DCE use address B (hex 01).

Refer to CCITT Recommendation X.25, 1980 (Yellow Book) for more details on the X.25 LAPB protocol itself. Appendix D contains additional information pertaining to the WD2511A's specific implementation. The individual commands and responses are summarized in Table 2.

#### 2.11 THE DIFFERENCE BETWEEN LAP AND LAPB

In March 1976, the CCITT adopted Recommendation X.25 as an interface standard for public packet-switching networks. The link level procedure adopted was called Link Access Procedure (LAP) and used the HDLC Asynchronous Response Mode (ARM). However, ARM was not designed for peer-to-peer communications so LAP had some subtle problems. Therefore, in 1977, when Provisional Recommendation X.25 was adopted, a procedure called LAPB was added. LAPB is Link Access Procedure-Balanced and operates under the HDLC Asynchronous Balanced Mode (ABM). Unfortunately, the 1977 LAPB lacked good symmetry between the DTE and DCE, and was unworkable.

In the April 1979 CCITT meeting, the LAPB was greatly enhanced, especially in the DTE/DCE symmetry. This enhanced version was approved in the February 1980 Plenary meeting of the CCITT. We now have a good, workable LAPB standard. LAPB is a superior procedure and the usage of LAP is being replaced with LAPB.

| FRAME TYPE         | COMMAND             | RESPONSE |   |      |     | BIT | # |      |   |   |

|--------------------|---------------------|----------|---|------|-----|-----|---|------|---|---|

|                    |                     |          | 7 | 6    | _ 5 | 4   | 3 | 2    | 1 | 0 |

| INFORMATION<br>(I) | I-FRAME<br>(PACKET) |          |   | N(R) |     | Р   |   | N(S) | ) | 0 |

| UNNUMBERED         | SABM                |          | 0 | 0    | 1   | Р   | 1 | 1    | 1 | 1 |

| (U)                | DISC                |          | 0 | 1    | 0   | Р   | 0 | 0    | 1 | 1 |

|                    |                     | UA       | 0 | 1    | 1   | F   | 0 | 0    | 1 | 1 |

|                    |                     | FRMR     | 1 | 0    | 0   | F   | 0 | _1   | 1 | 1 |

|                    |                     | DM       | 0 | 0    | 0   | F   | 1 | 1    | 1 | 1 |

| SUPERVISORY        | RR                  | RR       |   | N(R) |     | P/F | 0 | 0    | 0 | 1 |

| (S)                | RNR                 | RNR      |   | N(R) |     | P/F | 0 | 1    | 0 | 1 |

|                    | REJ                 | REJ      |   | N(R) |     | P/F | 1 | 0    | 0 | 1 |

LAPB Commands and Responses (Bit 0 is transmitted first). Only the FRMR and I-frame contain I-fields.

## Table 2. FRAME TYPES

- N(S) Transmitter send sequence number (bit 2 = low order bit)

- N(R) Transmitter receive sequence number (bit 6 = low order bit)

- S Supervisory function bit

- M Modifier function bit

- P/F Poll bit when issued as a command, final bit when issued as a response (1 = Poll/Final)

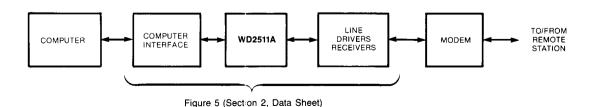

Figure 5. SYSTEM CONNECTION INTERFACE

## 3.0 REGISTER DESCRIPTION

Figure 5 shows how the WD2511A interfaces to other system components.

The WD2511A is controlled and monitored by sixteen I/O registers. Control, status, and error bits will be referred to as CR, SR, or ER, respectively, along with two digits. For example, SR16 refers to status register #1 and bit 6, which is "XBA."

**Table 3. REGISTER DEFINITION**

| REG<br># | IA3 | IA2 | IA1 | IA0 | REGISTER          | REGISTER<br>GROUPING |

|----------|-----|-----|-----|-----|-------------------|----------------------|

| 0        | 0   | 0   | 0   | 0   | CR0               |                      |

| 1 '      | 0   | 0   | 0   | 1   | CR1               | OVERALL CONTROL      |

| 2        | 0   | 0   | 1   | 0   | *SR0              | AND                  |

| 3        | 0   | 0   | 1   | 1   | *SR1              | MONITOR              |

| 4        | 0   | 1   | 0   | 0   | *SR2              | Mornion              |

| 5        | 0   | 1   | 0   | 1   | *ER0              |                      |

| 6        | 0   | 1   | 1   | 0   | *CHAIN MONITOR    | RECEIVER             |

| 7        | Ö   | 1   | 1   | 1   | *RECEIVED C-FIELD | MONITOR              |

| 8        | 1   | 0   | 0   | 0   | T1                | TIMER                |

| 9        | 1   | Ö   | 0   | 1   | N2/T1             | TIMER                |

| Α        | 1   | 0   | 1   | 0   | TLOOK HI          |                      |

| В        | 1   | 0   | 1   | 1   | TLOOK LO          | DMA SET-UP           |

| č        | 1   | 1   | 0   | 0   | CHAIN/BUFFER SIZE | DIVIA SEI-UP         |

| Ď        | 1   | 1   | 0   | 1   | NOT USED          |                      |

| Е        | 1   | 1   | 1   | 0   | XMT COMMAND "E"   | "A" FIELD            |

| F        | 1   | 1   | 1   | 1   | XMT RESPONSE "F"  | "A" FIELD            |

<sup>\*</sup>USER READ ONLY. (Write Not Possible)

## NOTE:

Registers 8 through F should be set-up while MDISC = 1.

Table 4. CONTROL, STATUS, ERROR REGISTERS

|          | BIT # |      |                    |                |              |      |      |       |  |  |  |  |

|----------|-------|------|--------------------|----------------|--------------|------|------|-------|--|--|--|--|

| REGISTER | 7     | 6    | 5                  | 4              | 3            | 2    | 1    | 0     |  |  |  |  |

| CR0      | ADISC | 0    | H/F                | ACTIVE PASSIVE | LOOP<br>TEST | RAMT | RECR | MDISC |  |  |  |  |

| CR1      | TXMT  | TRCV | XI                 | ADRV           | 0            | 0    | 0    | SEND  |  |  |  |  |

| SR0      | NA2   | NA1  | NA0                | RNRR           | NB2          | NB1  | NB0  | RNRX  |  |  |  |  |

| SR1      | 1PKR  | 1XBA | <sup>1</sup> ERROR | 0              | NE2          | NE1  | NE0  | 0     |  |  |  |  |

| SR2      | T1OUT | IRTS | REC<br>IDLE        | 0              | 0            | 0    | 0    | LINK  |  |  |  |  |

| ER0      | ER07  | ER06 | ER05               | ER04           | ER03         | ER02 | ER01 | ER00  |  |  |  |  |

<sup>1</sup>Causes interrupt (INTR Goes Low).

## 3.1 CONTROL REGISTERS (CR0/CR1)

Table 5. CONTROL REGISTER 0

| REGISTER | CR07                   | CR06                                                                                                                                                                                                                                                                                                                                                                 | CR05          | CR04                                          | CR03           | CR02          | CR01          | CR00                            |  |  |  |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------|----------------|---------------|---------------|---------------------------------|--|--|--|

| CR0      | ADISC                  | 0                                                                                                                                                                                                                                                                                                                                                                    | H/F           | ACTIVE<br>PASSIVE                             | LOOP<br>TEST   | RAMT          | RECR          | MDISC                           |  |  |  |

| ВІТ      |                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |               |                                               |                |               |               |                                 |  |  |  |

| CR00     | causes the protocol. S | MDISC (Mandatory Disconnect command). After Master Reset MDISC will be set. Clearing MDISC causes the W2511A to move to its initialization state where it will be ready to activate the Link Layer protocol. Setting MDISC causes the chip to send one or more DISC frames to disconnect the link. No DMA accessed data will be transferred as long at MDISC is set. |               |                                               |                |               |               |                                 |  |  |  |

| CR01     | RECR (Rethe WD25       | RECR (Receiver Ready). Indicates the CPU's receiver buffer is Ready (CR01 = 1). If RECR = 1, the WD2511A may begin receiving I-frames. (See SR00)                                                                                                                                                                                                                    |               |                                               |                |               |               |                                 |  |  |  |

| CR02     | RAMT (RA               | M Test). This                                                                                                                                                                                                                                                                                                                                                        | bit activates | an internal re                                | gister test. R | lefer to SELF | TESTS secti   | on for details.                 |  |  |  |

| CR03     | receiver in            | put pins RD                                                                                                                                                                                                                                                                                                                                                          | an RC are t   | connect the<br>then logically<br>d must be eq | disconnecte    | ed from the i | nternal circu | ita input. The<br>itry. The "E" |  |  |  |

| CR04     | initiate the           | ACTIVE/PASSIVE. Once MDISC has been cleared this bit takes effect. When set, the WD2511A will initiate the link up procedures; when cleared, it will wait for a link up command or DM response from the remote station. (See Note)                                                                                                                                   |               |                                               |                |               |               |                                 |  |  |  |

| CR05     |                        | H/F. Selects full duplex if CR05 = 0 and half duplex if CR05 = 1 (See Appendix B for half-duplex operation)                                                                                                                                                                                                                                                          |               |                                               |                |               |               |                                 |  |  |  |

| CR06     | Reserved,              | should be 2                                                                                                                                                                                                                                                                                                                                                          | Zero          |                                               |                |               |               |                                 |  |  |  |

| CR07     | will be trai           | Reserved, should be Zero  ADISC. Used when CR04 = 1 (ACTIVE). When the WD2511A actively initiates link set-up, a DISC will be transmitted and acknowledged prior to transmission of the SABM if CR07 = 0. If CR07 = 1, The WD2511A will send only the SABM. (see Note)                                                                                               |               |                                               |                |               |               |                                 |  |  |  |

## NOTE:

Changes to CR07 and CR04 only take affect when the chip is disconnected (MDISC = 1).

Table 6. CONTROL REGISTER 1

| BIT     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

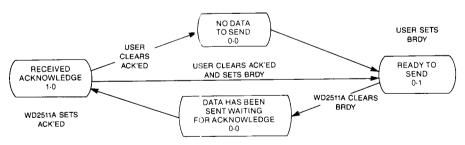

| CR10    | SEND. The SEND bit is used to command the WD2511A to send one or more packets of user data. If SEND is set, the WD2511A will read from TLOOK the BRDY bit of the next segment to be transmitted. If BRDY is clear, the Send bit will be cleared, and no transmission of user data takes place. If BRDY is set, however, the WD2511A will read TSADR and TCNT from that TLOOK segment and transmit the data accordingly. |

|         | After transmitting the data, the WD2511A clears BRDY of the segment just sent and reads BRDY for the next TLOOK segment. If BRDY is set, the user data is sent as above. If BRDY is not set, the SEND bit is cleared and transmission of user data stops until SEND is set again. As a matter of good practice, SEND should be set each time a BRDY bit is set.                                                         |

| CR11-13 | Reserved – should be zeros.                                                                                                                                                                                                                                                                                                                                                                                             |

| CR14    | ADRV. The Address Valid bit is the control for the 16-bit output addresses (A0-A15). If ADRV is clear, the outputs are tri-state and are in Hi-z (except when DACK is low). If ADRV is set, the outputs are always low impedance (TTL) and are forced hi-level (logical 1) when DRQ0, DRQ1, and DACK are all high.                                                                                                      |

| CR15    | $\overline{XI}$ . This bit is used in conjunction with CR17 (TXMT) for transparent mode transmission. If $\overline{XI}$ is clear, the frame to be sent has an I-field, i.e. is 3 or more bytes long; if XI is set, the frame is 2 bytes long. (excluding FCS and Flag). (See Note)                                                                                                                                     |

| CR16    | TRCV. The Transparent Receive bit, when set, causes the WD2511A to pass all received unknown frames to the user. (See Note)                                                                                                                                                                                                                                                                                             |

| CR17    | TXMT. The Transparent Transmit bit, when set, allows the user to build a frame for the WD2511A. (See Note).                                                                                                                                                                                                                                                                                                             |

## NOTE:

Refer to Appendix A for a complete description of Transparent MODE.

## 3.2 STATUS REGISTERS (SR0/SR1/SR2)

## Table 7. STATUS REGISTER 0

| REGISTER  | SR07     | SR06                                                       | SR05                          | SR04                          | SR03                    | SR02            | SR01        | SR00         |  |

|-----------|----------|------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------|-----------------|-------------|--------------|--|

| SR0       | NA2      | NA1                                                        | NA0                           | RNRR                          | NB2                     | NB1             | NB0         | RNRX         |  |

| BIT       |          |                                                            |                               | DESC                          | RIPTION                 |                 |             |              |  |

| SR00      | RNRX. Ar | n RNR has be                                               | een transmit<br>are available | ted or will be<br>and leave i | at the next o<br>t set. | pportunity. T   | he CPU sho  | uld set RECR |  |

| SR03-SR01 | NB2-NB0  | . Next block                                               | to be transr                  | nitted. (See I                | Note)                   |                 |             |              |  |

| SR04      |          | his bit is set<br>r UA is recei                            |                               | IR frame is re                | eceived. Onc            | ce set, it is c | leared when | an RR, REJ   |  |

| SR07-SR05 | NA2-NA0  | NA2-NA0.Next block of transmitted data to be acknowledged. |                               |                               |                         |                 |             |              |  |

## NOTE:

Values zero through 7 correspond to NS in the control field of transmitted information frames. When reading the values in SR0, read the value until 2 consecutive reads produce identical values.

## Table 8. STATUS REGISTER 1

| REGISTER  | SR17       | SR16         | SR15                                         | SR14         | SR13         | SR12         | SR11       | SR10                     |  |  |  |

|-----------|------------|--------------|----------------------------------------------|--------------|--------------|--------------|------------|--------------------------|--|--|--|

| SR1       | ₁PKR       | 1XBA         | ₁ERROR                                       | 0            | NE2          | NE1          | NE0        | 0                        |  |  |  |

| BIT       |            |              |                                              | DESC         | RIPTION      |              |            |                          |  |  |  |

| SR10      | 0 (not use | 0 (not used) |                                              |              |              |              |            |                          |  |  |  |

| SR13-SR11 | NE2-NE0.   | Next expec   | ted packet n                                 | umber and    | next RLOOK   | segment nu   | mber. (See | Note 2)                  |  |  |  |

| SR14      | 0 (not use | ed)          |                                              |              |              |              |            |                          |  |  |  |

| SR15      | or a signi | ficant event | bit indicates:<br>has occurred               | d. (see Note | 3)           |              | _          | the WD2511A<br>ext page. |  |  |  |

| SR16      | transmitte | ed Blocks ha | mitted block a<br>ve been ackr<br>each segme | nowledged b  | y the remote | Station. Upo | n acknowle |                          |  |  |  |

| SR17      | free and i |              | et Received) tequence acco                   |              |              |              |            |                          |  |  |  |

## Table 9. STATUS REGISTER 2

| REGISTER  | SR27        | SR26           | SR25          | SR24           | SR23           | SR22          | SR21          | SR20                        |  |  |  |

|-----------|-------------|----------------|---------------|----------------|----------------|---------------|---------------|-----------------------------|--|--|--|

| SR2       | T10UT       | IRTS           | REC<br>IDLE   | 0              | 0              | 0             | 0             | LINK                        |  |  |  |

| BIT       |             | DESCRIPTION    |               |                |                |               |               |                             |  |  |  |

| SR20      | LINK. If th | ne link is est | tablished, Ll | NK = 0. If the | ne link is log | ically discon | nected, LINE  | ζ = 1.                      |  |  |  |

| SR24-SR21 | Unused B    | Unused Bits-0. |               |                |                |               |               |                             |  |  |  |

| SR25      | REC IDLE    | . Receiver I   | dle indicates | that the W     | D2511A has     | received at I | east 15 conti | guous 1's.                  |  |  |  |

| SR26      | IRTS. Inter | •              | To-Send indi  | cates that the | transmitter i  | s attempting  | (successful o | r not) to send              |  |  |  |

| SR27      | = 1, T1 is  |                | . NOTE: Thi   |                |                |               |               | When T1OUT<br>een intervals |  |  |  |

## NOTE 1:

The three interrupt-causing bits are SR17, SR16, and SR15. Any of the three will cause an interrupt request (INTR goes low). After SR1 is read, all three bits are rest to 0, and INTR returns to high. Before exiting the interrupt service routine, re-read SR1 to insure there are no new interrupts to be processed.

## NOTE 2:

Values 0 through 7 correspond to NS in the Control field of received information frames. When reading this field, read the value until the results of 2 consecutive reads are identical.

## NOTE 3:

After MR, there exists a possibility that the chip will falsely report one transmitter underrun when MDISC is cleared. This error after MR is not significant; clear it by reading register SR1 then continue with initialization.

# 3.3 ERROR REGISTER (ER0) Table 10. ERROR REGISTER 0

| HEX VALUE | ERROR/EVENT                                                                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02        | Receiver overrun (ROR). The Receiver Register (RR) had a character to load into the FIFO but the FIFO was full. (Note 2.)                                                                    |

| 04        | Transmitter underrun (TUR). The transmitter (TR) needed a character from the Transmitter Holding Register (THR) but the THR was not ready. The frame being transmitted is aborted. (Note 2.) |

| 10        | RLOOK not ready. REC RDY bit of next segment is 0 but RECR = 1. This interrupt will no occur if RECR = 0.                                                                                    |

| 21        | Link is up. Was down.                                                                                                                                                                        |

| 22        | DISC sent. REC IDLE for time T1 x N2.                                                                                                                                                        |

| 24        | DISC sent. SABM sent N2 times without receiving UA.                                                                                                                                          |

| 30        | Received DISC or DM while link was up.                                                                                                                                                       |

| 41        | Going to next receive chain segment.                                                                                                                                                         |

| 42        | Next chain segment of the Receiver was not ready.                                                                                                                                            |

| 80        | Link reset (SABM) received.                                                                                                                                                                  |

| 88        | S-command sent N2 times without acknowledgement.                                                                                                                                             |

| C0        | Frame Reject (FRMR) received. (Note 1.)                                                                                                                                                      |

| C1        | Frame Reject (FRMR) transmitted. (Note 3.) The received C-Field (returned in the first I-field byte of the FRMR (frame) was invalid. (W)                                                     |

| C3        | Frame Reject (FRMR) transmitted. (Note 3.) The received and rejected frame contained a I-field which is not permitted with this frame type. (W,X)                                            |

| C4        | Frame Reject (FRMR) transmitted. (Note 3.) Received I-field exceeded the total amount of I-field data bytes established in Register C. (Y)                                                   |

| C8        | Frame Reject (FRMR) transmitted. (Note 3.) The received frame contained an invalid N(R) (Z)                                                                                                  |

| TEO.      | contains W.X.Y.Z.Q.Q.Q. where W is the LSB                                                                                                                                                   |

## NOTES:

- Whenever a Frame Reject (FRMR) is received, the I-field will have been placed in the next available RLOOK memory location by the DMA. A link reset (SABM) will be transmitted but no additional interrupt is generated. The NB is not advanced.

- 2. Receiver overrun and Transmitter underrun are an indication that the TC/RC clocks are either too fast for the WD2511A, or the DACK response is too slow, or both. The chip recovers from these errors the same as for line noise errors the protocol time out recovery. The host need only monitor TUR/ROR for excessive occurance. An initial TUR interrupt (at start up) is not valid and should be ignored unless it occurs a second time.

- As a result of FRMR transmitted, a SABM is received, causing link reset. In this case, only the Frame Reject interrupt is indicated.

## FRMR FORMAT

A frame reject (FRMR) contains a three byte I-field. The first byte is the rejected frame control field. The second byte contains the current N(S) and N(R) counts of the station reporting the reject condition. The third byte

contains W-X-Y-Z-0-0-0 where W is the LSB.

W indicates that the control field received and returned in the first I-field byte was invalid.

X indicates the rejected frame contained an I-field which is not permitted with this command. W is also set in this case.

Y indicates the received I-field exceeded the maximum I-field data byte count established (CHAIN/BUFFER SIZE). Y is mutually exclusive with W.

Z indicates the received control field contained an invalid N(R). Z is mutually exclusive with W.

In the FRMR I-field, bit 4 of the second byte is set if the rejected frame was a response.

Upon receiving a FRMR, the WD2511A will place the 3 byte I-field in memory by DMA, just as if the FRMR were a packet.

When the WD2511A transmits a FRMR, the frame reject condition is entered. Only a received SABM or DISC will clear this condition. If any other command is received, the WD2511A will re-transmit the FRMR. Also, the WD2511A will not transmit packets while in the frame reject condition. If no SABM is received after N2 X T1 time, the WD2511A will send a SABM.

#### 3.4 RECEIVED C-FIELD REGISTER

Register 7 contains the C-field of the last received frame, provided the A-field of the frame was equal to either register E or F, the FCS was good, the frame contained 32 or more bits, and the WD2511A is not waiting for a SABM or DISC in response to a transmitted FRMR.

## 3.5 TIMER/COUNTER REGISTER

Registers 8 and 9 define a 10-bit timer (T1) and a 6-bit Maximum Number of Transmission/Retransmissions counter (N2).

|          |     |   |    | BI | T # |     |     |     |

|----------|-----|---|----|----|-----|-----|-----|-----|

| REGISTER | 7   | 6 | 5  | 4  | 3   | 2   | 1   | 0   |

| 8        |     |   |    | T1 | •   |     |     | LSB |

| 9        |     |   | N2 |    |     |     |     |     |

|          | MSB |   |    |    |     | LSB | MSB |     |

MSB = Most Significant Bit LSB = Least Significant Bit

T1 provides the value of a delay in waiting for a response and/or acknowledgement. The delay is the binary count multiplied by time CT where:

$$CT = \frac{16384}{CLK} sec$$

Thus, if CLK = 2 MHz, then T1 may be set in increments 8,192 milliseconds, to a maximum delay of 8.39 seconds. All ones in T1 is the maximum delay.

Once the CPU establishes T1 and N2, there is no need to write into T1 and N2 again unless a master reset (MR) has occurred, there is a power loss, or the user needs to change T1 or N2. If a time-out occurs, the WD2511A will still retain T1 and N2.

The conditions for starting, stopping, or restarting T1 are shown in Figure 6. ("Re-start" means starting T1 before it ran-out).

## 3.6 ADDRESS REGISTERS

Registers E and F provide a programmable A-field. This allows the WD2511A to be a super-set of the X.25 document. That is, the WD2511A can handle a wider range of applications than the DTE-DCE links defined in X.25. These wider ranges include: DTE-to-DTE connection, multipoint, and loop-back testing. If the

WD2511A is strictly in an X.25 DTE-DCE link, use the values shown below:

DTE Register E = 01

Register F = 03

DCE Register E = 03

Register F = 01

If performing a loop-back test, either internal (CR03 = 1) or external (CR03 = 0), registers E and F should be the same.

#### 4. MEMORY ACCESS METHOD

The WD2511A memory access is accomplished by the use of DMA and two look-up tables. These tables are setup to allow up to 7 I-frames to be outstanding in each direction of the communication link. The look-up tables are divided into a transmit and a receive area. (TLOOK and RLOOK) and are located in memory external to the WD2511A.

| TLOOK |  |

|-------|--|

| RLOOK |  |

These tables contain address and control information for individual Transmit/Receive packets.

To provide the WD2511A access to TLOOK and RLOOK load only the starting address of TLOOK into the WD2511A registers A and B.

| REG A | A15 | A14 | A13        | A12       | A11 | A10        | A9 | A8 |

|-------|-----|-----|------------|-----------|-----|------------|----|----|

| REG B | A7  | A6  | <b>A</b> 5 | <b>A4</b> | АЗ  | <b>A</b> 2 | A1 | A0 |

A0-A15 16 bit TLOOK starting address

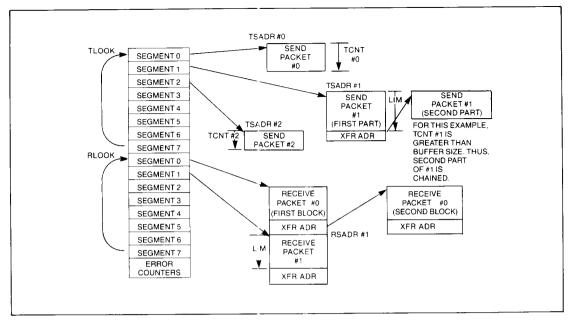

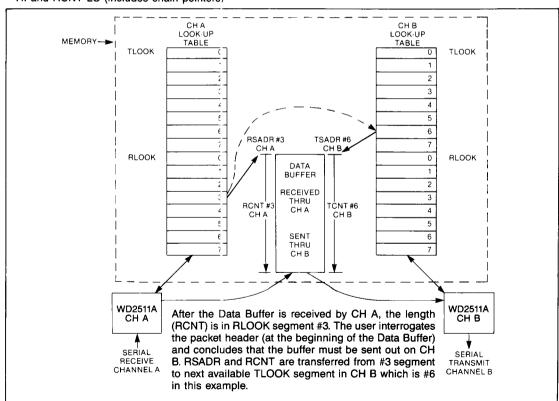

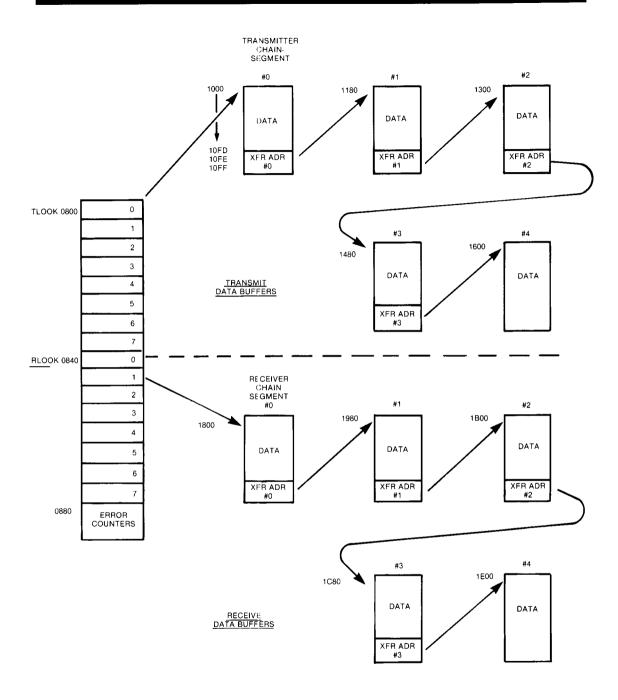

The TLOOK and RLOOK tables are each divided into 8 segments and each segment contains 8 bytes. Figure 7 illustrates the segmentation of TLOOK and RLOOK. Figures 9 and 11 illustrate the contents of a single TLOOK and RLOOK segment.

| START T1                                                                   | RE-START T1                                               | STOP T1                                    |

|----------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|

| *I-frame sent and T1 not already in progress due to previous I-frame.      | *Acknowledgement received to some, but not all, I-frames. | Acknowledgement received for all I-frames. |

| 2. —                                                                       | *RNR received while link up.                              |                                            |

| <ol> <li>*SABM or DISC sent. (N2 restarted at first occurrence)</li> </ol> | _                                                         | UA or DM Received                          |

| 4. Receiver Idle (REC IDLE = 1)                                            | *Frame sent, while REC IDLE<br>= 1                        | Detected REC IDLE = 0                      |

| 5. S — command sent                                                        |                                                           | _                                          |

\*N2 is restarted.

Figure 6. TIME OUT CONDITIONS

Figure 7. MEMORY ACCESS SCHEME

## 4.1 TRANSMIT (TLOOK)

Figure 9 details the individual segments of the TLOOK table which the user must program to cause data to be sent. The WD2511A will transmit data from host memory buffers when the next sequential TLOOK segment (starting at 0, modulo 8) has a buffer available, indicated by BRDY = 1 in TLOOK, and SEND = 1 in CR1.

The address field (TSADR) contains a 16 bit binary field pointing to the user's memory buffer. HI represents the upper 8 bits; LO the lower 8. The length field (TCNT) is a 12 bit binary field representing the length of the Information field to be sent including any Chain Pointers (refer to section 4.5 on Chaining even if you do not intend to use Chaining.)

To transmit, the WD2511A reads from TLOOK the starting address and length of the packet to be transmitted. It automatically transmits the Flag, Address, and Control fields. Next, the Information field data is transmitted from the memory buffer using DMA. At the end of the Information field, the WD2511A automatically appends the FCS and the closing Flag.

After the frame has been sent, the WD2511A will clear BRDY in the current TLOOK segment and move to the next. If BRDY is set, the process will repeat. If the WD2511A encounters a TLOOK segment where BRDY = 0, it will stop transmitting and clear SEND. To cause new buffers to be sent, the user need only set up the next sequential TLOOK segment(s), set BRDY, and then set SEND again.

After transmitting a packet, LAPB requires that an acknowledgement (ACK) be received from the remote device. ACKs are contained in the N(R) field of a received S-frame or I-frame. Upon receipt of an ACK, the WD2511A

will set the ACK'ED bit in the appropriate TLOOK segment(s) and generate a Transmitted Block Acknowledged interrupt (XBA = 1). Note that more than one packet at a time can be ACK'd by the remote. This means that more than one TLOOK's ACK'ED bit could be set on one XBA interrupt.

Before assigning a new buffer to a TLOOK segment, the user must make sure that the previous block which used the segment has been ACK'd, i.e. ACK'ED = 1.

The WD2511A sets a timer (T1) to monitor the receipt of frame acknowledgements. If the timer expires, the WD2511A will poll the remote device for its status. The WD2511A also responds to requests to resend packets that were missed or received in error. If retransmission of one or more (up to a maximum of 7 out of the 8) packets becomes necessary, the WD2511A automatically resends the required packets. The user's software does not become involved in this retransmission. An error counter is incremented when this occurs (see Error Counters, section 4.8). The status of SEND has no effect on the WD2511A's monitoring of frame acknowledgement.

Under normal operation, the user brings up the link by programming CR0. Once communication with the remote device has been established and the link has been initialized (LINK = 0), user data can be sent using the above procedures. Note, however, that if the user sets up TLOOK and sets SEND, the WD2511A will begin to send the user's data, even if LINK = 1 (Link is "down"). In this state, the WD2511A will not monitor for ACKs received and will reset itself once the Link Initialization does occur. Therefore, the user should never set SEND until after the Link is up (LINK = 0) unless operating in the Transparent mode (see Appendix A).

## 4.2 RECEIVE (RLOOK)

Figure 11 details the individual segments for the RLOOK table which the user must program to cause data to be received from the remote device. The WD2511A will DMA data to host memory buffers when the next sequential RLOOK segment (starting at 0, modulo 8) has a buffer available, indicated by REC RDY = 1 in RLOOK, and RECR = 1 in CR0.

The address field (RSADR) contains a 16 bit binary field. HI represents the upper 8 bits; LO the lower 8. The length field (RCNT) is a 12 bit binary field representing the length of the received Information field including any Chain Pointers (refer to section 4.5 on Chaining even if you do not intend to use Chaining).

To receive user data into memory, the WD2511A reads from RLOOK the starting address and length of an empty buffer. As an incoming frame is being received, it is checked for correct Address and FCS fields and for Control field content. If it is an Information frame, the Information field is placed in the empty user buffer. If it arrives without an FCS error and with the proper N(S) sequence number, the WD2511A will, in order:

- Clear REC RDY, set FRCML (frame complete), and store any received residual count for non-8 bit byte data) in byte 0 of the current RLOOK segment,

- Store the received length in bytes of the I-field in RCNT HI and RCNT LO (includes chain pointers)

- · Advance the NE count (modulo 8) in SR1,

- Generate a Packet Received (PKR) interrupt (even if the N(R) field is not valid).

Then, if the N(R) field was valid, the WD2511A prepares for the next packet by moving to the next RLOOK segment (modulo 8) and acknowledges the received I-frame at the first opportunity.

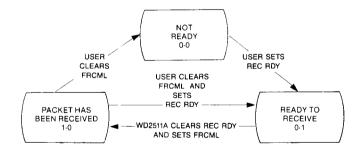

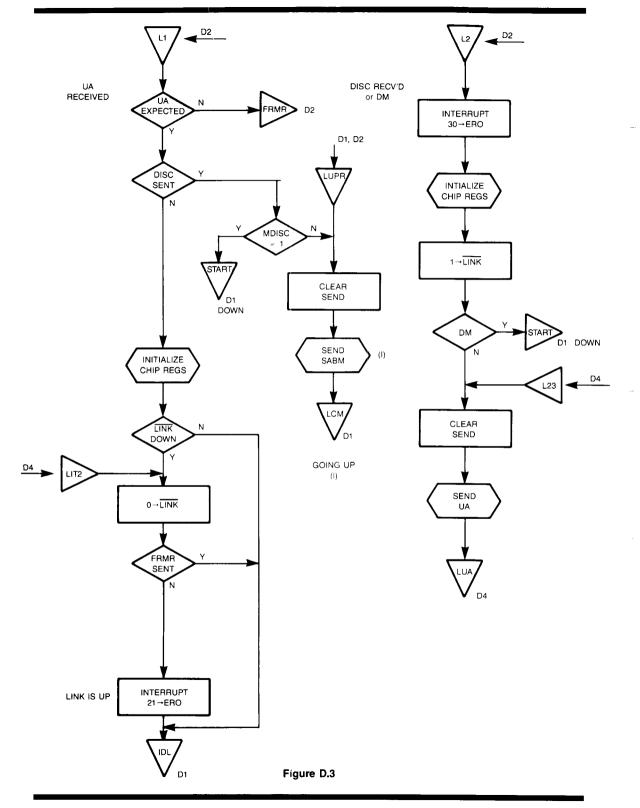

Note that if the host is processing the RLOOK entries, sequentially examining the FRCML bits, there is a possibility that the host could read the byte count of a completed frame before the chip updates it. For this reason, the RCNT HI/LO should be initialized to 0 each time a new empty buffer is stored into an RLOOK segment. Then, if the host ever reads an RCNT of 0, it should read RCNT once more.