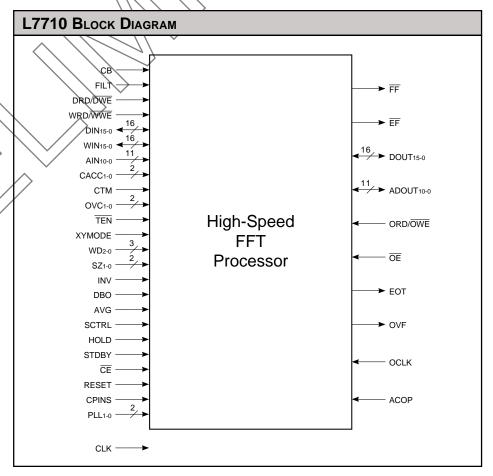

# L7710 - DragonFly <sup>™</sup> High-Speed FFT Processor

#### FEATURES

- 100 MHz Operation

- □ 3.3 Volt Power Supply

- 5 Volt Tolerant I/O

- Computes up to a 1024 Point Complex FFT in 18 µs\*, the fastest single-chip 1K Complex FFT compute time yet to date!

- 4 Programmable Complex FFT Point Sizes: 16 Point (240 ns), 64 Point (1.2 μs), 256 Point (3.4 μs), and 1024 Point (18 μs)\*\*

- Standby Modes result in Significant Power Savings while simultaneously Retaining Internal Memory Data

- Supports Both Forward and Inverse Fast Fourier Transforms

- □ Configurable as a FIR Filter with up to 1024 Complex Taps

- Device Contains Seven Built-In Windowing Functions in ROM

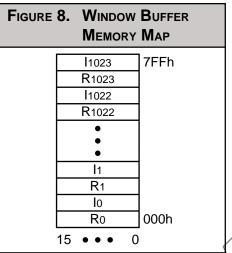

- Window Buffer (2K x 16-bit) Enables Users to Program their own Complex Window Functions through Independent Address and Data Input Lines

- 16-bit Fixed Point Data Precision (96 dB Dynamic Range) on Output with 20-bit Internal Computation Precision

- **224K-bit Internal RAM**

- □ 1.2M-bit Internal Function RQM

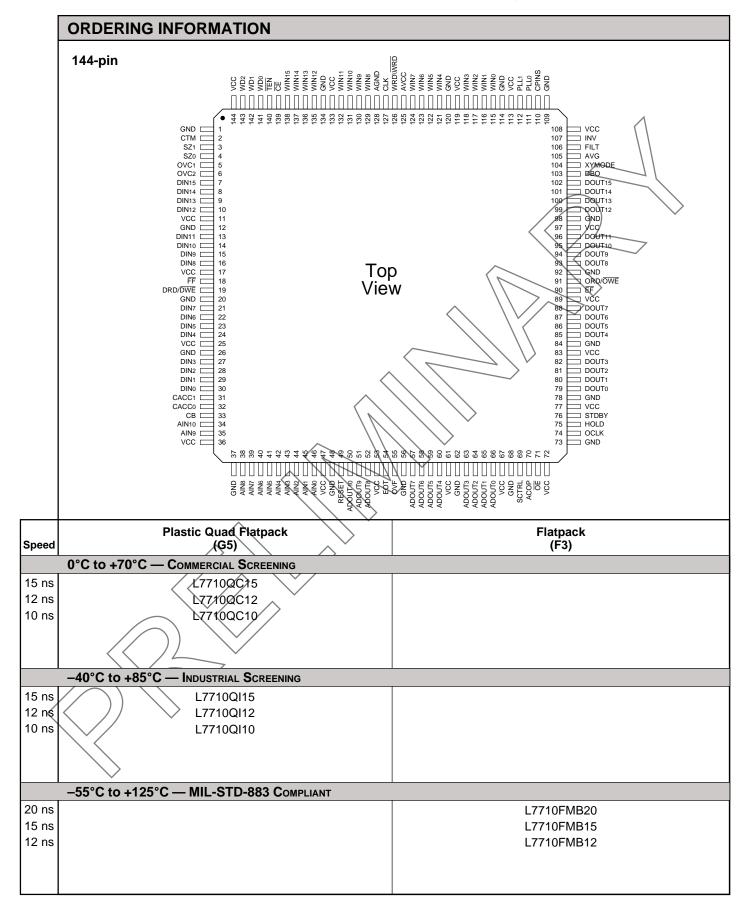

- □ Package Styles Available:

- 144-pin Plastic Quad Flatpack

- 144-pin Flatpack

- \* 1024 Complex FFT Computation time based on XY Mode with 25% Input Overlap. 1024 Complex FFT with No Overlap and Averaged Linear or Decibel Power is computed in 24 μs.

- \*\* All Computation times based on XY Mode with 25% Input Overlap.

# DESCRIPTION

The **L7710** is a high-speed Fast Fourier Transform Processor. The L7710 allows extremely fast FFT computations to take place within a single monolithic device. All data buffering and working storage required for up to a 1024 point complex FFT operation are on-chip. This eliminates the need for expensive, high-speed external memories, while decreasing internal computation time.

The interface to the device appears to the user as if it were a synchronous SRAM with all appropriate signaling.

There are several programmable options available on the device to perform complex input data windowing, forward/inverse transform, transform overlap, and exponential averaging of the output, 20-bit block floating point precision is achieved with internal scaling logic. Exact specified scaling is also an option through the use of a scaling register.

The core transform processor is comprised of a "Dragonfly" processor which computes 4-point complex transforms in approximately 10 nsec when the pipeline is fully loaded. It consists of several multipliers and adders in parallel to achieve this high, sustained computation throughput rate. Input data and twiddle factor coefficients are presented to the processor core every 10 nsec and output is clocked out at the same rate giving the processing performances indicated.

Some applications of the L7710 in the telecommunication field are: Wireless Base Stations, Satellite Communications, Software Defined Radios, Cable Modems and OFDM Applications; while some sample instrumentation applications are: Digital Spectrum Analyzers, Modulation Analyzers, and Distortion Analyzers.

#### SIGNAL DEFINITIONS

#### Power

Vcc and GND

+3.3 V power supply. All pins must be connected.

#### Clock

CLK — Master Clock

The rising edge of CLK strobes all enabled registers and input memory latches.

OCLK — Output Clock

The rising edge of OCLK strobes the output buffer memory and the following flags: EF, OVF and EOT.

#### Inputs

DIN15-0 — Data Input

DIN15-0 is the 16-bit registered data input port. This input port is actually bidirectional. Depending on the value present on CACC1-0 and DRD/DWE, this port may act as an output port. Data is latched on the rising edge of CLK, provided DRD/DWE is held LOW. The data format is two's complement.

AIN10-0 — Qata/Window Input Address

AIN10-0 is the input address bus for DIN15-0 and WIN15-0 and controlled by CACC1-0. Refer to table 5.

#### WIN15-0 — Window Input

WIN15-0 is the 16-bit registered data input port. This input port is actually bidirectional. Depending on the value present on CACC1-0 and WRD/WWE, this port may act as an output port. Data is latched on the rising edge of CLK, provided WRD/WWE is held LOW. The data format is two's complement.

#### Outputs

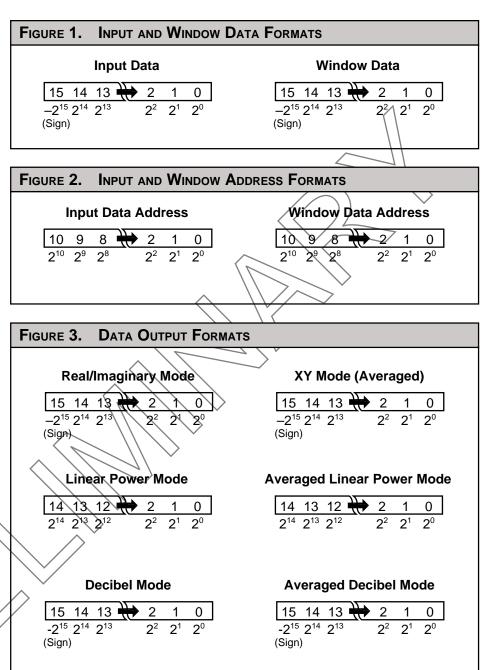

DOUT15-0 — Data Output

DOUT15-0 is the 16-bit registered data output port. See Figure 3.

#### ADOUT10-0 — Data Output Address

ADOUT10-0 provides address information for DOUT15-0. This bus is bidirectional. In Continuous Mode (CTM=1), the LF7710 outputs data

| DEVICES INCORPORATED |  |

|----------------------|--|

| TABLE 1. | OVERLAP MODE  |

|----------|---------------|

| OVC1-0   | Configuration |

| 0 0      | No Overlap    |

| 0 1      | 25 %          |

| 10       | 50%           |

| 11       | 75%           |

| TABLE 2. | WINDOW MODE        |

|----------|--------------------|

| WD2-0    | Configuration      |

| 000      | Rectangular Window |

| 001      | Bartlett           |

| 010      | Hamming            |

| 011      | Hanning            |

| 100      | Trapezoidal        |

| 101      | Blackman-Harris    |

| 110      | Welch              |

| 111      | Buffer             |

| TABLE 3. | PLL MODE    |

|----------|-------------|

| PLL1-0   | Bus Options |

| 0 0      | x1          |

| 0 1      | x2          |

| 10       | x3          |

| 11       | x4          |

output address information automatically. However, should the user desire to read out data from DOUT15-0 in any order, they may present addresses to ADOUT10-0, provided they are in Non-Continuous Mode (CTM=0).

#### EOT — End of Transform

The EOT signal goes HIGH when the transform has completed and goes LOW again when either a new  $\overline{\text{TEN}}$  is

| TABLE 5. | 5. Address Line Control (CTM = 0 & CB =0) |                               |  |  |  |

|----------|-------------------------------------------|-------------------------------|--|--|--|

| CACC1-0  | Active Loading Location                   | Active Corresponding Data Bus |  |  |  |

| 0 0      | Control Register                          | WIN15-0                       |  |  |  |

| 0 1      | Window RAM                                | WIN15-0                       |  |  |  |

| 1 0      | Data Input RAM                            | DIN15-0                       |  |  |  |

| 11       | Data Input & Window RAM                   | DIN15-0 & WIN15-0             |  |  |  |

| 1 1      |                                           | DIN13-0 & WIN13-0             |  |  |  |

| TABLE 6. | Address Line Control    | (CTM = 1 & CB=0)              |

|----------|-------------------------|-------------------------------|

| CACC1-0  | Active Loading Location | Active Corresponding Data Bus |

| 0 0      | Control Register        | WIN15-0                       |

| 0 1      | Window RAM              | WIN15-0                       |

| 10       | N/A                     | N/A                           |

| 11       | Window RAM              | WIN15-0                       |

|          |                         |                               |

| TABLE 7. BUFFER RESET (CB=1) |                        |  |  |  |  |

|------------------------------|------------------------|--|--|--|--|

| CACC1-0                      | Location to be Cleared |  |  |  |  |

| 0 0                          | Control Register       |  |  |  |  |

| 0 1                          | Window RAM             |  |  |  |  |

| 10                           | Input RAM              |  |  |  |  |

| 11                           | Output RAM             |  |  |  |  |

pulsed in Non-Continuous Mode or the window stage of the next transform is completed in Continuous Mode.

OVF — Overflow Flag

When OVF goes HIGH, this is indicative of an internal data overflow. Note: OVF will not go HIGH if SCALE has been set to the default mode, all zeros. In this mode, the device performs block floating point which acts as an automatic internal scale to prevent overflow. If SCALE is set to any value other than 0, the user should be monitor OVF.

# FF — Full Flag

FF will go LOW indicating to the user that the data input buffer is full.  $\overline{FF}$ will be asserted at all other times.  $\overline{FF}$ will automatically become asserted upon system reset.

## $\overline{EF}$ — Empty Flag

STØBY

0

0

1

1

**EF** will go LOW indicating to the user that the data output buffer is empty. **EF** will be asserted at all other times. **EF** will automatically become deasserted upon system reset.

TABLE 8. STANDBY MODES

Operation

Normal Operation

**Output Buffer Held**

Soft Standby Hard Standby

HOLD

0

1

0

1

#### Controls

#### CTM — Continuous Transform Mode

When CTM is LOW, Non-Continuous Transform operation is possible. When  $\overline{\text{TEN}}$  is pulsed LOW, the transform starts (or restarts if the previous transform was in midcomputation). When CTM is HIGH, Continuous Transform Mode is enabled, which places the device in synchronous operation. While in Continuous Transform Mode, the part acts like a "Data Pump." Data MUST be made available on the input buffers when expected and likewise, output will be shifted out in a FIFO-like

| TABLE 8 | TABLE 8. VALID COMBINATIONS OF OVERLAP MODES (OVC1-0) AND PLL MODES (PLL1-0) FOR CTM=1 |        |                          |        |                          |  |

|---------|----------------------------------------------------------------------------------------|--------|--------------------------|--------|--------------------------|--|

| Full    | Complex Transform                                                                      | F      | Real Transform           | Ima    | aginary Transform        |  |

| OVC1-0  | PLL1-0 Mode x1 (100 MHz)                                                               | OVC1-0 | PLL1-0 Mode x1 (100 MHz) | OVC1-0 | PLL1-0 Mode x1 (100 MHz) |  |

| 00      | Valid Operation                                                                        | 00     | Valid Operation          | 00     | Valid Operation          |  |

| 01      | Valid Operation                                                                        | 01     | Valid Operation          | 01     | Valid Operation          |  |

| 10      | Valid Operation                                                                        | 10     | Valid Operation          | 10     | Valid Operation          |  |

| 11      | Valid Operation                                                                        | 11     | Valid Operation          | 11     | Valid Operation          |  |

| OVC1-0  | PLL1-0 Mode x2 (50 MHz)                                                                | OVC1-0 | PLL1-0 Mode x2 (50 MHz)  | OVC1-0 | PLL1-0 Mode x2 (50 MHz)  |  |

| 00      | Data Starvation                                                                        | 00     | Valid Operation          | 00     | ) Valid Operation        |  |

| 01      | Data Starvation                                                                        | 01     | Valid Operation          | 01     | Valid Operation          |  |

| 10      | Valid Operation                                                                        | 10     | Valid Operation          | 10     | Valid Operation          |  |

| 11      | Valid Operation                                                                        | 11     | Valid Operation          | 11     | Valid Operation          |  |

| OVC1-0  | PLL1-0 Mode x3 (33 MHz)                                                                | OVC1-0 | PLL1-0 Mode x3 (33 MHz)  | OVE1-0 | PLL1-0 Mode x3 (33 MHz)  |  |

| 00      | Data Starvation                                                                        | 00     | Data Starvation          | 00     | Data Starvation          |  |

| 01      | Data Starvation                                                                        | 01     | Data Starvation          | 01     | Data Starvation          |  |

| 10      | Data Starvation                                                                        | 10     | Valid Operation          | 10     | Valid Operation          |  |

| 11      | Valid Operation                                                                        | 11     | Valid Operation          | 11     | Valid Operation          |  |

| OVC1-0  | PLL1-0 Mode x4 (25 MHz)                                                                | OVC1-0 | PLL1-0 Mode x4 (25 MHz)  | OVC1-0 | PLL1-0 Mode x4 (25 MHz)  |  |

| 00      | Data Starvation                                                                        | 00     | Data Starvation          | 00     | Data Starvation          |  |

| 01      | Data Starvation                                                                        | 01     | Data Starvation          | 01     | Data Starvation          |  |

| 10      | Data Starvation                                                                        | 10     | Valid Operation          | 10     | Valid Operation          |  |

| 11      | Valid Operation                                                                        | 11     | Valid Operation          | 11     | Valid Operation          |  |

autonomous fashion. Note: In either mode, the user should follow the recommended combinations of Overlap Modes (OVC1-0) and PLL Modes (PLL1-0) in order to avoid unexpected data on the output. See Table 8.

## TEN — Transform Enable Control

When the device is in Continous Transform Mode (CTM=1), TEN should be held LOW. When the device is in Non-Continuous Mode (CTM=0), TEN can be pulsed LOW to start a transform. Should TEN be pulsed LOW in the middle of a transform computation, the transform will restart.

# HOLD — Hold Output Buffer Data

Holds output buffer contents steady while HOLD is held HIGH. When HOLD is held LOW, the output buffer allows data to be changed. When the device is in Standby Mode, the data in all the buffers is static, regardless of the status of HOLD. If HOLD and STDBY are HIGH, the device is in a "hard standby mode". Refer to table 8 for standby modes.

#### SCTRL — Scale Control

When SCTRL is LOW, scaling is automatically handled internally through block floating point. When SCTRL is HIGH, scaling is achieved through the scaling registers and is under user control.

#### DBO — Linear Power/dB Output

When DBO is HIGH, dB Output format is selected. When DBO is LOW, Linear Power format is selected. See Table 9.

#### XYMODE — XY Mode

When XYMODE is HIGH, the device is in XY Mode. The output mode can be either Real/Imaginary or XY Mode (Averaged), depending on the value of AVG. If XYMODE is LOW the device is in Power Mode. The output can be in one of the following modes: Linear Power, Decibel, Averaged Linear Power, and Averaged Decibel Power.

# XX • • • XX 7FFh • • XX • • • XX 004h ALPHA 003h SCALE 002h

AVG — Average Real and Imaginary

CR1

CR0

15 • • •

001h

000h

0

When AVG is enabled, Exponential Window Averaging on Power is performed. See Table 9.

FILT — FFT/FIR Operation Mode

When FILT is held LOW, the device is in FFT Mode. When FILT is held HIGH, the device is in FIR Mode.

#### WD2-0 — Window Configuration

WD2-0 is the 3-bit Window Configuration mode select which determines the type of Window used and is selected from the seven predefined configurations stored in the Window Configuration ROM or user-definable Window RAM. See Table 2. INV — Forward/Inverse Transform Control

When INV is LOW, Forward Transform is selected. When INV is HIGH, Inverse Transform is selected. This signal is internally automatically controlled when the device is in Filter Mode.

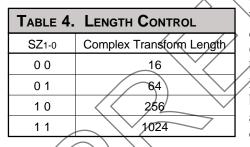

SZ1-0 — Complex Transform Length

SZ1-0 is the 2-bit Transform Length selector and is selected from the four predefined configurations. See Table 4.

OVC1-0 — Overlap Control

OVC1-0 is the 2-bit Overlap Control which determines the type of overlap used and is selected from the four predefined configurations. See Table 1.

PLL1-0 — PLL Mode

PLL1-0 is the 2-bit PLL mode selector and is selected from the four predefined configurations. See Table 3.

CACC1-0 — Control Access

CACC10 determines the active buffer loading location (i.e. Control Register, Window RAM and/or Data Input RAM) depending on the value of CTM. It also determines the buffer location to be cleared depending on the value of CB. For instance, in order for the user to read the Control Register 1, CACC1-0 should be set to 00. The value 001h would then be loaded through AIN10-0. Data from Control Register 1 would then be made available at WIN15-0. Refer to Tables 5-7 for CACC1-0 mapping. See Figure 4 for the Control Register Map. See Figures 5 and 6 for Control Register 0 and Internal Mapping.

**High-Speed FFT Processor**

# CPINS — Control Pins

CPINS changes control from the external control pins to the control registers. If CPINS is HIGH, control of the device is determined by the external control pins. If CPINS is LOW, control of the device is determined by the internal control registers.

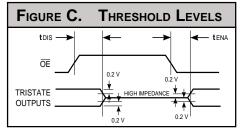

# $\overrightarrow{OE} \rightarrow Output Enable$

Data is available on the output port (DOUT15-0) on the falling edge of CLK while  $\overline{OE}$  is held LOW. When  $\overline{OE}$  is HIGH, DOUT15-0 is placed in a high-impedance state. CLKOUT is not affected by  $\overline{OE}$ .

#### DRD/DWE — Data Read/Write Enable

If DRD/ $\overline{\text{DWE}}$  is held LOW while CE is held LOW, data on DIN15-0 is written to the corresponding location associated with CACC1-0 on the rising edge of CLK. If DRD/ $\overline{\text{DWE}}$  is HIGH while

| FIGURE 5. CONTROL REGISTER 0 MAPPING |         |                   |             |                |              |           |           |           |          |             |           |            |           |          |          |

|--------------------------------------|---------|-------------------|-------------|----------------|--------------|-----------|-----------|-----------|----------|-------------|-----------|------------|-----------|----------|----------|

| 0                                    | 0       | EQT<br>13         | OVF<br>12   |                | WD2<br>10    | WD1<br>9  | WDo<br>8  | FILT<br>7 | AVG<br>6 | XYMODE<br>5 | DBO<br>4  | SCTRL<br>3 | HOLD<br>2 | TEN<br>1 | СТМ<br>0 |

| RESER                                | VED BIT | <b>8</b> : 15, 14 |             |                |              | EOT       | AND O     | VF ARE    | ONLY R   | EAD-ON      | LY BITS   | 6, THE R   | EST RE    | AD-WRI   | TEABLE   |

|                                      |         |                   |             |                |              |           |           |           |          |             |           |            |           |          |          |

| Figure                               | 6. Co   | NTROL             | REGIST      | rer <b>1 N</b> |              | G         |           |           |          |             |           |            |           |          |          |

| FIGURE                               | 6. Co   | NTROL<br>0        | Regist<br>0 | <b>TER 1 N</b> | <b>APPIN</b> | G<br>PLL1 | PLL0      | 0         | 0        | OVC1        | OVC0      | 0          | 0         | SZ1      | SZ0      |

|                                      |         |                   |             |                |              |           | PLL0<br>8 | 0         | 0        | OVC1<br>5   | OVC0<br>4 | 0          | 0         | SZ1      | SZ0<br>0 |

# Logic Products

$\overline{\text{CE}}$  is LOW, DIN15-0 is placed in an output mode in order to read data. If  $\overline{\text{CE}}$  is HIGH, DIN15-0 is tri-stated.

#### WRD/WWE — Window Read/Write Enable

If WRD/WWE is held LOW while CE is held LOW, data on WIN15-0 is written to the corresponding location associated with CACC1-0 on the rising edge of CLK. If WRD/WWE is HIGH while  $\overline{CE}$  is LOW, DIN15-0 is placed in an output mode in order to read data. If  $\overline{CE}$  is HIGH, DIN15-0 is tri-stated.

#### $\overline{CE}$ — Chip Enable

If  $\overline{CE}$  is LOW, DIN15-0 and WIN15-0 are active as either input or output ports determined by DRD  $\overline{DWE}$  and WRD  $\overline{WWE}$ . If CE is HIGH, both ports are tri-stated Only WIN15-0 is affected when CTM=1.

CB — Clear Buffer

Clears the Input Buffer, Output Buffer, Control Register or Window Buffer to all zeros when pulsed HIGH for one clock cycle depending on the value present at CACC1-0. WC has no effect. Refer to table 7 for buffer selection.

#### STDBY — Standby Mode

By asserting STDBY to HIGH, the device is placed in a standby state. Power consumption drops, due to the

fact that FFT engine has been powered down. The data in all the buffers is static, regardless of the status of HOLD. If both STDBY and HOLD are held HIGH, additional power savings is achieved by the powering down of the PLL, or going into a "hard standby mode". To return from a the hard standby state, the user must drop HOLD to a logic LOW and wait at least a tPLL time in order to allow the PLL to restart before dropping STDBY. Refer to table 8 for standby modes.

#### ACOP — Automatic Continuous Operation

The ACOP signal automatically controls the FFT engine based on the user read-rate of the output buffer when in continous transfer mode. ACOP allows the device to guarantee succesive completed transforms without loss of output data and user intervention, i.e. HOLD and/or STDBY going high. When ACOP = 1and CTM = 1, the output buffer will not be written over until the empty flag, EF, is asserted. However, the input buffer may go full, i.e. the FF flag is asserted, waiting for the user to read the output buffer. The HOLD signal is not necessary when ACOP and CTM are active, except for standby modes. ACOP is not valid when CTM = 0.

# **High-Speed FFT Processor**

#### RESET — System Reset

The RESET signal resets all pointers to all buffers, however it does not reset any RAM, with the exception of the control registers. All values inside Control Registers 0 and 1 are reset to zero in addition to both the Alpha and Scale Registers.

#### USER ACCESSIBLE RESOURCES

#### Data I/O Interface Description

When FILT is held LOW, the device is in FFT Mode. When FILT is held HIGH, the device is in FIR Mode.

Real and imaginary data enter the device through an "SRAM-style" interface, which is synchronous with the CLK signal. Input data (to both the input and window buffers) is clocked in on the rising edge of CLK when both DRD/DWE and WRD/ WWE are held LOW. Output is clocked out on the falling edge of CLK while  $\overline{OE}$  is held LOW, acting much like a FIFO to the user.

#### **Continuous Transform Mode**

In Continuous Transform Mode (CTM=1), the device I/O is clocked in synchronism with the PLL mode (PLL1-0) and the overlap mode (OVC1-0). For example, if the PLL mode is x2 (PLL1-0=01), and overlap is in 50% overlap (OVC1-0=10) and the clock input is 50 MHz, then synchronous data should be clocked into the device at a 50 MHz input rate according to the input memory map and the size of the transform specified.

There will be 2N (N is specified by SZ1-0 in Table 4) locations which are automatically sequenced for both input and output, beginning with zero, and appear at their respective address lines. This allows the device to be directly interfaced to a parallel type A/D converter at the input or to a parallel DAC, Digital Signal Processor or DMA controller at the output. Output data is memory mapped

according to the output mode selected (see Figures 10 and 11). Output is streamed through the use of an onboard FIFO to the DOUT15-0 pins, following an address present on ADOUT10-0 for the given address setup time and  $\overline{OE}$  asserted LOW. Illegal combinations of PLL Modes and OVC Modes with CTM=1 are shown in Table 8. EOT will be generated after the first output is received into the internal output buffer. This is designed to prevent user access prior to any post transform computations, such as log or averaging operations. Addresses of input data are automatically generated in consideration of the overlap mode.

#### Non-Continuous Transform Mode

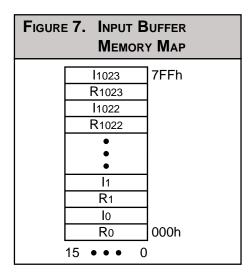

In non-continuous mode (CTM=0), the user has direct control over addressing the input and output data. The user is free to place data anywhere in the 2K input memory map by writing to its corresponding memory location directly according the input buffer memory map (See Figure 7). Data on the DIN15-0 and WIN15-0 pins are latched into the buffer memories via the use of DRD/DWE and WRD/ WWE along with CE. With CE held  $LOW, DRD/\overline{DWE}$  or  $WRD/\overline{WWE}$  (or both) are used to latch the data into the corresponding internal SRAM buffers at the address specified by the individual address lines, AIN10-0.

| TABL | е <b>9. О</b> итри | т Мор | ES FOR COMBINATIONS OF AVG, XYMODE AND DBO       |

|------|--------------------|-------|--------------------------------------------------|

| AVG  | XYMODE             | DBO   | Output Modes                                     |

| 0    | 0                  | 0     | Linear Power Mode (Refer to Figure 11)           |

| 0    | 0                  | 1     | Decibel Mode (Refer to Figure 11)                |

| 0    | 1                  | 0     | Real/Imaginary Mode (Refer to Figure 10)         |

| 0    | 1                  | 1     | Invalid Mode                                     |

| 1    | 0                  | 0     | Averaged Linear Power Mode (Refer to Figure 11)  |

| 1    | 0                  | 1     | Averaged Decibel Power Mode (Refer to Figure 11) |

| 1    | 1                  | 0     | XY Mode (Averaged) (Refer to Figure 10)          |

| 1    | 1                  | 1     | Invalid Mode                                     |

# **High-Speed FFT Processor**

Once data has been clocked into the device, a logic LOW on TEN pin will start transform operations. Approximately 18 microseconds later (for a 1024 Point FFT), EOT will go HIGH indicating results are available on the output data bus. Addresses of desired output locations are driven via an external device (e.g. DSP or DMA controller). Between EOT and the next TEN assertion, new input data, as well as any new window data, can be entered into the device with timing based on tCVC.

The user must be aware that if the overlap control is in any mode other than (OVC10=00) then aged data (located at lower addresses) is overwritten by more recent data prior to ÈQT assertion. For example, in 25% overlap mode (OVC10=01) and a 1024 point complex transform (SZ10=11); real and imaginary points 768 and higher (600h-7FFh) are copied to the first 256 real and imaginary locations of the buffer (000h-1FFh). (See Figure 7 for the Input Buffer Memory Map). In this example, the user should start addressing the most recent data beginning at 200h (point 256 and higher).

#### Data I/O Interface Description

By setting CACC1-0 to 00 and CB to 0, the window buffer is disabled and causes the first four locations to be treated as "configuration" registers. Control Registers 0 and 1 are found in the corresponding first two locations 000h and 001h (See Figure 4). Figures 5 and 6 show the formats of Control Registers 1 and 2. Control Register 0 consists of 16 bits which are readable and writable with the exception of EOT which is read-only. Control Register 1 also consists of 16-bits, however the last 9 bits are reserved. All 7 of the first bits are read/writable. See the Signal Definitions section for descriptions of each bit.

The SCALE control register at location 002h is for input "power-of-two" scaling. The device scales each stage of the processing by a fixed value of 2<sup>o</sup> to  $2^{+4}$ , in the event the user does not wish to use the block-floating point scaling provided by the hardware. Warning: Internal computations may

overflow if the user is not careful about input scaling. When SCALE is set to other than 0 (which is the default reset state), the device will not automatically scale internally to prevent an overflow condition. Should an overflow condition occur, the overflow pin (OVF) will go HIGH.

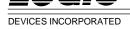

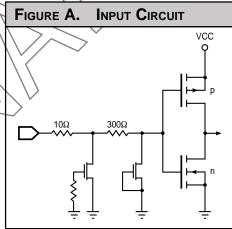

**Operational Modes**

This device has two operating modes, functioning as an FFT and as an FIR filter. In FFT mode (FILT=0), an FFT is executed according to the size specified by SZ1-0 bits as is shown in Table 4. Data is loaded into the unit (according to the status of CTM) and

only to 2N memory locations, N being the transform size. Data up to the first 2N input memory locations will be pre-multiplied (complex) by any user window specification and then transformed. Transform results are output according to the output format chosen and in like manner to the input, occupy the first 2N output buffer locations. In continuous mode (CTM=1), the memory locations are automatically sequenced out of the output buffer. In non-continuous mode, results remain in the output buffer for individual interrogation.

In FIR mode (FILT=1), a FIR filter is implemented. The filter takes a little more than twice as long to operate since it must, of necessity, perform two transforms an FFT and an inverse FFT. First, the data is input according the SZ1-0 and the status of CTM up to 2N locations, N being the filter size. Once the first FFT transform is complete, the results are multiplied by the data found in the window buffer. The window buffer acts as coefficient storage for the filter. Finally, a second inverse transform is executed and the operation is complete. The results on the output buffer are the filtered data. The data is output in a similar fashion to that of the FFT output however, the EØT will not be asserted until the second transform is completed. Also, the XVV is toggled by the device automatically and is not affected by the designated pin or bit in CR0. Since the window buffer is used for coefficient storage, the user is limited to using one of the built in window functions for the first FFT pass. Control pins AVG, DBO, XYMODE and INV are ignored in FIR mode.

#### **Data Handling and Formats**

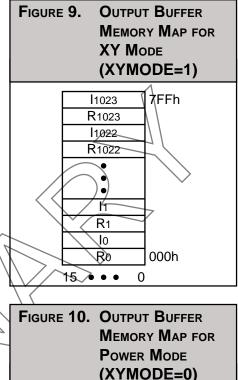

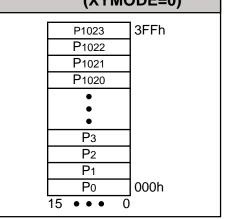

There are a variety of output modes which affect the presentation of output data and in some cases, its format. For example, in Real/Imaginary mode (XYMODE=1), at the completion of a transform, data appears at the output buffer as interleaved real and imaginary (See Figure 10) and in 16-bit two's complement format (See Figure 3). In Linear Power mode, data is presented to the first half (N) output buffer locations and is in 15-bit magnitude format. In Decibel Output mode (DBO=1), data is presented to the output buffer in negative magnitude format (16 bits wide but bit 15 is always 1) indicating a maximum of 0 dB at 0 and descending negatively from there.

In the continuous mode (CTM=1), the address lines are driven from the device and are sequenced from 0 to 2N memory locations for XYMODE=1 or N memory locations for power mode (XYMODE=0).

#### DEVICES INCORPORATED

# High-Speed FFT Processor

# MAXIMUM RATINGS Above which useful life may be impaired (Notes 1, 2, 3, 8)

| Storage temperature                       | –65°C to +150°C |

|-------------------------------------------|-----------------|

| Operating ambient temperature             | –55°C to +125°C |

| VCC supply voltage with respect to ground |                 |

| Input signal with respect to ground       | –0.5 V to 5.5 V |

| Signal applied to high impedance output   | –0.5 V to 5.5 V |

| Output current into low outputs           | 25 mA           |

| Latchup current                           |                 |

| ESD (MIL-STD-883E Method 3015.7)          |                 |

|                                           |                 |

| <b>OPERATING CONDITIONS</b> To meet specified electrical and switching characteristics |                                                                           |  |  |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Mode                                                                                   | Temperature Range (Ambient) Supply Voltage                                |  |  |  |  |

| Active Operation, Commercial                                                           | 0°C to +70°C $3.00 \text{ V} \le \text{V}_{\text{CC}} \le 3.60 \text{ V}$ |  |  |  |  |

| Active Operation, Military                                                             | $-55^{\circ}$ C to $+125^{\circ}$ C 3.00 V $\leq$ Vcc $\leq$ 3.60 V       |  |  |  |  |

|                                                                                        |                                                                           |  |  |  |  |

| ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 4) |                        |                                                         |     |     |     |      |  |  |

|---------------------------------------------------------------|------------------------|---------------------------------------------------------|-----|-----|-----|------|--|--|

| Symbol                                                        | Parameter              | Test Condition                                          | Min | Тур | Max | Unit |  |  |

| <b>V</b> он                                                   | Output High Voltage    | $V_{CC} = Min., IOH = -2.0 mA$                          | 2.4 |     |     | V    |  |  |

| VOL                                                           | Output Low Voltage     | $V_{CC} = Min., IOL = 4.0 \text{ mA}$                   |     |     | 0.4 | V    |  |  |

| <b>V</b> IH                                                   | Input High Voltage     |                                                         | 2.0 |     | Vcc | V    |  |  |

| <b>V</b> IL                                                   | Input Low Voltage      | (Note 3)                                                | 0.0 |     | 0.8 | V    |  |  |

| lix                                                           | Input Current          | Ground $\leq$ VIN $\leq$ VCC (Note 12)                  |     |     | ±10 | μA   |  |  |

| loz                                                           | Output Leakage Current | Ground $\leq$ <b>V</b> OUT $\leq$ <b>V</b> CC (Note 12) |     |     | ±10 | μA   |  |  |

| ICC1                                                          | Vcc Current, Dynamic   | (Notes 5, 6)                                            |     |     | 200 | mA   |  |  |

| ICC2                                                          | Vcc Current, Quiescent | Soft Standby, PLL Running (Note 7)                      |     |     | 10  | mA   |  |  |

| ICC3                                                          | Vcc/Current, Quiescent | Hard Standby, PLL Disabled (Note 7)                     |     |     | 2   | mA   |  |  |

| CIN                                                           | Input Capacitance      | <b>T</b> A = 25°C, f = 1 MHz                            |     |     | 10  | pF   |  |  |

| COUT                                                          | Output Capacitance     | <b>T</b> A = 25°C, f = 1 MHz                            |     |     | 10  | pF   |  |  |

# SWITCHING CHARACTERISTICS

| Commercial Operating Range (0°C to +70°C) Notes 9, 10 (ns) |                                            |     |       |                           |     |     |     |  |

|------------------------------------------------------------|--------------------------------------------|-----|-------|---------------------------|-----|-----|-----|--|

|                                                            |                                            |     | L7710 |                           |     |     |     |  |

|                                                            |                                            | 1   | 15    |                           | 12  |     | D   |  |

| Symbol                                                     | Parameter                                  | Min | Max   | Min                       | Max | Min | Max |  |

| <b>t</b> CYC                                               | Cycle Time                                 | 15  |       | 12                        |     | 10  |     |  |

| <b>t</b> PW                                                | Clock Pulse Width                          | 6   |       | 5                         |     | 4   |     |  |

| ts                                                         | Input Setup Time                           | 5   |       | 4                         |     | 3   |     |  |

| tн                                                         | Input Hold Time                            | 0   |       | 0                         | ) ) | 0   | >   |  |

| tD                                                         | Output Delay                               |     | 10    | $\langle \langle \rangle$ | /-8 |     | 7   |  |

| <b>t</b> ena                                               | Three-State Output Enable Delay (Note 11)  |     | 15    |                           | 12  |     | 10  |  |

| tDIS                                                       | Three-State Output Disable Delay (Note 11) |     | 15    |                           | 12  |     | 10  |  |

|                                                            |                                            |     |       |                           |     |     |     |  |

| MILITARY OPERATING RANGE (-55°C to +125°C) Notes 9, 10 (ns) |                                            |     |     |     |     |     |     |  |

|-------------------------------------------------------------|--------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| L7710                                                       |                                            |     |     |     |     |     |     |  |

|                                                             |                                            | 20  |     | 15  |     | 12  |     |  |

| Symbol                                                      | Parameter                                  | Min | Max | Min | Max | Min | Max |  |

| <b>t</b> CYC                                                | Cycle Time                                 | 20  |     | 15  |     | 12  |     |  |

| <b>t</b> PW                                                 | Clock Pulse Width                          | 8   |     | 6   |     | 5   |     |  |

| ts                                                          | Input Setup Time                           | X   |     | 5   |     | 4   |     |  |

| tн                                                          | Input Hold Time                            | 2   |     | 1   |     | 0   |     |  |

| <b>t</b> D                                                  | Output Delay                               |     | 12  |     | 10  |     | 8   |  |

| <b>t</b> ena                                                | Three-State Output Enable Delay (Note 11)  |     | 17  |     | 15  |     | 12  |  |

| tDIS                                                        | Three-State Output Disable Delay (Note 11) |     | 17  |     | 15  |     | 12  |  |

# NOTES

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

3. This device provides hard clamping of transient undershoot and overshoot. Input levels below ground or above VCC will be clamped beginning at -0.6 V and VCC + 0.6 V. The device can withstand indefinite operation with inputs in the range of -0.5 V to +7.0 V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

5. Supply current for a given application can be accurately approximated by:

NCV<sup>2</sup>F

#### where

N = total number of device outputs C = capacitive load per output V = supply voltage F = clock frequency

6. Tested with all outputs changing every cycle and no load, at a X MHz clock rate.

7. Tested with all inputs within 0.1 V of VCC or Ground, no load.

8. These parameters are guaranteed but not 100% tested.

9. AC specifications are tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tENA/tDIS test), and input levels of nominally 0 to 3.0 V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5 V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed. For tENABLE and tDISABLE measurements, the load current is increased to 10 mA to reduce the RC delay component of the measurement,

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

a. A 0.1  $\mu$ F ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

b. Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

c. Input voltages should be adjusted to compensate for inductive ground and VCC noise to maintain required DUT input levels relative to the DUT ground pin.

10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from

the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

11. Transition is measured ±200 mV from steady-state voltage with specified loading.

12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

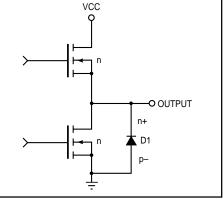

# FIGURE B. OUTPUT CIRCUIT

#### DEVICES INCORPORATED

# **High-Speed FFT Processor**