# 54F/74F411

## FIFO RAM Controller

The 'F44' I F6 in M Controller (FRC) is an address and status generator designed to inform it a high-speed First-In/First-Out (FIFO) stack utilizing standary of the inell RAMs. The 'F411 can control up to 16K words of buffer mellion in the mobilizate buffer sizes can be selected (see device functional descriptions tall invarbitration logic controls read/write operations on first-come/first-samp disease.

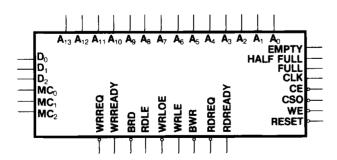

### **Connection Diagrams**

Pin Assignment for DIP

Ordering Code: See Section 5

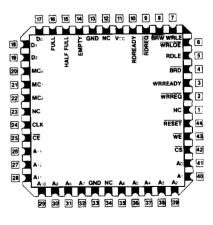

## **Logic Symbol**

Pin Assignment for LCC and PCC

Input Loading/Fan-Out: See Section 3 for U.L. definitions

| Pin Names                        | Description                           | <b>54F/74F(U.L.)</b><br>HIGH/LOW |

|----------------------------------|---------------------------------------|----------------------------------|

| A <sub>0</sub> -A <sub>13</sub>  | Read/Write Address                    | 75/15 (12.5)                     |

| MC <sub>0</sub> -MC <sub>2</sub> | Memory Clock Select                   | 0.5/0.375                        |

| $D_0 \cdot D_2$                  | FIFO Depth Select                     | 0.5/0.375                        |

| EMPTY                            | Status Line                           | 25/12.5                          |

| HALF FULL                        | Status Line                           | 25/12.5                          |

| FULL                             | Status Line                           | 25/12.5                          |

| BRD, BWR                         | Burst Read, Burst Write               | 0.5/0.375                        |

| WRLE, RDLE                       | Write Latch Enable, Read Latch Enable | 25/12.5                          |

| RDREQ                            | Read Request                          | 0.5/0.375                        |

| WRREQ                            | Write Request                         | 0.5/0.375                        |

| WE                               | RAM Write Enable                      | 25/12.5                          |

| CSO                              | RAM Chip Select Output                | 25.12.5                          |

| RESET                            | Master Reset                          | 0.5/0.375                        |

| CLK                              | Clock                                 | 0.5/0.375                        |

| CE                               | Chip Enable                           | 0.5/0.375                        |

| WRREADY                          | Write Ready                           | 25/12.5                          |

| RDREADY                          | Read Ready                            | 25/12.5                          |

| WRLOE                            | Write Latch Output Enable             | 25/12.5                          |

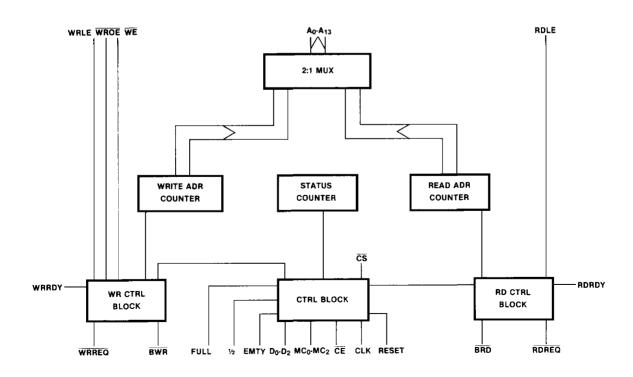

#### **Functional Description**

The 'F411 FIFO RAM Controller consists of three 14-bit counters. Two of these counters provide read/write addresses for FIFO read/write operations respectively. The third counter is an up-down counter. Depending on the operation of FIFO, the counter is either incremented (write operation) or decremented (read operation). The output of the counter is decoded according to the memory length select lines D<sub>0</sub>-D<sub>2</sub> to produce EMPTY, HALF FULL, or FULL status lines. (See Table 2).

The arbitration logic handles all read/write requests on first-come/first-served basis. In the event of a tie, the priority is based on the HALF FULL status signal. Normally write requests have higher priority over read requests unless the HALF FULL signal is active, in which case the read requests have priority over write requests. The arbiter decision can be disabled by Burst Read or Burst Write request in which case all subsequent read or write requests are denied until burst read or write operation is terminated. The priority will be the same as normal read and write should Burst Write and Burst Read become active simultaneously. (See Table 3.)

The WRLE and RDLE signals control the external latches at the top and bottom of the FIFO stack. Read (RD) and Write (WR) pulses are used to transfer data to and from the RAM locations specified by the address bus. Read and Write pulse widths can be programmed using memory clock pins MC<sub>0</sub>-MC<sub>2</sub>, (See Table 1). RESET will reset all counters to zero. HALF FULL and FULL status lines are forced LOW and EMPTY status forced HIGH.

#### **Functional Operation**

#### A<sub>0</sub> A<sub>13</sub>

Fourteen 3-state outputs are capable of driving an 8 mA DC load. The FIFO can address up to 16K words of data.

The three Memory Clock select lines determine the number of master clock cycles by which Write or Read pulse width is extended. See Table 1 for selection guide.

#### $D_0 \cdot D_2$

The length of the FIFO memory can be hardware-selected via the length select  $(D_0-D_2)$  inputs. When less than the maximum length is selected, the unused high-order bits of the address outputs are held in the high-impedance state.

#### Write Request (WRREQ)

Write request for write cycle; active LOW input.

#### Read Request (RDREQ)

Read request for read cycle; active LOW input.

#### Write Enable (WE)

Write cycle address valid, active LOW 3-State output.

#### Chip Select Output (CSO)

When active, the RAM will be selected. Active LOW, 3-State output.

#### RESET

Active LOW master reset input. The user must force the RESET input LOW to initialize the chip. The following actions occur when RESET is active:

- 1. All internal counters are set to '0'.

- 2. Half Full and Full outputs are forced LOW.

- 3. WE, CSO and EMPTY outputs are forced HIGH.

- 4. WRREADY and RDREADY signals are forced HIGH and LOW respectively.

- 5. Write latch will be disabled and transparent.

- 6. Read latch will be disabled and transparent.

- 7. RAM write address selected.

#### Burst Read (BRD)

Active LOW input; the following actions occur when BRD is active:

- 1. Write Ready is forced HIGH.

- Priority is always given to read requests.

#### Burst Write (BWR)

Active LOW input; the following actions occur when  $\overline{\mbox{BWR}}$  is active:

- 1. Read Ready is forced HIGH.

- 2. Priority is always given to write requests.

#### Write Ready (WRREADY)

Active HIGH output; WRREADY HIGH signals that FIFO is ready to accept write requests. WRREADY goes LOW on the positive-going edge of Master Clock on a pending write request. The WRREADY will go from LOW-to-HIGH one clock cycle later if FULL signal is LOW.

#### Read Ready (RDREADY)

Active HIGH output; RDREADY HIGH signals that FIFO is ready to accept read requests. RDREADY goes LOW on the positive-going edge of Master Clock on a pending read request. The RDREADY will go from LOW-to-HIGH on the positive going edge of  $\overline{\text{CS}}$  if EMPTY signal is LOW.

#### Clock (CLK)

Clock input to the FIFO (variable); typical clock = 50 MHz.

#### Chip Enable (CE)

Active LOW input; when inactive all RAM interface signals are held in high impedance state and further read or write requests are denied. Read or Write cycles in progress when  $\overline{\text{CE}}$  goes HIGH will finish before the chip is deactivated.

#### Read Latch Enable (RDLE)

Active HIGH output; on the HIGH-to-LOW transition of RDLE, FIFO data is latched into the external output data latch.

Note RDLE will remain HIGH for modes 0-3 of MC.

#### Write Latch Enable (WRLE)

Active HIGH output; on the HIGH-to-LOW transition of WRLE data to be written into the FIFO is latched into the external input data latch.

#### Write Latch Output Enable (WRLOE)

Active LOW output; on the HIGH-to-LOW transition of WRLOE the output of external input data latch is enabled.

#### **FULL**

Memory Full status output. The FULL signal goes HIGH on the negative-going edge of Master Clock if WRREADY is LOW and all bits of status counter for selected length are equal to '1'. The FULL signal goes from HIGH-to-LOW on the negative-going edge of Master Clock if RDREADY is LOW.

Note: WRREADY will remain LOW so long as full signal is active.

### HALF FULL

Memory Half Full status output. The HALF FULL operates in the same way as FULL signal except that it goes HIGH when status counter reaches a

count of 127 ( $D_2 = H$ ,  $D_1 = H$ ,  $D_0 = L$ ). The HALF FULL signal goes from HIGH-to-LOW on the negative-going edge of Master Clock if RDREADY is LOW.

#### **EMPTY**

Memory Empty Status Output. The EMPTY signal goes HIGH on the negative-going edge of Master Clock if status counter contains a value of '1' and RDREADY is LOW. The EMPTY signal goes from HIGH-to-LOW on the negative-going edge of Master Clock if WRREADY is LOW.

Note: RDREADY will remain LOW so long as EMPTY signal is valid.

#### **Block Diagram**

Table 1

| MC <sub>2</sub> | MC <sub>1</sub> | MC <sub>0</sub> | Mode | WE<br>Duration | CS<br>Duration |

|-----------------|-----------------|-----------------|------|----------------|----------------|

| 0               | 0               | 0               | 0    | 1              | LOW*           |

| 0               | 0               | 1               | 1    | 2              | LOW*           |

| 0               | 1               | 0               | 2    | 3              | LOW*           |

| 0               | 1               | 1               | 3    | 4              | LOW*           |

| 1               | 0               | 0               | 4    | 1              | 1              |

| 1               | 0               | 1 1             | 5    | 2              | 2              |

| 1               | 1               | 0               | 6    | 3              | 3              |

| 1               | 1               | 1               | 7    | 4              | 4              |

<sup>\*</sup>Chip Select output remains LOW irrespective of MC<sub>n</sub>settings.

Table 2

| $D_2$ | D <sub>1</sub> | D <sub>0</sub> | Half Length<br>Words | Full Length<br>Words |

|-------|----------------|----------------|----------------------|----------------------|

| 0     | 0              | 0              | 8K                   | 16K                  |

| 0     | 0              | 1              | 4K                   | 8K                   |

| 0     | 1              | 0              | 2K                   | 4K                   |

| 0     | 1              | 1              | 1K                   | 2K                   |

| 1     | 0              | 0              | 512                  | 1024                 |

| 1     | 0              | 1              | 256                  | 512                  |

| 1     | 1 1            | 0              | 128                  | 256                  |

| 1     | 1              | 1              | 64                   | 128                  |

Table 3

| RDREQ | WRREQ | BWR | BRD | Half Full | Priority |

|-------|-------|-----|-----|-----------|----------|

| L     |       | L   | L   | L         | NOOP     |

| L     | L     | L   | L   | н         | NOOP     |

| L     | L     | L   | н   | L         | WRITE    |

| L     | L     | L   | н   | н         | WRITE    |

| L     | L     | Н   | L   | L         | READ     |

| L     | L     | Н   | L   | н         | READ     |

| L     | L     | н   | н   | L         | WRITE    |

| L     | L     | Н   | Н   | н         | READ     |

| L     | Н     | L   | L   | L         | NOOP     |

| L     | Н     | L   | L   | н         | NOOP     |

| L     | Н     | L   | Н   | L         | NOOP     |

| L     | Н     | L   | н   | н         | NOOP     |

| L     | Н     | H   | L   | L         | READ     |

| L     | н     | н   | L   | н         | READ     |

| L     | Н     | н   | Н   | L         | READ     |

| L     | н     | н   | н   | Н         | READ     |

| Н     | L     | L   | L   | L         | NOOP     |

| Н     | L     | L   | L   | н         | NOOP     |

| н     | L     | L   | Н   | L         | WRITE    |

| Н     | L     | L   | Н   | н         | WRITE    |

| Н     | L     | Н   | L   | L         | NOOP     |

| Н     | L     | н   | L   | Н         | NOOP     |

| Н     | L     | н   | н   | L         | WRITE    |

| Н     | L     | н   | H   | н         | WRITE    |

| Н     | н     | Х   | х   | ×         | NOOP     |

## DC Characteristics over Operating Temperature Range (unless otherwise specified)

|        |                      | 54F/74F |     |     |       |                       |  |

|--------|----------------------|---------|-----|-----|-------|-----------------------|--|

| Symbol | Parameter            | Min     | Тур | Max | Units | Conditions            |  |

| Icc    | Power Supply Current |         | 125 | 190 | mA    | V <sub>CC</sub> = Max |  |

## AC Characteristics: See Section 3 for waveforms and load configurations

| Symbol           | Parameter                                            | 54F/74F                                              | 54F                                     | 74F                                    | Units |

|------------------|------------------------------------------------------|------------------------------------------------------|-----------------------------------------|----------------------------------------|-------|

|                  |                                                      | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V<br>$C_L = 50$ pF | $T_A$ , $V_{CC} = Mil$<br>$C_L = 50 pF$ | $T_A$ , $V_{CC} =$ $Com$ $C_L = 50 pF$ |       |

|                  |                                                      | Min Typ Max                                          | Min Max                                 | Min Max                                |       |

| f <sub>max</sub> | Maximum Clock Frequency<br>Data Rate with 20 ns SRAM | 50<br>25                                             |                                         |                                        | MHz   |

| t <sub>PHL</sub> | Propagation Delay<br>CSO to WE                       | 5.0                                                  |                                         |                                        | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>WRREQ to WRREADY                | 13.0<br>13.0                                         |                                         |                                        | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>WRREADY to WRLE                 | 10.0<br>10.0                                         |                                         |                                        | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>WRREADY to WRLOE                | 10.0<br>10.0                                         |                                         |                                        | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>Clock to WRREADY                | 6.0<br>6.0                                           |                                         |                                        | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>WRREADY to Status Output        | 20.0<br>20.0                                         |                                         |                                        | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>RDREADY to RDLE                 | 25.0<br>25.0                                         |                                         |                                        | ns    |

# AC Operating Requirements: See Section 3 for waveforms

| Symbol                                   | Parameter                          | 54F/74F                             | 54F                                | 74F                                       | Units |  |

|------------------------------------------|------------------------------------|-------------------------------------|------------------------------------|-------------------------------------------|-------|--|

|                                          |                                    | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V | T <sub>A</sub> , V <sub>CC</sub> = | T <sub>A</sub> , V <sub>CC</sub> =<br>Com |       |  |

|                                          |                                    | Min Typ Max                         | Min Max                            | Min Max                                   |       |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>RAM Add | 5.0<br>5.0                          |                                    |                                           |       |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>RAM Add  | 5.0<br>5.0                          |                                    |                                           | ns    |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW WRREQ      | 5.0<br>5.0                          |                                    |                                           |       |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW WRREQ       | 5.0<br>5.0                          |                                    |                                           | ns    |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW            | 5.0<br>5.0                          |                                    |                                           |       |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW             | 5.0<br>5.0                          |                                    |                                           | ns    |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>BRD     | 5.0<br>5.0                          |                                    |                                           | ns    |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>BRD      | 5.0<br>5.0                          |                                    |                                           | ns    |  |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CSO Pulse Width<br>HIGH or LOW     | 20.0<br>20.0                        |                                    |                                           | ns    |  |

Fig. 411-a Write Cycle CLOCK WREQ MSEL WREADY WRITE NEXT NEXT **ADDRESS** ADD ADD ADD WE WRLE cso ADDRESS COUNTER CLKE WRLOE VALID DATA VALID DATA WRITE DATA STATUS COUNTER CLKE STATUS COUNTER DATA HALF FULL  $\begin{array}{l} MC_0 = L \\ MC_1 = L \end{array}$  $\begin{array}{l} D_0 = L \\ D_1 = H \end{array}$  $MC_2 = H$  $D_2 = H$

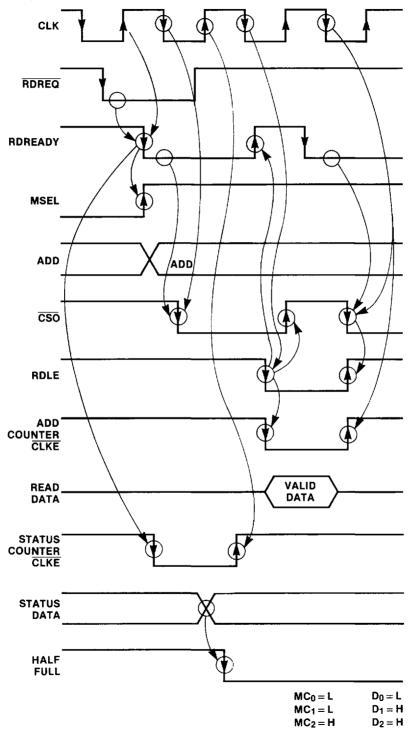

Fig. 411-b Read Cycle