# 100VG-AnyLAN Category 3/5 **4-UTP Transceiver**

### **Product Features**

- Complete PMD interface for 100VG-AnyLAN

- Supports Category 3/5 UTP cables

- 100 Mbps Transmission through 4 channels

- Adaptive equalization

- Digital PLLs

- Low Power

- IEEE 802.12 Standard compliant MII Interface

- Packages available:

- 44-pin plastic PLCC (J44)

# **Product Description**

The 100VG-AnyLAN Category 3/5 4-UTP Transceiver integrated circuit provides the complete physical layer (PMD) functions for 4-pair Category-3 or -5 unshielded twisted pair links as specified by the IEEE 802.12 standard. The device enables 100VG-AnyLAN adapter and hub implementations by providing a standard Media Independent Interface (MII) that can connect to either hub or MAC implementations with no additional glue logic. The four differential twisted pair drivers connect directly to commonly available 802.12 4-UTP filter-transformer modules. The device supports 100Mbps transmission over twisted-pair lengths from 0 to 100 meters on Category-3 cable, and longer lengths on Category-5 cable.

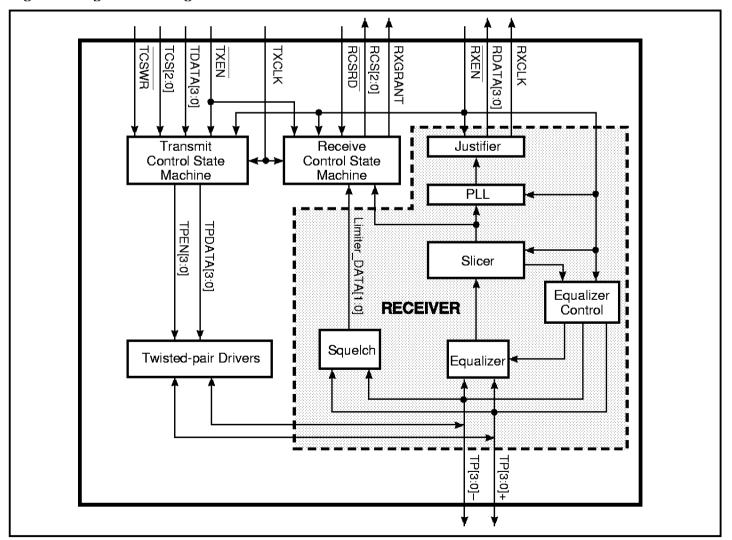

Figure 1. Logic Block Diagram

During packet reception, the device provides all timing and data recovery functions for the four incoming data streams and justifies the received data streams from the four independent twisted-pairs to a common received clock. Control signals received on twisted pairs 0 and 1 are decoded by the receive control machine to provide line state information at the MII interface. The receive data path includes a first order linear

equalizer and timing recovery circuits for each of the four twisted pairs.

Transmit control signals are generated by the device on twisted pairs 2 and 3 based on the requested transmit control state presented at the MII. During packet transmission all four twisted pairs are driven with the transmit data received from the MII.

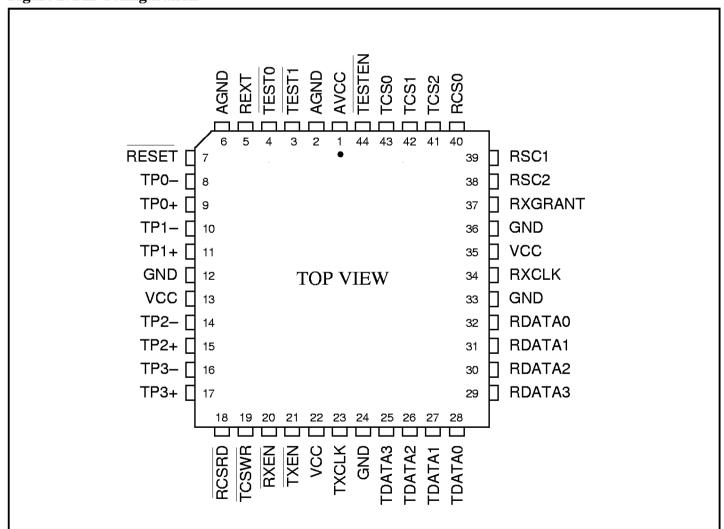

Figure 2. Pin Configuration

Table 1. Pin Description

| Pin No. | Signal     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AVCC       | _   | Analog Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2       | AGND       |     | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3       | TEST1      | I   | Test pin (Active LOW). Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4       | TESTO      | I   | Test pin (Active LOW). Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5       | REXT       | _   | <b>R External</b> . $(24.9 \text{K}\Omega \pm 1\%)$ . This pin is used to attach an external precision resistor used as a current reference.                                                                                                                                                                                                                                                                                                                                         |

| 6       | AGND       | _   | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7       | RESET      | I   | <b>Reset.</b> (Active LOW) When asserted causes a reset of all internal state machines, counters and logic. RESET must be asserted for a minimum of 20 microseconds.                                                                                                                                                                                                                                                                                                                 |

| 8, 9    | TP0-, TP0+ | I/O | <b>Twisted Pair Zero Input/Output ±.</b> TP0+, TP0– is a differential pair of twisted-pair drivers.                                                                                                                                                                                                                                                                                                                                                                                  |

| 10, 11  | TP1-, TP1+ | I/O | <b>Twisted Pair One Input/Output ±.</b> TP1+, TP1- is a differential pair of twisted-pair drivers.                                                                                                                                                                                                                                                                                                                                                                                   |

| 12      | GND        |     | Twisted Pair I/O Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13      | VCC        |     | Twisted Pair I/O Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14, 15  | TP2-, TP2+ | I/O | <b>Twisted Pair Two Input/Output ±.</b> TP2+, TP2- is a differential pair of twisted-pair drivers.                                                                                                                                                                                                                                                                                                                                                                                   |

| 16, 17  | TP3-, TP3+ | I/O | <b>Twisted Pair Three Input/Output ±.</b> TP3+, TP3- is a differential pair of twisted-pair drivers.                                                                                                                                                                                                                                                                                                                                                                                 |

| 18      | RCSRD      | I   | Receive Control Read Enable. (Active LOW) When RCSRD is asserted LOW, the device drives the RXGRANT and RCS[2:0] outputs. When RCSRD is deasserted, RXGRANT and RCS[2:0] are tri-stated.                                                                                                                                                                                                                                                                                             |

| 19      | TCSWR      | I   | Transmit Control Code Write Enable. (Active LOW) This signal must be asserted LOW to enable the Transmit Control Machine to sample TCS[2:0]. TCSWR is synchronous with TXCLK.                                                                                                                                                                                                                                                                                                        |

| 20      | RXEN       | I   | Receive Enable. (Active LOW) When RXEN is asserted, the device is enabled to receive packet data from the TP[3:0] inputs. When RXEN is deasserted, RXCLK and RDATA[3:0] are tri-stated. When RXEN is asserted and preamble is detected, RXCLK begins to transition, at which time the RDATA[3:0] outputs are active and valid. When RXEN is asserted, the four twisted pair drivers are disabled. (The transmitters on TP2 and TP3 are disabled after DC balance has been achieved.) |

| 21      | TXEN       | I   | Transmit Enable. (Active LOW) When TXEN is asserted, the device transmits data on the TDATA[3:0] inputs to the TP[3:0] outputs once a DC balance point has been reached on the twisted pairs. When TXEN is deasserted, control codes encoded by TCS[2:0] are transmitted. TXEN is synchronous to TXCLK.                                                                                                                                                                              |

| 22      | VCC        |     | Digital Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23      | TXCLK      | I   | Transmit Clock. 30 MHz ±100ppm with 45%-55% duty cycle. TCS[2:0], TCSWR, TXEN, TDATA[3:0], RCS[2:0], RCSRD, RXEN, and RXGRANT are synchronous to TXCLK.                                                                                                                                                                                                                                                                                                                              |

| 24      | GND        |     | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Note: I = Input, O = Output, Z = Tristate, — = N/A

# **Table 1: Pin Description** (continued)

| Pin No. | Signal     | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25-28   | TDATA[3:0] | I    | Transmit Data. A 4-bit unidirectional serial transmit bus. Data presented on these inputs are transmitted onto TP[3:0] when TXEN is asserted LOW. TDATA[3:0] inputs are synchronized to the rising edge of TXCLK. Data on TDATA3 is transmitted on TP0. Data on TDATA2 is transmitted on TP1. Data on TDATA1 is transmitted on TP2. Data on TDATA0 is transmitted on TP3.                                                                                                                                                                     |

| 29-32   | RDATA[3:0] | O/Z  | Receive Data. A 4-bit unidirectional serial receive bus that contains valid receive data when RXEN is asserted and a packet is being received from the medium. RDATA3 contains data present on TP3, RDATA2 contains data present on TP2, RDATA1 contains data present on TP1 and RDATA0 contains data present on TP0. RDATA[3:0] are synchronous to RXCLK. Upon RXEN deassertion, RDATA[3:0] is immediately tristated. When RXEN is asserted, RDATA[3:0] is driven low until RXCLK is active, at which point valid preamble is on RDATA[3:0]. |

| 33      | GND        | _    | CMOS Output Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 34      | RXCLK      | O/Z  | Receive Clock. Recovered 30 MHz clock from the data on the twisted pairs. RXCLK is synchronous with the RDATA[3:0] outputs. It is active only when RXEN has been asserted LOW and the device has acquired phase and frequency lock from the incoming data. At the time RXCLK becomes active, valid preamble is presented on the RDATA[3:0] outputs. RXCLK will continue to be active as long as RXEN is asserted.                                                                                                                             |

| 35      | VCC        |      | CMOS Output Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 36      | GND        |      | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 37      | RXGRANT    | O/Z  | Receive Grant. When RXGRANT is asserted, the device has determined that the GRANT code has been transmitted by the upstream node. When RXGRANT is deasserted, another control code is being received. RXGRANT is synchronous with TXCLK. It is tri-stated if RCSRD is deasserted.                                                                                                                                                                                                                                                             |

| 38-40   | RCS[2:0]   | O/Z  | <b>Receive Control Code.</b> RCS[2:0] are the encoded values of the control codes received from the medium on TP[1:0]. The signals are valid when RCSRD is asserted and are synchronous to TXCLK. When RCSRD is deasserted, these signals are tristated.                                                                                                                                                                                                                                                                                      |

| 41-43   | TCS[2:0]   | I    | Transmit Control Code. The 3-bit encoded value of the transmit control code. The TCS is processed and transmitted onto pairs TP[3:2] by the device. The values on these three inputs will be sampled only when TCSWR is asserted. TCS[2:0] may be changed when TXEN is asserted, but will not take effect until TXEN has been deasserted.                                                                                                                                                                                                     |

| 44      | TESTEN     | I    | Test Enable Pin. (Active LOW) When RESET is deasserted and TESTEN is asserted, the chip-to-board contact test is enabled. See Table 2 for detailed pin mapping during the contact test.                                                                                                                                                                                                                                                                                                                                                       |

| Table 2: Pin Mapping for Chip-to-Board Contact Tes   | t(RESET = 1 TESTEN = 0)                                                   |

|------------------------------------------------------|---------------------------------------------------------------------------|

| Table 2. I in Mapping for Chip-to-Doard Contact I cs | $\mathbf{L}(\mathbf{NLSL}_1 = \mathbf{I}, \mathbf{LLSLL}_1 = \mathbf{U})$ |

| INPUT` | TEST1 | TEST0   | TCS[2:0] | TDATA[3:0] | RCSRD     | TCSWR     | RXEN      | TXEN      | TXCLK |

|--------|-------|---------|----------|------------|-----------|-----------|-----------|-----------|-------|

| OUTPUT | REXT  | RXGRANT | RCS[2:0] | RDATA[3:0] | TP0+/TP0- | TP1+/TP1- | TP2+/TP2- | TP3+/TP3- | RXCLK |

5

Note: When RESET is asserted, the contact test is disabled. This is used to check the contact for the RESET pin.

# **Functional Description**

#### **Twisted-Pair Drivers**

The four twisted-pair drivers provide a differential output impedance of 50 Ohms from their respective twisted-pair pins. These drivers are tristated during reception and driven during transmission. The twisted-pair drivers transmit NRZ data, i.e., a value of 1 is indicated by a positive differential voltage and a value of 0 is indicated by a negative differential voltage.

#### Receiver

The receiver consists of four sets of switchable first order linear equalizers followed by slicers, which determine the voltage level (1 or 0) on each of the twisted pair differential signals. Following the assertion of RXEN, the timing recovery circuits are engaged to detect packet preamble and create a receive clock for each of the four data channels. Each channel's receive clock and sampled data is provided to the justifier circuit, which retimes the received data to the output RXCLK. During periods of packet reception, data on all four twisted-pairs is passed through the equalizer circuits, if they are enabled. The decision to enable an equalizer will be based on the amplitude of the preamble sequence of the previous packet.

When packet data is expected, the receiver will also perform a signal detect function, which is an indication that TP[3:0] may have incoming preamble. (This is distinguished from control codes). Timing and data recovery is performed on all four twisted pairs independently and the resulting four clocks are justified to a single RXCLK recovered from TP0. Data and timing recovery continues until  $\overline{RXEN}$  is deasserted at the MII interface. If valid data bits are not incoming while  $\overline{RXEN}$  is asserted, RXCLK may drift.

#### Control State Machine

Two control tone signals, CS1 and CS2, are generated and transmitted on twisted pair wires for Receive Control State Machine (RCSM) and Transmit Control State Machine (TCSM) interpretation. CS1 is a continuous repetition of 16 "1's" followed by 16 "0's" transmitted at 30 Mbaud, and CS2 is continuous repetition of 8 "1's" followed by 8 "0's" transmitted at 30 MBaud. The fundamental frequency of CS1 is 0.9375 MHz, and that of CS2 is 1.875 MHz.

### **Transmit Control State Machine**

The TCSM has two major functions: the generation of control signals and their subsequent transmission, and the transmission of data present on the TDATA[3:0] inputs. The transmit control machine encodes the 3-bit value of TCS[2:0] for transmission onto TP[3:2] when TXEN is deasserted and provides the proper termination control codes prior to transmitting serial data on TP[3:0] when TXEN is asserted. NRZ coding is used to transmit both data and control codes. The transmit control machine must also monitor RXEN in order to disable control signal transmissions on TP[1:0] during packet reception.

Data on TDATA[3:0] shall be transmitted synchronously with TXCLK onto TP[3:0] when TXEN is asserted and a DC balance point has been reached. A DC balance point is defined as an equal number of 1's and 0's having been transmitted on both TP3 and TP2. When both TXEN and RXEN are deasserted, TCS disables the transmitters on channels 0 and 1, and generates the following control signals on channels 2 and 3 based on the values of TCS[2:0] as shown in table 3.

Table 3. TCS - TP Mapping

| TCS[2:0] | TP2     | TP3     |  |

|----------|---------|---------|--|

| 000      | Disable | Disable |  |

| 001      | CS1     | CS1     |  |

| 010      | CS1     | CS2     |  |

| 011      | CS2     | CS1     |  |

| 100      | CS2     | CS2     |  |

| 101      | _       | _       |  |

| 110      | _       | _       |  |

| 111      | Disable | Disable |  |

When TXEN is asserted, the TCS continues to transmit control signals on TP2 and TP3 until an equal number of 0's and 1's (DC balance) on both channels have been transmitted. At that point, the TCS then begins to transmit data from TDATA[3:0] onto all four twisted pairs according to Table 4.

Table 4. TDATA to TP Mapping

| Input  | Output |  |

|--------|--------|--|

| TDATA0 | TP3    |  |

| TDATA1 | TP2    |  |

| TDATA2 | TP1    |  |

| TDATA3 | TP0    |  |

### **Receive Control State Machine**

The Receive Control State Machine (RCSM) is responsible for recovering received control signals from TP1 and TP0 via LIMITER\_DATA[1:0], and determining the receive control state for indication on RCS[2:0] and RXGRANT.

Control signals are interpreted mainly during periods when packets are not being received. During times of packet reception and transmission, the RCSM is mainly inactive, though signal monitoring functions are performed during packet reception. Table 5 illustrates the mapping from the twisted pair signals to the RDATA signals during packet reception.

Table 5. TP to RDATA Mapping

| Input | Output |  |

|-------|--------|--|

| TP0   | RDATA0 |  |

| TP1   | RDATA1 |  |

| TP2   | RDATA2 |  |

| TP3   | RDATA3 |  |

RXGRANT is asserted by the RCSM when the lack of energy or SILENCE is detected on TP0 and TP1. It is deasserted otherwise. The signal level measurement function is performed by the squelch circuits on TP0 and TP1. The relationship between TP0 and TP1 with the received control state is given in Table 6.

Table 6. TP0/1 Mapping TO RCS

| TP0             | TP1             | RCS[2:0] |

|-----------------|-----------------|----------|

| Mode Transition | Mode Transition | 000      |

| CS1             | CS1             | 001      |

| CS2             | CS1             | 010      |

| CS1             | CS2             | 011      |

| CS2             | CS2             | 100      |

| Data            | Data            | 101      |

|                 | _               | 110      |

| Link Warning    | Link Warning    | 111      |

PS7052A 02/10/97

6

### **MAXIMUM RATINGS**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Maximum Supply Voltage (Vcc)                            | V  |

|---------------------------------------------------------|----|

| Storage Temperature (Ts)                                | C  |

| Ambient Temperature with Power Applied (TA) 0°C to +70° | ,C |

| Signal Pin Voltage0.5 to Vcc+0.5                        | V  |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Table 7. DC Electrical Characteristics (Over the Operating Range)

| Description    |               | Min. | Тур. | Max. | Units |

|----------------|---------------|------|------|------|-------|

| Supply Voltage |               | 4.75 | 5.0  | 5.25 | V     |

| Supply Current | Idle          | _    | 46   | _    | mA    |

|                | Transmit Tone |      | 130  |      | mA    |

|                | Transmit Data |      | 198  |      | mA    |

|                | Receive Data  | _    | 132  | _    | mA    |

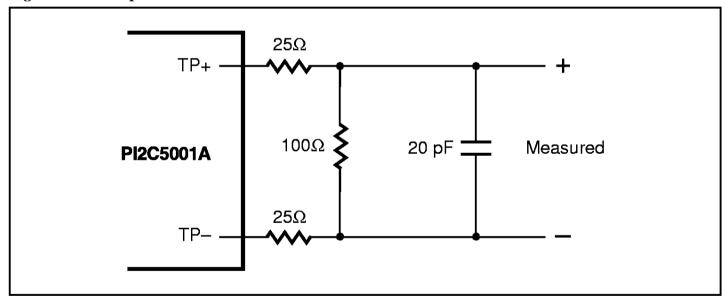

## Table 8. Twisted Pair Output Specifications (See Figure 6)

| Description                                    | Min. | Тур. | Max. | Units |

|------------------------------------------------|------|------|------|-------|

| Differential Source Resistance                 | 40   | 50   | 60   | Ω     |

| Rise/Fall Time with 150Ω/20pF Load, 10% to 90% | 6.0  | _    | 12.0 | ns    |

| Output Voltage with 150Ω Load                  | 3.4  | 3.8  | 4.2  | V     |

| Differential Pair Skew                         | _    | _    | 1.0  | ns    |

## **Table 9. Twisted Pair Input Specifications**

| Description                    | Min. | Тур. | Max. | Units |

|--------------------------------|------|------|------|-------|

| Differential Input Resistance  | 35   | 50   | 65   | Ω     |

| Differential Input Capacitance | _    | 15   | 20   | pF    |

# Table 10. CMOS Input

| Description          | Condition | Min.    | Тур. | Max. | Units |

|----------------------|-----------|---------|------|------|-------|

| VIH                  |           | Vcc – 1 | _    | _    | V     |

| V <sub>IL</sub>      |           | _       | _    | 1.0  | V     |

| Input Leakage        |           | _       | _    | 10   | μА    |

| Input Capacitance    |           | _       | _    | 6    | pF    |

| Input Rise/Fall Time | 20%-80%   | _       | _    | 5    | ns    |

7

Table 11. CMOS Output

| Description           | Condition            | Min.      | Тур. | Max. | Units |

|-----------------------|----------------------|-----------|------|------|-------|

| Voh                   | Sourcing 2 mA        | Vcc – 0.5 | _    | _    | V     |

| Vol                   | Sinking 2 mA         | _         | _    | 0.5  | V     |

| Ouput Leakage Current | High-Impedance State | _         | _    | 10   | μΑ    |

| Output Rise/Fall Time | See Figure 3         | 1         | _    | 6    | ns    |

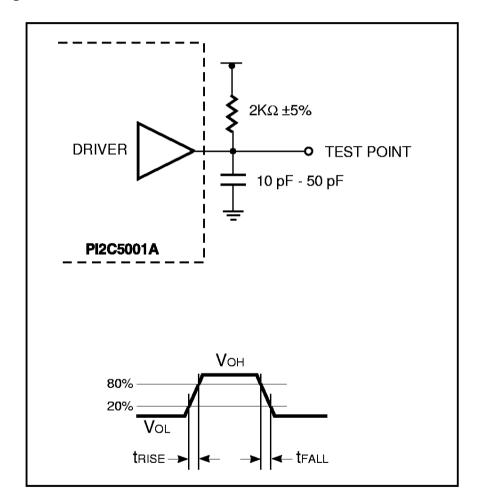

Figure 3. MII Output Driver Test Condition

8

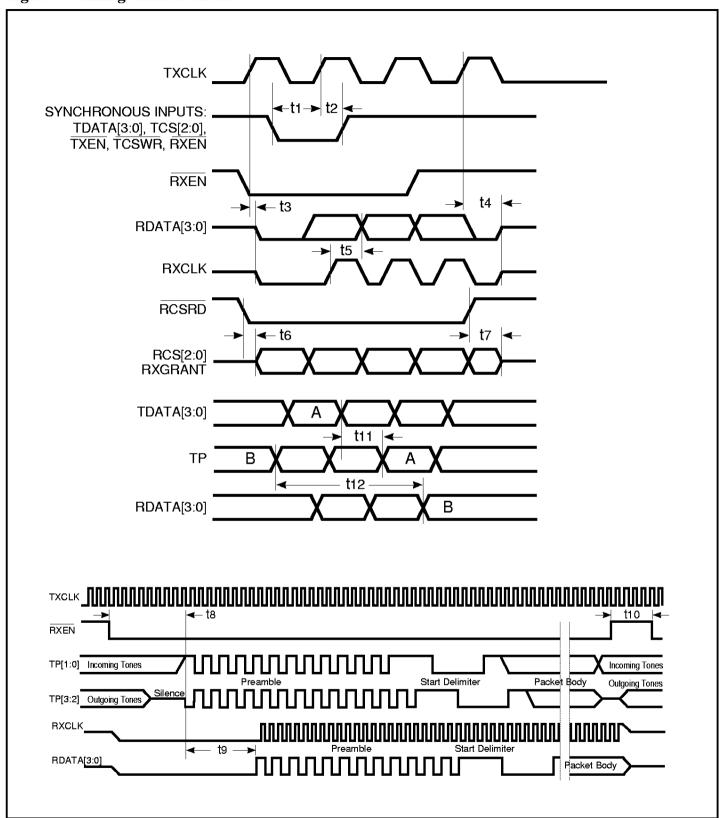

**Table 12. Timing Specifications** (BT = Bit Times) (See Figure 4)

| Symbol | Parameter      | Description                                                                                      | Min. | Тур. | Max. | Units |

|--------|----------------|--------------------------------------------------------------------------------------------------|------|------|------|-------|

| t1     | tsetup         | Synchronous Input Setup Time to Rising Edge of TXCLK for TDATA[3:0], TCS[2:0], TXEN, TCSWR, RXEN | 7    | _    |      | ns    |

| t2     | thold          | Synchronous Input Hold Time to Rising Edge of TXCLK for TDATA[3:0]. TCS[2:0], TXEN, TCSWR, RXEN  | 2    | _    | _    | ns    |

| t3     | trxen          | Time from TXCLK (RXEN Asserted) to RXCLK and RDATA[3:0] Driven                                   | _    | _    | 15   | ns    |

| t4     | trxdis         | Time from TXCLK (\overline{RXEN} Deasserted) to RXCLK and RDATA[3:0] Tri-stated                  | _    | _    | 15   | ns    |

| t5     | trdv           | RDATA Valid after RXCLK Rising Edge                                                              | 3    | _    | 20   | ns    |

| t6     | trcsen         | RCSRD Asserted to RCS[2:0] and RXGRANT Valid                                                     | _    |      | 15   | ns    |

| t7     | trcsdis        | RCSRD Deasserted to RCS[2:0] and RXGRANT Tri-stated                                              | _    | _    | 15   | ns    |

| t8     | trxpre         | RXEN Asserted to Start of Preamble for Valid Packet Reception                                    | 6    | _    |      | ВТ    |

| t9     | <b>t</b> prerd | Time from Preamble to RDATA, RXCLK Valid                                                         | _    | _    | 20   | ВТ    |

| t10    | trxmin         | Minimum Time for RXEN must be deasserted so that DC balance can be achieved for TCS requirement  | 16   | _    | _    | ВТ    |

| t11    | <b>t</b> DTP   | TDATA to TP                                                                                      | 33   |      | 167  | ns    |

| t12    | <b>t</b> PRD   | TP to RDATA                                                                                      | 65   | _    | 235  | ns    |

| _      | tskew          | Timing Skew Between TP Inputs During Start of Preamble                                           | _    |      | 2    | ВТ    |

|        |                | RXCLK Duty Cycle                                                                                 | 40   | _    | 60   | %     |

| _      | trxj           | RXCLK Cycle-to-cycle Jitter                                                                      | _    |      | ±2.0 | ns    |

|        | <b>t</b> TXPJ  | TXCLK Peak-to-peak Jitter                                                                        | _    |      | 1.0  | ns    |

9

Figure 4. Timing Characteristics

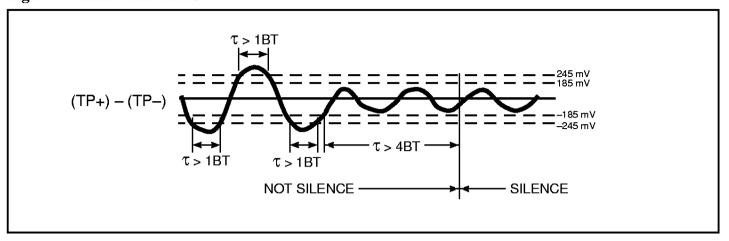

Figure 5. Silence Thresholds

Figure 6. TP Output Data Test Load

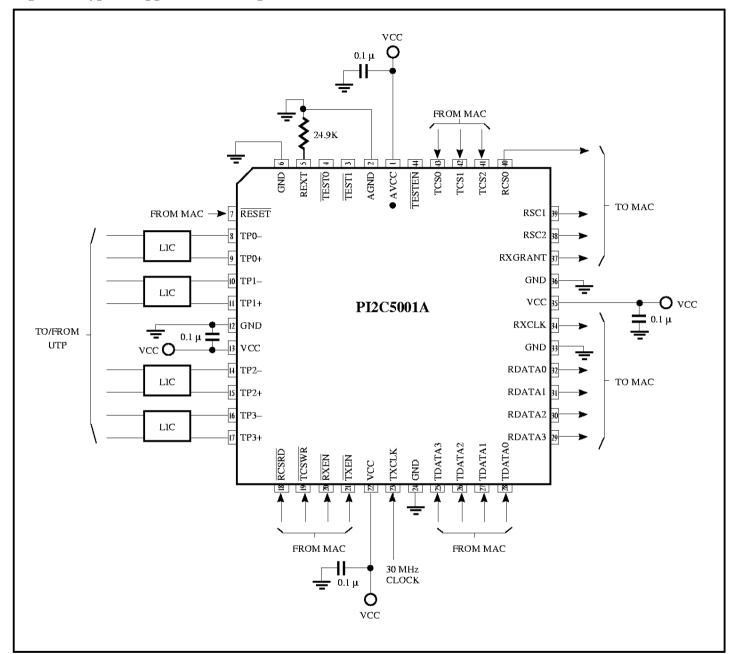

Figure 7. Typical Application Configuration

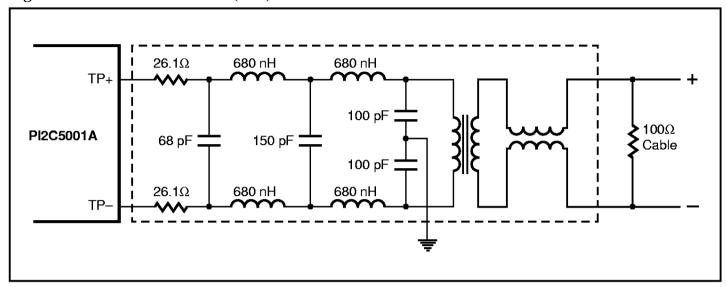

Figure 8. Line Interface Circuit (LIC)

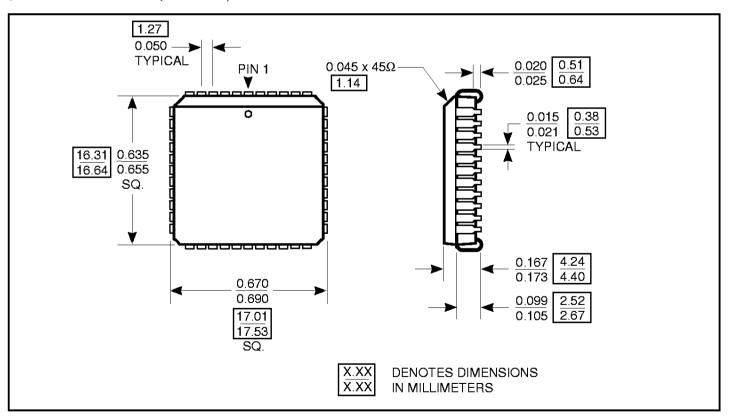

# **Package Information**

## J-44 — 44-Pin PLCC (680 x 680)

### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com