# **82C89**

#### CMOS Bus Arbiter

#### Features

- Pin Compatible with Bipolar 8289

- Scaled SAJI IV CMOS Process

- Low Power Operation

- Compatible with 5MHz and 8MHz 80C86 and 80C88

- Provides Multi-Master System Bus Control and Arbitration

- Provides Simple Interface With 82C88/8288 Bus Controller

- Synchronizes 80C86/8086, 80C88/8088 Processors with Multi-Master Bus

- . Bipolar Drive Capability, Fully TTL Compatible

- Four Operating Modes for Flexible System Configuration

- Wide Operating Temperature Ranges:

- ► C82C89 ......0°C to +70°C

- ▶ 182C89.....-40°C to +85°C

- ► M82C89.....-55°C to +125°C

## Description

The Harris 82C89 Bus Arbiter is manufactured using a self-aligned silicon gate CMOS process (Scaled SAJI IV). This circuit along with the 82C88 bus controller, provides full bus arbitration and control for multi-processor systems. The 82C89 is typically used in medium to large 80C86 or 80C88 systems where access to the bus by several processors must be coordinated. The 82C89 also provides high output current and capacitive drive to eliminate the need for additional bus buffering.

Static CMOS circuit design insures low operating power. The advanced Harris SAJI CMOS process results in performance equal to or greater than existing equivalent products at a significant power savings.

#### **Pinouts** TOP VIEW <u>\$2</u>d 1 20 Þ VCC 丽山2 19 651 SYSB/RESB 3 18 D 50 RESB 7 4 17 bclk 16 DIOCK BCLK II 5 INIT d 6 15 CROLCK BREO M 7 14 HANYROST BPRO d B 13 DAEN BPRN - 9 12 LCBRO GND 🗖 10 11 DBUSY LCC/PLCC TOP VIEW 18 ∏ 50 RESR 17 CLK 16 \\ \\_\\_\tagk INIT [ 15 CROLCK ANYROST

# Pin Description

| SYMBOL        | PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCC           | 20            |      | VCC: The +5V Power supply pin. A $0.1\mu\mathrm{F}$ capacitor between pins 10 and 20 is recommended for decoupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| GND           | 10            |      | GROUND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| \$0, \$1, \$2 | 1, 18-19      | 1    | STATUS INPUT PINS: The status input pins from an 80C86, 80C88 or 8089 processor. The 82C89 decodes these pins to initiate bus request and surrender actions. (See Table 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| CLK           | 17            | ı    | CLOCK: From the 82C84A or 82C85 clock chip and serves to establish when bus arbiter actions are initiated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| LOCK          | 16            | I    | LOCK: A processor generated signal which when activated (low) prevents the arbiter from surrendering the multi-master system bus to any other bus arbiter, regardless of its priority.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CROLCK        | 15            | I    | COMMON REQUEST LOCK: An active low signal which prevents the arbiter from surrendering the multi-master system bus to any other bus arbiter requesting the bus through the CBRQ input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RESB          | 4             | ı    | RESIDENT BUS: A strapping option to configure the arbiter to operate in systems having both a multi-master system bus and a Resident Bus. Strapped high, the multi-master system bus is requested or surrendered as a function of the SYSB/RESB input pin. Strapped low, the SYSB/RESB input is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| ANYRQST       | 14            | l    | ANY REQUEST: A strapping option which permits the multi-master system bus to be surrendered to a lower priority arbiter as if it were an arbiter of higher priority (i.e., when a lower priority arbiter requests the use of the multi-master system bus, the bus is surrendered as soon as it is possible). When ANYROST is strapped low, the bus is surrendered according to Table 1. If ANYRQST is strapped high and CBRQ is activated, the bus is surrendered at the end of the present bus cycle. Strapping CBRQ low and ANYROST high forces the 82C89 arbiter to surrender the multi-master system bus after each transfer cycle. Note that when surrender occurs BREQ is driven false (high).                                                                                                                                                                                                                                                                                                   |  |

| ЮВ            | 2             | ı    | IO BUS: A strapping option which configures the 82C89 Arbiter to operate in system naving both an IO Bus (Peripheral Bus) and a multi-master system bus. The arbiter request and surrenders the use of the multi-master system bus as a function of the status line. So the multi-master system bus is permitted to be surrendered while the processor performing IO commands and is requested whenever the processor performs a memor command. Interrupt cycles are assumed as coming from the peripheral bus and are treated as an IO command.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| ĀĒN           | 13            | 0    | ADDRESS ENABLE: The output of the 82C89 Arbiter to the processor's address latches, to the 82C88 Bus Controller and 82C84A or 82C85 Clock Generator. AEN serves to instruct the Bus Controller and address latches when to three-state their output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| INIT          | 6             | l    | INITIALIZE. An active low multi-master system bus input signal used to reset all the bus arbiters on the multi-master system bus. After initialization, no arbiters have the use of the multi-master system bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SYSB/RESB     | 3             | ţ    | SYSTEM BUS/RESIDENT BUS: An input signal when the arbiter is configured in the System/Resident Mode (RESB is strapped high) which determines when the multi-master system bus is requested and multi-master system bus surrendering is permitted. The signal is intended to originate from a form of address-mapping circuitry, such as a decoder or PROM attached to the resident address bus. Signal transitions and glitches are permitted on this pin from $\phi$ 1 of T4 to $\phi$ 1 of T2 of the processor cycle. During the period from $\phi$ 1 of T2 to $\phi$ 1 of T4, only clean transitions are permitted on this pin (no glitches). If a glitch occurs, the arbiter may capture or miss it, and the multi-master system bus may be requested or surrendered, depending upon the state of the glitch. The arbiter requests the multi-master system bus in the System/Resident Mode when the state of the SYSB/RESB pin is nigh and permits the bus to be surrendered when this pin is low. |  |

## Pin Description

| SYMBOL | PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBRQ   | 12            | 1/0  | COMMON BUS REQUEST: An input signal which instructs the arbiter if there are any other arbiters of lower priority requesting the use of the multi-master system bus.  The CBRQ pins (open-drain output) of all the 82C89 Bus Arbiters which surrender to the multi-master system bus upon request are connected together.  The Bus Arbiter running the current transfer cycle will not itself pull the CBRQ line low. Any other arbiter connected to the CBRQ line can request the multi-master system bus. The arbiter presently running the current transfer cycle drops its BREQ signal and surrenders the bus whenever the proper surrender conditions exist. Strapping CBRQ low and ANYRQST high allows the multi-master system bus to be surrendered after each transfer cycle. See the pin definition of ANYRQST. |

| BCLK   | 5             | I    | BUS CLOCK: The multi-master system bus clock to which all multi-master system bus interface signals are synchronized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BREQ   | 7             | 0    | BUS REQUEST: An active low output signal in the Parallel Priority Resolving Scheme which the arbiter activates to request the use of the multi-master system bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BPRN   | 9             | 1    | BUS PRIORITY IN: The active low signal returned to the arbiter to instruct it that it may acquire the multi-master system bus on the next falling edge of BCLK BPRN active indicates to the arbiter that it is the highest priority requesting arbiter presently on the bus. The loss of BPRN instructs the arbiter that it has lost priority to a higher priority arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BPRO   | 8             | 0    | BUS PRIORITY OUT: An active low output signal used in the serial priority resolving scheme where BPRO is daisy-chained to BPRN of the next lower priority arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BUSY   | 11            | I/O  | BUSY: An active low open-drain multi-master system bus interface signal used to instruct all the arbiters on the bus when the multi-master system bus is available. When the multi-master system bus is available the highest requesting arbiter (determined by BPRN) seizes the bus and pulls BUSY low to keep other arbiters off of the bus. When the arbiter is done with the bus, it releases the BUSY signal, permitting it to go high and thereby allowing another arbiter to acquire the multi-master system bus                                                                                                                                                                                                                                                                                                  |

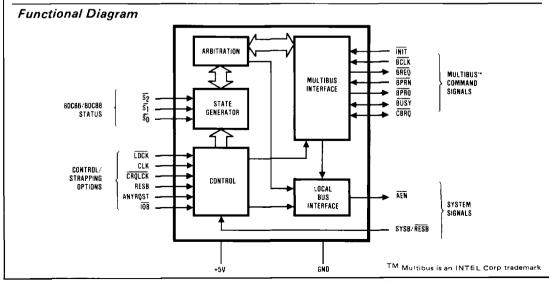

## Functional Description

The 82C89 Bus Arbiter operates in conjunction with the 82C88 Bus Controller to interface 80C86, 80C88 processors to a multi-master system bus (both the 80C86 and 80C88 are configured in their max mode). The processor is unaware of the arbiter's existence and issues commands as though it has exclusive use of the system bus. If the processor does not have the use of the multi-master system bus, the arbiter prevents the Bus Controller (82C88), the data transceivers and the address latches from accessing the system bus (e.g. all bus driver outputs are forced into the high impedance state). Since the command sequence was not issued by the 82C88, the system bus will appear as "Not Ready" and the processor will enter wait states. The processor will remain in Wait until the Bus Arbiter acquires the use of the multi-master system bus whereupon the arbiter will allow the bus controller, the data transceivers, and the address latches to access the system. Typically, once the command has been issued and a data transfer has taken place, a transfer acknowledge (XACK) is returned to the processor to indicate "READY" from the accessed slave device. The processor then completes its transfer cycle. Thus the arbiter serves to multiplex a processor (or bus master) onto a multi-master system bus and avoid contention problems between bus masters.

#### **Arbitration Between Bus Masters**

In general, higher priority masters obtain the bus when a lower priority master completes its present transfer cycle. Lower priority bus masters obtain the bus when a higher priority master is not accessing the system bus. A strapping option (ANYRQST) is provided to allow the arbiter to surrender the bus to a lower priority master as though it were a master of higher priority. If there are no other bus masters requesting the bus, the arbiter maintains the bus so long as its processor has not entered the HALT State. The arbiter will not voluntarily surrender the system bus and has to be forced off by another master's bus request, the HALT State being the only exception. Additional strapping options permit other modes of operation wherein the multi-master system bus is surrendered or requested under different sets of conditions.

#### **Priority Resolving Techniques**

Since there can be many bus masters on a multi-master system bus, some means of resolving priority between bus masters simultaneously requesting the bus must be provided. The 82C89 Bus Arbiter provides several resolving techniques. All the techniques are based on a priority

concept that at a given time one bus master will have priority above all the rest. There are provisions for using parallel priority resolving techniques, serial priority resolving techniques, and rotating priority techniques.

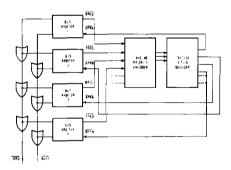

#### Parallel Priority Resolving

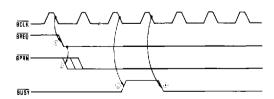

The parallel priority resolving technique uses a separate bus request line BREQ for each arbiter on the multi-master system bus, see Figure 1. Each BREQ line enters into a priority encoder which generates the binary address of the highest priority BREQ line which is active. The binary address is decoded by a decoder to select the corresponding BPRN (Bus Priority In) line to be returned to the highest priority requesting arbiter. The arbiter receiving priority (BPRN true) then allows its associated bus master onto the multi-master system bus as soon as it becomes available (i.e., the bus is no longer busy). When one bus arbiter gains priority over another arbiter it cannot immediately seize the bus, it must wait until the present bus transaction is complete. Upon completing its transaction the present bus occupant recognizes that it no longer has priority and surrenders the bus by releasing BUSY BUSY is an active low "OR" tied signal line which goes to every bus arbiter on the system bus. When BUSY goes inactive (high), the arbiter which presently has bus priority (BPRN true) then seizes the bus and pulls BUSY low to keep other arbiters off of the bus. See waveform timing diagram, Figure 2. Note that all multi-master system bus transac-

FIGURE 1. PARALLEL PRIORITY RESOLVING TECHNIQUE

#### NOTES

- ① Higher priority bus arbiter requests the Multi-Master system bus

- ② Attains priority.

- ① Lower priority bus arbiter releases BUSY

- Higher priority bus arbiter then acquires the bus and pulls BUSY down

FIGURE 2. HIGHER PRIORITY ARBITER OBTAINING THE BUS FROM A LOWER PRIORITY ARBITER

tions are synchronized to the bus clock ( $\overline{BCLK}$ ). This allows the parallel priority resolving circuitry or any other priority resolving scheme employed to settle.

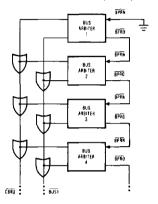

#### Serial Priority Resolving

The serial priority resolving technique eliminates the need for the priority encoder-decoder arrangement by daisy-chaining the bus arbiters together, connecting the higher priority bus arbiter's BPRO (Bus Priority Out) output to the BPRN of the next lower priority. See Figure 3.

NOTE

The number of arbiters that may be daisy-chained together in the serial priority resolving scheme is a function of BCLK and the propagation delay from arbiter to arbiter. Normally, at 10MHz only 3 arbiters may be daisy-chained.

#### FIGURE 3. SERIAL PRIORITY RESOLVING

#### **Rotating Priority Resolving**

The rotating priority resolving technique is similar to that of the parallel priority resolving technique except that priority is dynamically re-assigned. The priority encoder is replaced by a more complex circuit which rotates priority between requesting arbiters thus allowing each arbiter an equal chance to use the multi-master system bus, over time

#### Which Priority Resolving Technique To Use

There are advantages and disadvantages for each of the techniques described above. The rotating priority resolving technique requires substantial external logic to implement while the serial technique uses no external logic but can accommodate only a limited number of bus arbiters before the daisy-chain propagation delay exceeds the multi-master's system bus clock (BCLK). The parallel priority resolving technique is in general a good compromise between the other two techniques. It allows for many arbiters to be present on the bus while not requiring too much logic to implement.

#### 82C89 Modes Of Operation

There are two types of processors for which the 82C89 will provide support: An Input/Output processor (i.e. an NMOS 8089 IOP) and the 80C86, 80C88. Consequently,

there are two basic operating modes in the 82C89 bus arbiter. One, the IOB (I/O Peripheral Bus) mode, permits the processor access to both an I/O Peripheral Bus and a multi-master system bus. The second, the RESB (Resident Bus mode), permits the processor to communicate over both a Resident Bus and a multi-master system bus. An I/O Peripheral Bus is a bus where all devices on that bus, including memory, are treated as I/O devices and are addressed by I/O commands. All memory commands are directed to another bus, the multi-master system bus. A Resident Bus can issue both memory and I/O commands, but it is a distinct and separate bus from the multi-master system bus. The distinction is that the Resident Bus has only one master, providing full availability and being dedicated to that one master.

The IOB strapping option configures the 82C89 Bus Arbiter into the IOB mode and the strapping option RESB

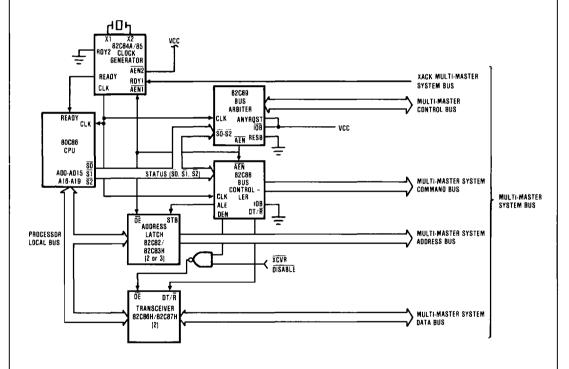

configures it into the RESB mode. It might be noted at this point that if both strapping options are strapped false, the arbiter interfaces the processor to a multi-master system bus only (see Figure 4). With both options strapped true, the arbiter interfaces the processor to a multi-master system bus. a Resident Bus. and an I/O Bus.

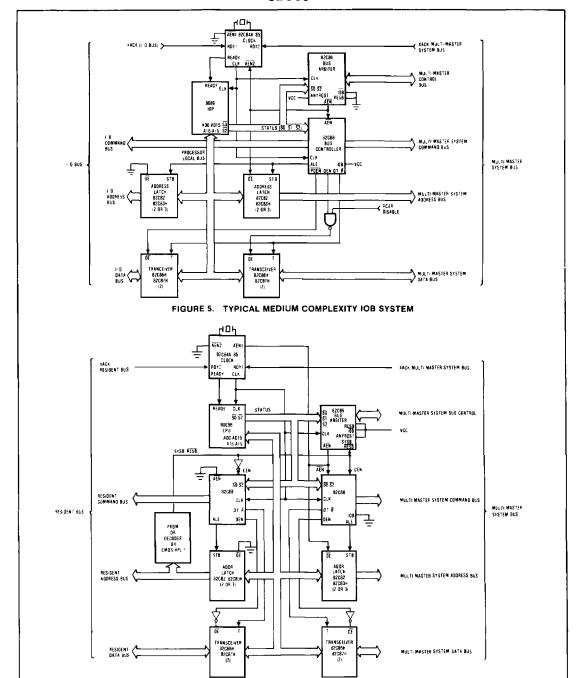

In the  $\overline{\text{IOB}}$  mode, the processor communicates and controls a host of peripherals over the Peripheral Bus. When the I/O Processor needs to communicate with system memory, it does so over the system memory bus. Figure 5 shows a possible I/O Processor system configuration.

The 80C86 and 80C88 processors can communicate with a Resident Bus and a multi-master system bus. Two bus controllers and only one Bus Arbiter would be needed in such a configuration as shown in Figure 6. In such a system configuration the processor would have access to

FIGURE 4. TYPICAL MEDIUM COMPLEXITY CPU SYSTEM

\* By adding another 82C89 arbiter and connecting its AEN to the 82C88 whose AEN is presently grounded. The processor could have access to two multi-master buses.

FIGURE 6. 82C89 BUS ARBITER SHOWN IN SYSTEM- RESIDENT BUS CONFIGURATION

memory and peripherals of both busses. Memory mapping techniques are applied to select which bus is to be accessed. The SYSB/RESB input on the arbiter serves to instruct the arbiter as to whether or not the system bus is to be accessed. The signal connected to SYSB/RESB

also enables or disables commands from one of the bus controllers.

A summary of the modes that the 82C89 has, along with its response to its status lines inputs, is shown in Table 1.

TABLE 1. SUMMARY OF 82C89 MODES, REQUESTING AND RELINQUISHING THE MULTI-MASTER SYSTEM BUS

| STATUS LINES FROM<br>80C86 OR 80C88 OR 8088 |            | 10B MODE   |           | IOB MODE I | SINGLE BUS MODE TOB = HIGH RESB = LOW |               |                |               |          |

|---------------------------------------------|------------|------------|-----------|------------|---------------------------------------|---------------|----------------|---------------|----------|

|                                             | <u>\$2</u> | <u>\$1</u> | <u>50</u> |            | SYSB/RESB=High                        | SYSB/RESB=Low | SYSB/RESB=High | SYSB/RESB=Low |          |

| I/O                                         | 0          | 0          | 0         | x          | <b>√</b>                              | ×             | ×              | x             | ,        |

| COMMANDS                                    | 0          | Q          | 1         | x          | ✓                                     | ×             | x              | ×             | <i></i>  |

|                                             | 0          | 1          | 0         | x          | ✓                                     | x             | x              | ×             | ✓        |

| HALT                                        | 0          | 1          | 1         | ×          | х                                     | x             | х              | x             | ×        |

| MEM                                         | 1          | 0          | 0         | _          |                                       | ×             | <b>√</b>       | x             | _        |

| COMMANDS                                    | 1          | 0          | 1         | ✓          | ✓                                     | X             | √              | ×             | ✓        |

|                                             | 1          | 1          | 0         | ✓          | ✓                                     | x             | ✓              | x             | <b>✓</b> |

| IDLE                                        | 1          | 1          | 1         | х          | ×                                     | X             | x              | X             | ×        |

#### NOTES

- 1 X = Multi-Master System Bus is allowed to be Surrendered.

- 2. J = Multi-Master System Bus is Requested

|                                 |                           | MULTI-MASTER SYSTEM BUS                         |                                                                        |  |  |

|---------------------------------|---------------------------|-------------------------------------------------|------------------------------------------------------------------------|--|--|

| MODE                            | PIN<br>STRAPPING          | REQUESTED**                                     | SURRENDERED*                                                           |  |  |

| Single Bus<br>Multi-Master Mode | IOB = High<br>RESB = Low  | Whenever the processor's status lines go active | HLT + TI • CBRQ + HPBRQ †                                              |  |  |

| RESB Mode Only                  | IOB = High<br>RESB = High | SYSB/RESB = High •<br>ACTIVE STATUS             | (SYSB RESB = Low + TI) •<br>CBRO + HLT + HPBRQ                         |  |  |

| IOB Mode Only                   | IOB = Low<br>RESB = Low   | Memory Commands                                 | (I/O Status + TI) • CBAQ +<br>HLT + HPBRQ                              |  |  |

| IOB Mode RESB Mode              | IOB = Low<br>RESB = High  | (Memory Command) ●<br>(SYSB/RESB = High)        | ((I O Status Commands) +<br>SYSB:RESB = LOW) ◆ CBRO<br>+ HPBRQ † + HLT |  |  |

#### NOTES:

- · LOCK prevents surrender of Bus to any other arbiter CRQLCK prevents surrender of Bus to any lower priority arbiter

- \*\* Except for HALT and Passive or IDLE Status.

- † HPBRQ. Higher priority Bus request or BPRN = 1.

- 1 IOB Active Low.

- 2. RESB Active High

- 3. + is read as 'OR" and as 'AND

- 4. Ti = Processor Idle Status \$2, \$1, \$0 = 111

- 5. HLT = Processor Half Status \$\overline{52}\$, \$\overline{51}\$, \$\overline{50}\$ = 011

# Specifications 82C89

# **Absolute Maximum Ratings**

| Supply Voltage                                    |                                               | +8.0 Volts                          |

|---------------------------------------------------|-----------------------------------------------|-------------------------------------|

| Input, Output or I/O Voltage Applied              |                                               |                                     |

| Maximum Package Power Dissipatio                  | n                                             | 1 Watt                              |

| Storage Temperature Range                         |                                               |                                     |

| θ <sub>iC</sub>                                   | 26°C/W (CERDIP package),                      | 31ºC/W (LCC package)                |

| $\theta_{ia}$                                     |                                               |                                     |

| Gate Count                                        |                                               | 200 Gates                           |

| Junction Temperature                              |                                               | +150°C                              |

| Lead Temperature (Soldering, Ten S                | Seconds)                                      | +275°C                              |

| CAUTION: Stresses above those listed in the "A    | BSOLUTE MAXIMUM RATINGS may cause             | e permanent damage to the device.   |

| This is a stress only rating and operation of the | device at these or any other conditions above | re those indicated in the operation |

# **Operating Conditions**

| Operating Voltage Range     | +4.5V to +5.5V  |

|-----------------------------|-----------------|

| Operating Temperature Range |                 |

| C82C89                      | 0°C to +70°C    |

| 182C89                      | 40°C to +85°C   |

| M82C89                      | -55°C to +125°C |

**D.C. Electrical Specifications** VCC = 5.0V  $\pm$  10%; T<sub>A</sub> = 0°C to +70°C (C82C89); T<sub>A</sub> = -40°C to +85°C (I82C89); T<sub>A</sub> = -55°C to +125°C (M82C89)

| SYMBOL          | PARAMETER                                    | MIN             | MAX                  | UNITS  | TEST CONDITIONS                                                            |

|-----------------|----------------------------------------------|-----------------|----------------------|--------|----------------------------------------------------------------------------|

| VIH             | Logical One Input Voltage                    | 2.0<br>2.2      |                      | V<br>V | C82C89, 182C89<br>M82C89                                                   |

| VIL             | Logical Zero Input Voltage                   |                 | 0.8                  | ٧      |                                                                            |

| VIHC            | CLK Logical One Input Voltage                | 0.7 VCC         |                      | ٧      |                                                                            |

| VILC            | CLK Logical Zero Input Voltage               |                 | 0.2 VCC              | ٧      |                                                                            |

| V <sub>OL</sub> | Output Low Voltage BUSY, CBRQ AEN BPRO, BREQ |                 | 0.45<br>0.45<br>0.45 | V<br>V | I <sub>OL</sub> = 20mA<br>I <sub>OL</sub> = 16mA<br>I <sub>OL</sub> = 10mA |

| νон             | Output High Voltage<br>BUSY, CBRQ            | Open            | -Drain               |        |                                                                            |

|                 | All other Outputs                            | 3.0<br>VCC -0.4 |                      | V<br>V | I <sub>OH</sub> = -2.5mA<br>I <sub>OH</sub> = -100μA                       |

| II              | Input Leakage Current                        | -1.0            | 1.0                  | μΑ     | VIN = GND or VCC<br>DIP Pins 1-6, 9, 14-19                                 |

| 10              | I/O Leakage                                  | -10.0           | 10.0                 | μΑ     | VO = GND orVCC<br>DIP Pins 11-12                                           |

| ICCSB           | Standby Power Supply Current                 |                 | 10                   | μΑ     | VCC = 5.5V<br>VIN = VCC or GND<br>Outputs Open                             |

| ICCOP           | Operating Power Supply Current               |                 | 1                    | mA/MHz | VCC = 5.5V<br>Outputs Open<br>See Note 1                                   |

NOTE 1 Maximum current defined by CLK or BCLK, whichever has the highest operating frequency

# Capacitance TA = 25°C

| SYMBOL | PARAMETER          | TYPICAL | UNITS | TEST CONDITIONS                                      |

|--------|--------------------|---------|-------|------------------------------------------------------|

| CiN    | Input Capacitance  | 5       | pF    | FREQ = 1MHz, all measure-<br>ments are referenced to |

| Соит   | Output Capacitance | 15      | pF    | device GND                                           |

**A.C. Electrical Specifications**  $VCC = +5V \pm 10\%$ , GND = 0V:  $T_A = 0^{\circ}C$  to  $70^{\circ}C$  (C82C89)  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$  (I82C89)  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  (M82C89)

| SYMBOL      | PARAMETER                  | MIN                 | MAX         | UNIT | TEST CONDITION           |

|-------------|----------------------------|---------------------|-------------|------|--------------------------|

| (1) TCLCL   | CLK Cycle Period           | 125                 |             | ns   | Note 3                   |

| (2) TCLCH   | CLK Low Time               | 55                  |             | ns   | 1                        |

| (3) TCHCL   | CLK High Time              | 35                  |             | ns   |                          |

| (4) TSVCH   | Status Active Setup        | 65                  | TCLCL-10    | ns   |                          |

| (5) TSHCL   | Status Inactive Setup      | 50                  | TCLCL-10    | ns   | ]                        |

| (6) THVCH   | Status Inactive Hold       | 10                  |             | ns   |                          |

| (7) THVCL   | Status Active Hold         | 10                  |             | ns   |                          |

| (8) TBYSBL  | BUSY* Setup to BCLK        | 20                  |             | ns   |                          |

| (9) TCBSBL  | CBRQ⊺⊥ Setup to BCLK.      | 20                  |             | ns   |                          |

| (10) TBLBL  | BCLK Cycle Time            | 100                 |             | ns   |                          |

| (11) TBHCL  | BCLK High Time             | 30                  | 0.65(TBLBL) | ns   | ]                        |

| (12)TOLLL1  | LOCK Inactive Hold         | 10                  |             | ns   | ]                        |

| 13)TCLLL2   | LOCK Active Setup          | 40                  |             | ns   | 1 1                      |

| (14) TPNBL  | BPRN11 to BCLK Setup Time  | 20                  |             | ns   |                          |

| (15)TCLSR1  | SYSB/RESB Setup            | 0                   |             | ns   | 1                        |

| -16)TCLSR2  | SYSB/RESB Hold             | 30                  | <u> </u>    | ns   | 1                        |

| 17) TIVIH   | Initialization Pulse Width | 3 TBLBL+<br>3 TCLCL |             | ns   | ]                        |

| (18) TBLBRL | BCLK to BREQ Delay.        |                     | 35          | ns   | 1 +                      |

| 19)TBLPOH   | BCLK to BPROIT             |                     | 35          | ns   | Note 1 and 3             |

| 201 TPNPO   | BPRNII to BPROIT Delay     |                     | 22          | ns   | Note 1 and 3             |

| (21)TBLBYL  | BCLK to BUSY Low           |                     | 60          | ns   | Note 3                   |

| 1221TBLBYH  | BCLK to BUSY Float         |                     | 35          | ns   | Note 2 and 3             |

| (23)TCLAEH  | CLK to AEN High            |                     | 65          | ns   | Note 3                   |

| (24)TBLAEL  | BCLK to AEN Low            | 1                   | 40          | ns   | Note 3                   |

| (25)TBLCBL  | BCLK to CBRQ Low           |                     | 60          | ns   | Note 3                   |

| :26:TBLCBH  | BCLK to CBRQ Float         |                     | 35          | ns   | Note 2 and 3             |

| (27) TOLOH  | Output Rise Time           |                     | 20          | ns   | From 0.8V to 2 0V Note 4 |

| (28) TOHOL  | Output Fall Time           |                     | 12          | ns   | From 2.0V to 0.8V Note 4 |

| (29) TILIH  | Input Rise Time            |                     | 20          | ns   | From 0.8V to 2.0V        |

| (30) TIHIL  | Input Fall Time            |                     | 20          | ns   | From 2 0V to 0.8V        |

NOTES: 1. BCLK generates the first BPRO wherein subsequent BPRO changes lower in the chain are generated through BPRON

- 2. Measured at 0.5V above GND.

- a. Inveasured at 0.5V above GND.

All A C\_parameters tested as per test circuits in Figures 7—9. Input rise and fall times are driven at 1ns/V.

Except BUSY and CBRO.

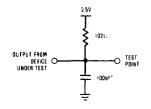

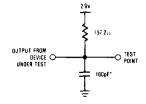

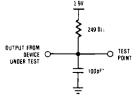

## A.C. Test Circuits

\*Includes stray and jig capacitance

FIGURE 7. **BUSY, CBRQ LOAD CIRCUIT**

FIGURE 8. **AEN LOAD CIRCUIT**

FIGURE 9. BPRO, BREQ LOAD CIRCUIT

# A.C. Testing Input, Output Waveforms

A C Testing. Inputs are driven at VIH+0.4V for a logic "1" and VIL -0.4V for a logic "0" The clock is driven at 4.1V and 0.4V. Timing measurements are made at 1.5V for both a logic "1" and "0"

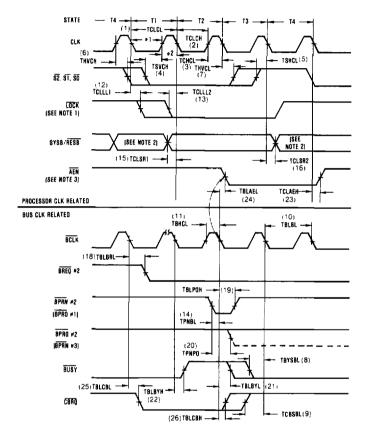

#### Waveforms

#### NOTES

- 1 Lock active can occur during any state last long as the relationships shown above with respect to the CLK are maintained. LOCK inactive has no critical time and can be asynchronous. GROLCK has no critical timing and is considered an asynchronous input signal.

- 2. Glitching of SYSB RESB is permitted during this time. After φ2 of T1, and before φ1 of T4, SYSB RESB should be stable to maintain system effi-

- 3 AEN leading edge is related to BCLK trailing edge to CLK. The trailing edge of AEN occurs after bus priority is lost

#### ADDITIONAL NOTES

The signals related to CLK are typical processor signals, and do not relate to the depicted sequence of events of the signals referenced to BCLK. The signals shown related to the BCLK represent a hypothetical sequence of events for illustration. Assume 3 bus arbiters of priorities 1,2 and 3 configured in serial priority resolving scheme (as shown in Figure 3). Assume arbiter 1 has the <u>bus</u> and is holding BUSY low. Arbiter #2 detects its processor wants the bus and pulls low. BREG #2 if BRN #2 is high (as shown), arbiter #2 will pull low. CPRQ line. CBRQ signals to the higher priority arbiter #1 that a lower priority arbiter would be granted BPRN when it makes the bus request rather than having to wait for another arbiter to release the bus through CBRQ. "Arbiter #1 will reinquish the multi-master system bus when it enters a state not requiring it (see Table 1), by lowering its BPRQ #1 itted to BPRN #2) and releasing BUSY Arbiter #2 now sees that is has priority from BPRN #2 being low and releases CBRQ. As soon as BUSY signifies the bus is available (high), arbiter #2 pouls BUSY low on next falling edge of BCLK. Note that if arbiter #2 didn't want the bus at the time it received priority, it would pass priority to the next lower priority arbiter by lowering its BPRQ #2 [TPNPQ].

\*Note that even a higher priority arbiter which is acquiring the bus through BPRN will momentarily drop CBRQ until it has acquired the bus