# FPD87392

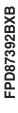

FPD87392BXB +3.3V TFT-LCD Timing Controller with Dual LVDS Inputs/Dual RSDS Outputs for TFT-LCD Monitor and Notebook (SXGA/SXGA+/UXGA)

Literature Number: SNOSAD3A

# FPD87392BXB +3.3V TFT-LCD Timing Controller with Dual LVDS Inputs/Dual RSDS<sup>™</sup> Outputs for TFT-LCD Monitor and Notebook (SXGA/SXGA+/UXGA)

# **General Description**

The FPD87392BXB Panel Timing Controller is an integrated FPD-Link + RSDS™ + TFT-LCD Timing Controller. The logic architecture is implemented using standard and default timing controller functionality based on an Embedded Gate Array. The device is reconfigurable to the needs of a specific application by providing user-defined specifications or customer supplied VHDL/Verilog code.

The FPD87392BXB is a timing controller that combines an LVDS dual pixel input interface with National's Reduced Swing Differential Signaling (RSDS<sup>™</sup>) output column driver interface for SXGA, SXGA+ and UXGA resolutions. It resides on the TFT-LCD panel and provides the data buffering and control signal generation. The RSDS<sup>™</sup> data path to the column driver contributes toward lowering radiated EMI and reduced system dynamic power consumption. The RSDS<sup>™</sup> dual 12 pair differential bus conveys up to 24-bit color data for SXGA/SXGA+/UXGA panels when using VESA 60Hz standard timing.

### **Features**

- Input frequency range from 25 MHz to 85 MHz

- Support display resolutions SXGA (1280x1024), SXGA+ (1400x1050) and UXGA (1600x1200)

- Embedded gate array for custom panel timing

- RSDS™ (Reduced Swing Differential Signaling) Column Driver bus for low power and reduced EMI

- Drives RSDS<sup>™</sup> column driver up to 170 Mb/s with an 85 MHz clock

- 6 or 8 bit LVDS dual pixel input interface (FPD-Link)

- Virtual 8-bit color depth in FRC mode

- Flexible RSDS<sup>™</sup> data output mapping for Bottom or Top mount

- Supports 1 and 2 line inversion mode for RVS output

- Supports Graphics Controllers with spread spectrum interface for lower EMI

- Free Run Mode Function

- Fail-safe function in DE mode (Bonding Option)

Supports DE mode and SYNC only mode (Bonding

- Option)

- Power-On-Reset Support

- CMOS circuitry operates from a 3.0V to 3.6V supply

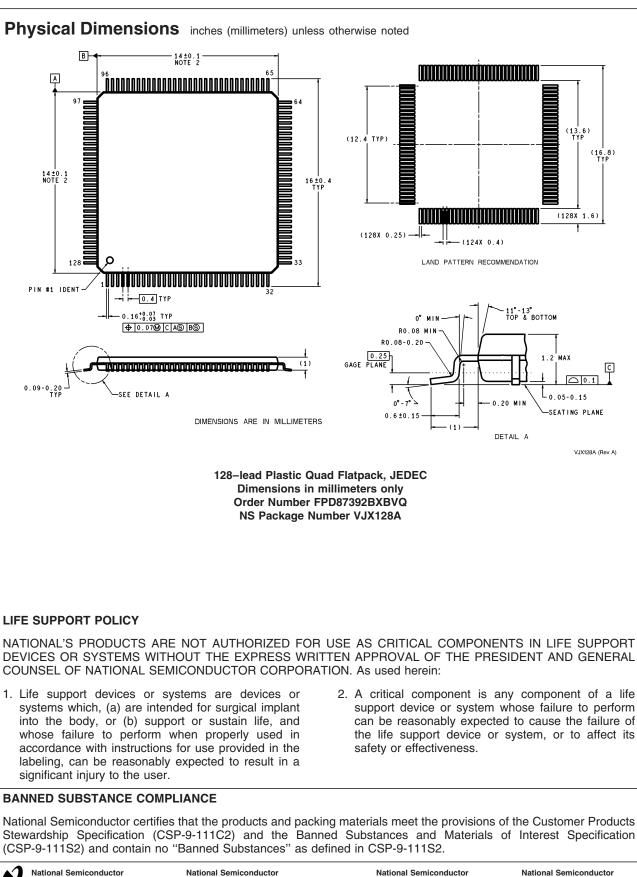

- 128 TQFP package with body size 14mm x 14mm x 1.0mm, 0.4mm Pitch

July 2004

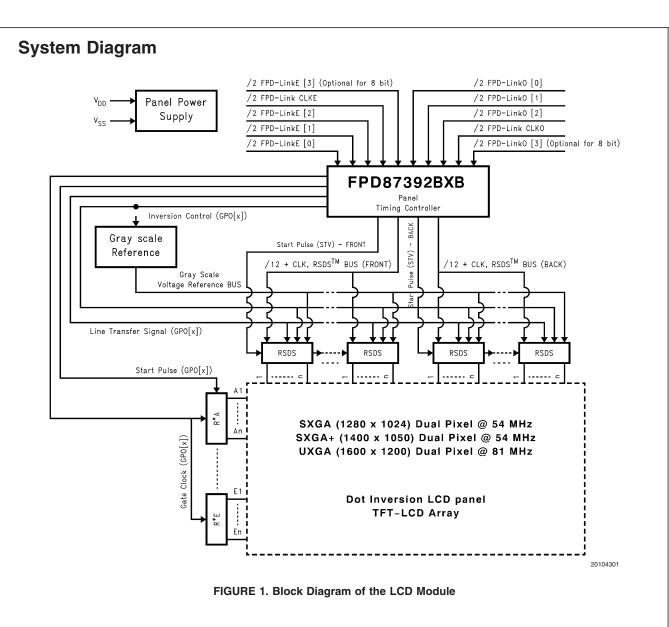

FIGURE 2. Block Diagram

# **Functional Description**

#### DUAL FPD-LINK RECEIVERS

The LVDS based FPD-Link Receivers inputs video data and control timing through 8 pairs of LVDS channels plus 2 pairs of LVDS clocks to provide 24-bit color or use only 6 pairs of LVDS channels plus 2 LVDS clocks to provide 18-bit color. The video data is converted to a parallel data stream and routed to the 8-6 bit translator.

#### SPREAD SPECTRUM SUPPORT

The FPD-Link receiver supports graphics controllers with Spread Spectrum interfaces for reducing EMI. The Spread Spectrum methods supported are Center and Down Spread. A maximum of 2% total is supported at a frequency modulation of 100kHz maximum.

#### 8-6 BIT TRANSLATOR

8-bit data is reduced to a 6-bit data path via a time multiplexed dithering technique or simple truncation of the LSBs. This function is enabled via the input control pins.

#### DATAPATH BLOCK AND RSDS TRANSMITTER

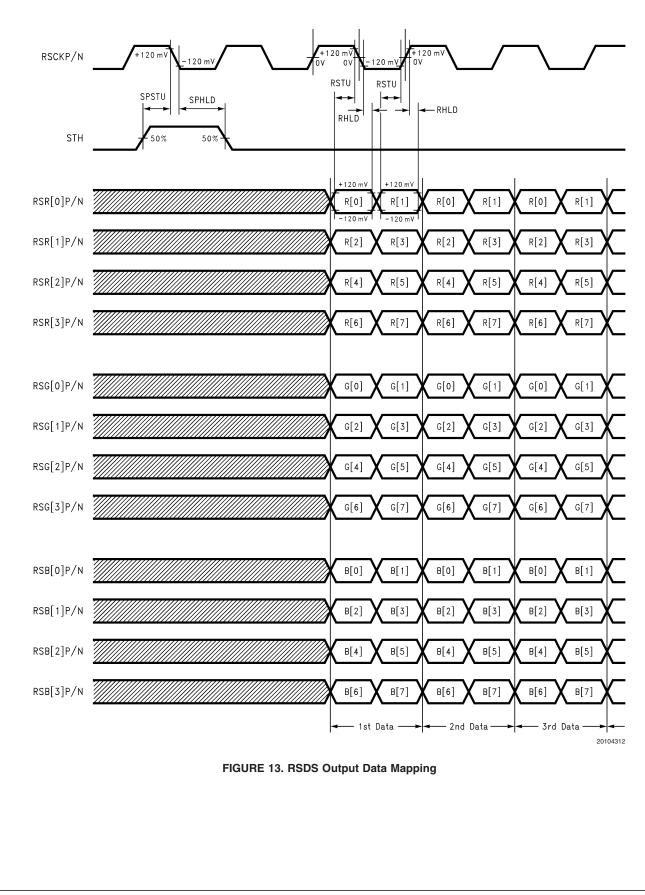

6(8)-bit video data (RGB) is input to the Datapath Block supports up to an 85 MHz dual pixel rate. The data is delayed to align the Column Driver Start Pulse (STH) with the Column Driver data. The dual data bus (RSR[3:0]P/N, RSG[3:0]P/N, RSB[3:0]P/N) outputs at a 170 MHz rate on 24 differential output channels. The clock is output on the (Front, Back) RSCKP/N differential pairs. The RSDS Column Drivers latch data on both positive and negative edges of the clock. The swap function provides flexible RSDS data output mappings for either Top or Bottom mount. The RSDS output setup/hold timings are also adjustable through the RSKEW[2:0] input pins.

#### TIMING CONTROL FUNCTION

The Timing Control function generates control to Column Drivers, Row Drivers, and power supply. The GPOs (General Purpose Outputs) provide for CD latch pulse, REV, and Row Driver control generation. The General Purpose Outputs allow the user to generate control anywhere within the frame data. Standard Row Driver interface or Custom Row Driver interfaces can be implemented with the GPOs (General Purpose Outputs).

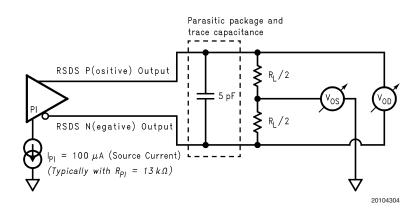

#### **RSDS OUTPUT VOLTAGE CONTROL**

The RSDS output voltage swing is controlled through an external load resistor connected to the RPI pin. The RSDS output signal levels can be adjusted to suit the particular application. This is dependent on overall LCD module design characteristics such as trace impedance, termination, etc. The RSDS output voltage is inversely related to the RPI value. Lower RPI values will increase the RSDS output voltage swing and consequently overall power consumption will also increase.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>DD</sub> )        | -0.3V to +4.0V                    |

|------------------------------------------|-----------------------------------|

| DC TTL Input Voltage (V <sub>IN</sub> )  | -0.3V to (V <sub>DD</sub> + 0.3V) |

| DC LVDS Input Voltage (V <sub>IN</sub> ) | -0.3V to (V <sub>DD</sub> + 0.3V) |

| DC Output Voltage (V <sub>OUT</sub> )    | -0.3V to (V <sub>DD</sub> + 0.3V) |

| Junction Temperature                     | +150°C                            |

| Storage Temperature Range                |                                   |

| (T <sub>STG</sub> )                      | -65°C to +150°C                   |

| Lead Temperature $(T_L)$                 |                                   |

| (Soldering 10 sec.)                      | 260°C                             |

#### ESD Rating:

| (C <sub>ZAP</sub> = 120 pF, | MM = 200V,  |

|-----------------------------|-------------|

| R <sub>ZAP</sub> = 1500W)   | HBM = 2000V |

# **Operating Conditions**

|                                   | Min | Max | Units     |  |

|-----------------------------------|-----|-----|-----------|--|

| Supply Voltage (V <sub>DD</sub> ) | 3.0 | 3.6 | V         |  |

| Operating Temp. Range $(T_A)$     | 0   | 70  | °C        |  |

| Supply Noise Voltage              |     | 100 | $mV_{PP}$ |  |

# **DC Electrical Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 3.0V$  to 3.6V,  $I_{PI} = 100 \ \mu A$  (Unless otherwise specified)

# **TTL DC Electrical Characteristics**

| Symbol          | Parameter                  | Conditions                                                                                                                                                                                                                                                                     | Min                  | Тур                                                 | Мах                                                 | Units |

|-----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------|-----------------------------------------------------|-------|

| V <sub>DD</sub> | Core Supply Voltage        |                                                                                                                                                                                                                                                                                | 3.0                  | 3.3                                                 | 3.6                                                 | V     |

| V <sub>IH</sub> | Minimum Input High Voltage |                                                                                                                                                                                                                                                                                | 2.0                  |                                                     |                                                     | V     |

| V <sub>IL</sub> | Maximum Input Low Voltage  |                                                                                                                                                                                                                                                                                |                      |                                                     | 0.8                                                 | V     |

| V <sub>OH</sub> | Output High Voltage        | I <sub>OH</sub> = -8mA                                                                                                                                                                                                                                                         | V <sub>DD</sub> -0.6 |                                                     |                                                     | V     |

| V <sub>OL</sub> | Output Low Voltage         | I <sub>OL</sub> = 8 mA                                                                                                                                                                                                                                                         |                      |                                                     | 0.4                                                 | V     |

| I <sub>IN</sub> | Input Current              | $V_{IN} = V_{DD}, \text{ GND}$                                                                                                                                                                                                                                                 |                      |                                                     | ±10                                                 | μA    |

| I <sub>PU</sub> | Pull-Up Current            | $V_{DD} = 3.3V, V_{IN} = V_{DD}$                                                                                                                                                                                                                                               |                      |                                                     | -50                                                 | μA    |

| I <sub>PD</sub> | Pull-Down Current          | $V_{DD} = 3.3V, V_{IN} = GND$                                                                                                                                                                                                                                                  |                      |                                                     | +50                                                 | μA    |

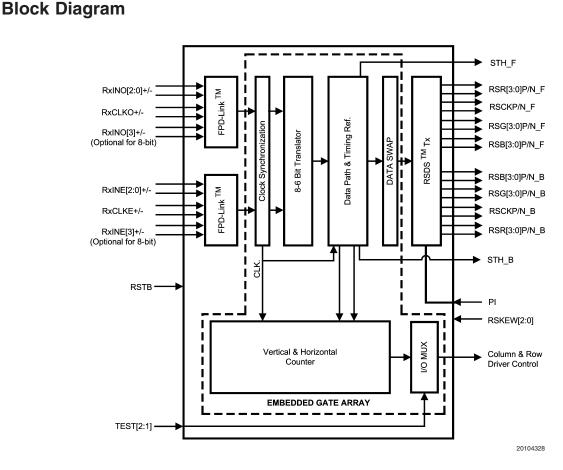

| I <sub>DD</sub> | Average Supply Current     | $C_{L(TTL)} = 15 \text{ pF},$<br>$R_{L(RSDS)} = 100\Omega \text{ and}$<br>$C_{L(RSDS)} = 5 \text{ pF}$<br>(jig & test fixture capacitance),<br>$I_{PI} = 100 \mu A$<br>(Typically PI pin connected to<br>13 k $\Omega$ to ground), See <i>Figure 3</i><br>for input conditions |                      | 170<br>(CLK = 65<br>MHz,<br>V <sub>DD</sub> = 3.3V) | 250<br>(CLK = 85<br>MHz,<br>V <sub>DD</sub> = 3.6V) | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

### **DC Electrical Characteristics**

$T_{A}$  = 0°C to 70°C,  $V_{DD}$  = 3.0V to 3.6V,  $I_{PI}$  = 100  $\mu A$  (Unless otherwise specified) (Continued)

#### FPD-Link (LVDS) Receiver Input Characteristics Symbol Parameter Conditions Min Max Units Тур LVDS RECEIVER DC SPECIFICATIONS Note: LVDS Receiver DC parameters are measured under static and steady state conditions which may not reflect the actual performance in the end application. Differential Input High Threshold $V_{\text{TH}_{LVDS}}$ +100mV Voltage $V_{CM} = 1.2V$ Differential Input Low Threshold V<sub>TLIVDS</sub> -100 mV Voltage $I_{\rm IN}$ Input Current $V_{IN} = 2.05V, V_{DD} =$ ±10 μA 3.6V $V_{IN} = 0.55V, V_{DD} =$ ±10 μA 3.6V $V_{DD} = 3.0 - 3.6V$ V $V_{IN}$ Input Voltage Range (Single-ended) 0.55 2.00 $|V_{ID}|$ **Differential Input Voltage** 0.100 0.600 V Common Mode Voltage Offset ٧ $V_{\rm CM}$ $V_{DD} = 3.0 - 3.6V$ $0.55 + |V_{ID}|/2$ $2.05 - |V_{ID}|/2$ $|V_{\rm ID}| = 100 \, {\rm mV}$ 2.05V $V_{CM} = 2.00V$ 1.95V $|V_{|D}| = 600 \, \text{mV}$ = 1.75VV<sub>см</sub> 1.45V $|V_{1D}| = 350 \, \text{mV}$ = 1.25 mV 1.15V .075V = 850 mV $|V_{|D}| = 600 \text{ mV}$ 650 m V $V_{CM} = 600 \text{ mV}$ $|V_{\text{ID}}| = 100 \text{ mV}$ GND 0.55V $V_{CM} = (1.25V); |V_{ID}| = 350mV$ Typical Application $V_{CM} = (850 \text{ mV to } 1.75\text{V}); |V_{ID}| = 600 \text{ mV}$ $V_{CM}$ range with Maximum $|V_{ID}|$ $|V_{ID}|$ and $V_{CM}$ Allowable Operating Range 20104303 FIGURE 4. FPD-Link Receiver $V_{\text{ID}}$ and $V_{\text{CM}}$ Definitions

FPD87392BXB

# **DC Electrical Characteristics**

$T_{A}$  = 0°C to 70°C,  $V_{DD}$  = 3.0V to 3.6V,  $I_{PI}$  = 100  $\mu A$  (Unless otherwise specified) (Continued)

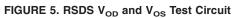

### **RSDS Output**

| Symbol  | Parameter                   | Conditions        | Min | Тур  | Max | Units |

|---------|-----------------------------|-------------------|-----|------|-----|-------|

| VODRSDS | Differential Output Voltage | $R_L = 100\Omega$ |     | ±200 |     | mV    |

| VOSRSDS | Offset Voltage              |                   | 1.1 | 1.3  | 1.5 | V     |

FIGURE 6. RSDS Output Waveforms: Single Ended vs Differential

# **AC Electrical Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 3.0V$  to 3.6V,  $I_{PI} = 100 \ \mu A$  (Unless otherwise specified)

#### LVDS Data Input

| Symbol | Parameter                                      | Conditions                              | Min | Max | Units |

|--------|------------------------------------------------|-----------------------------------------|-----|-----|-------|

| RPLLS  | FPD-Link Receiver Phase Lock Loop Wake-up Time |                                         |     | 10  | ms    |

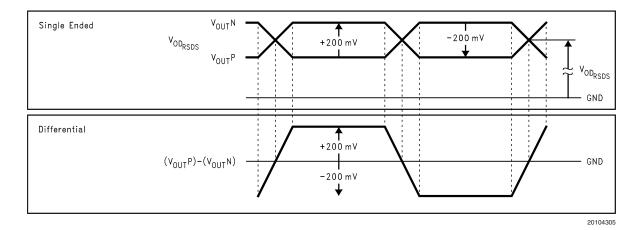

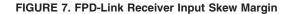

| RSKM   | RxIN Skew Margin (Note 2) and (Figure 7)       | V <sub>DD</sub> = 3.3V,<br>CLK = 85 MHz | 240 |     | ps    |

Note 2: Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin takes into account transmitter pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window: RSPOS). This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type and length of cable), and source clock (FPD-Link Transmitter TxCLK IN) jitter. The specified RSKM minimum assumes a TPPOS max of 200 ps.

#### RSKM = cable skew (type, length) + source clock jitter (cycle to cycle) + remaining margin for data sampling (20)

This parameter is guaranteed by design. The limits are based on statistical analysis of the device performance over PVT (Process, Voltage, Temperature) range.

#### Definitions:

RSKM

SW

SW: Setup and Hold Time (Internal data sampling window)

RSKM: Cable Skew (type, length) + Source Clock Jitter (cycle to cycle) + Remaining margin for data sampling (≥ 0) Cable Skew: Typically 10 ps - 40 ps per foot.

FIGURE 8. Ideal Strobe Position for LVDS Input

### **AC Electrical Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 3.0V$  to 3.6V,  $I_{PI} = 100 \ \mu A$  (Unless otherwise specified) (Continued)

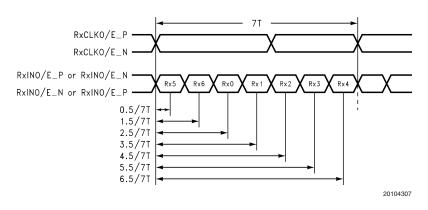

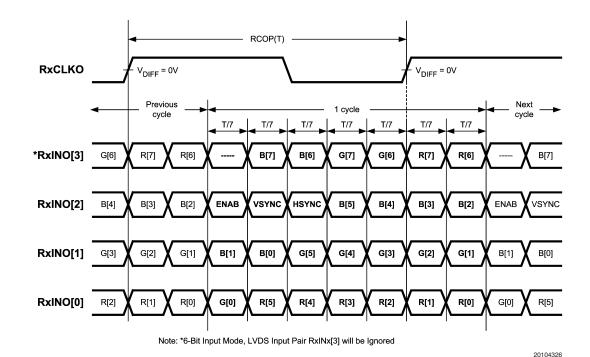

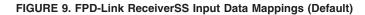

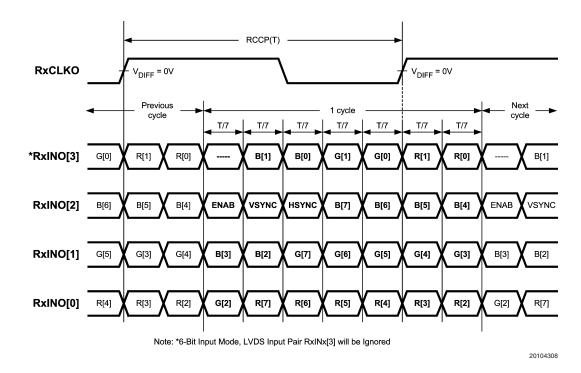

FIGURE 10. FPD-Link Receiver NS Input Data Mappings

# **AC Electrical Characteristics**

$T_{A}$  = 0°C to 70°C,  $V_{DD}$  = 3.0V to 3.6V,  $I_{PI}$  = 100  $\mu A$  (Unless otherwise specified) (Continued)

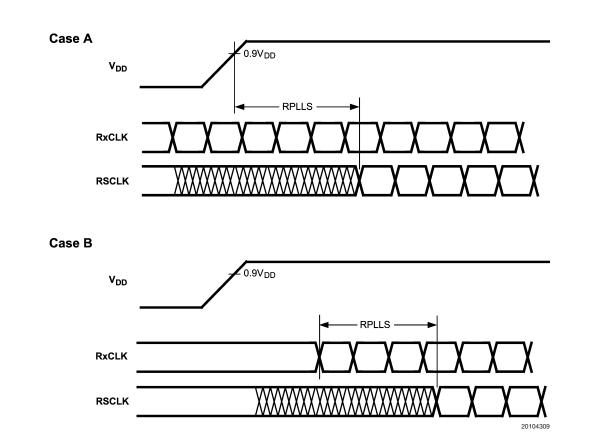

FIGURE 11. FPD-Link Receiver Phase Lock Loop Wake-up Time

# **AC Electrical Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 3.0V$  to 3.6V,  $I_{PI} = 100 \ \mu A$  (Unless otherwise specified) (Continued)

#### **Output Timing**

| Symbol | Parameter                                               | Conditions                                                                                                                                                                   | Min | Тур  | Мах | Units |

|--------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| RCHP   | RSDS Clock (RSCK) High Period                           | $R_T$ = 100Ω, $I_{PI}$ = 100 μA,<br>CLK= 85 MHz                                                                                                                              |     | 5.7  |     | ns    |

| RCLP   | RSDS Clock (RSCK) Low Period                            | $R_{T} = 100\Omega$ , $I_{PI} = 100 	mu{A}$ ,<br>CLK = 85 MHz                                                                                                                |     | 5.8  |     | ns    |

| SPSTU  | STH Rising to RSCK Falling                              | $R_{T} = 100\Omega$ , $I_{PI} = 100 	mu{A}$ ,<br>CLK = 85 MHz                                                                                                                | 3.0 |      |     | ns    |

| SPHLD  | STH Falling to RSCK Falling                             | R <sub>T</sub> = 100Ω, I <sub>PI</sub> = 100 μA,<br>CLK = 85 MHz                                                                                                             | 3.0 |      |     | ns    |

| RSTU   | RS(R, G, B) Setup to Falling or<br>Rising Edge of RSCK  | $\begin{split} R_{T} &= 100\Omega, \ C_{L(RSDS)} = 5 \ \text{pF}, \\ I_{\text{PI}} &= 100 \ \mu\text{A}, \\ CLK &= 85 \ \text{MHz}, \ \text{RSDS}[2:0] = ``100" \end{split}$ |     | 3.28 |     | ns    |

| RHLD   | RS(R, G, B) Hold from Falling or<br>Rising Edge of RSCK | $\begin{split} R_{T} &= 100\Omega, \ C_{L(RSDS)} = 5 \ pF, \\ I_{PI} &= 100 \ \mu\text{A}, \ CLK = 85 \ MHz, \\ RSDS[2:0] &= ``100'' \end{split}$                            |     | 1.87 |     | ns    |

# **RSDS Setup and Hold Time with Data Skew Control Values - Reference Only**

$(RxCLKP/N = 85 \text{ MHz}; V_{DD} = 3.0 \text{ to } 3.6\text{V}, R_T = 100\Omega; I_{PI} = 100 \ \mu\text{A}; \text{Duty Clock} = 50\%/50\%, \pm 5\%; 25^{\circ}\text{C})$ Note: Typical values on this table are measured under Static and Steady state conditions which may not be reflective of its performance in the end application.

| DeDela-01 | S   | Setup Time (RSTU) |     |     | Hold Time (RHLD) |     |       |  |

|-----------|-----|-------------------|-----|-----|------------------|-----|-------|--|

| RSDS[2:0] | Min | Тур               | Мах | Min | Тур              | Max | Units |  |

| 000       |     | 1.26              |     |     | 3.91             |     |       |  |

| 001       |     | 1.75              |     |     | 3.41             |     |       |  |

| 010       |     | 2.30              |     |     | 2.90             |     |       |  |

| 011       |     | 2.77              |     |     | 2.41             |     |       |  |

| 100       |     | 3.28              |     |     | 1.87             |     | ns    |  |

| 101       |     | 3.79              |     |     | 1.37             |     |       |  |

| 110       |     | 4.27              |     |     | 0.89             |     |       |  |

| 111       |     | 4.77              |     |     | 0.76             |     |       |  |

### **AC Electrical Characteristics**

$T_{A}$  = 0°C to 70°C,  $V_{DD}$  = 3.0V to 3.6V,  $I_{PI}$  = 100  $\mu A$  (Unless otherwise specified) (Continued)

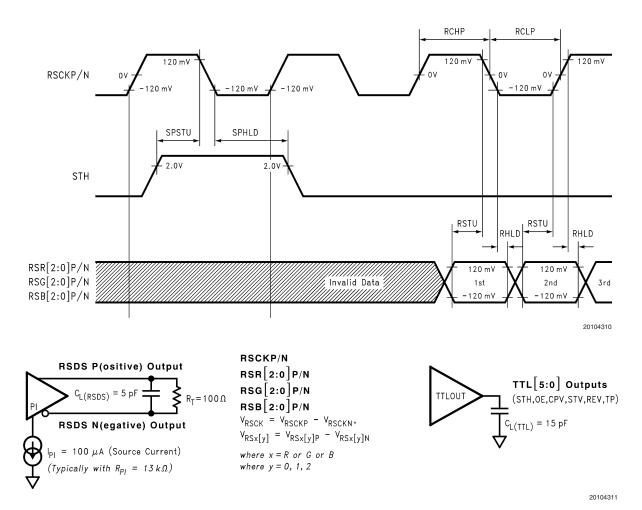

FIGURE 12. RSDS and TTL (CMOS) Output Timing Diagram

### **AC Electrical Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 3.0V$  to 3.6V,  $I_{PI} = 100 \ \mu A$  (Unless otherwise specified) (Continued)

# **AC Electrical Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 3.0V$  to 3.6V,  $I_{PI} = 100 \ \mu A$  (Unless otherwise specified) (Continued)

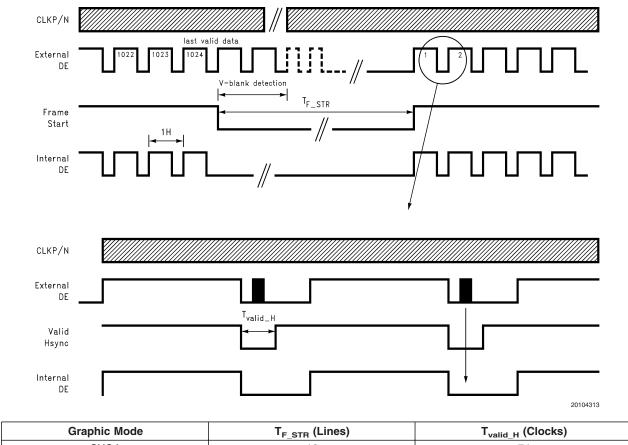

#### Failure Detect (B/O pin "FDE" = High)

This function is valid in DE mode and FDE pin set to "High". Invalid external DE pulse does not affect the internal operation during failure zone.

| Graphic Mode | T <sub>F_STR</sub> (Lines) | T <sub>valid_H</sub> (Clocks) |

|--------------|----------------------------|-------------------------------|

| SXGA         | 12                         | 74                            |

| SXGA+        | 12                         | 74                            |

| UXGA         | 12                         | 101                           |

Note: T<sub>F\_STR</sub> (Frame Start Time) and T<sub>valid\_H</sub> (Valid H Time) is estimated numbers. These values may not work properly for the specific application and needs optimization procedure on the actual system.

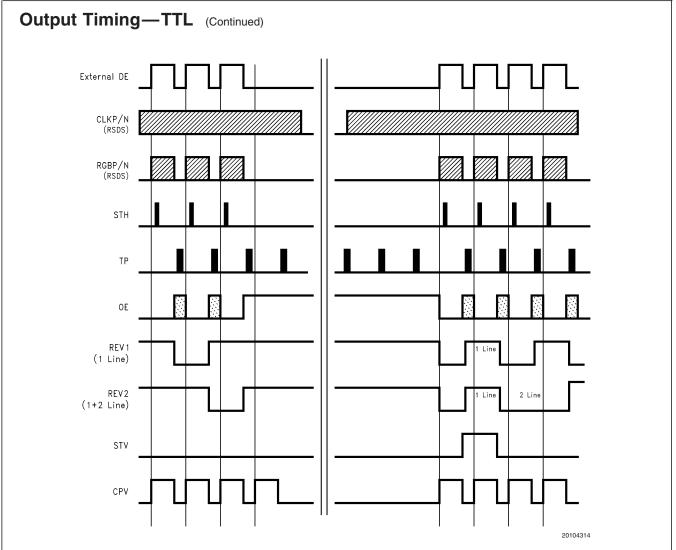

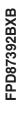

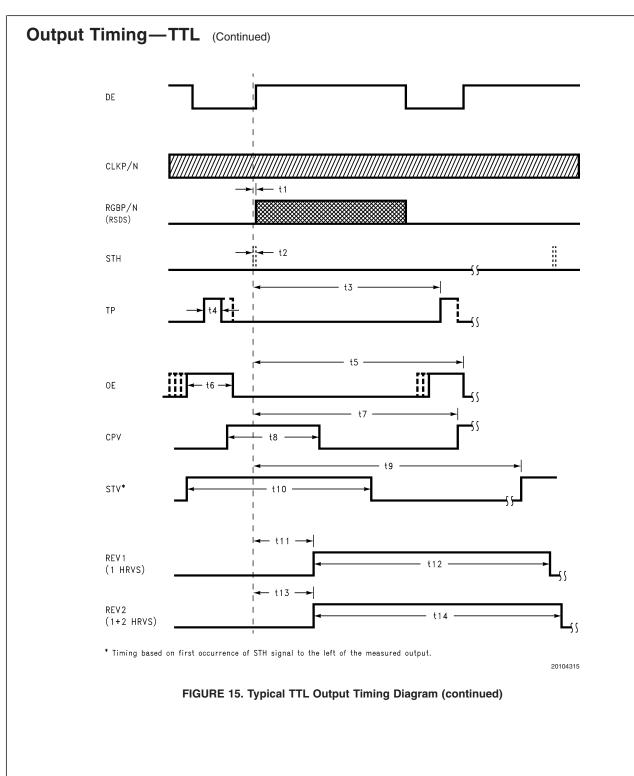

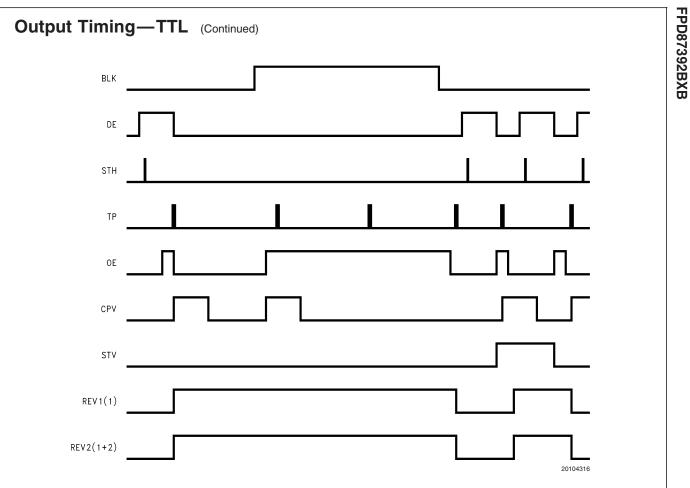

# Output Timing—TTL

| Parameter  | Comments                               | SXGA                 | SXGA+                | UXGA                 | Remarks/ |

|------------|----------------------------------------|----------------------|----------------------|----------------------|----------|

| Faranieler | (TPW, OE2, OE1 : 3'b000)               | @ 54 MHz             | @ 54 MHz             | @ 81 MHz             | Unit     |

| t1         | STH Rising to Active Data              | 2                    | 2                    | 2                    | CLKP/N   |

| t2         | High Duration of STH                   | 1                    | 1                    | 1                    | CLKP/N   |

| t3         | STH Rising to TP Rising                | 660                  | 720                  | 820                  | CLKP/N   |

| t4         | High Duration of TP                    | 54                   | 54                   | 81                   | CLKP/N   |

| t5         | STH Rising to OE Falling               | 687                  | 747                  | 861                  | CLKP/N   |

| t6         | High Duration of OE                    | 189                  | 189                  | 284                  | CLKP/N   |

| t7         | STH Rising to CPV                      | 660                  | 720                  | 820                  | CLKP/N   |

| t8         | High Duration of CPV                   | 422                  | 422                  | 540                  | CLKP/N   |

| t9         | STH Rising to STV                      | 238                  | 298                  | 280                  | CLKP/N   |

| t10        | High Duration of STV                   | 1                    | 1                    | 1                    | Line     |

|            |                                        | (844)                | (844)                | (1080)               | (CLKP/N) |

| t11        | STH Rising to REV (1 LINE)             | 645                  | 705                  | 805                  | CLKP/N   |

| t12        | High/Low Duration of REV (1 LINE)      | 1                    | 1                    | 1                    | Line     |

|            |                                        | (844)                | (844)                | (1080)               | (CLKP/N) |

| t13        | STH Rising to REV2 (1 + 2 LINE)        | 645                  | 705                  | 805                  | CLKP/N   |

| t14        | High/Low Duration of REV2 (1 + 2 LINE) | 1 (the first line)/2 | 1 (the first line)/2 | 1 (the first line)/2 | Line     |

|            |                                        | (844/1688)           | (844/1688)           | (1080/2160)          | (CLKP/N) |

Line = Hsync Cycle

# **TP/OE Duty Control Configuration**

| Resolution  | TPW | OEW2 | OEW1 | ТР                                           | ΟE<br>(µs) | @ 54 MHz<br>(CLK) | @ 81 MHz<br>(CLK) |

|-------------|-----|------|------|----------------------------------------------|------------|-------------------|-------------------|

| SXGA, SXGA+ | 0   | 0    | 0    | 1.0                                          | 3.5        | 189               | 284               |

|             | 0   | 0    | 1    | 1.0 μs<br>54 CLK @ 54 MHz<br>27 CLK @ 81 MHz | 3.0        | 162               | 243               |

|             | 0   | 1    | 0    |                                              |            | 2.5               | 135               |

| @ 54 MHz    | 0   | 1    | 1    |                                              | 2.0        | 108               | 162               |

| UXGA        | 1   | 0    | 0    | 0.5                                          | 3.5        | 189               | 284               |

| @ 81 MHz    | 1   | 0    | 1    | 0.5 μs<br>27 CLK @ 54 MHz                    | 3.0        | 162               | 243               |

|             | 1   | 1    | 0    | 41 CLK @ 54 MHz                              | 2.5        | 135               | 203               |

|             | 1   | 1    | 1    |                                              | 2.0        | 108               | 162               |

# Output Timing—TTL (Continued) 8-BIT RSDS Output Data Mapping

| <b>D</b> ' |           | DMAP   | 2, DMAP1 |         |         | DMAP2, DMAP1 |       |        |         |

|------------|-----------|--------|----------|---------|---------|--------------|-------|--------|---------|

| Pin<br>No. | 00        | 01     | 10       | 11      | Pin No. | Pin No. 00   |       | 10     | 11      |

| NO.        | Top Mount |        | Botto    | m Mount | ]       | Тор Г        | Nount | Botto  | m Mount |

| 47         | R3P_F     | R0N_F  | B0N_B    | B3P_B   | 78      | R3P_B        | R0N_B | B0N_F  | B3P_F   |

| 48         | R3N_F     | R0P_F  | B0P_B    | B3N_B   | 79      | R3N_B        | R0P_B | B0P_F  | B3N_F   |

| 49         | R2P_F     | R1N_F  | B1N_B    | B2P_B   | 80      | R2P_B        | R1N_B | B1N_F  | B2P_F   |

| 50         | R2N_F     | R1P_F  | B1P_B    | B2N_B   | 81      | R2N_B        | R1P_B | B1P_F  | B2N_F   |

| 51         | R1P_F     | R2N_F  | B2N_B    | B1P_B   | 82      | R1P_B        | R2N_B | B2N_F  | B1P_F   |

| 52         | R1N_F     | R2P_F  | B2P_B    | B1N_B   | 83      | R1N_B        | R2P_B | B2P_F  | B1N_F   |

| 53         | R0P_F     | R3N_F  | B3N_B    | B0P_B   | 84      | R0P_B        | R3N_B | B3N_F  | B0P_F   |

| 54         | R0N_F     | R3P_F  | B3P_B    | B0N_B   | 85      | R0N_B        | R3P_B | B3P_F  | B0N_F   |

| 56         | G3P_F     | G0N_F  | G0N_B    | G3P_B   | 87      | G3P_B        | G0N_B | G0N_F  | G3P_F   |

| 57         | G3N_F     | G0P_F  | G0P_B    | G3N_B   | 88      | G3N_B        | G0P_B | G0P_F  | G3N_F   |

| 58         | G2P_F     | G1N_F  | G1N_B    | G2P_B   | 89      | G2P_B        | G1N_B | G1N_F  | G2P_F   |

| 59         | G2N_F     | G1P_F  | G1P_B    | G2N_B   | 90      | G2N_B        | G1P_B | G1P_F  | G2N_F   |

| 60         | G1P_F     | G2N_F  | G2N_B    | G1P_B   | 91      | G1P_B        | G2N_B | G2N_F  | G1P_F   |

| 61         | G1N_F     | G2P_F  | G2P_B    | G1N_B   | 92      | G1N_B        | G2P_B | G2P_F  | G1N_F   |

| 62         | G0P_F     | G3N_F  | G3N_B    | G0P_B   | 93      | G0P_B        | G3N_B | G3N_F  | G0P_F   |

| 63         | G0N_F     | G3P_F  | G3P_B    | G0N_B   | 94      | G0N_B        | G3P_B | G3P_F  | G0N_F   |

| 65         | CLKP_F    |        | CLKP_B   |         | 95      | CLKP_B       |       | CLKP_F |         |

| 66         | CLKN_F    | CLKN_F |          |         | 96      | CLKN_B       |       | CLKN_F |         |

| 67         | B3P_F     | B0N_F  | R0N_B    | R3P_B   | 98      | B3P_B        | B0N_B | R0N_F  | R3P_F   |

| 68         | B3N_F     | B0P_F  | R0P_B    | R3N_B   | 99      | B3N_B        | B0P_B | R0P_F  | R3N_F   |

| 69         | B2P_F     | B1N_F  | R1N_B    | R2P_B   | 100     | B2P_B        | B1N_B | R1N_F  | R2P_F   |

| 70         | B2N_F     | B1P_F  | R1P_B    | R2N_B   | 101     | B2N_B        | B1P_B | R1P_F  | R2N_F   |

| 71         | B1P_F     | B2N_F  | R2N_B    | R1P_B   | 102     | B1P_B        | B2N_B | R2N_F  | R1P_F   |

| 72         | B1N_F     | B2P_F  | R2P_B    | R1N_B   | 103     | B1N_B        | B2P_B | R2P_F  | R1N_F   |

| 73         | B0P_F     | B3N_F  | R3N_B    | R0P_B   | 104     | B0P_B        | B3N_B | R3N_F  | R0P_F   |

| 74         | B0N_F     | B3P_F  | R3P_B    | R0N_B   | 105     | B0N_B        | B3P_B | R3P_F  | R0N_F   |

| 107        | ST        | H_F    | S        | ΓH_B    | 108     | STI          | H_B   | S      | TH_F    |

# Output Timing—TTL (Continued) 6-BIT RSDS Output Data Mapping

|         |           | DMAI  | DMAP2, DMAP1 |              |            | DMAP2, DMAP1 |       |        |          |  |

|---------|-----------|-------|--------------|--------------|------------|--------------|-------|--------|----------|--|

| Pin No. | 00        | 01    | 10           | 11           | Pin<br>No. | 00           | 01    | 10     | 11       |  |

|         | Top Mount |       | Botto        | Bottom Mount |            | Тор          | Mount | Botto  | om Mount |  |

| 47      | HI-Z      | R0N_F | B0N_B        | HI-Z         | 78         | HI-Z         | R0N_B | B0N_F  | HI-Z     |  |

| 48      | HI-Z      | R0P_F | B0P_B        | HI-Z         | 79         | HI-Z         | R0P_B | B0P_F  | HI-Z     |  |

| 49      | R2P_F     | R1N_F | B1N_B        | B2P_B        | 80         | R2P_B        | R1N_B | B1N_F  | B2P_F    |  |

| 50      | R2N_F     | R1P_F | B1P_B        | B2N_B        | 81         | R2N_B        | R1P_B | B1P_F  | B2N_F    |  |

| 51      | R1P_F     | R2N_F | B2N_B        | B1P_B        | 82         | R1P_B        | R2N_B | B2N_F  | B1P_F    |  |

| 52      | R1N_F     | R2P_F | B2P_B        | B1N_B        | 83         | R1N_B        | R2P_B | B2P_F  | B1N_F    |  |

| 53      | R0P_F     | HI-Z  | HI-Z         | B0P_B        | 84         | R0P_B        | HI-Z  | HI-Z   | B0P_F    |  |

| 54      | R0N_F     | HI-Z  | HI-Z         | B0N_B        | 85         | R0N_B        | HI-Z  | HI-Z   | B0N_F    |  |

| 56      | HI-Z      | G0N_F | G0N_B        | HI-Z         | 87         | HI-Z         | G0N_B | G0N_F  | HI-Z     |  |

| 57      | HI-Z      | G0P_F | G0P_B        | HI-Z         | 88         | HI-Z         | G0P_B | G0P_F  | HI-Z     |  |

| 58      | G2P_F     | G1N_F | G1N_B        | G2P_B        | 89         | G2P_B        | G1N_B | G1N_F  | G2P_F    |  |

| 59      | G2N_F     | G1P_F | G1P_B        | G2N_B        | 90         | G2N_B        | G1P_B | G1P_F  | G2N_F    |  |

| 60      | G1P_F     | G2N_F | G2N_B        | G1P_B        | 91         | G1P_B        | G2N_B | G2N_F  | G1P_F    |  |

| 61      | G1N_F     | G2P_F | G2P_B        | G1N_B        | 92         | G1N_B        | G2P_B | G2P_F  | G1N_F    |  |

| 62      | G0P_F     | HI-Z  | HI-Z         | G0P_B        | 93         | G0P_B        | HI-Z  | HI-Z   | G0P_F    |  |

| 63      | G0N_F     | HI-Z  | HI-Z         | G0N_B        | 94         | G0N_B        | HI-Z  | HI-Z   | G0N_F    |  |

| 65      | CLKP_F    |       | CLKP_B       |              | 95         | CLKP_B (     |       | CLKP_F | CLKP_F   |  |

| 66      | CLKN_F    |       | CLKN_B       |              | 96         | CLKN_B       |       | CLKN_F |          |  |

| 67      | HI-Z      | B0N_F | R0N_B        | HI-Z         | 98         | HI-Z         | B0N_B | R0N_F  | HI-Z     |  |

| 68      | HI-Z      | B0P_F | R0P_B        | HI-Z         | 99         | HI-Z         | B0P_B | R0P_F  | HI-Z     |  |

| 69      | B2P_F     | B1N_F | R1N_B        | R2P_B        | 100        | B2P_B        | B1N_B | R1N_F  | R2P_F    |  |

| 70      | B2N_F     | B1P_F | R1P_B        | R2N_B        | 101        | B2N_B        | B1P_B | R1P_F  | R2N_F    |  |

| 71      | B1P_F     | B2N_F | R2N_B        | R1P_B        | 102        | B1P_B        | B2N_B | R2N_F  | R1P_F    |  |

| 72      | B1N_F     | B2P_F | R2P_B        | R1N_B        | 103        | B1N_B        | B2P_B | R2P_F  | R1N_F    |  |

| 73      | B0P_F     | HI-Z  | HI-Z         | R0P_B        | 104        | B0P_B        | HI-Z  | HI-Z   | R0P_F    |  |

| 74      | B0N_F     | HI-Z  | HI-Z         | R0N_B        | 105        | B0N_B        | HI-Z  | HI-Z   | R0N_F    |  |

| 107     | S         | TH_F  | S            | TH_B         | 108        | S            | TH_B  | S      | STH_F    |  |

Note: Note: For 6-bit output mode, RSDS pair 3P/Ns will be in HI-Z mode.

# LVDS Input and RSDS Output Data

| RxMap | BIT_CFG2 | BIT_CFG1 | Input Data | Output Data | Functional Description            |

|-------|----------|----------|------------|-------------|-----------------------------------|

| 0     | 0        | 0        | 8-bit      | 8-bit       | Data is unchanged (NS mapping)    |

| 0     | 0        | 1        | 8-bit      | 6-bit       | 2 MSBs are HI-Z, FRC Enabled (NS) |

| 0     | 1        | 0        | 6-bit      | 8-bit       | 2 LSBs are zero (NS)              |

| 0     | 1        | 1        | 6-bit      | 6-bit       | 2 MSBs are HI-Z (NS)              |

| 1     | 0        | 0        | 8-bit      | 8-bit       | Data is unchanged (SS mapping)    |

| 1     | 0        | 1        | 8-bit      | 6-bit       | 2 MSBs are HI-Z, FRC Enabled (SS) |

| 1     | 1        | 0        | 6-bit      | 8-bit       | 2 LSBs are zero (SS)              |

| 1     | 1        | 1        | 6-bit      | 6-bit       | 2 MSBs are HI-Z (SS)              |

FPD87392BXB

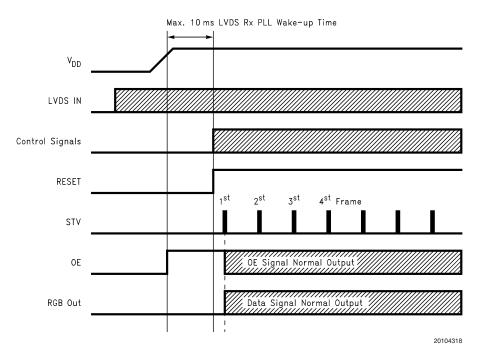

# **Input Signal Timing**

Sync only mode, no DE inputted, is supported when the SYNC pin (Bonding Option pin) is enable high. Whenever DE signal is inputted, it works as DE mode. In the DE mode, H-blank min is considered with Failure detection mode enabled. In the defaults mode, T<sub>valid\_H</sub> should be subtracted in the table below.

|                  |                         | Sync                                  | Mode (Bon | ding Option)                           | )    |         |                      | Node                | Number of                  | Number of             |

|------------------|-------------------------|---------------------------------------|-----------|----------------------------------------|------|---------|----------------------|---------------------|----------------------------|-----------------------|

| Graphia          | H-Timing (clocks)       |                                       |           | V-Timing (lines)                       |      |         | H-Timing<br>(clocks) | V-Timing<br>(lines) | Total                      | Total Pixel<br>Clocks |

| Graphic<br>Mode  | From<br>Sync<br>to Data | Total H-Timing                        |           | From<br>Sync Total V-Timing<br>to Data |      | H-Blank | H-Blank<br>Detection | Blank Lines in a    | in a<br>Horizontal<br>Line |                       |

|                  | Тур                     | Min                                   | Max       | Тур                                    | Min  | Мах     | Min                  | Min                 | Тур                        | Тур                   |

| SXGA             | 248                     | 1430                                  | 2047      | 38                                     | 1066 | 2047    | 150                  | 2                   | 1066                       | 1688                  |

| SXGA+            | 128                     | 1550                                  | 2047      | 12                                     | 1066 | 2047    | 150                  | 2                   | 1066                       | 1688                  |

| UXGA             | 304                     | 1804                                  | 4095      | 46                                     | 1250 | 2047    | 204                  | 2                   | 1250                       | 2160                  |

| H-Sy<br>va<br>da |                         | (VBP)                                 |           |                                        |      | ;       |                      |                     |                            | -                     |

| H-Sync (HSW)     |                         |                                       |           |                                        |      |         |                      |                     |                            |                       |

|                  | valid data              | · · · · · · · · · · · · · · · · · · · | From sync | to data<br>  <del></del>               |      | (WIDTH) |                      | > ∢                 | (HFP)<br>→                 | 20104317              |

FIGURE 17. Video Signal Format

# Supports VESA Standard in SYNC Mode (B/O SYNC Pin = High)

| WIDTH<br>HFP<br>HSW<br>HBP | 1280<br>48<br>112<br>248 | 1400<br>48<br>112            | 1600<br>64<br>192                          | clock<br>clock<br>clock                                  |

|----------------------------|--------------------------|------------------------------|--------------------------------------------|----------------------------------------------------------|

| HSW<br>HBP                 | 112                      | 112                          | 192                                        |                                                          |

| HBP                        |                          |                              |                                            | clock                                                    |

|                            | 248                      | 100                          |                                            |                                                          |

|                            | -                        | 128                          | 304                                        | clock                                                    |

| HEIGHT                     | 1024                     | 1050                         | 1200                                       | Line                                                     |

| VFP                        | 1                        | 1                            | 1                                          | Line                                                     |

| VSW                        | 3                        | 3                            | 3                                          | Line                                                     |

| VBP                        | 38                       | 12                           | 46                                         | Line                                                     |

|                            | •                        | •                            |                                            |                                                          |

|                            |                          |                              |                                            |                                                          |

|                            | VFP<br>VSW               | VFP      1        VSW      3 | VFP      1      1        VSW      3      3 | VFP      1      1      1        VSW      3      3      3 |

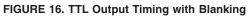

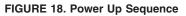

# Power Up Sequence (Defaults)

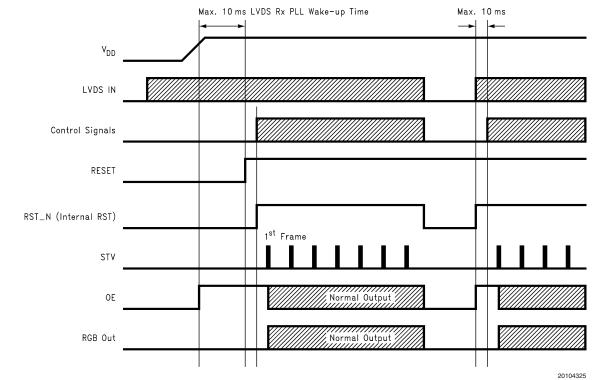

When Power is ON, the TCON start to operate and generate the control signals by inputted LVDS signals. LVDS Receiver will take maximum 10 ms for the PLL wake-up time. Whether LVDS signals exist before the power-on doesn't effect. When the Reset is reach to 2.0V, the R, G, B data and control signals are outputted sequentially and the sequence is just as following figure.

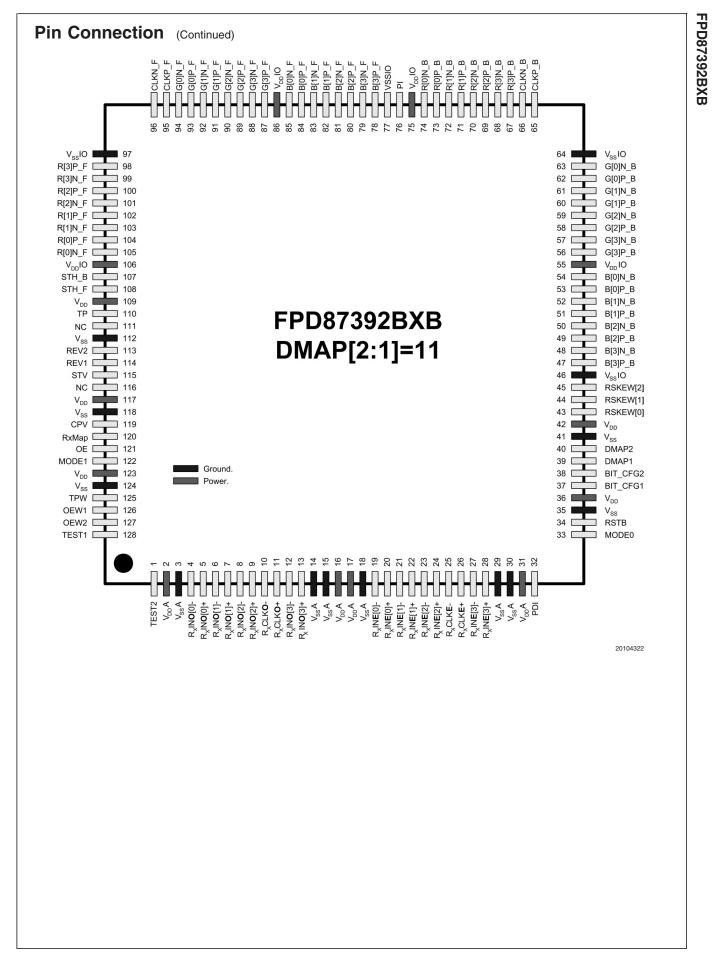

# Pin Description System Interface

| Symbol          | Pin No. | Туре  | Function                                |  |

|-----------------|---------|-------|-----------------------------------------|--|

| RxINO[0]P/N and | 4, 5    | LVDSI | FPD-Link Data Differential Pair 0 Input |  |

| RxINE[0]P/N     | 19, 20  |       |                                         |  |

| RxINO[1]P/N and | 6, 7    | LVDSI | FPD-Link Data Differential Pair 1 Input |  |

| RxINE[1]P/N     | 21, 22  |       |                                         |  |

| RxINO[2]P/N and | 8, 9    | LVDSI | FPD-Link Data Differential Pair 2 Input |  |

| RxINE[2]P/N     | 23, 24  |       |                                         |  |

| RxINO[3]P/N and | 12, 13  | LVDSI | FPD-Link Data Differential Pair 3 Input |  |

| RxINE[3]P/N     | 25, 26  |       |                                         |  |

| RxCLKOP/N and   | 10, 11  | LVDSI | FPD-Link Clock Differential Pair Input  |  |

| RxCLKEP/N       | 27, 28  |       |                                         |  |

# **RSDS** Interface

| Symbol      | Pin No.             | Туре                                                                | Function                                                                 |

|-------------|---------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------|

| B[3:0]P/N_B | 47–54               | RSO                                                                 | Blue Reduced Swing Differential Outputs to Back Column Drivers           |

| G[3:0]P/N_B | 56-63               | RSO                                                                 | Green Reduced Swing Differential Outputs to Back Column Drivers          |

| R[3:0]P/N_B | 67–74               | 4 RSO Red Reduced Swing Differential Outputs to Back Column Drivers |                                                                          |

| CLKP/N_B    | 65, 66              | RSO                                                                 | Clock Reduced Swing Differential Outputs to Back Column Drivers          |

| B[3:0]P/N_F | 78–85               | RSO                                                                 | Blue Reduced Swing Differential Outputs to Front Column Drivers          |

| G[3:0]P/N_F | 87–94               | RSO                                                                 | Green Reduced Swing Differential Outputs to Front Column Drivers         |

| R[3:0]P/N_F | 98–105              | RSO                                                                 | Red Reduced Swing Differential Outputs to Front Column Drivers           |

| CLKP/N_F    | CLKP/N_F 95, 96 RSO |                                                                     | Clock Reduced Swing Differential Outputs to Front Column Drivers         |

|             |                     | I                                                                   | External Resistor Input for RSDS Output (V <sub>OD</sub> ) Level Control |

|             |                     | I                                                                   | Output RSDS Data Skew Control (Default 3'b000)                           |

# **Column/Row Driver Control**

| Symbol     | Pin No. | Туре | Function                                               |

|------------|---------|------|--------------------------------------------------------|

| TP         | 110     | то   | Line Latch Signal Output to Column Drivers             |

| STH_B      | 107 TO  |      | Horizontal Start Signal Output to Back Column Drivers  |

| STH_F      | 108     | то   | Horizontal Start Signal Output to Front Column Drivers |

| REV1       | 114     | то   | Data Inversion Output to Column Driver (1 Line)        |

| REV2       | 113 TO  |      | Data Inversion Output to Column Driver (1 + 2 Line)    |

| STV        | 115 TO  |      | Row Driver Start Pulse                                 |

| CPV 119 TO |         | то   | Row Driver Shift Clock                                 |

| OE         | 121     | то   | Control TFT Gate Pulse Width to Row Drivers            |

# Pin Description (Continued) Control Input

| Symbol     | Pin No.  | Туре | Function                                              |

|------------|----------|------|-------------------------------------------------------|

| BIT_CFG1/2 | 37, 38   | I    | LVDS Input and RSDS Output Bit Selection              |

| MODE[1:0]  | 122, 33  | I    | Graphic Mode Selection                                |

|            |          |      | "00": SXGA, "01": SXGA+, "10": UXGA, "11": Don't Care |

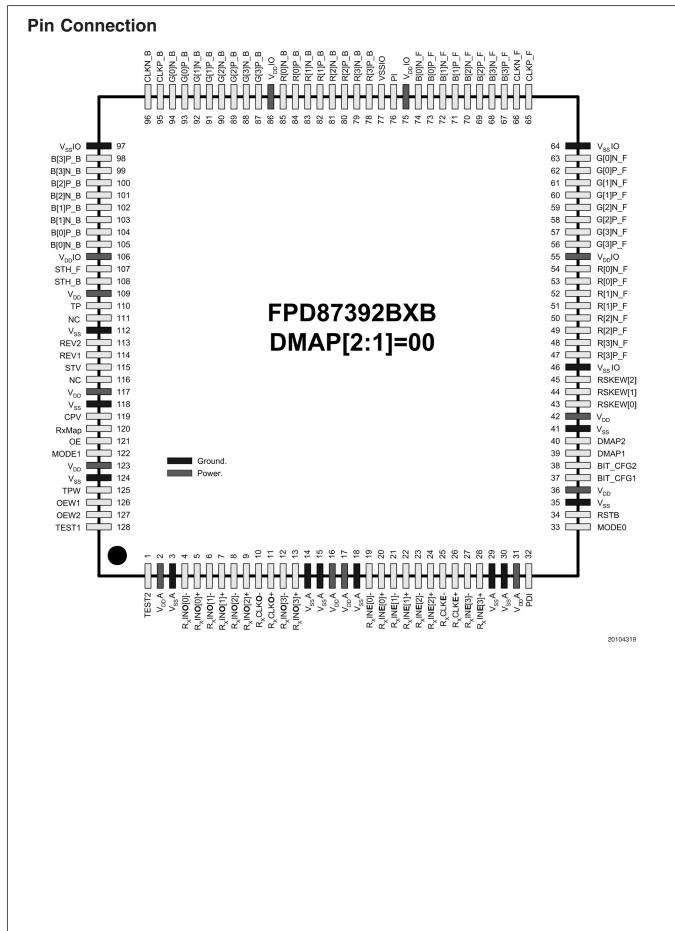

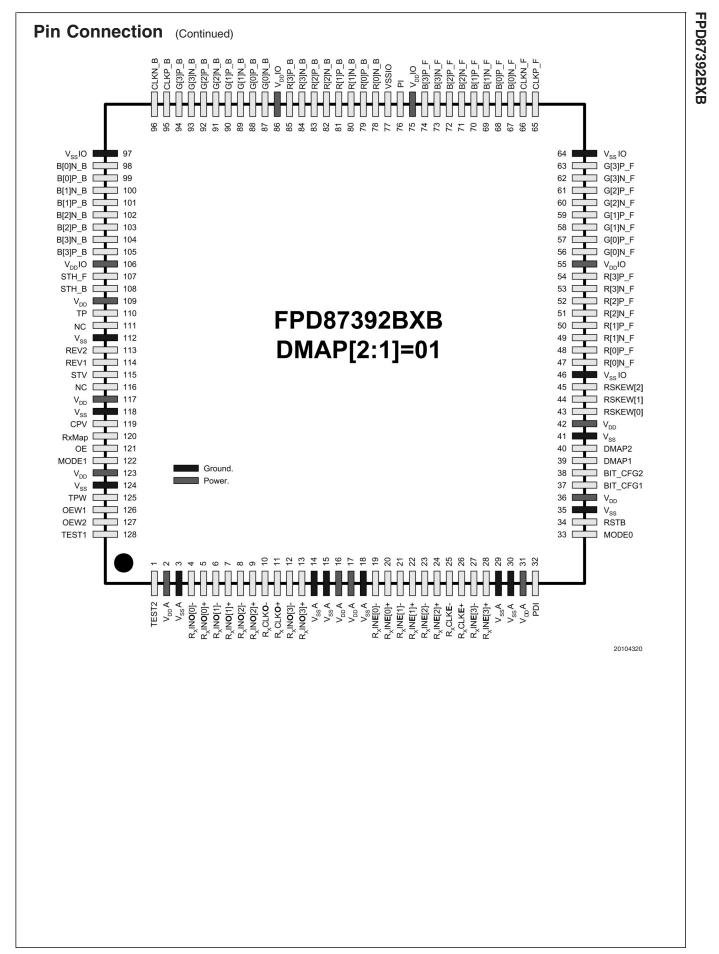

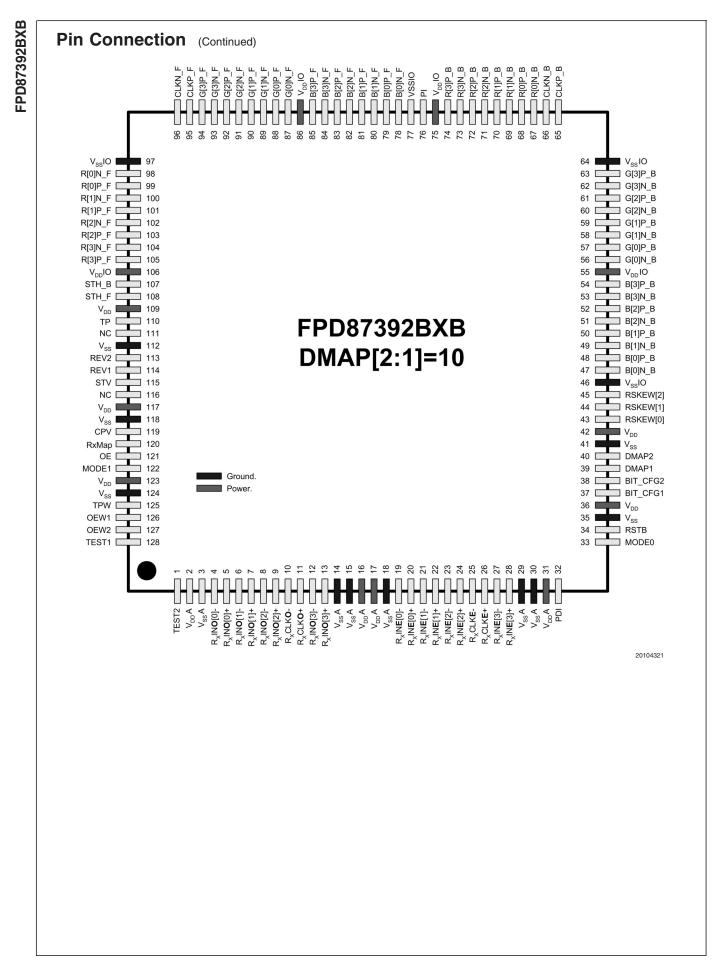

| DMAP1/2    | 39, 40   | I    | RSDS Output Data Mapping                              |

| TPW        | 125      | I    | TP Duty Control (Default Low)                         |

| OEW1/2     | 126, 127 | I    | OE Duty Control (Default 2'b00)                       |

| TEST1/2    | 128, 1   | I    | Test Mode                                             |

|            |          |      | Low: Normal Operation, High: Test Mode                |

| PDI        | 32       | I    | LVDS Power Down (Active Low)                          |

| RSTB       | 34       | I    | System Reset (Active Low)                             |

| RxMap      | 120      | I    | RxMap=1(SS Mapping); RxMap=0, NS Mapping              |

| NC         | 111, 116 |      | No Connect                                            |

# Power Supply

| Symbol            | Pin No.      | Туре | Function                                            |

|-------------------|--------------|------|-----------------------------------------------------|

| V <sub>DD</sub>   | 36, 42, 109, | Р    | Digital Power for Logic Core and LVDS Deserializer  |

|                   | 117, 123     |      |                                                     |

| V <sub>SS</sub>   | 35, 41, 112, | G    | Digital Ground for Logic Core and LVDS Deserializer |

|                   | 118, 124     |      |                                                     |

| V <sub>DDA</sub>  | 2, 16, 17,   | Р    | Power for LVDS PLL and Analog Bandgap               |

|                   | 31           |      |                                                     |

| V <sub>SSA</sub>  | 3, 14, 15,   | G    | Ground for LVDS PLL and Analog Bandgap              |

|                   | 18, 29, 30   |      |                                                     |

| V <sub>DDIO</sub> | 55, 75, 86,  | Р    | Digital I/O Power and RSDS Outputs                  |

|                   | 106          |      |                                                     |

| V <sub>SSIO</sub> | 46, 64, 77,  | G    | Digital I/O Ground and RSDS Outputs                 |

|                   | 97           |      |                                                     |

# Bonding Option (B/O)

| Symbol | Pin No. | Туре | Function                   |

|--------|---------|------|----------------------------|

| SYNC   | B/O     | PU   | SYNC Mode                  |

|        |         |      | High: Enable, Low: Disable |

| FRM    | B/O     | PU   | Free Run Mode              |

|        |         |      | High: Enable, Low: Disable |

| FDE    | B/O     | PU   | Failure Detection          |

|        |         |      | High: Enable, Low: Disable |

| POR    | B/O     |      | Power-On-Reset             |

|        |         |      | High: Enable, Low: Disable |

# **Pin Types**

| I     | -Input (3.3V TTL-Compatible)           | G  | -Ground    |

|-------|----------------------------------------|----|------------|

| то    | -TTL Output (3.3V TTL-Compatible)      | PU | -Pull-Up   |

| LVDSI | -Low Voltage Differential Signal Input | PD | -Pull-Down |

RSO -Reduced Swing Differential Output

P -Power

# Appendix 1. DE Mode Timing Details

#### DE Mode (Disabled SYNC Pin)

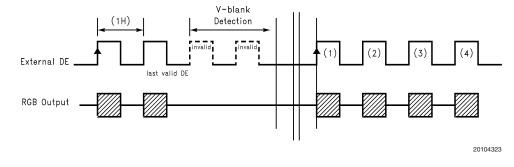

Always true whenever DE is exist as inputted signal. If V<sub>SYNC</sub>, H<sub>SYNC</sub> and DE are available, DE mode is superior and generate the control timing. "V-blank Detection" period is two cycles of the previous DE signals. After the V-blank detection period, "Counter" start to count whenever DE signal available followed on the rising edge.

Case 1: Disabled Failure Detection Mode

Case 2: Enabled Failure Detection Mode (SXGA). Please refer to the "Failure Detect" on page 10.

# Appendix 2. Free Run Mode Function (B/O Pin FRM "Low" to Disable)

Either input DE signal, ENA, on the DE mode or  $V_{SYNC}$  on the SYNC mode are lost more than 5 frames (here, "lost" means ENA or  $V_{SYNC}$  signal more than 5 frames without change), then the TCON will enter the Free Run Mode. In the Free Run Mode, the vertical and horizontal period will follow VESA 60 Hz standard and output data will be in the Low Level.

When TCON detects input signal back to normal ("normal" means ENA or V<sub>SYNC</sub> signal has to change from Low Level to High Level), then output control signals will return to the Normal Mode. In the next frame, output data will also return to Normal Mode.

# Appendix 3. Power-Up Sequence on "POR Enabled" Mode

When Bonding option pins, POR (Power-On-Reset), enable set to "High", TCON start running as POR mode. If the input LVDS clocks lost with any reasons during the normal operation, POR output signal (RST\_N) will be low until LVDS clock comeback again. The Reset counter start to count with LVDS clock resume then turn to normal operation mode before the 10 ms PLL Wake-Up time limits.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated