# VM65060 ANALOG PRML CHANNEL

970801

## PRELIMINARY

August, 1997

## **FEATURES**

- Register programmable user data rates from 46 to 140 Mbps

- Sampled data read channel with maximum likelihood Viterbi detection

- Programmable continuous-time filter with two independently-variable real zeros

- Programmable seven-tap transversal filter for PR4 equalization

- · Self-adapting option for FIR tap weights

- Programmable two-level write precompensation with 1.25% resolution

- · Direct Write/Read feature for equalizer optimization

- Analog/sampled AGC

- · Zero phase restart for fast acquisition

- · Servo area detectors for burst demodulation

- Fast timing control during acquisition by bypassing FIR filter

- Register programmable power management (<5 mW Power Down mode)</li>

- · 4 or 8-bit wide parallel data interface to disk controller

- Serial interface port for access to internal program storage registers to load and verify

- Single power supply (5V ±10%)

- · Small footprint 80-pin PQFP package

## DESCRIPTION

The VM65060 is a high performance BiCMOS read channel IC that provides all of the data processing needed to implement a Partial Response Maximum Likelihood (PRML) read channel for zoned recording MR hard disk drive systems with user data rates from 46 to 140 Mbps.

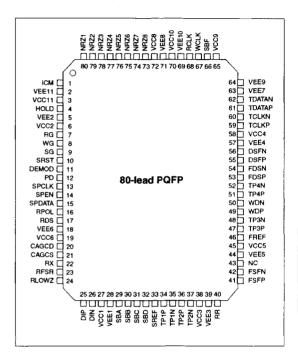

BiCMOS process technology along with advanced circuit design techniques result in high performance devices with low power consumption. The part requires a single +5V power supply and is available in a 80-Lead PQFP package.

Functional blocks include AGC, programmable continuous time filter, adaptive FIR filter, maximum likelihood Viterbi detector, frequency synthesizer, 2-level nonlinear write precomp and area detectors for servo bursts. Programmable functions such as data rate, filter cutoff/boost, FIR tap weights, adaption parameters, write precomp values, etc. are controlled by writing to the serial port registers. No external component changes are required to change zones.

### **CONNECTION DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage                            |                                  |

|-------------------------------------------------|----------------------------------|

| V <sub>CC</sub>                                 | 0.3V to +7V                      |

| Input Voltages                                  |                                  |

| Digital Input Voltage VIN                       | . $-0.3V$ to $(V_{CC} + 0.3)V$   |

| Analog Input Voltage VIN                        | 0.3V to (V <sub>CC</sub> + 0.3)V |

| Storage Temperature T <sub>stg</sub>            | 65°C to 150°C                    |

| Junction Temperature T <sub>J</sub>             |                                  |

| Thermal Impedance Characteristics, $\Theta_{J}$ | A:                               |

| 80-Lead PQFP                                    | 39°C/W                           |

#### **RECOMMENDED OPERATING CONDITIONS**

| Power Supply Voltage:               |               |

|-------------------------------------|---------------|

| V <sub>CC</sub>                     | <br>+5V ± 10% |

| Junction Temperature T <sub>J</sub> |               |

#### **BLOCK DIAGRAM DESCRIPTION**

#### **AUTOMATIC GAIN CONTROL:**

- Dual mode AGC, analog during acquisition, sampled during read data

- Separate AGC level storage pins for data and servo

- Dual rate attack and decay charge pump for rapid AGC recovery

- Programmable, symmetric, charge pump currents during read data

- Charge pump currents track programmable data rate

- · Low drift AGC hold circuitry

- · Internal Low Z for write mode.

- Externally adjustable one-shot pulse width for LOWZ control

- AGC hold, fast recovery, and AGC input impedance control signals

- Wide bandwidth, precision full-wave rectifier

#### LOW PASS FILTER/EQUALIZER:

- · Programmable, 7-pole, continuous time filter provides:

- Channel filter and pulse slimming equalization for equalization to PR4

- Programmable cutoff frequency from 7 to 48 MHz

- Programmable boost/equalization of 0 to 13 dB

- Programmable group delay of ±30%

- Differentiator outputs match normal output phase

- Minimized size and power

#### FIR FILTER/EQUALIZER:

- · Seven tap filter

- · Individual tap adjustment for fine equalization to PR4 target

- · No external components required

- · Independent and/or dependent self adaption of tap weights

- · User programmable adaption parameters:

- Integration time

- Dead zone control

- Tap starting points

- Number of taps to adapt

- Selection of which taps to independently adjust

#### LEVEL QUALIFICATION:

- · Level pulse qualifier for servo and sync field reads

- Independent positive and negative thresholds for asymmetrical signals (e.g. from MR heads)

- · Independent thresholds for servo

## MAXIMUM LIKELIHOOD DETECTOR:

- Sampled Viterbi detection of signal equalized to PR4

- · Programmable threshold window

- · Survival register length of five

#### FREQUENCY SYNTHESIZER:

- · Better than 1% frequency resolution

- Up to 200 MHz frequency output

- · Independent M and N divide-by registers

- · No active external components required

#### TIMING RECOVERY

- · Single external capacitor required

- Register programmable to user data rate of 140 Mbps operation

- Fast Acquisition, sampled data phase lock loop

- Decision directed clock recovery from data samples

- Programmable damping ratio which is constant over all data rates

#### WRITE PRECOMPENSATION:

- Independently-programmable write precompensation for three data patterns

- Step resolution of 1.25% up to 40%

- · Precompensation tracks Frequency Synthesizer period

- · Differential PECL write data output

- · Precoding function suited for PR4 channel

#### SERVO:

- · Wide bandwidth, precision full-wave rectifier

- Separate, automatically-selected registers for servo f<sub>c</sub>, boost, and group delay

- · Individual area detectors for servo bursts A, B, C and D

- Programmable servo gain of ± 4 dB

#### DIGITAL BACKEND:

- 4-bit (nibble) and 8-bit (byte) wide Bidirectional NRZ interface

- · Parallel-to-Serial and Serial-to-Parallel converters

- 8/9 (0, 4/4) Encoder and Decoder

- 8-bit wide data Scrambler and Descrambler, with Pseudo Random Number Generator

- SYNC Byte detector, programmable, dual byte ("or" type)

- · Channel clock divider

- · 4-bit or 8-bit Direct Test Write and Read

#### **PIN FUNCTIONS AND DESCRIPTION**

Pin functions are described on page 57.

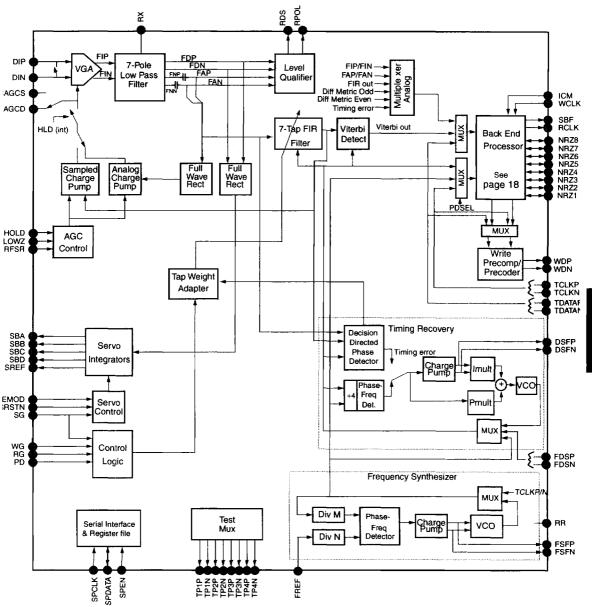

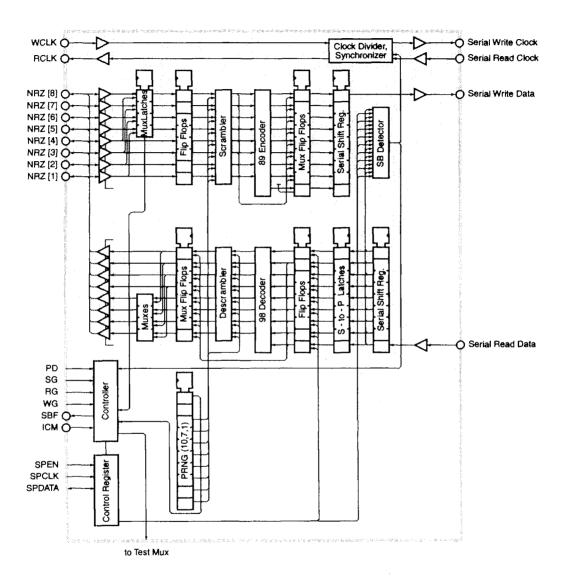

## **BLOCK DIAGRAM**

## DIGITAL BACK END TOP LEVEL SCHEMATIC / LOGIC BLOCKS

#### **BLOCK-BY-BLOCK FUNCTIONAL DESCRIPTION**

TheVM65060 implements a complete high performance PRML read channel. The VM65060 includes an AGC, programmable filter/equalizer, adaptive FIR filter, Viterbi detector, frequency synthesizer, decision-directed timing recovery, write precompensation and area detect servo, and supports user data rates up to 140 Mbps. A serial port is provided to read and write control data to the 16 internal programmable storage registers.

#### **GAIN CONTROL (GC)**

The Gain Control section of the VM65060 consists of a wideband variable gain amplifier (VGA) and a programmable continuous time filter, with a charge pump, amplitude detector, and exponentiator. The Gain Control has two modes: Automatic (AGC), and Programmable (PGC). The mode is selected with the PGC register bit.

Servo reads employ a fully differential analog AGC loop, while data reads employ both the analog loop (for fast acquisition) and a sampled/decision-directed loop (for fine tuning of the gain). The programmable gain control (PGC) circuit controls the VGA gain with an internal DAC. In PGC mode, the AGC loop is disabled and the VGA gain is a linear function of the DAC count.

The read signal is externally AC-coupled into the VGA amplifier on the DIP/DIN pins. The gain of the VGA is controlled by the voltage stored on the CAGCD hold capacitor for data reads (SG=0) and CAGCS for servo reads (SG=1). Two external holding capacitors allow for data and servo fields to have independent charge and discharge rates to avoid long reacquisitions of the gain at the beginning of the servo and data fields. The read signal is amplified and equalized by a low pass filter. The AGC loop locks the differential peak-to-peak voltage at FAP/FAN to  $V_{FA} = 0.5V_{ppd}$  for inputs ranging from 20 to 200 m $V_{ppd}$ . Test modes are provided in which the normal and differentiated filter outputs (FNP/FNN, FDP/FDN), the VGA inputs and outputs (DIP/DIN, DOP/DON), and the pulse qualifier inputs (FAP/FAN) are multiplexed to the TP2P/TP2N output pins respectively.

The analog AGC loop consists of the VGA amplifier, programmable continuous time filter, amplitude detector, exponentiator, and dual rate charge pump for fast transient recovery. Charge currents (decay) increase the capacitor voltage, V<sub>capox</sub>, and increase the VGA gain while discharge currents (attack) lower

the capacitor voltage, V<sub>cagcx</sub>, and reduce the VGA gain.

When switching between data and servo modes, the VGA gain is momentarily squelched and the input impedance is reduced by a factor of 10 (to allow quick recovery from transient offsets), then a fast recovery mode is initiated. External resistor R<sub>LOWS</sub> sets the amount of time the low Z state is on.

During ultra fast recovery, the VGA gain is increased to 144 times its normal rate until the signal exceeds its target value. The loop then enters a "fast" mode. This high bandwidth mode continues until the fast acquisition window T<sub>FAQ</sub> times-out, whereupon normal charge pump currents are reinstated and loop bandwidth is reduced to its normal value for servo mode. External resistor R<sub>FSQ</sub> sets the fast acquisition window period, T<sub>FAQ</sub>.

To optimize recovery for constant density recording, all charge pump currents track with the value loaded in the data rate register (DRR); current magnitude ranges from  $l_{\rm QXX}$  at maximum DR to  $l_{\rm QXX}/2$  at minimum DR. The magnitude of the charge pump currents,  $l_{\rm QXX}$ , are set by an external resistor connected between the RX pin and ground and are given by the following equations:

$$I_{QND} = \frac{2.16V}{RX}$$

(DRR = 11111), RX = 6 k $\Omega$  (eq. 1)

$I_{QNC} = I_{QND}/18$  ,  $I_{QFC} = I_{QND}/2..0$ ,  $I_{QUFC} = 8.6I_{QND}$  ,  $I_{QFD} = 8I_{QND}$

The RX = 6 k $\Omega$  has been optimized for user data rates of 70-140 Mbps and can be scaled appropriately for lower data rates. VTC recommends that the AGC loop response be altered by varying the CAGCx capacitors and not the RX resistor. Since servo data is written at a lower fixed frequency, the magnitudes of charge pump currents in servo mode are set equal to those that occur at the minimum data rate in read mode.

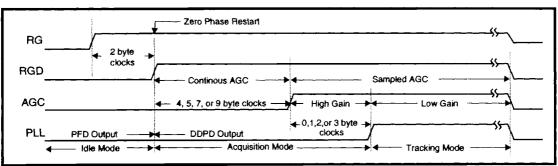

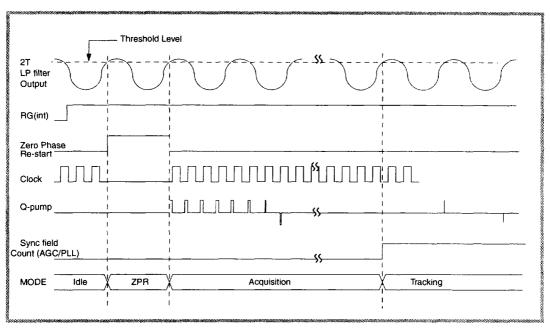

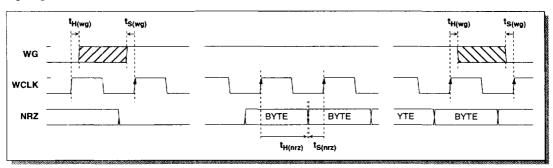

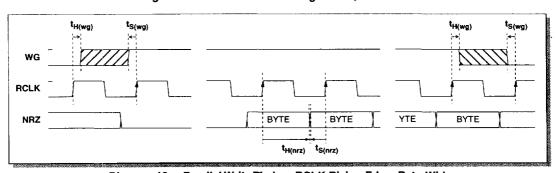

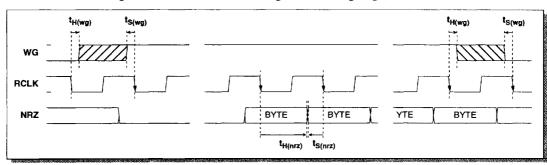

For data reads, the analog AGC loop is utilized to quickly lock onto the incoming sync field preamble. When RG is asserted, the FIR, Viterbi detector, and decision-directed AGC and timing recovery circuits are powered up (if the programmable power reduction feature is enabled). An internal, delayed RG signal (RGD) is then generated two byte times after external RG is asserted. The sync field count begins when RGD is asserted. Refer to Diagram 2.

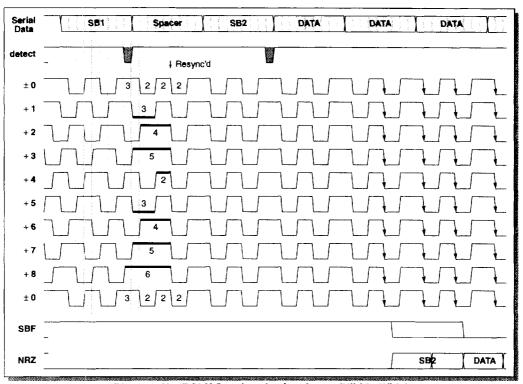

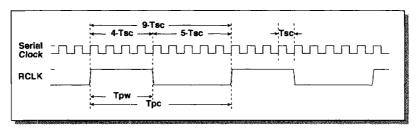

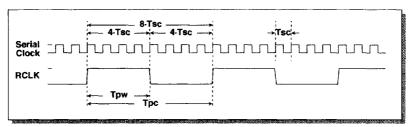

Diagram 2 VCO Sync Field Timing Diagram

The AGC transition in high gain mode and the PLL transition into tracking mode are based on two programmable sync-field counters, the AGC SF counter and the PLL SF counter. The AGC transition from continuous to sampled high gain is determined by one of four programmable counts of 4, 5, 7, or 9 byte times (for this discussion, a 'byte time' equals 8 channel-bit times) which are derived from the frequency synthesizer clock; this is the AGC SF count.

Additionally, the PLL acquisition time can be extended by one of four progammable counts of 0, 1, 2 or 3 byte times following the AGC SF count; this is the PLL SF count. The sampled AGC remains in the high gain mode for the sum of both counts, then transitions into low gain. The PLL transitions from idle to acquisition mode when RGD is asserted. The PLL remains in acquisition mode through the sum of both the AGC SF and PLL SF counts, whereupon, it transitions into the tracking mode.

The sampled AGC loop consists of the VGA, the programmable continuous time filter, the sampling 7-tap FIR equalizer, the decision amplitude detector and charge pump. Symmetrical charge and discharge currents are utilized in the sampled mode. To optimize recovery for constant density recording, the charge pump currents in the sampled mode track with the value loaded in the data rate register (DRR); current magnitude ranges from  $I_Q$  at maximum data rate (DR) to  $I_Q/2$  at minimum DR. The magnitude of the charge pump currents,  $I_Q$ , can be programmed from the sample loop control register to 0, 20, 40, or 60  $\mu A$  for DRR = 11111. The high gain charge pump current is fixed at 180  $\mu A$ .

The VGA has an exponential characteristic of gain versus control voltage in order to minimize response time over the entire range of input voltages. When in the PGC mode, the amplitude detector, charge pump, and exponentiator are disabled, and the gain of the VGA is controlled by the PGC control register. The VGA has a linear gain versus DAC count and is expressed by the following equation:

$$A_V = 2.8(N) + 2.4$$

(eq. 2)

where N ranges between 0 and 15 decimal or 0000 to 1111 binary

#### **PULSE QUALIFIER**

The pulse detector (PD), converts analog read data into a digital pulse stream, utilizing amplitude discrimination. The timing between peaks is provided on the rising edges of the RDS output. The timing channel inputs, FDP/FDN, are direct-coupled from the differentiated output of the filter. The level channel inputs FAP/FAN are AC-coupled from the normal outputs of the filter.

The timing channel inputs (FD = FDP/FDN) are derived from the differentiated output of the low pass filter. A zero-cross comparator at FD detects the peaks of the waveform to preserve the timing of the read pattern. A bi-directional one shot circuit with nominal pulse width of 4ns clocks the D-type Flip-Flop on either positive or negative transitions of the FD input. Visibility into the timing channel signal HRCLK is provided in test mode "Test Modes" on page 54.

The HRCLK pulses are qualified by signals which are derived from the low pass filter output. Two comparators indicate when the positive (LP) and negative (LN) extents of the signal VFA = VFAP-VFAN exceed either the positive threshold (VTHP) or the negative threshold (V<sub>THN</sub>) level. Independent control of positive and negative thresholds is provided with 5-bit DACs ranging from 20-80% of VFA. Vthx=20+1.9×VALUE in percent, where VALUE ranges from 0 to 31. Once the signal exceeds the level threshold, a high level is presented to the D-input of the Flip-Flop. When the peak is reached, the timing channel clocks a '1' into the Flip-Flop and triggers a one-shot producing the RDS output. The Flip-Flop resets on the rising edge of RDS and is ready for the next bit after the one-shot times out. A nominal pulse width of 24 ns is provided at the RDS output. Consecutive same-polarity pulses are also qualified. RDS polarity information is provided with the RPOL output.

# PROGRAMMABLE LOW PASS FILTER (LPF) / EQUALIZER

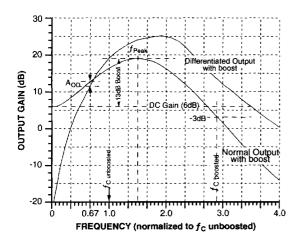

The filter is implemented as a 7-pole 0.05 degree linear phase equiripple low pass filter with matched normal and differentiated outputs. The cutoff frequency, boost, and DC group delay equalization are programmable.

The filter supplies normal and differentiated low-pass outputs with matched group delays. The normal output goes to the AGC and servo sections. The differentiated output, along with the normal output, is used by the level qualifier block to provide data and servo peak position information. The relative gain  $AO_D$  of the differentiated output to the normal output is nearly constant (at two-thirds the unboosted cutoff frequency) over the range of the cutoff frequency and boost level of the filter.

Cutoff frequency is controlled by the continuous time filter  $f_C$  DAC. The control word for the DAC is read from the CTF Data  $f_C$  register when SG=0; otherwise its read from the CTF Servo  $f_C$  register (see Table 9 Serial Register Bit Descriptions). Cutoff frequency ( $f_C$ ), in MHz, is related to the binary control word by the following equation:

$$f_C = (0.343 \times N) + 4.5$$

(eq. 3)

where N ranges between 0 and 127 decimal

The amount of boost equalization depends on the output of the BOOST DAC. Boost is programmable from 0 to 13dB as measured from the low-frequency gain portion of the frequency domain transfer function to the peak in the transfer function.

Graph 1 shows normalized filter response curves with maximum boost for both the normal and differentiated outputs.

**Graph 1 Normal and Differentiated Output Gains**

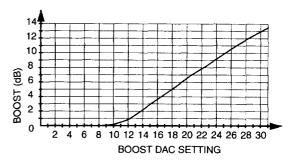

Graph 2 shows the nominal relationship between the BOOST control word and the resulting boost level.

Graph 2 Ideal Boost (in dB) versus BOOST DAC VALUE

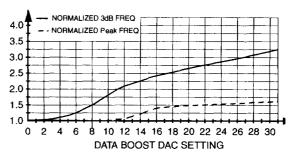

Graph 3 shows the effect of boost on the cutoff frequency.

Graph 3 Normalized  $f_c$  and  $f_{peak}$  versus DATA

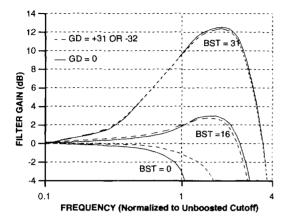

Setting the desired boost through the boost register (with the group delay register set to zero) produces symmetric zeros on the real axis. This maintains the constant group delay as in the no boost case. The group delay register can be used to produce asymmetry in the zeros causing the group delay to vary. This can be desirable to compensate for asymmetry in the heads/ media components. Group delay can be varied by  $\pm 30\%$  from the symmetric zero (group delay register = 0) condition. The boost is held nearly constant as group delay is varied.

Graph 4 shows what happens to the magnitude response as the Group Delay register varies over extremes and under several boost conditions.

Graph 4 Gain Variations with Different Boost and Group Delay Settings

The group delay register is six bits wide in "two's complement" format. A code of +31 corresponds to a DC shift in group delay of +30%; a code of -32 corresponds to -30% shift in DC group delay. Group delay is expressed as:

$$GD_{DC} = 0.95 \times GD_{DAC}$$

(eq. 4)

Group delay for an ideal 0.05 degree equiripple filter is flat within one percent out to twice the unboosted cutoff frequency. Because group delay is extremely sensitive to device mismatches and parasitic effects, a "real" filter will have variations of several percent. Group delay flatness is defined as the variation about an average value out to the specified frequency. The VM65060 group delay flatness is specified to be less then  $\pm 2\%$  out to 1.5 times the unboosted cutoff frequency. It is expressed in percent because the group delay is inversely related to the unboosted cutoff frequency, and is about 12 ns at a cutoff of 48 MHz. Thus at this cutoff frequency, the group delay varies by less than 0.18 ns out to 72 MHz.

The absolute group delay through the Gain Control block and the filter consists of both a fixed delay and a delay that varies inversely with cutoff frequency. The group delay ( $T_{\rm GD}$ ), in nanoseconds, is expressed below as a function of the cutoff frequency in MHz.

$$T_{GD} = \left[3 + \frac{434}{f_C}\right] \text{ns} \qquad (eq. 5)$$

#### FIR FILTER EQUALIZER

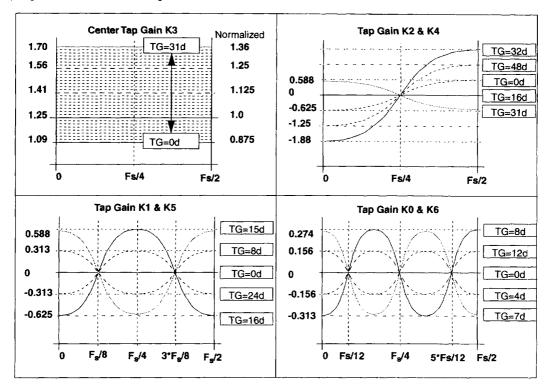

The FIR is a seven (7) tap transversal filter with independently-controllable tap weights. Independent control provides both gain and phase adjustment of the input signal. The following plot illustrates the possible gain variations achievable when symmetric taps are swept together over the allowable ranges, as listed in Table 1.

Graph 5 Symmetric Tap, frequency response curves

The  $H_0$  term provides only a real valued response equal to the center tap gain. The gain response also includes finite bandwidth characteristics of the sampler. The sampler BW is about 350 MHz and will have some effect on the frequency characteristics. The ideal gain limits for the taps are shown below.

Table 1 FIR Tap Gain settings

| Тар         | K.3              | K.2                        | K.,            | Ko             | K <sub>1</sub> | K <sub>2</sub>   | K <sub>3</sub>   |

|-------------|------------------|----------------------------|----------------|----------------|----------------|------------------|------------------|

| Gain Range  | -0.156<br>+0.137 | -0.312<br>+0.293           | 9375<br>+0.293 | +1.09<br>+1.70 | 9375<br>+0.293 | -0.312<br>+0.293 | -0.156<br>+0.137 |

| Actual bits | 4                | 5                          | 6              | 5              | 6              | 5                | 4                |

| Eff. bits   | 7                | 7                          | 7              | 7              | 7              | 7                | 7                |

| Resolution  |                  | (1/64) X 1.25 = 19.56 mV/V |                |                |                |                  |                  |

#### **FIR ADAPTION CIRCUIT**

#### Normal operation:

The adaption process starts after RG has been asserted and the internal delayed read gate RGDP has become active. It should be noted that since the part is accessing the serial registers during adaption, the user should NOT attempt any serial register operation while RG is asserted and the AE bit is set.

#### **Parameter Descriptions:**

- Adaptation Control Test "ACTST"

- These bits allow the basic verification of the Adaptation Control logic.

- Adaptation Enable "AE"

- This bit controls whether adaptation is to be performed. It cannot be modified during an adaptation read cycle.

- Dead Zone "DZ"

- This three-bit control specifies how many update samples are required in either direction to cause adaptation in that direction. The value sets the threshold in a symmetrical manner.

- Integration Length "INTL"

- This two-bit control selects the number of samples to average for each update cycle (12, 15, 18, or 21)

- Initial Tap Weight "ITW"

- This value selects which tap to adapt first.

- No Sync Byte "NOSB"

- This feature causes adaptation to occur at the point where the timing recovery circuit makes the transition from acquisition to tracking modes. This occurs during the VCO sync field even before the sync bytes.

- This option may be useful during initial drive optimization and data recovery modes.

- Tap Weight Range "TWR"

- This value sets the number of taps that are adjusted. If all six taps are to be adjusted this value should be set to "0". By setting this value to "1" through "4" a reduced range of taps will be adjusted. The taps that are not adjusted are still active but are held at their preprogrammed values.

- Symmetry control "SYMC"

- This two-bit control selects which sets of taps should be controlled in a symmetrical manner.

Tap weights can be written and read by the controller. Thus the initial tap weight values can be preset near their optimal values and the final values can be read back after each adaption read cycle. The final taps weights remain as the initial tap weights for subsequent read cycles.

Proper selection of DZ and INTL can allow for rapid adaptation or for slow highly-stable tracking of system changes.

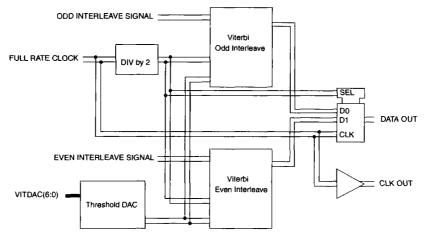

#### VITERBI DETECTOR

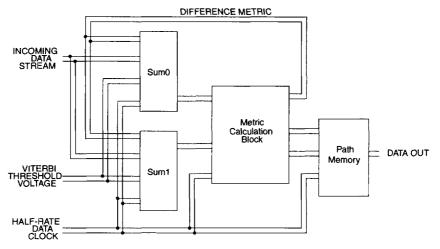

The Viterbi detector implements the maximum likelihood (ML) detector for PRML. The Viterbi detector block diagram is shown in Diagram 3.

Diagram 3 Viterbi Detector Block Diagram

Note that all signals are differential. The incoming signal (from the FIR filter via the timing recovery block) has been demultiplexed into the odd and even interleaves on a bit-by-bit basis. This is shown in the diagram as the odd interleave signal and the even interleave signal. Each interleave of the Viterbi detector runs at 1/2 the channel data rate. Note that the odd and even interleaves of the Viterbi detector are clocked on opposite phases of the full rate data clock. Each interleave independently processes its data stream. The data streams from the odd and even interleaves are then multiplexed back together on a bit-by-bit basis to yield the recovered bit stream.

The nominal Viterbi threshold window size is set by a 7-bit DAC which is controlled by the Viterbi DAC serial control register. Positive and negative thresholds in the Viterbi detector are modified based on the received data.

The dynamic thresholds in the Viterbi detector function to reject pulses of the same polarity as the most recent pulse, but of lesser amplitude. If a pulse of the same polarity as the most recent pulse exceeds the amplitude of the previous pulse, the 1 associated with the previous pulse (which is of lesser amplitude) is erased in the Viterbi detector's path memory. The path memory only has the ability to erase these smaller pulses if four or fewer zeroes have occurred between the two pulses of the same polarity. This requirement is satisfied by the (0.4.4) encoding that is used with this part.

The AGC circuit adjusts the signal amplitude to ±250 mV peak. Side sampling for PR4 produces a nominal sampled-signal amplitude of ±180 mV. This is a pseudo-ternary signal with the ±1 levels equal to ±180 mV and the zero level equal to 0 mV. Thus, the Viterbi threshold, VIT<sub>TH</sub>, is nominally set to 90 mV. Since the data is pseudo-ternary, the nominal Viterbi threshold window size is 2•VIT<sub>TH</sub>.

$$VIT_{TH} = \left[0.047 + 0.376 \left(\frac{VALUE}{127}\right)\right] mV$$

(eq. 6)

where VALUE is between 0 and 127, inclusive

Diagram 4 shows a block diagram of a Viterbi detector interleave.

Diagram 4 Viterbi Interleave Block Diagram

The summing blocks, Sum0 and Sum1, each form two signals that are fed to the metric calculation block. Opposite polarities of the incoming data stream and the difference metric are used by Sum0 and Sum1. The metric calculation block outputs the difference metric (which is fed back to the Sum0 and Sum1 blocks) and the two data streams that are used by the path memory block. One of these two data streams from the metric calculation block represents 1's that come from positive pulses in the ternary data signal. The other data stream represents 1's due to the negative pulses in the ternary data stream. Two 1's in one of the data streams without an intervening 1 in the other data stream results in the path memory erasing the first of these two consecutive 1's. A 0 results when neither of the two data streams is a 1. Decoding of the ternary signal is straightforward: a positive or negative pulse results in a 1; no pulse decodes to a 0. This decoding action can be thought of as undoing the precoding function.

#### FREQUENCY SYNTHESIZER

The Frequency Synthesizer (FS) is a PLL-based circuit that provides a programmable reference frequency for constant density recording applications. The frequency synthesizer output frequency can be programmed with a better than 1% accuracy via the M,N ("divide by") and DR (Data Rate) Registers. The synthesizer output frequency, F<sub>OUT</sub>, should be programmed as close as possible to ((9/8)\*User Data Rate). The synthesizer also supplies the timing reference for write precompensation so that the precompensation tracks the VCO period.

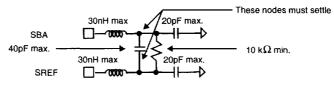

The frequency synthesizer requires an external passive loop filter to control its PLL locking characteristics. This filter is pseudo-differential and balanced in order to reduce the effects of common mode noise.

In Write and Idle modes, the programmable frequency synthesizer is used to provide a stable reference frequency to the timing recovery loop. In the Write and Idle modes, the frequency synthesizer output, when selected by the Control Test Mode Register, can be monitored at the TP3 test pin. In the Read mode, the FS output should not be selected for output on the test pins so that the possibility of jitter in the timing recovery PLL is minimized.

The synthesizer output frequency is programmed using the M and N registers of the frequency synthesizer via the serial port, and is related to the external reference clock input, FREF, as follows:

$$f_{\text{out}} = f_{\text{FREF}} \left[ \frac{(M+1)}{(N+1)} \right] \tag{eq. 7}$$

The M and N values should be chosen with the consideration of phase detector update rate and the external passive loop filter design. The Data Rate Register must be set to the correct VCO center frequency.

The DR register value directly affects the following:

- Center frequency of the frequency synthesizer VCO

- Center frequency of the timing recovery VCO

- · Phase detector gain of the frequency synthesizer phase detector

- Write precompensation

The reference current for the DR DAC is set by an external resistor, RR, connected between the GND and RR pins. The VCO center frequency,  $f_c$ , and the charge pump current,  $I_{QP}$ , are given by the equations below. RR is the resistance of the external resistor in Ohms, X is the decimal equivalent of the DR Register bits and  $K_{VCO}$  (radV \* s) is the VCO gain.

$$\omega_{C} = \left(\frac{4 \times 10^{10}}{BB}\right) \times (33 + X) \quad (0 \le X \le 31)$$

(eq. 8)

$$K_{VCO} = 0.35 \times \omega_{C} \tag{eq. 9}$$

$$I_{QP} = \left(\frac{0.01875}{BB}\right) \times (63 - X)$$

(eq. 10)

#### TIMING RECOVERY

The data synchronizer uses a fully integrated, fast acquisition, PLL to perform clock recovery from the incoming data stream.

Fast acquisition is obtained by locking the loop to the synthesizer during Write, Servo & Idle modes which minimizes the frequency transient that occurs when the Read mode is initiated. Thus the timing recovery PLL uses two separate phase detectors to drive the loop. A Decision-directed Phase Detector (DDPD) is used in the Read mode and phase-frequency detector (PFD) is used in the Write, Servo, and Idle modes.

The Read mode is initiated by performing a zero phase restart of the VCO, which will force a phase alignment to the incoming 2T (1/4 data-rate) clock pattern. The samples taken immediately after the restart will be used by the DDPD to "coarse adjust" the VCO. After the sync field count has reached the programmed count (AGC + PLL offset), as shown in Diagram 2, the PLL will be switched to tracking mode which reduces the loop bandwidth (BW) by a factor of 2 or 4 depending on the register settings. In the tracking mode the input to the DDPD is taken from the output of the FIR filter.

#### **TIMING RECOVERY OPERATION**

In Write or Idle mode, active when the RG (read gate) line is low, the mux selects the PFD as the input to the Q-pump and P-mult circuits. The two signal paths provide Proportional and Integral error terms to the VCO input. The benefit of this architecture is independent control of the loop parameters BW (bandwidth) and  $\zeta$  (damping factor) via the control registers. The proportional term is controlled by the Damping Ratio DAC and the integral term is controlled by the Data Rate (DR) DAC. The VCO center frequency is set by the DR DAC; as the rate is increased the VCO gain must increase in order to maintain a constant locking range. The damping factor remains constant as the loop BW is changed. The net result of the loop is that it will settle in a constant number of clock cycles independent of the clock period.

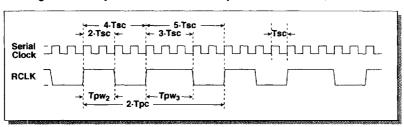

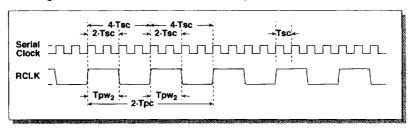

The Read mode is initiated by a positive transition on the "RG" line as shown in Diagram 5.

Diagram 5 Timing Recovery Operation

The VCO is held in a low output state when the 2T input signal crosses the threshold set by the Zero Phase Restart DAC. The second time the threshold is crossed the VCO restarts. The threshold is set to align the VCO to the ideal PR4 sample phase of  $\Pi$ /4, which is 0.707 times the AGC's analog servo voltage  $V_{TH}$ . The analog and digital delays in the samplers and the VCO require a slight variation of that sample threshold so a multiplying DAC is used to obtain the optimal set point. Once the VCO restarts, the DDPD output is used as the phase error to drive the PLL. The initial gain will be high to minimize the acquisition time and the computation of the phase error is done with a robust technique which prevents any false lock-up modes. After the sync field count has been reached the error detection mode will be changed to allow for three valid signal levels (only two are used in Acquisition) and the gains are reduced to reduce jitter. Since the AGC gain control is independent the timing control it can be switched at any point after the FIR has taken 7 samples (7-tap filter) and is switched slightly before the timing transition from Acquisition to Tracking. If the DSP mode is in progress this transition will enable the detection of the sync byte.

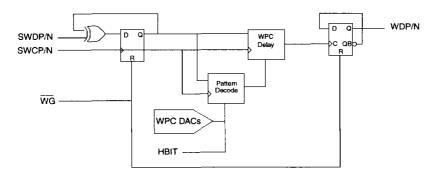

#### WRITE PRECOMPENSATION

The write precompensation circuitry is provided to compensate for media bit shift caused by magnetic nonlinearities. The circuit recognizes six specific write data patterns of 4 channel bit lengths and can add delay in the transition of write data bits to counteract the magnetic non-linearity effect. The magnitude of the time shift is programmable via a Register and is made proportional to the frequency synthesizer's VCO period (i.e. data rate). Since the WPC operation is performed prior to the final T-FF (which is part of the precoding function) only three distinct patterns are decoded. Each of these three patterns may be independently programmed. The precoding operation is included with the WPC circuitry.

Each DAC allows write precompensation delay (Twpc) values to be programmed from 0 to 0.20T with 1.25% resolution as shown in the following equations.

$$Twpc(Pattern1,3) = (0.013 \bullet Kwp + 0.20 \bullet WPCHR) \bullet T$$

(eq. 11)

$$Twpc(Pattern2) = (0.013 \bullet Kwp) \bullet T$$

(eq. 12)

where T is the period of the VCO, in nano-seconds, and Kwp is the value of the 4-bit DAC word for any of the three patterns

HBIT is an independently-programmable bit which allows an addition 20% precompensation for patterns 1 and 3. By setting this bit high, patterns 1 and 3 will have a range from 20 to 40 percent of the VCO period. HBIT does not affect pattern 2. If no compensation is desired for any of the three patterns, then that particular DAC word may be set to 0.

The precoder and all internal states in the WPC get reset with the de-assertion of write gate (WG) so that the write path is always in the same state upon assertion of WG. This also prevents any false data from being sent to the preamp during non-write modes.

| Pattern | Data Pattern | Write Data Pattern |

|---------|--------------|--------------------|

| 1       | 011          | 0010/1101          |

| 2       | 101          | 0110/1001          |

| 3       | 111          | 0101/1010          |

Diagram 6 WPC/Precoder Block Diagram

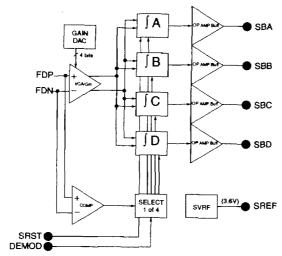

#### SERVO DEMODULATOR

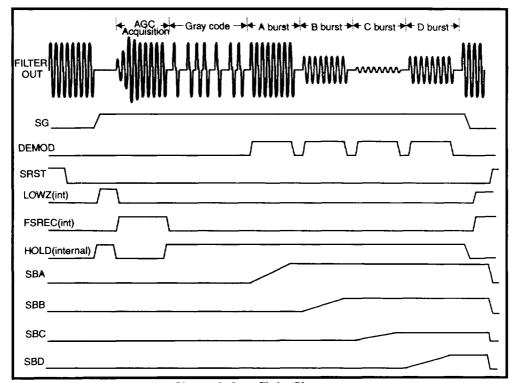

The embedded servo demodulator processor extracts the head position error information from the embedded servo bursts using an area detection technique. It supports full quadrature demodulation through the use of an array of four area detector channels. The area detection technique provides improved noise immunity over peak detection. A block diagram for the servo demodulator is shown in Diagram 7.

Diagram 7 Servo Demodulator Block Diagram

The demodulator contains a variable gain amplifier, rectifier, four pulse area detectors and required timing logic. The differentiated filtered servo bursts are input to a variable gain amplifier (VGA). The VGA allows the demodulator block to accommodate a wide dynamic range of servo burst amplitudes and process variations of the internal integration capacitors and resistors. The gain range of the VGA is ±40% in steps of 5%, as defined in the servo gain control register. The amplified signal is full-wave rectified and input to an array of four area detectors. The area detector consists of a gm stage driving an on-chip integration capacitor. Note that the ±30% tolerance of the on-chip capacitors and gm block can be calibrated by adjusting the gain of the VGA.

Each area detector is selectively enabled when the DEMOD control input goes high and integrates the pulse voltage amplitude of the servo burst. After the burst pulses have been integrated, the DEMOD signal is brought low, the area detector is disabled and the final integrated voltage is held. Consecutive cycles of the DEMOD pin cause the A, B, C, and D area detectors to sample the input waveform. Upon the low level of SRST, the servo burst outputs are reset to the SREF voltage.

Diagram 8 Servo Timing Diagram

#### DIGITAL BACK END

The VM65060's digital back end section consists of the following blocks: byte-wide (eight bit) parallel data interface, nibble-wide (four bit) parallel data interface, 8-bit wide scrambler/descrambler with PRNG, 8/9 (0, 4, 4) encoder/decoder, parallel/serial circuitry, sync byte circuitry, channel clock divider and mode control circuitry. These blocks are described below.

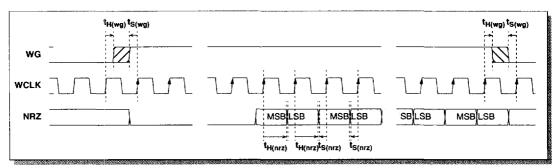

#### 8-bit (Byte-Wide) Bidirectional NRZ interface

The 8-bit NRZ interface is a set of eight bidirectional pins that provide the ability to interface with a byte-wide disk controller. Each pin has a TTL level input detector and a tristate TTL level output driver. The input detector is disabled during sleep mode. The output driver is put into high impedance when not driving the NRZ line. These pins, when not driving data out of the digital back end, must be driven by external sources (as all CMOS inputs).

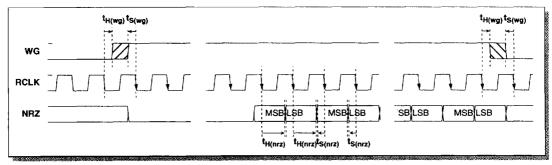

In write mode, the NRZ data can be latched-in on the rising edge of WCLK or either edge of RCLK. The setting of two control register bits determines the configuration. The length of the VCO Sync Field is user-determined. Internal circuitry ignores the first two NRZ bytes, assuming them to be zero. This allows for a possible late driving of the NRZ bus with respect to the rising edge of WG. The end of the VCO Sync Field, and the start of the SYNC Byte section, is determined by the first non-zero byte strobed into the VM65060. NRZ[8] through NRZ[5] are used for non-zero detection. NRZ[4] through NRZ[1] are not monitored by the non-zero detector circuitry. Thus the MSB half of the first SYNC Byte must be non-zero, while the LSB half can be all zero.

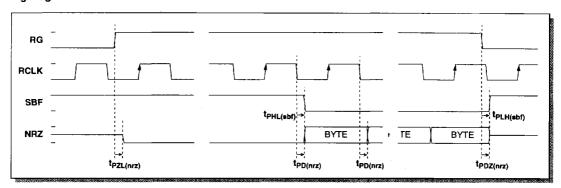

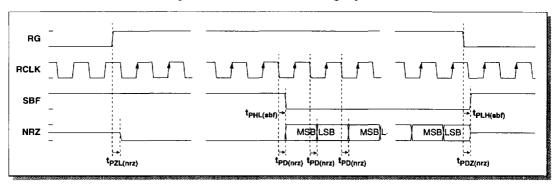

In read mode, the NRZ data is driven out on the falling edge of RCLK. When RG goes high, the NRZ interface will drive low until either SYNC byte has been detected. The first non-zero data driven out on the NRZ pins will be either the first User Data word or else the SYNC Byte pattern. The user has the option to precede the User Data with the SYNC Byte pattern.

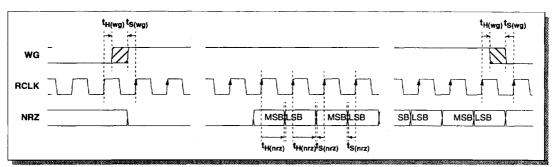

#### 4-bit (Nibble-Wide) Bidirectional NRZ interface

The operation of the 4-bit NRZ interface is similar to that of the 8-bit interface. The main difference being that only the pins NRZ[4] through NRZ[1] are used, with NRZ[8] through NRZ[5] being tied-off by the user. Eight-bit words are still used but they are broken into two 4-bit nibbles. The first nibble is the MSB half and the second nibble is the LSB half. Within the VM65060 the two 4-bit halves are concatenated into a full 8-bit word. During nibble operations the RCLK is run at twice the frequency as the internal byte clock, thus maintaining equivalent byte speed operation.

#### 8-bit wide Scrambler / Descrambler, with PRNG

The Scrambler and Descrambler circuits, which are used to randomize user data, half-add each bit of an 8-bit Pseudo Random Number (PRN) to each bit of the 8-bit user data. The half-adding is done through the use of eight XNOR gates. The same PRN is half-added during write and again during read, resulting in the original user data being returned. The PRN comes from a shared Pseudo Random Number Generator (PRNG) which itself is based upon the  $X^{10} + X^3 + 1$  polynomial.

At the beginning of write mode the PRNG is initialized to all 0's. The PRNG then generates a PRN of continuous  $00_H$  until it is set with the FF<sub>H</sub> seed. This continuous  $00_H$  PRN in turn allows the scrambler to act as inverting buffers on the NRZ's VCO Sync Field during write mode. This causes the continuous  $00_H$  being detected on the NRZ inputs to be inverted into continuous FF<sub>H</sub> before entering the Encoder. At the end of the VCO Sync Field the PRNG is set to all 1's. This allows for a maximum run length PRN pattern as well as allowing the scrambler to act as a noninverting buffer on the NRZ's SYNC Bytes and Spacer byte. At the end of the three Sync Byte cycles, the PRNG is enabled into a free-running condition where PRN's are generated and half-added to the User Data until the end of the write mode.

At the beginning of read mode the PRNG is initialized to all 1's. Following the successful detection of a Sync Byte, the PRNG is enabled into a free-running condition where PRN's are generated and half-added to the User Data before being passing on to the NRZ output drivers until the end of the read mode.

During Idle, Sleep, or Direct Test modes the PRNG's clock is disabled to save power. During normal Write or Read modes the PRNG's clock is enabled. The user has the option to not scramble and descramble the User Data by not generating PRN's with the PRNG. When this option is chosen, the PRNG remains set at all 1's throughout the User Data fields, and the scrambler and descrambler circuitries simply buffer the User Data in both the write path and the read path.

#### 8/9 (0, 4, 4) Encoder / Decoder

In order to provide for proper partial response maximum likelihood (PRML) signaling and detection in the recording channel, a run length limited (RLL) code of parameters (0, 4, 4) is being provided. As 8-bit data words are being provided for recording, the simplest (0, 4, 4) RLL code for 8-bit words is to use a set of qualified 9-bit code words. There are 279 qualified 9-bit code words, out of the possible 512 9-bit words. Only 256 of these are required to encode the 8-bit data word. This is known as an 8/9 code. The code word to data word assignments have been made to minimize both logic delay and chip area. Circuitry has been designed to provide for both encoding and decoding the 8-bit data words.

Table 2 and Table 3 show the relationships between the 8-bit data words (shown in hexadecimal notation) and the 9-bit code words (shown in octal notation) incorporated in the encoder circuitry. Unused or invalid codewords are not shown.

| DATA     | CODE  | DATA         | CODE        | DATA : CODE          | DATA : CODE          |

|----------|-------|--------------|-------------|----------------------|----------------------|

| 00       | : 356 | 40           | 756         | 80 : 456             | CO : 416             |

| 01       | : 351 | 41           |             | 81 : 451             | C1 : 411             |

| 02       | : 357 | 42           | 222         | 82 : 457             | C2 : 622             |

| 03       | : 341 | 43           | 223         | 83 : 441             | C3 : 623             |

| 04       | : 354 | 44 :         | 754         | 84 : 454             | C4 : 414             |

| 05       | 355   | 45 :         | 755         | 85 : 455             | C5 : 415             |

| 06       | : 344 | 46           | 226         | 86 : 444             | C6 : 626             |

| 07       | 345   | 47 :         | 227         | 87 : 445             | C7 : 627             |

| 08       | 353   | 48 :         | 753         | 88 : 453             | C8 : 413             |

| 09       | 311   | 49           | 231         | 89 : 431             | C9 : 631             |

| OA :     | : 307 | 4A :         | 232         | 8A : 432             | CA : 632             |

| 0B       |       | 48 :         | 233         | 8B : 433             | CB : 633             |

|          | 314   | 4C :         |             | 8C : 434             | CC : 634             |

| 0D       | : 315 | 4D :         |             | 8D : 435             | CD : 635             |

| 0E       | 316   | 4E :         | 236         | 8E : 436             | CE : 636             |

| 0F       | 317   | 4F :         | 237         | 8F : 437             | CF : 637             |

| 10       | 656   | 50 :         |             | 90 : 446             | D0 : 646             |

| 11       |       | 51 :         |             | 91 : 461             | D1 : 661             |

| 12       | 657   | 52 :         |             | 92 : 462             | D2 : 662             |

| 13       |       | 53           |             | 93 : 463             | D3 : 663             |

| 14       |       | 54 :         |             | 94 : 464             | D4 : 664             |

| 15       |       | 55 :         | 265         | 95 : 465             | D5 : 665             |

| 16       | 644   | 56 :<br>57 : | 266         | 96 : 466             | D6 : 666             |

|          |       |              | 267         | 97 : 467             | D7 : 667             |

| 18       |       | 58 :<br>59 : | 703         | 98 : 443<br>99 : 471 | D8 : 643             |

| 19<br>1A |       | 59 :<br>5A : | 271         | 99 : 471<br>9A : 472 | D9 : 671<br>DA : 672 |

| 1B :     |       | 5A :         | 273         | 98 : 472<br>9B : 473 | DB : 673             |

| 1C :     | 614   | 5C :         |             | 9C : 474             | DC : 674             |

| 1D       | 615   | 5D :         | <del></del> | 9D : 475             | DD : 675             |

| 1E       |       | 5E :         | 276         | 9E : 476             | DE : 676             |

| 1F :     | 617   | 5F :         | 277         | 9F : 477             | DF : 677             |

| 20       | 156   | 60 :         | 116         | A0 : 556             | E0 : 516             |

| 21       | : 151 | 61 :         | 111         | A1 : 551             | E1 : 511             |

| 22       |       | 62 :         |             | A2 : 557             | E2 : 722             |

| 23       | 141   | 63 :         | 323         | A3 : 541             | E3 : 723             |

| 24       | 154   | 64 :         | 114         | A4 : 554             | E4 : 514             |

| 25 :     |       | 65 :         | 115         | A5 : 555             | E5 : 515             |

| 26 :     |       | 66 :         | 326         | A6 : 544             | E6 : 726             |

| 27 :     | 145   | 67 :         | 327         | A7 : 545             | E7 : 727             |

| 28 :     | 153   | 68 :         | 113         | A8 : 553             | E8 : 513             |

| 29 :     | 131   | 69 :         | 331         | A9 : 531             | E9 : 731             |

| 2A :     |       | 6A :         | 332         | AA : 532             | EA : 732             |

| 2B :     |       | 6B :         | 333         | AB : 533             | EB : 733             |

| 2C :     | 134   | 6C :         | 334         | AC : 534             | EC : 734             |

| 2D :     |       | 6D :         | 335         | AD : 535             | ED : 735             |

| 2E :     | 136   | 6E :         | 336         | AE : 536             | EE : 736             |

| 2F :     |       | 6F :         | 337         | AF : 537             | EF : 737             |

| 30 :     | 146   | 70 :<br>71 : | 346         | B0 : 546             | F0 : 746             |

| 31 :     | 161   | 71 :         | 361<br>362  | B1 : 561<br>B2 : 562 | F1 : 761<br>F2 : 762 |

|          |       |              | 363         |                      |                      |

| 33       | 164   | 73 :<br>74 : | 364         | B3 : 563<br>B4 : 564 | F3 : 763<br>F4 : 764 |

| 35 :     |       | 75 :         | 365         | B5 : 565             | F5 : 765             |

| 36       |       | 76 :         | 366         | B6 : 566             | F6 : 766             |

| 37 :     |       | 77 :         | 367         | B7 : 567             | F7 : 767             |

| 38       | 143   | 78           | 343         | B8 : 543             | F8 : 743             |

| 39       | 171   | 79 :         | 371         | B9 : 571             | F9 : 771             |

| 3A       |       | 7A :         | 372         | BA : 572             | FA : 772             |

| 3B :     |       | 7B :         | 373         | BB : 573             | FB : 773             |

| 3C :     |       | 7C :         | 374         | BC : 574             | FC : 774             |

| 3D :     |       | 7D :         | 375         | BD : 575             | FD : 775             |

| 3E :     |       | 7E :         | 376         | BE : 576             | FE : 776             |

| 3F :     |       | 7F :         | 377         | BF : 577             | FF : 777             |

| <u> </u> |       | <u> </u>     |             |                      |                      |

Table 2 8-bit Data Word (hexadecimal) to 9-bit Code Word (octal)

| CODE  | DATA     | CODE       | DATA  | CODE  | DATA      | CODE           | : DATA |

|-------|----------|------------|-------|-------|-----------|----------------|--------|

| 111 : | 61       | 313        | OB    | 461 : | 91        | 633            | СВ     |

| 113 : | 68       | 314        | : 0C  | 462 : | 92        | 634            | CC     |

| 114   | 64       | 315        | : OD  | 463 : | 93        | 635            | CD     |

| 115   | 65       | 316        | 0E    | 464 : | 94        | 636 :          | CE     |

| 116   | 60       | 317        | OF    | 465 : | 95        | 637 :          | CF     |

| 131 : | 29       | 322        | 62    | 466 : | 96        | 641 :          | 13     |

| 132 : | 2A       | 323 :      | 63    | 467 : | 97        | 643 :          | D8     |

| 133   | 2B       | 326        | 66    | 471 : | 99        | 644 :          |        |

| 134   | 2C       | 327        | 67    | 472 : | 9A        | 645 :          |        |

| 135   |          | 331        |       | 473 : | 9B        | 646 :          |        |

| 136   |          | 332        |       | 474 : | 9C        | 651 :          | 11     |

| 137   | 2F       | 333        | 6B    | 475 : | 9D        | 653            | 18     |

| 141   | 23       | 334        |       | 476 : | 9E        | 654            | 14     |

| 143   |          | 335        |       | 477   | 9F        | 655            | 15     |

| 144   | 26       | 336        |       | 511 : | E1        | 656            |        |

| 145   | 27       | 337        | 6F    | 513   | E8        | 657            | 12     |

| 146 : | 30       | 341        | 03    | 514 : | E4        | 661 :          |        |

|       |          | 343        | 78    |       | E5        | 662            | D2     |

|       |          |            |       |       |           |                |        |

| 153   |          | 344        |       | 516 : | E0        | 663 :          |        |

| 154   | 24       | 345        | 07    | 531 : | A9        | 664 :          | D4     |

| 155   | 25       | 346        | 70    | 532 : | AA        | 665 :          | D5     |

| 156   |          | 351        | 01    | 533 : | AB        | 666            |        |

| 157   | 22       | 353        |       | 534 : | AC        | 667 :          | D7     |

| 161 : |          | 354        | 04    | 535 : | AD        | 671 :          | _D9    |

| 162 : | 32       | 355        | 05    | 536 : | AE        | 672 :          | DA     |

| 163   | 33       | 356        | 00    | 537 : | AF        | 673 :          | DB     |

| 164 : | 34       | 357        | 02    | 541 : | A3        | 674 :          | DC     |

| 165   | 35       | 361        | 71    | 543 : | 88        | 675 :          | DD     |

| 166 : | 36       | 362        | 72    | 544 : | A6        | 676 :          | DE     |

| 167 : | 37       | 363        | 73    | 545 : | A7        | 677 :          | DF     |

| 171 ; | 39       | 364        | 74    | 546 : | B0        | 703 :          | 58     |

| 172   |          | 365        |       | 551   | A1        | 706 :          | 50     |

| 173 : | 3B       | 366        | 76    | 553 : | A8        | 722            | E2     |

| 174   | 3C       | 367        | 77    | 554 : | A4        | 723 :          | E3     |

| 175   | 3D       | 371 :      |       | 555 : | A5        | 726 :          | E6     |

| 176   | 3E       | 372        |       | 556 : | AO        | 727 :          | E7     |

| 177   | 3F       | 373        | 7B    | 557 : | A2        | 731 :          | E9     |

| 222   | 42       | 374        | 7C    | 561   | B1        | 732            | EA     |

| 223   | 43       | 375        | 7D    | 562 : | B2        | 733            | EB     |

| 226   |          | 376        |       | 563 : | B3        | 734 :          | EC     |

| 227   | 47       | 377        | 7F    | 564 : | B4        | 735 :          | ED     |

| 231 : | 49       | 411        | C1    | 565 : | B5        | 736 :          |        |

| 231   | 49<br>4A |            | C8    | 566 : | B6        | 730 :          | EF     |

|       |          |            |       |       |           |                |        |

| 233   | 4B       | 414 :      | C4    | 567 : | <u>B7</u> | 743            | F8     |

| 234 : | 4C       | 415        | C5    | 571 : | B9        | 746            | F0     |

| 235   | 4D       | 416        | CO    | 572 : | BA        | 751            | 41     |

| 236   | 4E       | 431        | 89    | 573 : | BB        | 753 :          | 48     |

| 237   | 4F       | 432        | ***** | 574 : | BC        | 754 :          | 44     |

| 261 : | 51       | 433        | 8B    | 575 : | BD        | 755 :          | 45     |

| 262   | 52       | 434        |       | 576 : |           | 756 :          | 40     |

| 263   | 53       | 435        | 8D    | 577 : | BF        | 761 :          | F1     |

| 264   |          | 436        |       | 607 : | 1A        | 762 :          |        |

| 265   | 55       | 437        | 8F    | 611 : | 19        | 763            |        |

| 266   | 56       | 441        | 83    | 613   | 1B        | 764 :          | F4     |

| 267   | 57       | 443        | 98    | 614 : | 1C        | 765            | F5     |

| 271 : |          | 444        |       | 615   | 1D        | 7 <b>6</b> 6 : |        |

| 272 : | 5A       | 445        | 87    | 616 : | 1E        | 767 :          | F7     |

| 273   | 5B       | 446        | 90    | 617 : | 1F        | 771 :          | F9     |

| 274   | : 5C     | 451        | : 81  | 622 : | C2        | 772            | FA     |

| 275   |          | 453        |       | 623 : | СЗ        | 773            |        |

| 276   | 5E       | 454        | 84    | 626   | C6        | 774            | FC     |

|       |          |            |       | 627   | C7        | 775            | FD     |

|       | : 5F     | 455        | . 60  |       |           |                |        |

| 277   | 5F<br>08 | 455<br>456 | 85    | 631 : | C9        | 776            |        |

Table 3 9-bit Code Word (octal) to 8-bit Data Word (hexadecimal)

279 of 512 9-bit words meet the (0, 4, 4) RLL requirement. Of these, only 256 are needed to encode the 256 8-bit data words. Therefore many breaks occur in the codeword sequence of Table 3.

The 256 codewords that are utilized (out of the 279 valid codewords) were chosen so as to be able to realize encoder and decoder logic circuitry in the simplest and fastest means possible. A maximum of five gate delays through the encoder and through the decoder have been realized.

Valid codewords do not allow for runs of more than four zeros in either the data sequence, or in either the even indexed or odd indexed interleaves. Codewords that have zero pairs at either end, in either the main sequence or in either of the interleaves are allowed. Therefore, codewords with zero triplets at either end of any sequence are invalid.

Invalid codeword configurations are identified below.

| 000 XXX XXX <sub>B</sub> |                    | XX0 000 0XX <sub>B</sub><br>603 <sub>O</sub> |                  | 000 X              |

|--------------------------|--------------------|----------------------------------------------|------------------|--------------------|

|                          |                    | 3330                                         | ,                |                    |

| 0X0 X0                   | X XXX <sub>B</sub> |                                              | XXX XC           | ROX0 X             |

| 20X <sub>O</sub>         | 24X <sub>O</sub>   |                                              | X02 <sub>O</sub> | X42 <sub>0</sub>   |

| 21X <sub>0</sub>         | 25X <sub>O</sub>   |                                              | X12 <sub>O</sub> | X52 <sub>0</sub>   |

| XOX OX                   | O XXX <sub>B</sub> |                                              | XXX 0X           | O XOX <sub>B</sub> |

| 10X <sub>O</sub>         | 42X <sub>0</sub>   |                                              | X01 <sub>O</sub> | X21 <sub>0</sub>   |

| 12X <sub>0</sub>         | 50X <sub>O</sub>   |                                              | X04 <sub>O</sub> | X24 <sub>0</sub>   |

| 40X <sub>0</sub>         | 52X <sub>0</sub>   |                                              | X05 <sub>0</sub> | X25 <sub>0</sub>   |

Invalid cases are shown in Table 4. A total of 233 9-bit words are invalid.

| CODE :         | DATA       | CODE : DATA | CODE : DATA          | CODE : DATA |

|----------------|------------|-------------|----------------------|-------------|

| 117 :          | 62         | 051 : 01    | 220 : 40             | 460 : 90    |

| 147 :          | 3A         | 052 : 08    | 221 : 41             | 470 : 98    |

| 303 :          | 08         | 053 : 08    | 224 : 44             | 500 : E2    |

| 306 :          | 00         | 054 : 04    | 225 : 45             | 501 : E3    |

| 347 :          | 7A         | 055 : 05    | 230 : 48             | 502 : E8    |

| 417 :          | C2         | 056 : 00    | 240 : 12             | 503 : E8    |

| 447 :          | 9A         | 057 : 02    | 241 : 13             | 504 : E6    |

| 517 :          | E2         | 060 : 10    | 242 : 58             | 505 : E7    |

| 547 :          | BA         | 061 : 11    | 243 : 58             | 506 : E0    |

| 606 :          | 10         | 062 : 12    | 244 : 16             | 507 : EA    |

| 647 :          | DA         | 063 : 13    | 245 : 17             | 510 : E0    |

| 707 :          | 5A         | 064 : 14    | 246 : 50             | 512 : E8    |

| 711 :          | 59         | 065 : 15    | 247 : 5A             | 520 : A0    |

|                | 5B         | 066 : 16    |                      | 521 : A1    |

| 713 :<br>714 : | 5C         | 067 : 17    | 250 : 10<br>251 : 11 | 522 : A2    |

| 715            | 5D         | 070 : 18    | 252 18               | 523 : A3    |

|                | 5E         | 070 : 18    | 252 . 18             | 523 . A3    |

| 716 :          |            |             |                      |             |

| 717 :          | 5F         | 072 : 1A    | 254 : 14             |             |

| 741 :          | 43         | 073 : 1B    | 255 : 15             | 526 : A6    |

| 744 :          | 46         | 074 : 1C    | 256 : 10             | 527 : A7    |

| 745 :          | 47         | 075 : 1D    | 257 : 12             | 530 : A8    |

| 747 :          | FA         | 076 : 1E    | 260 : 50             | 540 : A2    |

| 757 :          | 42         | 077 : 1F    | 270 : 58             | 542 : B8    |

| 000 :          | 42         | 100 : 62    | 300 : 02             | 550 : A0    |

| 001 :          | 43         | 101 : 63    | 301 : 03             | 552 : A8    |

| 002 :          | 48         | 102 : 68    | 302 : 08             | 560 : B0    |

| 003 :          | 48         | 103 : 68    | 304 : 06             | 570 : 88    |

| 004 :          | 46         | 104 : 66    | 305 : 07             | 600 : 12    |

| 005 :          | 47         | 105 : 67    | 310 : 08             | 601 : 13    |

| 006 :          | 40         | 106 : 60    | 312 : 0A             | 602 : 18    |

| 007 :          | 4A         | 107 : 6A    | 320 : 60             | 603 : 18    |

| 010 :          | 40         | 110 : 60    | 321 : 61             | 604 : 16    |

| 011 :          | 41         | 112 : 68    | 324 : 64             | 605 : 17    |

| 012 :          | 48         | 120 : 20    | 325 : 65             | 610 : 18    |

| 013 :          | 48         | 121 : 21    | 330 : 68             | 612 : 1A    |

| 014 :          | 44         | 122 : 22    | 340 : 02             | 620 : C0    |

| 015 :          | 45         | 123 : 23    | 342 : 78             | 621 : C1    |

| 016 :          | 40         | 124 : 24    | 350 : 00             | 624 : C4    |

| 017 :          | 42         | 125 : 25    | 352 : 04             | 625 : C5    |

| 020 :          | 00         | 126 : 26    | 360 : 70             | 630 : C8    |

|                |            |             |                      |             |

| 021 :          | 01         | 127 : 27    |                      |             |

| 022 :          | 02         | 130 : 28    | 400 : C2             | 642 : D8    |

| 023 :          | 03         | 140 : 22    | 401 : C3             | 650 : 10    |

| 024 :          | 04         | 142 : 38    | 402 : C8             | 652 : 18    |

| 025 :          | 05         | 150 : 20    | 403 : C8             | 660 : D0    |

| 026 :          | 06         | 152 : 28    | 404 : C6             | 670 : D8    |

| 027 :          | 07         | 160 : 30    | 405 : C7             | 700 : 52    |

| 030 :          | 08         | 170 : 38    | 406 : C0             | 701 : 53    |

| 031 :          | 09         | 200 : 12    | 407 : CA             | 702 : 58    |

| 032 :          | 0A         | 201 : 13    | 410 : C0             | 704 : 56    |

| 033 :          | 0B         | 202 : 18    | 412 : C8             | 705 : 57    |

| 034 :          | OC_        | 203 : 18    | 420 : 80             | 710 : 58    |

| 035 :          | 0 <b>D</b> | 204 : 16    | 421 : 81             | 712 : 5A    |

| 036 :          | 0E         | 205 : 17    | 422 : 82             | 720 : E0    |

| 037 :          | 0F         | 206 : 10    | 423 : 83             | 721 : E1    |

| 040 :          | 02         | 207 : 1A    | 424 : 84             | 724 : E4    |

| 041 :          | 03         | 210 : 18    | 425 : 85             | 725 : E5    |

| 042 :          | 18         | 211 : 19    | 426 : 86             | 730 : E8    |

| 043 :          | 18         | 212 : 1A    | 427 : 87             | 740 : 42    |

| 044            | 06         | 213 : 1B    | 430 : 88             | 742 : F8    |

| 045 :          | 07         | 214 : 1C    | 440 : 82             | 750 : 40    |

| 046            | 10         | 215 : 1D    | 442 : 98             | 752 : 48    |

|                |            |             |                      |             |

| 047            | 1A         | 216 : 1E    | 450 : 80             | 760 : F0    |

Table 4 Unused and Invalid 9-bit Word (octal) to 8-bit Word (hex)

#### Parallel-to-Serial and Serial-to-Parallel converters

One of the main features of the digital back end is the conversion of 8-bit parallel NRZ data into a high speed serial bit stream, and the conversion of high speed serial data back to 8-bit parallel NRZ data. In write operations a 9-bit word is loaded in parallel onto the high speed serial write data bit stream every ninth channel clock cycle (every eighth in direct test) and then shifted out to the analog front end. And in read operations nine bits of the high speed read data bit stream are captured in parallel every ninth channel clock cycle (every eighth in direct test) and then passed toward the NRZ pins.

The coordination of these transfers is timing critical. In write operations, the transfer takes place as a parallel load of a serial shift register for a single channel clock cycle during the second half of the internal NRZ write clock period. This allows the parallel data plenty of time to have settled prior to its parallel loading into the serial shift register of the high speed write data bit stream.

In read operations, the transfer only takes place following a successful SYNC Byte word detection so that the RCLK will have been synchronized with the user data word boundaries. Once synchronization of the clock has been achieved, the user data is captured in 9-bit segments once every ninth cycle and made available to the decoder, descrambler, and NRZ output pins. In direct test the user data is captured in 8-bit segments once every eighth cycle and bypasses the decoder and descrambler on its way to the NRZ output pins.

### SYNC Byte Detector, programmable

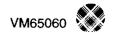

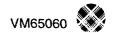

Detection of a SYNC Byte word in read mode is used to set the framing of the user data field into user data words that can then be passed on to the disk controller. The VCO Sync field, which precedes the SYNC Byte words, is searched at the beginning of read mode by the SYNC Byte detector circuitry. It is looking for either of the two SYNC Byte words to come along in the serial data stream so that the proper data word framing, or boundaries, can be determined and set.

In normal operation, the SYNC Byte words are two 9-bit words separated by a 9-bit spacer word, while in direct test operation they are the combination of 8-bit SYNC Byte words and the last bit of the VCO Sync Field, '1', for SB1 and the last bit of the 8-bit spacer word, '0', for SB2. In order to detect the SYNC Byte words, the detector circuitry must be informed for which pattern to search. The 9-bit SYNC Byte pattern for which to search is stored in the control register. This pattern is for the second SYNC Byte word, SB2, while the pattern for SB1 is the bit by bit inverse of SB2.

The SYNC Byte detector circuitry consists of a bank of nine XNOR/XOR gates. Each gate interrogates a single bit of the serial bit stream, resulting in a string of nine bits being checked in parallel. Each bit is checked with respect to the corresponding bit stored in the control register. If all nine serial stream bits mismatch their corresponding stored pattern, XNOR's  $\Rightarrow$  1, and SB1 is said to be found. If all nine bits are matched, XOR's  $\Rightarrow$  0, and SB2 is said to be found.

Upon detecting either SB1 or SB2 in the serial bit stream, a synchronization signal is passed on to the channel clock divider circuitry so that the divided clock can be adjusted for framing the user data word boundaries. Also, a blocking signal is set that stops the detector circuitry from continuing to search for and detecting subsequent patterns that also match the SYNC Byte patterns. In addition, a SYNC Byte Flag is set and eventually driven out on the SBF pin.

If the SYNC Byte detector circuitry fails to detect either SYNC Byte pattern as it passes through in the serial data stream, possibly due to a corrupted bit stream, the search is allowed to continue until the end of the read mode during which a possible false detection of user data patterns as the SYNC Byte words might occur. Acknowledging the failure to detect the SYNC Byte during the proper portion of the Read Mode is left up to the Controller chip.

The user has the option of requiring patterns SB1 and SB2 to *both* be detected prior to the passing of user data words on to the disk controller. In this way the user can configure tighter error tolerances during the SYNC Byte zone by requiring that both SYNC Bytes must be error free, rather than just one.

As there is a relationship between SB1 and SB2, they must be coordinated when chosen and written. Two tables have been include here to aid in determining pairs of SYNC Bytes.

Table 5 lists the 110 possible SYNC Byte pairs that can be used in 8/9 encoded normal modes. These all have SB1 and SB2 that are the bit-by-bit inverses of each other. SB1's that have NRZ[8:5]= 0 are excluded from this list as they would not be detected properly by the non-zero detector in the write path.

| SB1      |     |           | SB         | 2   | . " |

|----------|-----|-----------|------------|-----|-----|

| Hex      | Oct | Binary    | Binary     | Oct | Hex |

| 13       | 641 | 110100001 | 001011110  | 136 | 2E  |

| 16       | 644 | 110100100 | 001011011  | 133 | 2B  |

| 17       | 645 | 110100101 | 001011010  | 132 | 2A  |

| 19       | 611 | 110001001 | 001110110  | 166 | 36  |

| 1B       | 613 | 110001011 | 001110100  | 164 | 34  |

| 1C       | 614 | 110001100 | 001110011  | 163 | 33  |

| 1D       | 615 | 110001101 | 001110010  | 162 | 32  |

| 1E       | 616 | 110001110 | 001110001  | 161 | 31  |

| 21       | 151 | 001101001 | 110010110  | 626 | C6  |

| 23       | 141 | 001100001 | 1100111110 | 636 | CE  |

| 24       | 154 | 001101100 | 110010011  | 623 | C3  |

| 25       | 155 | 001101100 | 110010010  | 622 | C2  |

| 26       | 144 | 001101101 | 110010010  | 633 | CB  |

| 27       | 145 | 001100100 | 110011010  | 632 | CA  |

| 29       | 131 | 001100101 | 110100110  | 646 | DO  |

| 29<br>2A | 132 | 001011001 | 110100110  | 645 | 17  |

| 2B       | 132 |           | 110100101  | 644 | 16  |

| 2B       | 133 | 001011011 | 110100100  | 643 | D8  |

| 2E       |     | 001011100 | 110100011  | 641 | 13  |

|          | 136 |           | 110010001  | 631 | C9  |

| 30       | 146 | 001100110 |            |     |     |

| 31       | 161 | 001110001 | 110001110  | 616 | 1E  |

| 32       | 162 | 001110010 | 110001101  | 615 | 1D_ |

| 33       | 163 | 001110011 | 110001100  | 614 | 1C  |

| 34       | 164 | 001110100 | 110001011  | 613 | 18  |

| 36       | 166 | 001110110 | 110001001  | 611 | 19  |

| 38       | 143 | 001100011 | 110011100  | 634 | CC  |

| 42       | 222 | 010010010 | 101101101  | 555 | A5  |

| 43       | 223 | 010010011 | 101101100  | 554 | A4  |

| 46       | 226 | 010010110 | 101101001  | 551 | A1  |

| 49       | 231 | 010011001 | 101100110  | 546 | B0  |

| 4A       | 232 | 010011010 | 101100101  | 545 | A7  |

| 4B       | 233 | 010011011 | 101100100  | 544 | A6  |

| 4C       | 234 | 010011100 | 101100011  | 543 | 88  |

| 4E       | 236 | 010011110 | 101100001  | 541 | A3  |

| 51       | 261 | 010110001 | 101001110  | 516 | E0  |

| 52       | 262 | 010110010 | 101001101  | 515 | E5  |

| 53       | 263 | 010110011 | 101001100  | 514 | E4  |

| 54       | 264 | 010110100 | 101001011  | 513 | E8  |

| 56       | 266 | 010110110 | 101001001  | 511 | E1  |

| 60       | 116 | 001001110 | 110110001  | 661 | D1  |

| 61       | 111 | 001001001 | 110110110  | 666 | D6  |

| 62       | 322 | 011010010 | 100101101  | 455 | 85  |

| 63       | 323 | 011010011 | 100101100  | 454 | 84  |

| 64       | 114 | 001001100 | 110110011  | 663 | D3  |

| 65       | 115 | 001001101 | 110110010  | 662 | D2  |

| 66       | 326 | 011010110 | 100101001  | 451 | 81  |

| 68       | 113 | 001001011 | 110110100  | 664 | D4  |

| 69       | 331 | 011011001 | 100100110  | 446 | 90  |

| 6A       | 332 | 011011010 | 100100101  | 445 | 87  |

| 6B       | 333 | 011011011 | 100100100  | 444 | 86  |

| 6C       | 334 | 011011100 | 100100011  | 443 | 98  |

| 6E       | 336 | 011011110 | 100100001  | 441 | 83  |

| 70       | 346 | 011100110 | 100011001  | 431 | 89  |

| 71       | 361 | 011110001 | 100001110  | 416 | C0  |

| 72       | 362 | 011110010 | 100001101  | 415 | C5  |

| 1 4. | s   | B1        | SB        | 2   |       |

|------|-----|-----------|-----------|-----|-------|

| Hex  | Oct | Binary    | Binary    | Oct | Hex   |

| 73   | 363 | 011110011 | 100001100 | 414 | C4    |

| 74   | 364 | 011110100 | 100001011 | 413 | C8    |

| 76   | 366 | 011110110 | 100001001 | 411 | C1    |

| 78   | 343 | 011100011 | 100011100 | 434 | BC BC |

| 81   | 451 | 100101001 | 011010110 | 326 | 66    |

| 83   | 441 | 100100001 | 011011110 | 336 | 6E    |

| 84   | 454 | 100101100 | 011010011 | 323 | 63    |

| 85   | 455 | 100101101 | 011010010 | 322 | 62    |

| 86   | 444 | 100100100 | 011011011 | 333 | 6B    |

| 87   | 445 | 100100101 | 011011010 | 332 | 6A    |

| 89   | 431 | 100011001 | 011100110 | 346 | 70    |

| 8A   | 432 | 100011010 | 011100101 | 345 | 07    |

| 8B   | 433 | 100011011 | 011100100 | 344 | 06    |

| 8C   | 434 | 100011100 | 011100011 | 343 | 78    |

| 8E   | 436 | 100011110 | 011100001 | 341 | 03    |

| 90   | 446 | 100100110 | 011011001 | 331 | 69    |

| 91   | 461 | 100110001 | 011001110 | 316 | 0E    |

| 92   | 462 | 100110010 | 011001101 | 315 | 0D    |

| 93   | 463 | 100110011 | 011001100 | 314 | OC.   |

| 94   | 464 | 100110100 | 011001011 | 313 | 0B    |

| 96   | 466 | 100110110 | 011001001 | 311 | 09    |

| 98   | 443 | 100100011 | 011011100 | 334 | 6C    |

| A1   | 551 | 101101001 | 010010110 | 226 | 46    |

| A3   | 541 | 101100001 | 010011110 | 236 | 4E    |

| A4   | 554 | 101101100 | 010010011 | 223 | 43    |

| A5   | 555 | 101101101 | 010010011 | 222 | 42    |

| A6   | 544 | 101100100 | 010010010 | 233 | 4B    |

| A7   | 545 | 101100101 | 010011010 | 232 | 4A    |

| B0   | 546 | 101100110 | 010011001 | 231 | 49    |

| B8   | 543 | 101100011 | 010011100 | 234 | 4C    |

| CO   | 416 | 100001110 | 011110001 | 361 | 71    |

| C1   | 411 | 100001001 | 011110110 | 366 | 76    |

| C2   | 622 | 110010010 | 001101101 | 155 | 25    |

| C3   | 623 | 110010011 | 001101100 | 154 | 24    |

| C4   | 414 | 100001100 | 011110011 | 363 | 73    |

| C5   | 415 | 100001101 | 011110010 | 362 | 72    |

| C6   | 626 | 110010110 | 001101001 | 151 | 21    |

| C8   | 413 | 100001011 | 011110100 | 364 | 74    |

| C9   | 631 | 110011001 | 001100110 | 146 | 30    |

| CA   | 632 | 110011010 | 001100101 | 145 | 27    |

| СВ   | 633 | 110011011 | 001100100 | 144 | 26    |

| CC   | 634 | 110011100 | 001100011 | 143 | 38    |

| CE   | 636 | 110011110 | 001100001 | 141 | 23    |

| DO   | 646 | 110100110 | 001011001 | 131 | 29    |

| D1   | 661 | 110110001 | 001001110 | 116 | 60    |

| D2   | 662 | 110110010 | 001001101 | 115 | 65    |

| D3   | 663 | 110110011 | 001001100 | 114 | 64    |

| D4   | 664 | 110110100 | 001001011 | 113 | 68    |

| D6   | 666 | 110110110 | 001001001 | 111 | 61    |

| D8   | 643 | 110100011 | 001011100 | 134 | 2C    |

| EO   | 516 | 101001110 | 010110001 | 261 | 51    |

| E1   | 511 | 101001001 | 010110110 | 266 | 56    |

| E4   | 514 | 101001100 | 010110011 | 263 | 53    |

| E5   | 515 | 101001101 | 010110010 | 262 | 52    |

| E8   | 513 | 101001011 | 010110100 | 264 | 54    |

|      |     |           | , 3.000   |     | •     |

Table 5 SYNC Byte Pairs for 8/9 (0, 4, 4) Normal

Table 6 shows the 239 possible SYNC Byte pairs that can be used in 8/8 nonencoded direct test modes.

|               | SB1         | SB2          |     |

|---------------|-------------|--------------|-----|

| Hex           | Binary      | Binary       | Hex |

| 90            | (1)00000000 | (0)11111111  | FF  |

| 01            | (1)00000001 | (0)11111110  | FE  |

| 02            | (1)00000010 | (0)11111101  | FÐ  |

| 93            | (1)00000011 | (0)11111100  | FC  |

| 04            | (1)00000100 | (0)11111011  | FB  |

| 06            | (1)00000101 | (0)111111010 | FA  |

| 96            | (1)00000110 | (0)11111001  | F9  |

| 97            | (1)00000111 | (0)11111000  | F8  |

| 98            | (1)00001000 | (0)11110111  | F7  |

| 99            | (1)00001001 | (0)11110110  | F6  |

| 0A            | (1)00001010 | (0)11110101  | F5  |

| 98            | (1)00001011 | (0)11110100  | F4  |

| <del>9C</del> | (1)00001100 | (0)11110011  | F3  |

| <del>9D</del> | (1)00001101 | (0)11110010  | F2  |

| 0€            | (1)00001110 | (0)11110001  | F-1 |

| 0F            | (1)00001111 | (0)11110000  | F0  |

| 10            | (1)00010000 | (0)11101111  | €F  |

| 11            | (1)00010001 | (0)11101110  | EE  |

| 12            | (1)00010010 | (0)11101101  | ED  |

| 13            | (1)00010011 | (0)11101100  | EC  |

| 14            | (1)00010100 | (0)11101011  | EB  |

| 15            | (1)00010101 | (0)11101010  | EA  |

| 16            | (1)00010110 | (0)11101001  | E9  |

| 17            | (1)00010111 | (0)11101000  | E8  |

| 18            | (1)00011000 | (0)11100111  | E7  |

| 19            | (1)00011001 | (0)11100110  | E6  |

| 1A            | (1)00011010 | (0)11100101  | E5  |

| 18            | (1)00011011 | (0)11100100  | E4  |

| 1C            | (1)00011100 | (0)11100011  | E3  |

| 1D            | (1)00011101 | (0)11100010  | E2  |

| 1E            | (1)00011110 | (0)11100001  | E1  |

| 1F            | (1)00011111 | (0)11100000  | E0  |

| 20            | (1)00100000 | (0)11011111  | DF  |

| 21            | (1)00100001 | (0)11011110  | DE  |

| :             | :           | :            | _ : |

| :             | :           | : <u></u>    | :   |

| :             | ::          | <del> </del> | :   |