## **General Description**

The MAX24287 is a flexible, low-cost Ethernet interface conversion IC. The parallel interface can be configured for GMII, RGMII, TBI, RTBI, or 10/100 MII, while the serial interface can be configured for 1.25Gbps SGMII or 1000BASE-X operation. In SGMII mode, the device interfaces directly to Ethernet switch ICs, ASIC MACs, and 1000BASE-T electrical SFP modules. In 1000BASE-X mode, the device interfaces directly to 1Gbps 1000BASE-X SFP optical modules. The MAX24287 performs automatic translation of link speed and duplex autonegotiation between parallel MII MDIO and the serial interface.

This device is ideal for interfacing single-channel GMII/MII devices such as microprocessors, FPGAs, network processors, Ethernet-over-SONET or -PDH mappers, and TDM-over-packet circuit emulation devices. The device also provides a convenient solution to interface such devices with electrical or optical Ethernet SFP modules.

# **Applications**

Any System with a Need to Interface a Component with a Parallel MII Interface (GMII, RGMII, TBI RTBI, 10/100 MII) to a Component with an SGMII or 1000BASE-X Interface

Switches and Routers Telecom Equipment

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE                |

|---------------|----------------|----------------------------|

| MAX24287ETK2  | -40°C to +85°C | 68 TQFN-EP*<br>trays       |

| MAX24287ETK2T | -40°C to +85°C | 68 TQFN-EP*<br>tape & reel |

2 in suffix denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

Block Diagram appears on page 7.

Register Map appears on page 42.

### **Highlighted Features**

- Bidirectional Wire-Speed Ethernet Interface Conversion

- Can Interface Directly to SFP Modules and SGMII PHY and Switch ICs

- ◆ Serial Interface Configurable as 1000BASE-X or SGMII Revision 1.8 (4-, 6-, or 8-Pin)

- Parallel Interface Configurable as GMII, RGMII, TBI, RTBI, or 10/100 MII

- Serial Interface Has Clock and Data Recovery Block (CDR) and Does Not Require a Clock Input

- Translates Link Speed and Duplex Mode Negotiation Between MDIO and SGMII PCS

- ♦ Supports 10/100 MII or RGMII Operation with SGMII Running at the Same Rate

- Configurable for 10/100 MII DTE or DCE Modes (i.e., Connects to PHY or MAC)

- ◆ Can Also Be Configured as General-Purpose

1:10 SerDes with Optional Comma Alignment

- Supports Synchronous Ethernet by Providing a 25MHz or 125MHz Recovered Clock and Accepting a Transmit Clock

- Can Provide a 125MHz Clock for the MAC to Use as GTXCLK

- ◆ Accepts 10MHz, 12.8MHz, 25MHz or 125MHz Reference Clock

- ♦ Software Control Through MDIO Interface

- GPIO Pins Can Be Configured as Clocks, Status Signals and Interrupt Outputs

- ♦ 1.2V Operation with 3.3V I/O

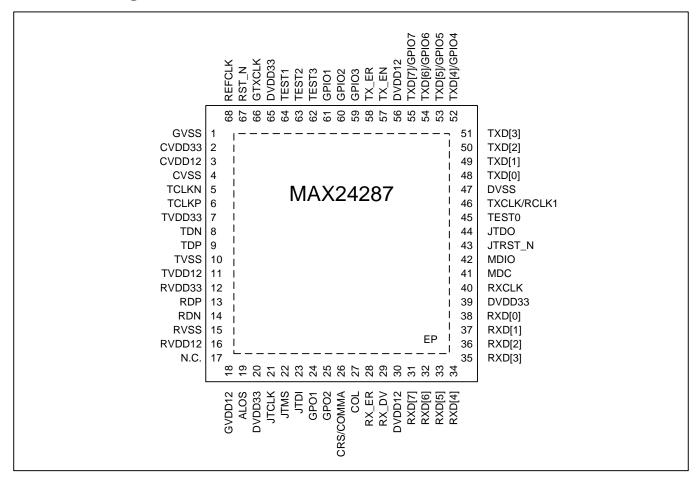

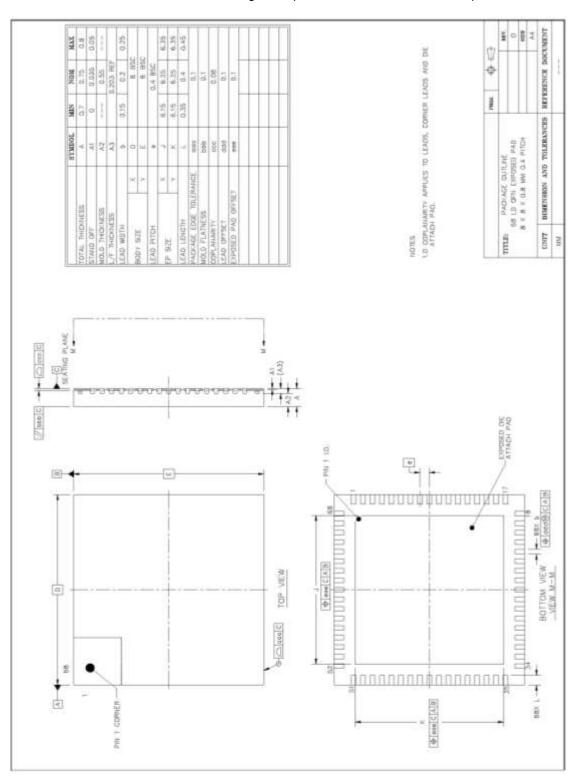

- ♦ Small, 8mm x 8mm, 68-Pin TQFN Package

# Table of Contents

| I. APPLICATION EXAMPLES                                               | 6  |

|-----------------------------------------------------------------------|----|

| 2. BLOCK DIAGRAM                                                      | 7  |

| 3. DETAILED FEATURES                                                  | 7  |

| 4. ACRONYMS, ABBREVIATIONS, AND GLOSSARY                              | 8  |

| 5. PIN DESCRIPTIONS                                                   | 8  |

| 5. FUNCTIONAL DESCRIPTION                                             | 17 |

| 6.1 PIN CONFIGURATION DURING RESET                                    | 17 |

| 6.2 GENERAL-PURPOSE I/O                                               |    |

| 6.2.1 Receive Recovered Clock Squelch Criteria                        |    |

| 6.3 RESET AND PROCESSOR INTERRUPT                                     |    |

| 6.3.1 Reset                                                           |    |

| 6.3.2 Processor Interrupts                                            |    |

| 6.4 MDIO INTERFACE                                                    | 20 |

| 6.4.1 MDIO Overview                                                   |    |

| 6.4.2 Examples of MAX24287 and PHY Management Using MDIO              |    |

| 6.5 SERIAL INTERFACE – 1000BASE-X OR SGMII                            |    |

| 6.6 PARALLEL INTERFACE – GMII, RGMII, TBI, RTBI, MII                  |    |

| 6.6.1 GMII Mode                                                       |    |

| 6.6.2 TBI Mode                                                        |    |

| 6.6.3 RGMII Mode                                                      |    |

| 6.6.4 RTBI Mode                                                       |    |

| 6.7 AUTO-NEGOTIATION (AN)                                             |    |

| 6.7.1 1000BASE-X Auto-Negotiation                                     |    |

| 6.7.2 SGMII Control Information Transfer                              |    |

| 6.8 DATA PATHS                                                        |    |

| 6.8.1 GMII, RGMII and MII Serial to Parallel Conversion and Decoding. |    |

| 6.8.2 GMII, RGMII and MII Parallel to Serial Conversion and Encoding. |    |

| 6.8.3 TBI, RTBI Serial to Parallel Conversion and Decoding            |    |

| 6.8.4 TBI Parallel to Serial Conversion and Encoding                  |    |

| 6.8.5 Rate Adaption Buffers, Jumbo Packets and Clock Frequency Diffe  |    |

| 6.9 TIMING PATHS                                                      |    |

| 6.9.1 RX PLL                                                          |    |

| 6.9.2 TX PLL                                                          |    |

| 6.9.3 Input Jitter Tolerance                                          |    |

| 6.9.4 Output Jitter Generation                                        |    |

| 6.9.6 GPIO Pins as Clock Outputs                                      |    |

| 6.10 LOOPBACKS                                                        |    |

| 6.10.1 Diagnostic Loopback                                            |    |

| 6.10.2 Terminal Loopback                                              |    |

| 6.10.3 Remote Loopback                                                |    |

| 6.11 DIAGNOSTIC AND TEST FUNCTIONS                                    |    |

| 6.12 DATA PATH LATENCIES                                              |    |

| 6.13 POWER SUPPLY CONSIDERATIONS                                      |    |

| 6.14 STARTUP PROCEDURE                                                |    |

| 7. REGISTER DESCRIPTIONS                                              |    |

|                                                                       |    |

| 7.1 REGISTER MAP                                                      | 42 |

| 7.2 | 2 REG  | SISTER DESCRIPTIONS                                    | 42        |

|-----|--------|--------------------------------------------------------|-----------|

|     | 7.2.1  | BMCR                                                   | 43        |

| -   | 7.2.2  | BMSR                                                   | 44        |

| -   | 7.2.3  | ID1 and ID2                                            | 45        |

| -   | 7.2.4  | AN_ADV                                                 | 46        |

|     | 7.2.5  | AN_RX                                                  | 46        |

| 7   | 7.2.6  | AN_EXP                                                 | 46        |

| 7   | 7.2.7  | EXT_STAT                                               | 47        |

|     | 7.2.8  | JIT_DIAG                                               |           |

|     | 7.2.9  | PCSCR                                                  |           |

|     | 7.2.10 | GMICR                                                  |           |

| 7   | 7.2.11 | CR                                                     |           |

|     | 7.2.12 | IR                                                     |           |

|     | 7.2.13 | PAGESEL                                                |           |

|     | 7.2.14 | ID                                                     |           |

| _   | 7.2.15 | GPIOCR1                                                |           |

|     | 7.2.16 | GPIOCR2                                                |           |

| _   | 7.2.17 | GPIOSR                                                 |           |

|     | 7.2.18 | PTPCR1                                                 | 55        |

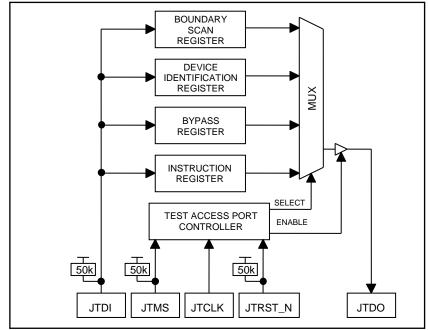

| 8.  | JTAG   | AND BOUNDARY SCAN                                      | <b>56</b> |

| 8.1 | I JTA  | G DESCRIPTION                                          | 56        |

| 8.2 |        | G TAP CONTROLLER STATE MACHINE DESCRIPTION             |           |

| 8.3 |        | G INSTRUCTION REGISTER AND INSTRUCTIONS                |           |

| 8.4 |        | G Test Registers                                       |           |

| _   |        |                                                        |           |

| 9.  | ELEC   | TRICAL CHARACTERISTICS                                 | 60        |

| 9.1 | l Red  | COMMENDED OPERATING CONDITIONS                         | 60        |

| 9.2 | 2 DC   | ELECTRICAL CHARACTERISTICS                             | 60        |

| 9   | 9.2.1  | CMOS/TTL DC Characteristics                            |           |

|     | 9.2.2  | SGMII/1000BASE-X DC Characteristics                    |           |

| 9.3 | AC     | ELECTRICAL CHARACTERISTICS                             |           |

| 9   | 9.3.1  | REFCLK AC Characteristics                              |           |

|     | 9.3.2  | SGMII/1000BASE-X Interface Receive AC Characteristics  |           |

|     | 9.3.3  | SGMII/1000BASE-X Interface Transmit AC Characteristics |           |

| 9   | 9.3.4  | Parallel Interface Receive AC Characteristics          |           |

| 9   | 9.3.5  | Parallel Interface Transmit AC Characteristics         | 65        |

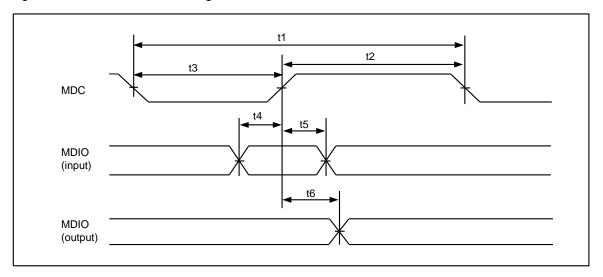

| 9   | 9.3.6  | MDIO Interface AC Characteristics                      | 67        |

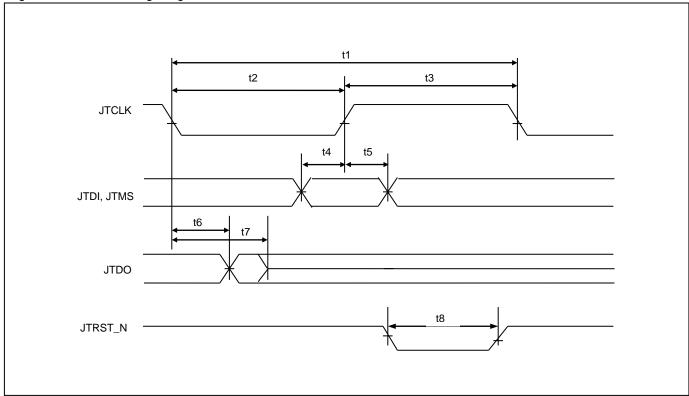

| 9   | 9.3.7  | JTAG Interface AC Characteristics                      | <i>68</i> |

| 10. | PIN A  | SSIGNMENTS                                             | 69        |

| 11. | DACL   | (AGE AND THERMAL INFORMATION                           | 70        |

| 11. | FACE   | MAGE AND THERWAL INFORMATION                           | 10        |

| 12  | DATA   | CHEET DEVISION LISTODY                                 | 74        |

# List of Figures

| Figure 2-1. Block Diagram                                                       | 7  |

|---------------------------------------------------------------------------------|----|

| Figure 6-1. MDIO Slave State Machine                                            |    |

| Figure 6-2. Management Information Flow Options, Case 1,Tri-Mode PHY            | 22 |

| Figure 6-3. Management Information Flow Options, Case 2, SGMII Switch Chip      |    |

| Figure 6-4. Management Information Flow Options, Case 3, 1000BASE-X Interface   |    |

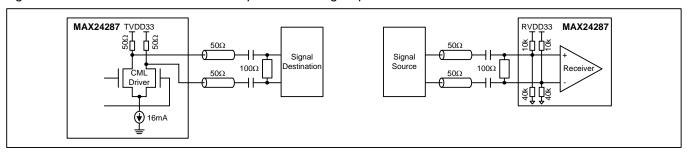

| Figure 6-5. Recommended External Components for High-Speed Serial Interface     |    |

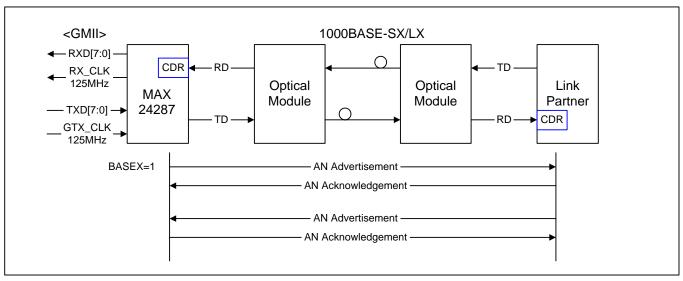

| Figure 6-6. Auto-Negotiation with a Link Partner over 1000BASE-X                |    |

| Figure 6-7. 1000BASE-X Auto-Negotiation tx_Config_Reg and rx_Config_Reg Fields  |    |

| Figure 6-8. SGMII Control Information Generation, Reception and Acknowledgement |    |

| Figure 6-9. SGMII tx_Config_Reg and rx_Config_Reg Fields                        |    |

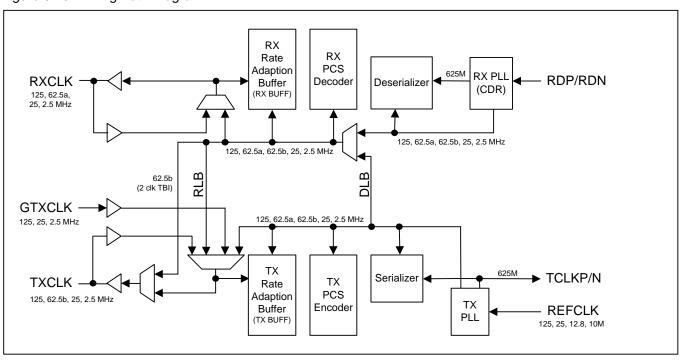

| Figure 6-10. Timing Path Diagram                                                |    |

| Figure 8-1. JTAG Block Diagram                                                  |    |

| Figure 8-2. JTAG TAP Controller State Machine                                   |    |

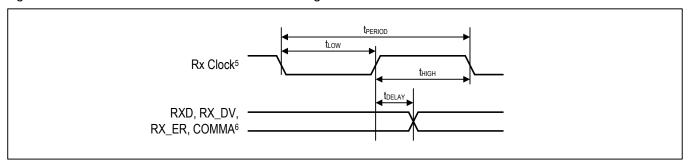

| Figure 9-1. MII/GMII/RGMII/TBI/RTBI Receive Timing Waveforms                    |    |

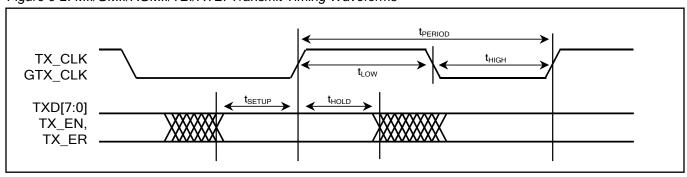

| Figure 9-2. MII/GMII/RGMII/TBI/RTBI Transmit Timing Waveforms                   |    |

| Figure 9-3. MDIO Interface Timing                                               |    |

| Figure 9-4. JTAG Timing Diagram                                                 |    |

|                                                                                 |    |

# List of Tables

| Table 5-1. Pin Type Definitions                                                        | 8  |

|----------------------------------------------------------------------------------------|----|

| Table 5-2. Detailed Pin Descriptions – Global Pins (2 Pins)                            |    |

| Table 5-3. Detailed Pin Descriptions – MDIO Interface (2 Pins)                         | 9  |

| Table 5-4. Detailed Pin Descriptions – JTAG Interface (5 pins)                         | 9  |

| Table 5-5. Detailed Pin Descriptions – GPIO signals (5 dedicated pins, 4 shared pins)  | 9  |

| Table 5-6. Detailed Pin Descriptions – SGMII/1000BASE-X Serial Interface (7 pins)      |    |

| Table 5-7. Detailed Pin Descriptions – Parallel Interface (25 pins)                    |    |

| Table 5-8. Detailed Pin Descriptions – Power and Ground Pins (17 pins)                 | 16 |

| Table 6-1. Reset Configuration Pins, 15-Pin Mode (COL=0)                               | 17 |

| Table 6-2. Parallel Interface Configuration                                            |    |

| Table 6-3. Reset Configuration Pins, 3-Pin Mode (COL=1)                                |    |

| Table 6-4. GPO1, GPIO1 and GPIO3 Configuration Options                                 |    |

| Table 6-5. GPO2 and GPIO2 Configuration Options                                        |    |

| Table 6-6. GPIO4, GPIO5, GPIO6 and GPIO7 Configuration Options                         |    |

| Table 6-7. Parallel Interface Modes                                                    |    |

| Table 6-8. GMII Parallel Bus Pin Naming                                                |    |

| Table 6-9. TBI Parallel Bus Pin Naming (Normal Mode)                                   |    |

| Table 6-10. TBI Parallel Bus Pin Naming (One-Clock Mode)                               |    |

| Table 6-11. RGMII Parallel Bus Pin Naming                                              |    |

| Table 6-12. RTBI Parallel Bus Pin Naming                                               |    |

| Table 6-13. MII Parallel Bus Pin Naming                                                |    |

| Table 6-14. AN_ADV 1000BASE-X Auto-Negotiation Ability Advertisement Register (MDIO 4) |    |

| Table 6-15. AN_RX 1000BASE-X Auto-negotiation Ability Receive Register (MDIO 5)        |    |

| Table 6-15. AN_AX 1000BASE-X Adio-negotiation Ability Receive Register (MDIO 3)        |    |

| Table 6-17. AN_RX SGMII Configuration Information Receive Register (MDIO 5)            |    |

| Table 6-17. AN_RX SGMI Configuration information Receive Register (MDIO 5)             |    |

| Table 6-19. Timing Path Muxes – No Loopback                                            |    |

|                                                                                        |    |

| Table 6-20. Timing Path Muxes – RLB Loopback                                           |    |

| Table 6-21. GMII Data Path Latencies                                                   |    |

| Table 7-1. Register Map                                                                |    |

| Table 8-1. JTAG Instruction Codes                                                      |    |

| Table 8-2. JTAG ID Code                                                                |    |

| Table 9-1. Recommended DC Operating Conditions                                         |    |

| Table 9-2. DC Characteristics                                                          |    |

| Table 9-3. DC Characteristics for Parallel and MDIO Interfaces                         |    |

| Table 9-4. SGMII/1000BASE-X Transmit DC Characteristics                                |    |

| Table 9-5. SGMII/1000BASE-X Receive DC Characteristics                                 |    |

| Table 9-6. REFCLK AC Characteristics                                                   |    |

| Table 9-7. 1000BASE-X and SGMII Receive AC Characteristics                             |    |

| Table 9-8. 1000BASE-X and SGMII Receive Jitter Tolerance                               |    |

| Table 9-9. SGMII and 1000BASE-X Transmit AC Characteristics                            |    |

| Table 9-10. 1000BASE-X Transmit Jitter Characteristics                                 |    |

| Table 9-11. GMII and TBI Receive AC Characteristics                                    |    |

| Table 9-12. RGMII-1000 and RTBI Receive AC Characteristics                             |    |

| Table 9-13. RGMII-10/100 Receive AC Characteristics                                    |    |

| Table 9-14. MII–DCE Receive AC Characteristics                                         |    |

| Table 9-15. MII–DTE Receive AC Characteristics                                         |    |

| Table 9-16. GMII, TBI, RGMII-1000 and RTBI Transmit AC Characteristics                 |    |

| Table 9-17. RGMII-10/100 Transmit AC Characteristics                                   |    |

| Table 9-18. MII–DCE Transmit AC Characteristics                                        |    |

| Table 9-19. MII–DTE Transmit AC Characteristics                                        |    |

| Table 9-20. MDIO Interface AC Characteristics                                          |    |

| Table 9-21. JTAG Interface Timing                                                      |    |

| Table 11-1 Package Thermal Properties Natural Convection                               | 71 |

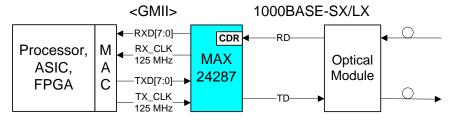

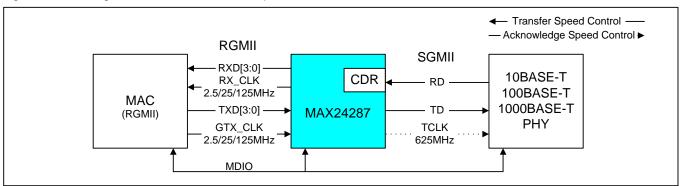

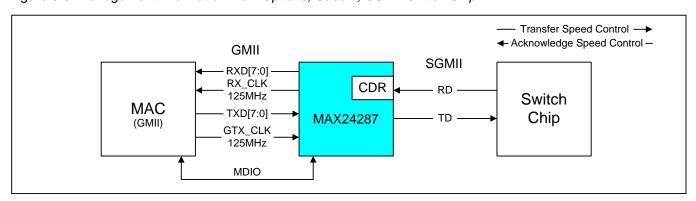

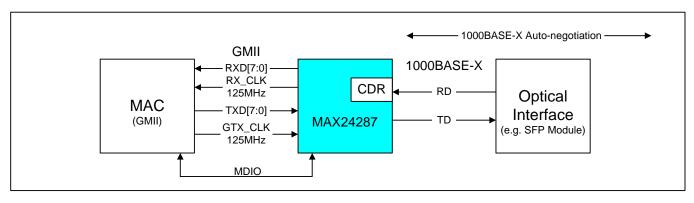

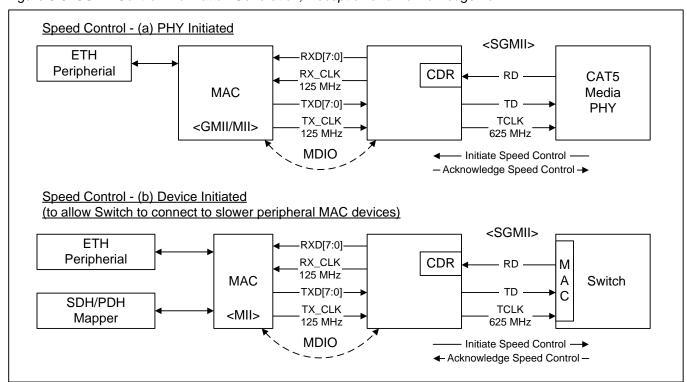

## 1. Application Examples

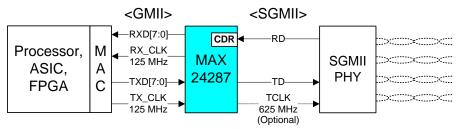

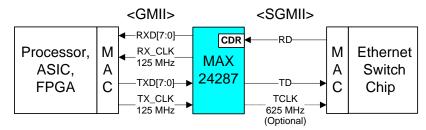

### a) Copper Media

### b) Connect Parallel MII Component to SGMII Component

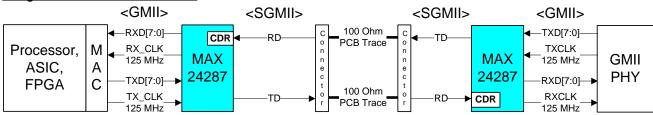

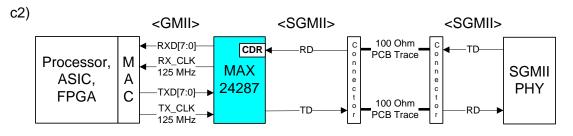

### c1) Long PCB Trace Card-to-Card

#### d) Fiber Module

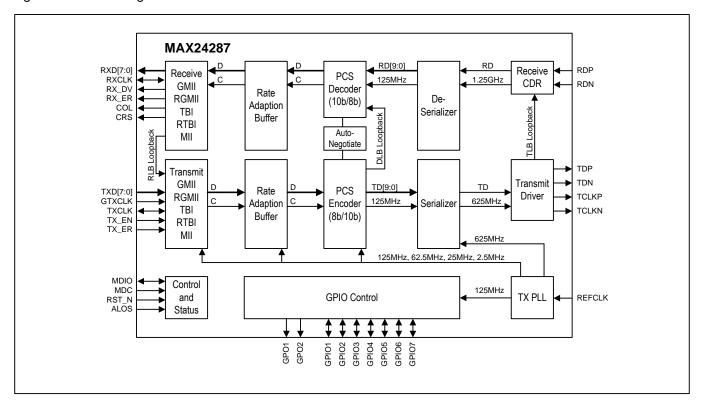

### 2. Block Diagram

Figure 2-1. Block Diagram

### 3. Detailed Features

#### **General Features**

- High-speed MDIO interface (12.5MHz slave only) with optional preamble suppression

- Operates from a 10, 12.8, 20, 25, or 125MHz reference clock

- Optional 125MHz output clock for MAC to use as GTXCLK

### Parallel-Serial MII Conversion Features

- Bidirectional wire-speed interface conversion

- Serial Interface: 1000BASE-X or SGMII revision 1.8 (4-, 6-, or 8-Pin)

- Parallel Interface: GMII, RGMII (10, 100 and 1000Mbps), TBI, RTBI or 10/100 MII (DTE or DCE)

- 8-pin source-clocked SGMII mode

- 4-pin 1000BASE-X SerDes mode to interface with optical modules

- Connects processors with parallel MII interfaces to 1000BASE-X SFP optical modules

- Connects processors with parallel MII interfaces to PHY or switch ICs with SGMII interfaces

- Interface conversion is transparent to MAC layer and higher layers

- Translates link speed and duplex mode between GMII/MII MDIO and SGMII PCS

- Configurable for 10/100 MII DTE or DCE Modes (i.e., connects to PHY or MAC)

### Synchronous Ethernet Features

- Receive path bit clock can be output on a GPIO pin to line-time the system from the Ethernet port

- Transmit path can be frequency-locked to a system clock signal connected to the REFCLK pin

# 4. Acronyms, Abbreviations, and Glossary

- DCE Data Communication Equipment

- DDR Dual Data Rate (data driven and latched on both clock edges)

- DTE Data Terminating Equipment

- PCB Printed Circuit Board

- PHY Physical. Refers to either a transceiver device or a protocol layer

- Ingress The serial (SGMII) to parallel (GMII) direction

Egress The parallel (GMII) to serial (SGMII) direction

Receive The serial (SGMII) to parallel (GMII) direction

Transmit The parallel (GMII) to serial (SGMII) direction

## 5. Pin Descriptions

Note that some pins have different pin names and functions under different configurations.

Table 5-1. Pin Type Definitions

| Туре  | Definition                           |  |  |

|-------|--------------------------------------|--|--|

| 1     | Input                                |  |  |

| Idiff | Input, differential                  |  |  |

| lpu   | Input, with pullup                   |  |  |

| lpd   | Input, with pulldown                 |  |  |

| Ю     | Bidirectional                        |  |  |

| IOr   | Bidirectional, sampled at reset      |  |  |

| lOz   | Bidirectional, can go high impedance |  |  |

| 0     | Output                               |  |  |

| Odiff | Output, differential (CML)           |  |  |

| Oz    | Output, can go high impedance        |  |  |

Table 5-2. Detailed Pin Descriptions – Global Pins (2 Pins)

| Pin Name | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                           |

|----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_N    | 67   | I    | Reset (active low, asynchronous) This signal resets all logic, state machines and registers in the device. Pin states are sampled and used to set the default values of several register fields as described in 6.1. RST_N should be held low for at least 100μs. See section 6.3.1.      |

| REFCLK   | 68   | I    | Reference Clock This signal is the reference clock for the device. The frequency can be 10MHz, 12.8MHz, 25MHz or 125MHz ± 100 ppm. At reset the frequency is specified using the RXD[3:2] pins (see section 6.1). The REFCLK signal is the input clock to the TX PLL. See section 6.9.    |

|          |      |      | Note: REFCLK frequency cannot be changed dynamically among the frequencies listed above. To change REFCLK frequency, (1) power down MAX24287, (2) change REFCLK frequency, then (3) power up MAX24287.  REFCLK is an analog input that is internally biased with a 10kΩ resistor to 1.2V. |

|          |      |      | This support AC-coupling if desired.                                                                                                                                                                                                                                                      |

| Pin Name | PIN# | Туре | Pin Description                          |

|----------|------|------|------------------------------------------|

| TEST0    | 45   | I    | Factory Test. Connect to DVDD33.         |

| TEST1    | 64   | I    | Factory Test. Connect to DVDD33 or DVSS. |

| TEST2    | 63   | Į    | Factory Test. Connect to DVDD33 or DVSS. |

| TEST3    | 62   | I/O  | Factory Test. Connect to DVDD33 or DVSS. |

Table 5-3. Detailed Pin Descriptions – MDIO Interface (2 Pins)

| Pin Name | PIN# | Туре | Pin Description                                                                  |

|----------|------|------|----------------------------------------------------------------------------------|

| MDC      | 41   | I    | MDIO Clock.                                                                      |

|          |      |      | MDC is the clock signal of the 2-wire MDIO interface. It can be any frequency up |

|          |      |      | to 12.5MHz. See section 6.4.                                                     |

| MDIO     | 42   | IOz  | MDIO Data.                                                                       |

|          |      |      | This is the bidirectional, half-duplex data signal of the MDIO interface. It is  |

|          |      |      | sampled and updated on positive edges of MDC. IEEE 802.3 requires a 2kΩ±5%       |

|          |      |      | pulldown resistor on this signal at the MAC. See section 6.4.                    |

Table 5-4. Detailed Pin Descriptions – JTAG Interface (5 pins)

| Pin Name | PIN# | Type | Pin Description                                                                    |

|----------|------|------|------------------------------------------------------------------------------------|

| JTRST_N  | 43   | I    | JTAG Test Reset (active low).                                                      |

|          |      |      | Asynchronously resets the test access port (TAP) controller. JTRST_N should be     |

|          |      |      | held low during device power-up. If not used, JTRST_N can be held low or high      |

|          |      |      | after power-up. See section 7.2.18.                                                |

| JTCLK    | 21   | I    | JTAG Test Clock.                                                                   |

|          |      |      | This clock signal can be any frequency up to 10MHz. JTDI and JTMS are              |

|          |      |      | sampled on the rising edge of JTCLK, and JTDO is updated on the falling edge       |

|          |      |      | of JTCLK. If not used, connect to DVDD33 or DVSS. See section 7.2.18.              |

| JTMS     | 22   | I    | JTAG Test Mode Select.                                                             |

|          |      |      | Sampled on the rising edge of JTCLK. Used to place the port into the various       |

|          |      |      | defined IEEE 1149.1 states. If not used, connect to DVDD33. See section            |

|          |      |      | 7.2.18.                                                                            |

| JTDI     | 23   | l    | JTAG Test Data Input.                                                              |

|          |      |      | Test instructions and data are clocked in on this pin on the rising edge of JTCLK. |

|          |      | _    | If not used, connect to DVDD33. See section 7.2.18.                                |

| JTDO     | 44   | Oz   | JTAG Test Data Output.                                                             |

|          |      |      | Test instructions and data are clocked out on this pin on the falling edge of      |

|          |      |      | JTCLK. If not used leave unconnected. See section 7.2.18.                          |

Table 5-5. Detailed Pin Descriptions – GPIO signals (5 dedicated pins, 4 shared pins)

| Pin Name | PIN# | Туре | Pin Description                                                                                                                                                                                                              |

|----------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPO1     | 24   | IOr  | General Purpose Output 1.  After reset, this pin can either be high impedance (TBI or RTBI mode) or an output that indicates link status, 0=link down, 1=link up.  The function can be changed after reset. See section 6.2. |

| GPO2     | 25   | IOr  | General Purpose Output 2.  After reset, this pin can either be high impedance (TBI or RTBI mode) or an output that indicates CRS (carrier sense).  The function can be changed after reset. See section 6.2.                 |

| Pin Name     | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                                       |

|--------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO1        | 61   | lOz  | General Purpose Input or Output 1.  After reset this pin can be either high impedance or generating a 125MHz clock signal.  GPO1=0 at reset: After reset, GPIO1 is high impedance.  GPO1=1 at reset: After reset, GPIO1 is 125MHz clock out The function can be changed after reset. See section 6.2. |

| GPIO2        | 60   | lOz  | General Purpose Input or Output 2.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                                                                                                                                 |

| GPIO3        | 59   | lOz  | General Purpose Input or Output 3. After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                                                                                                                                  |

| GPIO4/TXD[4] | 52   | lOz  | General Purpose Input or Output 4.  Available for use as a GPIO pin when the parallel interface is configured for MII, RGMII or RTBI modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                        |

| GPIO5/TXD[5] | 53   | lOz  | General Purpose Input or Output 5.  Available for use as a GPIO pin when the parallel interface is configured for MII, RGMII or RTBI modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                        |

| GPIO6/TXD[6] | 54   | lOz  | General Purpose Input or Output 6. Available for use as a GPIO pin when the parallel interface is configured for MII, RGMII or RTBI modes. After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                          |

| GPIO7/TXD[7] | 55   | lOz  | General Purpose Input or Output 7.  Available for use as a GPIO pin when the parallel interface is configured for MII, RGMII or RTBI modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                        |

Table 5-6. Detailed Pin Descriptions – SGMII/1000BASE-X Serial Interface (7 pins)

| Pin Name | PIN# | Туре  | Pin Description                                                                |  |

|----------|------|-------|--------------------------------------------------------------------------------|--|

| TDP,     | 9    | Odiff | Transmit Data Output                                                           |  |

| TDN      | 8    |       | These pins form a differential CML output for the 1.25Gbaud SGMII transmit     |  |

|          |      |       | signal to a neighboring 1000BASE-X optical module (SFP, etc.) or PHY with      |  |

|          |      |       | SGMII interface. See section 6.5.                                              |  |

| TCLKP,   | 6    | Odiff | Transmit Clock Output                                                          |  |

| TCLKN    | 5    |       | These pins form a differential CML output for an optional 625MHz clock for     |  |

|          |      |       | the SGMII transmit signal on TDP/TDN. This output is disabled at reset but is  |  |

|          |      |       | enabled by setting CR.TCLK_EN=1. See section 6.5.                              |  |

| RDP,     | 13   | ldiff | Receive Data Input                                                             |  |

| RDN      | 14   |       | These pins form a differential input for the 1.25Gbaud SGMII receive signal    |  |

|          |      |       | rom a neighboring 1000BASE-X optical module (SFP, etc.) or PHY with            |  |

|          |      |       | GGMII interface. A receive clock signal is not necessary because the device    |  |

|          |      |       | uses a built-in CDR to recover the receive clock from the signal on RDP/RDN.   |  |

| AL 00    | 40   |       | See section 6.5.                                                               |  |

| ALOS     | 19   | l     | Analog Loss of Signal                                                          |  |

|          |      |       | This pin receives analog loss-of-signal from a neighboring optical transceiver |  |

|          |      |       | module. If the optical module does not have an ALOS output, this pin should    |  |

|          |      |       | be connected to DVSS for proper operation. See section 6.5.                    |  |

|          |      |       | 0 = ALOS not detected or not required, normal operation                        |  |

|          |      |       | 1 = ALOS detected, loss of signal                                              |  |

Table 5-7. Detailed Pin Descriptions – Parallel Interface (25 pins)

| Pin Name | PIN# | Туре | Pin Description                                                                                                                     |  |

|----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| RXCLK    | 40   | 10   | Receive Clock                                                                                                                       |  |

|          |      |      | In all modes the frequency tolerance is ± 100 ppm.                                                                                  |  |

|          |      |      | GMII Mode: RXCLK is the 125MHz receive clock.                                                                                       |  |

|          |      |      | RGMII Modes: RXCLK is the 125MHz (RGMII-1000), 25MHz (RGMII-100) or                                                                 |  |

|          |      |      | 2.5MHz (RGMII-10) receive clock (DDR).                                                                                              |  |

|          |      |      | TBI Mode: In normal TBI mode (GMIICR.TBI_RATE=1 or RX_DV=1 at                                                                       |  |

|          |      |      | reset), RXCLK is the 62.5MHz receive clock for odd code groups and TXCLK/RCXCLK1 is the 62.5MHz receive clock for even code groups. |  |

|          |      |      | In one-clock TBI mode (GMIICR.TBI_RATE=0 or RX_DV=0 at reset),                                                                      |  |

|          |      |      | RXCLK is the 125MHz receive clock.                                                                                                  |  |

|          |      |      | RTBI Mode: RXCLK is the 125MHz receive clock (DDR).                                                                                 |  |

|          |      |      | MII Mode: RXCLK is the 25MHz (100Mbps MII) or 2.5MHz (10Mbps MII)                                                                   |  |

|          |      |      | receive clock.                                                                                                                      |  |

|          |      |      | In DTE mode (DCE_DTE)=1, RXCLK is an input.                                                                                         |  |

|          |      |      | In DCE mode (DCE_DTE)=0, RXCLK is an output.                                                                                        |  |

| Pin Name | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RXD[0]   | 38   | IOr  | Receive Data Outputs                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| RXD[1]   | 37   | lOr  | During reset these pins are configuration inputs. See section 6.1. After reset they are driven as outputs.                                                                                                                                                                                                                                                                                                                               |  |

| RXD[2]   | 36   | lOr  | GMII Mode: receive_data[7:0] is output on RXD[7:0] on the rising edge of RXCLK.                                                                                                                                                                                                                                                                                                                                                          |  |

| RXD[3]   | 35   | IOr  | MIL DOMIL 40 and DOMIL 400 Mades, massive, data[0:0] is sustant as                                                                                                                                                                                                                                                                                                                                                                       |  |

| RXD[4]   | 34   | lOr  | MII, RGMII-10 and RGMII-100 Modes: receive_data[3:0] is output on RXD[3:0] on the rising edge of RXCLK. RXD[7:4] are high impedance.                                                                                                                                                                                                                                                                                                     |  |

| RXD[5]   | 33   | IOr  | RGMII-1000 Mode: receive_data[3:0] is output on RXD[3:0] on the rising edge of RXCLK, and receive_data[7:4] is output on the falling edge of RXCLK.                                                                                                                                                                                                                                                                                      |  |

| RXD[6]   | 32   | IOr  | RXD[7:4] are high impedance.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RXD[7]   | 31   | IOr  | <u>TBI Mode</u> : In normal TBI mode (GMIICR.TBI_RATE=1 or RX_DV=1 at reset), receive_data[7:0] is output on RXD[7:0], receive_data[8] is output on RX_DV, and receive_data[9] is output on RX_ER on the rising edge of RXCLK and the rising edge of RXCLK1 (both 62.5MHz, 180 degrees out of phase). In one-clock TBI mode (GMIICR.TBI_RATE=0 or RX_DV=0 at reset), these same signals are output on the rising edge of RXCLK (125MHz). |  |

| DV DV    | 00   | 10.  | RTBI Mode: Receive_data[3:0] is output on RXD[3:0] and Receive_data[4] is output on RX_DV on the rising edge of RXCLK. Receive_data[8:5] is output on RXD[3:0] and receive_data[9] is output on RX_DV on the falling edge of RXCLK. RXD[7:4] are high impedance.                                                                                                                                                                         |  |

| RX_DV    | 29   | IOr  | Receive Data Valid  During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.  MII Mode and GMII Mode: RX_DV is output on the rising edge of RXCLK.                                                                                                                                                                                                                                        |  |

|          |      |      | RGMII Modes: The RX_CTL signal is output on RX_DV on both edges of RXCLK.                                                                                                                                                                                                                                                                                                                                                                |  |

|          |      |      | TBI Mode: In normal TBI mode (GMIICR.TBI_RATE=1 or RX_DV=1 at reset), receive_data[8] is output on RX_DV on the rising edge of RXCLK and the rising edge of RXCLK1 (both 62.5MHz, 180 degrees out of phase). In one-clock TBI mode (GMIICR.TBI_RATE=0 or RX_DV=0 at reset), receive_data[8] is output on RX_DV on the rising edge of RXCLK (125MHz).                                                                                     |  |

|          |      |      | RTBI Mode: Receive_data[4} is output on RX_DV on the rising edge of RXCLK. Receive_data[9] is output on RX_DV on the falling edge of RXCLK.                                                                                                                                                                                                                                                                                              |  |

| RX_ER    | 28   | IOr  | Receive Error  During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                                                                                                                   |  |

|          |      |      | MII Mode and GMII Mode: RX_ER is output on the rising edge of RXCLK.                                                                                                                                                                                                                                                                                                                                                                     |  |

|          |      |      | RGMII Mode and RTBI Mode: RX_ER pin is high impedance.                                                                                                                                                                                                                                                                                                                                                                                   |  |

|          |      |      | TBI Mode: In normal TBI mode (GMIICR.TBI_RATE=1 or RX_DV=1 at reset), receive_data[9] is output on RX_ER on the rising edge of RXCLK and the rising edge of RXCLK1 (both 62.5MHz, 180 degrees out of phase). In one-clock TBI mode (GMIICR.TBI_RATE=0 or RX_DV=0 at reset),                                                                                                                                                              |  |

|          |      |      | receive_data[9] is output on the rising edge of RXCLK (125MHz).                                                                                                                                                                                                                                                                                                                                                                          |  |

| Pin Name         | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COL              | 27   | lOr  | Collision Detect  During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                                                                                                                 |

|                  |      |      | MII Mode. GMII Mode and RGMII Modes: COL indicates that a Tx/Rx collision is occurring. It is meaningful only in half duplex operation. It is asynchronous to any of the clocks. COL is driven low at all times when BMCR.DLB=1 and BMCR.COL_TEST=0. When BMCR.DLB=1 and BMCR.COL_TEST=1, COL behaves as described in the COL_TEST bit description.  1 = Collision is occurring 0 = Collision is not occurring                            |

|                  |      |      | TBI Mode and RTBI Mode: This pin is high impedance.                                                                                                                                                                                                                                                                                                                                                                                       |

| CRS/COMMA        | 26   | IOr  | Carrier Sense / Comma Detect During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                                                                                                      |

|                  |      |      | MII Mode. GMII Mode and RGMII Modes: CRS is asserted by the device when either the transmit data path or the receive data path is active. This signal is asynchronous to any of the clocks.                                                                                                                                                                                                                                               |

|                  |      |      | TBI Mode and RTBI Mode: COMMA is asserted by the device when a comma pattern is detected in the receive data stream. In normal TBI mode (GMIICR.TBI_RATE=1 or RX_DV=1 at reset), COMMA is updated on the rising edge of RXCLK and the rising edge of RXCLK1 (both 62.5MHz, 180 degrees out of phase). In one-clock TBI mode (GMIICR.TBI_RATE=0 or RX_DV=0 at reset) and RTBI mode, COMMA is updated on the rising edge of RXCLK (125MHz). |

| TXCLK/<br>RXCLK1 | 46   | Ю    | MII Transmit Clock                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RXCLKI           |      |      | When TXCLK is an input, frequency tolerance is ±100ppm.  MII Mode: TXCLK is the 25MHz (100Mbps MII) or 2.5MHz 10Mbps MII) transmit clock.  In DTE mode (DCE_DTE)=1, TXCLK is an input.  In DCE mode (DCE_DTE)=0, TXCLK is an output.                                                                                                                                                                                                      |

|                  |      |      | GMII Mode, RGMII Mode and RTBI Mode: TXCLK can output a 125MHz clock for use by neighboring components (e.g. a MAC) when GMIICR.TXCLK_EN=1 (or TXCLK=1 at reset).                                                                                                                                                                                                                                                                         |

|                  |      |      | TBI Mode: In normal TBI mode (GMIICR.TBI_RATE=1 or RX_DV=1 at reset), this pin becomes the 62.5MHz RXCLK1 output for even code groups. In one-clock TBI mode (GMIICR.TBI_RATE=0 or RX_DV=0 at reset), TXCLK can output a 125MHz clock for use by neighboring components (e.g. a MAC) when GMIICR.TXCLK_EN=1 (or TXCLK=1 at reset).                                                                                                        |

| Pin Name     | PIN# | Туре | Pin Description                                                                                                                                                                                                                                    |  |

|--------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GTXCLK       | 66   | I    | GMII/RGMII Transmit Clock                                                                                                                                                                                                                          |  |

|              |      |      | In all modes the frequency tolerance is ± 100ppm.                                                                                                                                                                                                  |  |

|              |      |      | GMII Mode: GTXCLK is the 125MHz transmit clock.                                                                                                                                                                                                    |  |

|              |      |      | RGMII Modes: GTXCLK is the 125MHz (RGMII-1000), 25MHz (RGMII-100) or 2.5MHz (RGMII-10) transmit clock (DDR).                                                                                                                                       |  |

|              |      |      | TBI Mode: GTXCLK is the 125MHz transmit clock.                                                                                                                                                                                                     |  |

|              |      |      | RTBI Mode: GTXCLK is the 125MHz transmit clock (DDR).                                                                                                                                                                                              |  |

|              |      |      | MII Mode: This pin is not used and should be pulled low. See the TXCLK pin description.                                                                                                                                                            |  |

| TXD[0]       | 48   | I    | Transmit Data Inputs                                                                                                                                                                                                                               |  |

| TXD[1]       | 49   | ı    | Depending on the parallel MII interface mode, four or eight of these pins are used to accept transmit data from a neighboring component.                                                                                                           |  |

| TXD[2]       | 50   | ı    | GMII Mode: The rising edge of GTXCLK latches transmit_data[7:0] from TXD[7:0].                                                                                                                                                                     |  |

| TXD[3]       | 51   | I    |                                                                                                                                                                                                                                                    |  |

| TXD[4]/GPIO4 | 52   | lOz  | MII, RGMII-10 and RGMII-100 Modes: The rising edge of TXCLK (MII) or GTXCLK (RGMII) latches transmit_data[3:0] from TXD[3:0].  TXD[7:4] become GPIO7 – GPIO4.                                                                                      |  |

| TXD[5]/GPIO5 | 53   | lOz  |                                                                                                                                                                                                                                                    |  |

| TXD[6]/GPIO6 | 54   | lOz  | RGMII-1000 Mode: The rising edge of GTXCLK latches transmit_data[3:0] from TXD[3:0]. The falling edge of GTXCLK latches transmit_data[7:4] from TXD[3:0].                                                                                          |  |

| TXD[7]/GPIO7 | 55   | IOz  | TXD[7:4] become GPIO7 – GPIO4.                                                                                                                                                                                                                     |  |

|              |      |      | TBI Mode: The rising edge of GTXCLK latches transmit_data[7:0] from TXD[7:0], transmit_data[8] from TX_EN and transmit_data[9] from TX_ER.                                                                                                         |  |

|              |      |      | RTBI Mode: The rising edge of GTXCLK latches transmit_data[3:0] from TXD[3:0] and transmit_data[4] from TX_EN. The falling edge of GTXCLK latches transmit_data[8:5] from TXD[3:0] and transmit data[9] from TX_EN. TXD[7:4] become GPIO7 – GPIO4. |  |

| TX_EN        | 57   | I    | Transmit Enable                                                                                                                                                                                                                                    |  |

|              |      |      | MII Mode and GMII Mode: The rising edge of TXCLK (MII) or GTXCLK (GMII) latches the TX_EN signal from this pin.                                                                                                                                    |  |

|              |      |      | RGMII Modes: Both edges of GTXCLK latch the TX_CTL signal from this pin.                                                                                                                                                                           |  |

|              |      |      | TBI Mode: The rising edge of GTXCLK latches transmit_data[7:0] from TXD[7:0], transmit_data[8] from TX_EN and transmit_data[9] from TX_ER.                                                                                                         |  |

|              |      |      | RTBI Mode: The rising edge of GTXCLK latches transmit_data[3:0] from TXD[3:0] and transmit_data[4] from TX_EN. The falling edge of GTXCLK latches transmit_data[8:5] from TXD[3:0] and transmit data[9] from TX_EN.                                |  |

| Pin Name | PIN# | Туре | Pin Description                                                                                                                            |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| TX_ER    | 58   | I    | Transmit Error                                                                                                                             |

|          |      |      | MII Mode and GMII Mode: The rising edge of TXCLK (MII) or GTXCLK (GMII) latches the TX_ER signal from this pin.                            |

|          |      |      | RGMII Modes: This pin is not used.                                                                                                         |

|          |      |      | TBI Mode: The rising edge of GTXCLK latches transmit_data[7:0] from TXD[7:0], transmit_data[8] from TX_EN and transmit_data[9] from TX_ER. |

|          |      |      | RTBI Mode: This pin is not used.                                                                                                           |

Table 5-8. Detailed Pin Descriptions – Power and Ground Pins (17 pins)

| Pin Name    | PIN#       | Pin Description                                                                                                                                               |  |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DVDD12      | 30, 56     | Digital Power Supply, 1.2V (2 pins)                                                                                                                           |  |

| DVDD33      | 20, 39, 65 | Digital Power Supply, 3.3V                                                                                                                                    |  |

| DVSS        | 47         | Return for DVDD12 and DVDD33                                                                                                                                  |  |

| RVDD12      | 16         | 1.25G Receiver Analog Power Supply, 1.2V                                                                                                                      |  |

| RVDD33      | 12         | 1.25G Receiver Analog Power Supply, 3.3V                                                                                                                      |  |

| RVSS        | 15         | Return for RVDD12 and RVDD33                                                                                                                                  |  |

| TVDD12      | 11         | 1.25G Transmitter Analog Power Supply, 1.2V                                                                                                                   |  |

| TVDD33      | 7          | 1.25G Transmitter Analog Power Supply, 3.3V                                                                                                                   |  |

| TVSS        | 10         | Return for TVDD12 and TVDD33                                                                                                                                  |  |

| CVDD12      | 3          | TX PLL Analog Power Supply, 1.2V                                                                                                                              |  |

| CVDD33      | 2          | TX PLL Analog Power Supply, 3.3V                                                                                                                              |  |

| CVSS        | 4          | Return for CVDD12 and CVDD33                                                                                                                                  |  |

| GVDD12      | 18         | Analog Power Supply, 1.2V                                                                                                                                     |  |

| GVSS        | 1          | Return for GVDD12.                                                                                                                                            |  |

| Exposed Pad | EP         | Exposed pad (die paddle). Connect to ground plane. EP also functions as a heatsink. Solder to the circuit-board ground plane to maximize thermal dissipation. |  |

## 6. Functional Description

## 6.1 Pin Configuration During Reset

The MAX24287 initial configuration is determined by pins that are sampled at reset. The values on these pins are used to set the reset values of several register bits. Note that the behavior described in this section cannot be used for "hardware-only" operation. Some register accesses through the MDIO interface are required for proper operation as described in section 6.14.

The pins that are sampled at reset to pin-configure the device are listed described in Table 6-1. During reset these pins are high-impedance inputs and require  $10k\Omega$  pullup or pulldown resistors to set pin-configuration values. After reset, the pins can become outputs if configured to do so and operate as configured. There are two pin configuration modes: 15-pin mode and 3-pin mode.

In 15-pin mode (COL=0 during reset, see Table 6-1) all major settings associated with the PCS block are configurable. In addition, the input reference clock frequency on the REFCLK pin is configured during reset using the RXD[3:2] pins.

Table 6-1. Reset Configuration Pins, 15-Pin Mode (COL=0)

| Pin      | Function                 | Register Bit Affected         | Notes                                                                                                 |

|----------|--------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|

| CRS      | Double Date Rate         | GMIICR:DDR=CRS                | See Table 6-2.                                                                                        |

| GPO2     | 10/100 MII: DTE or DCE   | 10/100 MII: GMIICR:DTE_DCE    | 0=DCE, 1=DTE<br>(serial interface is configured for<br>SGMII mode, PCSCR:BASEX=0)                     |

|          | Other: Serial Interface  | Other: PCSCR:BASEX            | 0=SGMII, 1=1000BASE=X                                                                                 |

| GPO1     | GPIO1 Configuration      | GPIOCR1.GPIO1_SEL[2]          | 0=high impedance<br>1=125MHz from TX PLL                                                              |

| RXD[1:0] | Parallel Interface Speed | GMIICR:SPD[1:0]               | See Table 6-2.                                                                                        |

| RXD[3:2] | REFCLK Frequency         | None                          | 00=10MHz, 01=12.8MHz,<br>10=25MHz, 11=125MHz                                                          |

| RXD[7:4] | MDIO PHYAD[3:0].         | Internal MDIO PHYAD register  | Note: PHYAD[4:0]=11111 enables                                                                        |

| RX_ER    | MDIO PHYAD[4].           | (device address on MDIO bus). | factory test mode. Do not use.                                                                        |

| RX_DV    | TBI Mode                 | GMIICR:TBI_RATE               | 0=one-clock mode (125MHz)<br>1=normal mode (62.5MHz x 2)                                              |

|          | Other: Auto-negotiation  | BMCR:AN_EN                    | 0=Disable, 1=Enable                                                                                   |

| TXCLK    | TXCLK Enable             | GMIICR:TXCLK_EN               | 0=high impedance<br>1=125MHz from TX PLL<br>Ignored in MII mode and TBI with<br>two 62.5MHz Rx clocks |

Table 6-2. Parallel Interface Configuration

| SPD[1] | SPD[0] | Speed    | DDR=0 | DDR=1      |

|--------|--------|----------|-------|------------|

| 0      | 0      | 10Mbps   | MII   | RGMII-10   |

| 0      | 1      | 100Mbps  | MII   | RGMII-100  |

| 1      | 0      | 1000Mbps | GMII  | RGMII-1000 |

| 1      | 1      | 1000Mbps | TBI   | RTBI       |

In 3-pin mode (COL=1 during reset, see Table 6-3) the device is configured for a 1000Mbps RGMII or GMII parallel interface. This mode is targeted to the application of connecting an ASIC, FPGA or processor with an RGMII or GMII interface to a switch device with an SGMII interface or to a 1000BASE-X optical interface. In 3-pin mode, the REFCLK pin is configured for 25MHz, the PHY address is set to 0x04, 1000BASE-X auto-negotiation (or automatic transmission of SGMII control information) is enabled, TXCLK is configured to output a 125MHz clock, and the

TCLKP/TCLKN differential pair is disabled. Note: if RX\_ER and RXD[7:4] are all high when the device exits reset then the device enters factory test mode; for normal operation set these pins to any other combination of values.

Table 6-3. Reset Configuration Pins, 3-Pin Mode (COL=1)

| Pin  | Function         | Register Bit Affected | Notes                 |

|------|------------------|-----------------------|-----------------------|

| CRS  | Double Date Rate | GMIICR:DDR=CRS        | 0=GMII, 1=RGMII       |

| GPO2 | Serial Interface | PCSCR:BASEX           | 0=SGMII, 1=1000BASE=X |

Note: In 3-pin mode register fields are automatically set as follows: REFCLK clock rate to 25MHz, GMIICR:SPD[1:0]=10, MDIO PHYAD is set to 0x04, BMCR:AN\_EN=1, GMIICR:TXCLK\_EN=1, GPIOCR1=0 and GPIOCR2=0. All other registers are reset to normal defaults listed in the register descriptions.

## 6.2 General-Purpose I/O

The MAX24287 has two general-purpose output pins, GPO1, GPO2, and seven general-purpose input/output pins, GPIO1 through GPIO7. Each pin can be configured to drive low or high or be in a high-impedance state. Other uses for the GPO and GPIO pins are listed in Table 6-4 through Table 6-6. The GPO and GPIO pins are each configured using a GPxx\_SEL field in registers GPIOCR1 or GPIOCR2 with values as indicated in the tables below.

When a GPIO pin is configured as high impedance it can be used as an input. The real-time state of GPIOx can be read from GPIOSR.GPIOx. In addition, a latched status bit GPIOSR.GPIOxL is available for each GPIO pin. This latched status bit is set when the transition specified by GPIOCR2.GPIO13\_LSC (for GPIO1 through GPIO3) or by GPIOCR2.GPIO47\_LSC (for GPIO4 through GPIO7) occurs on the pin.

Note that GPIO4 through GPIO7 are alternate pin functions to TXD[7:4] and therefore are only available when the parallel MII is configured for MII, RGMII or RTBI.

Table 6-4. GPO1, GPIO1 and GPIO3 Configuration Options

| GPxx_SEL | Description                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------|

| 000      | High impedance, not driven, can be an used as an input                                                   |

| 001      | Drive logic 0                                                                                            |

| 010      | Drive logic 1                                                                                            |

| 011      | Interrupt output, active low. GPO1 drives low and high, GPIO1 and GPIO3 are open-drain.                  |

| 100      | Output 125MHz from the TX PLL                                                                            |

| 101      | Output 25MHz or 125MHz from receive clock recovery PLL. Not squelched. Frequency specified by CR.RCFREQ. |

| 110      | Output real-time link status, 0=link down, 1=link up                                                     |

| 111      | reserved value, do not use                                                                               |

Table 6-5. GPO2 and GPIO2 Configuration Options

| GPxx_SEL | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000      | High impedance, not driven, can be an used as an input                                                                                                                                                                  |

| 001      | Drive logic 0                                                                                                                                                                                                           |

| 010      | Drive logic 1                                                                                                                                                                                                           |

| 011      | reserved value, do not use                                                                                                                                                                                              |

| 100      | Output 125MHz from TX PLL                                                                                                                                                                                               |

| 101      | Output 25MHz or 125MHz from receive clock recovery PLL. The frequency is specified by CR.RCFREQ. Signal is automatically squelched (driven low) when CR.RCSQL=1 and any of several conditions occur. See section 6.2.1. |

| 110      | Output CRS (carrier sense) status                                                                                                                                                                                       |

| 111      | reserved value, do not use                                                                                                                                                                                              |

Table 6-6. GPIO4, GPIO5, GPIO6 and GPIO7 Configuration Options

| GPxx_SEL | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000      | High impedance, not driven, can be an used as an input                                                                                                                                                                  |

| 001      | Drive logic 0                                                                                                                                                                                                           |

| 010      | Drive logic 1                                                                                                                                                                                                           |

| 011      | reserved value, do not use                                                                                                                                                                                              |

| 100      | Output 125MHz from TX PLL                                                                                                                                                                                               |

| 101      | Output 25MHz or 125MHz from receive clock recovery PLL. The frequency is specified by CR.RCFREQ. Signal is automatically squelched (driven low) when CR.RCSQL=1 and any of several conditions occur. See section 6.2.1. |

| 110      | reserved value, do not use                                                                                                                                                                                              |

| 111      | reserved value, do not use                                                                                                                                                                                              |

### 6.2.1 Receive Recovered Clock Squelch Criteria

A 25MHz or 125MHz clock from the receive clock recovery PLL can be output on any of GPO2, GPIO2 and GPIO4-7. When CR.RCSQL=1, this clock is squelched (driven low) when any of the following conditions occur:

- IR.ALOS=1 (analog loss-of-signal occurred)

- IR.RLOS=1 (CDR loss-of-signal occurred))

- IR.RLOL=1 (CDR PLL loss-of-lock occurred)

- IR.LINK\_ST=0 (auto-negotiation link down occurred, latched low)

Since each of these criteria is a latched status bit, the output clock signal remains squelched until all of these latched status bits go inactive (as described in section 7.2).

### 6.3 Reset and Processor Interrupt

#### 6.3.1 Reset

The following reset functions are available in the device:

- 1. Hardware reset pin (RST\_N): This pin asynchronously resets all logic, state machines and registers in the device except the JTAG logic. When the RST\_N pin is low, all internal registers are reset to their default values. Pin states are sampled and used to set the default values of several register fields as described in section 6.1. RST N should be asserted for at least 100 us.

- 2. Global reset bit, GPIOCR1.RST: Setting this bit is equivalent to asserting the RST\_N pin. This bit is self-clearing.

- 3. Datapath reset bit, BMCR.DP\_RST. This bit resets the entire datapath from parallel MII interface through PCS encoder and decoder. It also resets the deserializer. It does not reset any registers, GPIO logic, or the TX PLL. The DP\_RST bit is self-clearing.

- 4. JTAG reset pin JTRST\_N. This pin resets the JTAG logic. See section 7.2.18 for details about JTAG operation.

#### 6.3.2 Processor Interrupts

Any of pins GPO1, GPIO1 and GPIO3 can be configured as an active low interrupt output by setting the appropriate field in GPIOCR1 to 011. GPO1 drives high and low while GPIO1 and GPIO3 are open-drain and require pullup resistors.

Status bits than can cause an interrupt are located in the IR register. The corresponding interrupt enable bits are also located in the IR register. The PAGESEL register has a top-level IR status bit to indicate the presence of

active interrupt sources. The PAGESEL register is available on all pages through the MDIO interface, allowing the interrupt routine to read the register without changing the MDIO page.

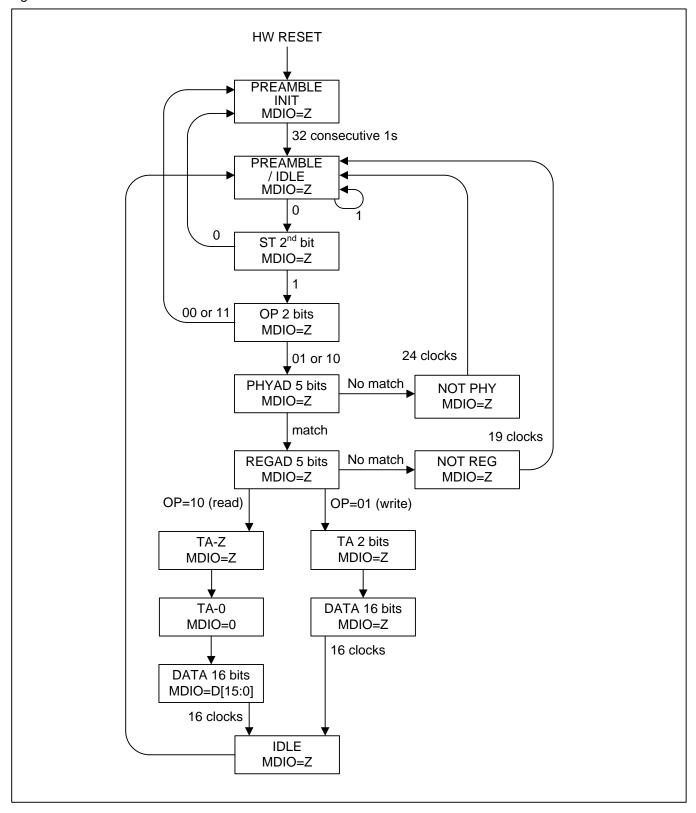

#### 6.4 MDIO Interface

#### 6.4.1 MDIO Overview

The MAX24287's MDIO interface is compliant to IEEE 802.3 clause 22. MAX24287 always behaves as a PHY on the MDIO bus. Because MAX24287 is not a complete PHY but rather a device that sits between a MAC and a PHY, it implements only a subset of the registers and register fields specified in 802.3 clause 22 as shown in the table below.

| MDIO<br>Address | 802.3 Name                                      | MAX24287<br>Name |  |  |

|-----------------|-------------------------------------------------|------------------|--|--|

| 0               | Control                                         | BMCR             |  |  |

| 1               | Status                                          | BMSR             |  |  |

| 2, 3            | PHY Identifier ID1, ID2                         |                  |  |  |

| 4               | Auto-Negotiation Advertisement                  | AN_ADV           |  |  |

| 5               | Auto-Negotiation Link Partner Base Page Ability | AN_RX            |  |  |

| 6               | Auto-Negotiation Expansion                      | AN_EXP           |  |  |

| 15              | Extended Status                                 | EXT_STAT         |  |  |