# Am29C325

CMOS 32-Bit Floating-Point Processor

# **FINAL**

# DISTINCTIVE CHARACTERISTICS

- Single VLSI device performs high-speed singleprecision floating-point arithmetic Floating-point addition, subtraction, and multiplication in a single clock cycle Internal architecture supports sum-of-products, Newton-Raphson division

- 32-bit, three-bus flow-through architecture Programmable I/O allows interface to 32- and 16-bit systems

- IEEE and DEC formats

Performs conversions between formats

Performs integer ←> floating-point conversions

- Input and output registers may be made transparent independently

- Pin and functionally compatible with the bipolar Am29325

- The Am29C325 uses less than one-quarter the power of the Am29325

- 145 PGA requires no heatsink

# **GENERAL DESCRIPTION**

The Am29C325 is a high-speed floating-point processor unit. It performs 32-bit single-precision floating-point addition, subtraction, and multiplication operations in a single VLSI circuit, using the format specified by the IEEE floating-point standard, 754. The DEC single-precision floating-point format is also supported. Operations for conversion between 32-bit integer format and floating-point format are available, as are operations for converting between the IEEE and DEC floating-point formats. Any instruction can be performed in a single clock cycle. Six flags — invalid operation, inexact result, zero, not-a-number, overflow, and underflow — monitor the status of operations.

The Am29C325 has a three-bus, 32-bit architecture, with two input buses and one output bus. This configuration

provides high I/O bandwidth, allows access to all buses, and affords a high degree of flexibility when connecting this device in a system. All buses are registered, with each register having a clock enable. Input and output registers may be made transparent independently. Two other I/O configurations, a 32-bit, two-bus architecture and a 16-bit, three-bus architecture, are user-selectable, easing interface with a wide variety of systems. Thirty-two-bit internal feedforward datapaths support accumulation operations, including sum-of-products and Newton-Raphson division.

Fabricated using Advanced Micro Devices' 1.2 micron CMOS process, the Am29C325 is powered by a single 5-volt supply. The device is housed in a 145-lead pin-grid-array package.

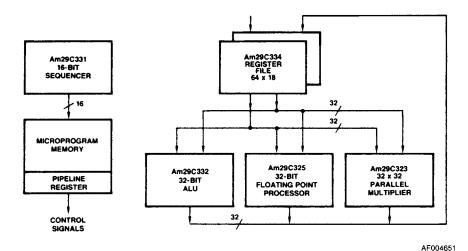

# Am29C300 FAMILY HIGH-PERFORMANCE SYSTEM BLOCK DIAGRAM

Publication # Rev. Amendment

07783 C /0

Issue Date: March 1989

Am29C325

# **RELATED AMD PRODUCTS**

| Part No.   | Description                                                  |

|------------|--------------------------------------------------------------|

| Am29027    | Am29K Arithmetic Accelerator                                 |

| Am29116    | High-Performance Bipolar 16-Bit Microprocessor               |

| Am29C116   | High-Performance CMOS 16-Bit Microprocessor                  |

| Am29CPL141 | CMOS 64 x 16 EPROM Field Programmable Controller             |

| Am29CPL142 | CMOS 128 x 16 EPROM Field Programmable Controller            |

| Am29CPL144 | CMOS 512 x 16 EPROM Field Programmable Controller            |

| Am29CPL151 | CMOS 64 x 16 EPROM Field Programmable Controller — Slim DIP  |

| Am29CPL152 | CMOS 128 x 16 EPROM Field Programmable Controller — Slim DIP |

| Am29CPL154 | CMOS 512 x 16 EPROM Field Programmable Controller — Slim DIP |

| Am29C323   | CMOS 32-Bit Parallel Multiplier                              |

| Am29C327   | CMOS Double-Precision Floating-Point Processor               |

| Am29331    | 16-Bit Microprogram Sequencer                                |

| Am29C331   | CMOS 16-Bit Microprogram Sequencer                           |

| Am29332    | 32-Bit Extended Function ALU                                 |

| Am29C332   | CMOS 32-Bit Extended Function ALU                            |

| Am29334    | 64 x 18 Four-Port, Dual-Access Register File                 |

| Am29C334   | CMOS 64 x 18 Four-Port, Dual-Access Register File            |

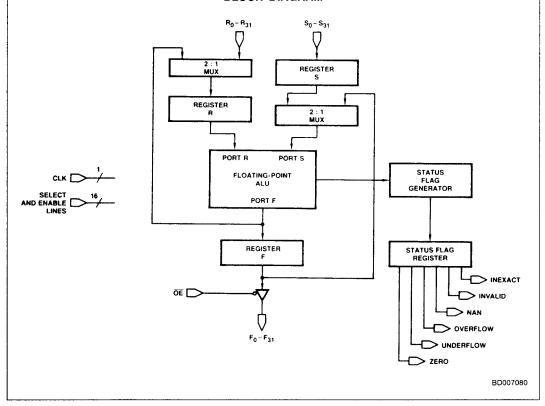

# **BLOCK DIAGRAM**

2-4 Am29C325

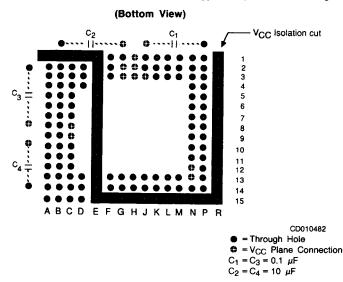

# **CONNECTION DIAGRAM** Top View

# **PGA**

|    | Α          | В    | С    | D    | E     | F     | G   | н   | J    | K    | Ĺ   | М   | N   | Р   | R   |

|----|------------|------|------|------|-------|-------|-----|-----|------|------|-----|-----|-----|-----|-----|

| 1  | INEX       | 12   | l1   | ENF  | 14    | OBUS  | ŌĒ  | vcc | CLK  | R31  | R30 | R25 | R24 | R21 | R20 |

| 2  | INVA       | NAN  | 10   | ı⁄δ  | FT0   | FT1   | vcc | vcc | RND0 | RND1 | R27 | R28 | R23 | R22 | R17 |

| 3  | F29        | ZERO | GNDO | ENR  | ENS   | 16/32 | vcc | vcc | vcc  | R29  | R26 | GND | GND | R19 | R18 |

| 4  | F30        | F31  | GNDO | *    |       |       |     |     |      |      |     |     | R15 | R16 | R13 |

| 5  | F23        | OVFL | UNFL |      |       |       |     |     |      |      |     |     | R14 | R11 | R12 |

| 6  | F26        | F27  | F28  |      |       |       |     |     |      |      |     |     | R9  | R10 | R7  |

| 7  | F21        | F24  | F25  |      |       |       |     |     |      |      |     |     | R8  | R5  | R6  |

| 8  | F22        | F19  | vcco |      |       |       |     |     |      |      |     |     | R3  | R4  | R1  |

| 9  | F17        | F20  | vcco |      |       |       |     |     |      |      |     |     | R0  | 13  | R2  |

| 10 | F18        | F15  | F16  |      |       |       |     |     |      |      |     |     | S28 | S31 | S30 |

| 11 | F13        | F14  | F11  |      |       |       |     |     |      |      |     |     | S27 | S26 | S29 |

| 12 | F12        | F9   | F10  |      |       |       |     |     |      |      |     |     | vcc | S25 | S24 |

| 13 | <b>F</b> 7 | F6   | GNDO | GNDO | GNDO  | GNDO  | GND | GND | GND  | S8   | S13 | S14 | vcc | S22 | S23 |

| 14 | F8         | F3   | F2   | GNDO | F0    | S1    | S2  | GND | S4   | S9   | S10 | S15 | S18 | S21 | S20 |

| 15 | F5         | F4   | F1   | GNDO | P/AFF | S0    | S3  | S5  | S7   | S6   | S11 | S12 | S17 | S16 | S19 |

CD010492

Key:

$16/\overline{32} = S16/\overline{32}$

$I/\overline{D} = IEEE/\overline{DEC}$

INEX = INEXACT

INVA = INVALID

OBUS = ONEBUS

OVFL = OVERFLOW P/AFF = PROJ/AFF

UNFL = UNDERFLOW

<sup>\*</sup>D4 is an alignment pin (not connected internally).

# PIN DESIGNATIONS

(Sorted by Pin No.)

| PIN NO.     | PIN NAME        | PIN NO. | PIN NAME        | PIN NO. | PIN NAME         | PIN NO. | PIN NAME        |

|-------------|-----------------|---------|-----------------|---------|------------------|---------|-----------------|

| <b>A</b> -1 | Inexact         | C-7     | F <sub>25</sub> | H-13    | GND              | N-10    | S <sub>28</sub> |

| A-2         | Invalid         | C-8     | Vcco            | H-14    | GND              | N-11    | S <sub>27</sub> |

| A-3         | F <sub>29</sub> | C-9     | Vcco            | H-15    | S <sub>5</sub>   | N-12    | Vcc             |

| A-4         | F <sub>30</sub> | C-10    | F <sub>16</sub> | J-1     | CLK              | N-13    | Vcc             |

| A-5         | F <sub>23</sub> | C-11    | F <sub>11</sub> | J-2     | RND <sub>0</sub> | N-14    | S <sub>18</sub> |

| A-6         | F <sub>26</sub> | C-12    | F <sub>10</sub> | J-3     | Vcc              | N-15    | S <sub>17</sub> |

| A-7         | F <sub>21</sub> | C-13    | GNDO            | J-13    | GND              | P-1     | R <sub>21</sub> |

| A-8         | F <sub>22</sub> | C-14    | F <sub>2</sub>  | J-14    | S <sub>4</sub>   | P-2     | R <sub>22</sub> |

| A-9         | F <sub>17</sub> | C-15    | F <sub>1</sub>  | J-15    | S <sub>7</sub>   | P-3     | R <sub>19</sub> |

| A-10        | F <sub>18</sub> | D-1     | ENF             | K-1     | R <sub>31</sub>  | P-4     | R <sub>16</sub> |

| A-11        | F <sub>13</sub> | D-2     | IEEE/DEC        | K-2     | RND <sub>1</sub> | P-5     | R <sub>11</sub> |

| A-12        | F <sub>12</sub> | D-3     | ENR             | K-3     | R <sub>29</sub>  | P-6     | R <sub>10</sub> |

| A-13        | F <sub>7</sub>  | D-13    | GNDO            | K-13    | S <sub>8</sub>   | P-7     | R <sub>5</sub>  |

| A-14        | F <sub>8</sub>  | D-14    | GNDO            | K-14    | S <sub>9</sub>   | P-8     | R <sub>4</sub>  |

| A-15        | F <sub>5</sub>  | D-15    | GNDO            | K-15    | S <sub>6</sub>   | P-9     | 13              |

| B-1         | 12              | E-1     | 14              | L-1     | R <sub>30</sub>  | P-10    | S <sub>31</sub> |

| B-2         | NAN             | E-2     | FT <sub>0</sub> | L-2     | R <sub>27</sub>  | P-11    | S <sub>26</sub> |

| B-3         | ZERO            | E-3     | ENS             | L-3     | R <sub>26</sub>  | P-12    | S <sub>25</sub> |

| B-4         | F <sub>31</sub> | E-13    | GNDO            | L-13    | S <sub>13</sub>  | P-13    | S <sub>22</sub> |

| B-5         | OVERFLOW        | E-14    | F <sub>0</sub>  | L-14    | S <sub>10</sub>  | P-14    | S <sub>21</sub> |

| B-6         | F <sub>27</sub> | E-15    | PROJ/AFF        | L-15    | S <sub>11</sub>  | P-15    | S <sub>16</sub> |

| B-7         | F <sub>24</sub> | F-1     | ONEBUS          | M-1     | R <sub>25</sub>  | R-1     | R <sub>20</sub> |

| B-8         | F <sub>19</sub> | F-2     | FT <sub>1</sub> | M-2     | R <sub>28</sub>  | R-2     | R <sub>17</sub> |

| B-9         | F <sub>20</sub> | F-3     | S16/32          | M-3     | GND              | R-3     | R <sub>18</sub> |

| B-10        | F <sub>15</sub> | F-13    | GNDO            | M-13    | S <sub>14</sub>  | R-4     | R <sub>13</sub> |

| B-11        | F <sub>14</sub> | F-14    | S <sub>1</sub>  | M-14    | S <sub>15</sub>  | R-5     | R <sub>12</sub> |

| B-12        | F <sub>9</sub>  | F-15    | S <sub>0</sub>  | M-15    | S <sub>12</sub>  | R-6     | R <sub>7</sub>  |

| B-13        | F <sub>6</sub>  | G-1     | ŌĒ              | N-1     | R <sub>24</sub>  | R-7     | R <sub>6</sub>  |

| B-14        | F <sub>3</sub>  | G-2     | Vcc             | N-2     | R <sub>23</sub>  | R-8     | R <sub>1</sub>  |

| B-15        | F <sub>4</sub>  | G-3     | Vcc             | N-3     | GND              | R-9     | R <sub>2</sub>  |

| C-1         | 11              | G-13    | GND             | N-4     | R <sub>15</sub>  | R-10    | S <sub>30</sub> |

| C-2         | i <sub>0</sub>  | G-14    | S <sub>2</sub>  | N-5     | R <sub>14</sub>  | R-11    | S <sub>29</sub> |

| C-3         | GNDO            | G-15    | S <sub>3</sub>  | N-6     | R <sub>9</sub>   | R-12    | S <sub>24</sub> |

| C-4         | GNDO            | H-1     | Vcc             | N-7     | R <sub>8</sub>   | R-13    | S <sub>23</sub> |

| C-5         | UNDERFLOW       | H-2     | Vcc             | N-8     | R <sub>3</sub>   | R-14    | S <sub>20</sub> |

| C-6         | F <sub>28</sub> | H-3     | Vcc             | N-9     | R <sub>0</sub>   | R-15    | S <sub>19</sub> |

Note: Pin number D4 = Alignment Pin

$V_{CCO}$  and GNDO are power and ground pins for the output buffers.  $V_{CC}$  and GND are power and ground pins for the rest of the logic.

2-6 Am29C325

# PIN DESIGNATIONS (Cont'd.)

# (Sorted by Pin Name)

| PIN NO. | PIN NAME        | PIN NO. | PIN NAME.       | PIN NO. | PIN NAME         | PIN NO. | PIN NAME.       |

|---------|-----------------|---------|-----------------|---------|------------------|---------|-----------------|

| J-1     | CLK             | E-2     | FT <sub>0</sub> | R-6     | R <sub>7</sub>   | K-14    | S <sub>9</sub>  |

| D-1     | ENF             | F-2     | FT <sub>1</sub> | N-7     | R <sub>8</sub>   | L-14    | S <sub>10</sub> |

| D-3     | ENR             | G-13    | GND             | N-6     | R <sub>9</sub>   | L-15    | S <sub>11</sub> |

| E-3     | ENS             | H-13    | GND             | P-6     | R <sub>10</sub>  | M-15    | S <sub>12</sub> |

| E-14    | F <sub>0</sub>  | H-14    | GND             | P-5     | R <sub>11</sub>  | L-13    | S <sub>13</sub> |

| C-15    | F <sub>1</sub>  | J-13    | GND             | R-5     | R <sub>12</sub>  | M-13    | S <sub>14</sub> |

| C-14    | F <sub>2</sub>  | M-3     | GND             | R-4     | R <sub>13</sub>  | M-14    | S <sub>15</sub> |

| B-14    | F <sub>3</sub>  | N-3     | GND             | N-5     | R <sub>14</sub>  | P-15    | S <sub>16</sub> |

| B-15    | F <sub>4</sub>  | C-3     | GNDO            | N-4     | R <sub>15</sub>  | F-3     | S16/32          |

| A-15    | F <sub>5</sub>  | C-4     | GNDO            | P-4     | R <sub>16</sub>  | N-15    | S <sub>17</sub> |

| B-13    | F <sub>6</sub>  | C-13    | GNDO            | R-2     | R <sub>17</sub>  | N-14    | S <sub>18</sub> |

| A-13    | F <sub>7</sub>  | D-13    | GNDO            | R-3     | R <sub>18</sub>  | R-15    | S <sub>19</sub> |

| A-14    | F <sub>8</sub>  | D-14    | GNDO            | P-3     | R <sub>19</sub>  | R-14    | S <sub>20</sub> |

| B-12    | Fg              | D-15    | GNDO            | R-1     | R <sub>20</sub>  | P-14    | S <sub>21</sub> |

| C-12    | F <sub>10</sub> | E-13    | GNDO            | P-1     | R <sub>21</sub>  | P-13    | S <sub>22</sub> |

| C-11    | F <sub>11</sub> | F-13    | GNDO            | P-2     | R <sub>22</sub>  | R-13    | S <sub>23</sub> |

| A-12    | F <sub>12</sub> | C-2     | lo              | N-2     | R <sub>23</sub>  | R-12    | S <sub>24</sub> |

| A-11    | F <sub>13</sub> | C-1     | l <sub>1</sub>  | N-1     | R <sub>24</sub>  | P-12    | S <sub>25</sub> |

| B-11    | F <sub>14</sub> | B-1     | 12              | M-1     | R <sub>25</sub>  | P-11    | S <sub>26</sub> |

| B-10    | F <sub>15</sub> | P-9     | l <sub>3</sub>  | L-3     | R <sub>26</sub>  | N-11    | S <sub>27</sub> |

| C-10    | F <sub>16</sub> | E-1     | 14              | L-2     | R <sub>27</sub>  | N-10    | S <sub>28</sub> |

| A-9     | F <sub>17</sub> | D-2     | IEEE/DEC        | M-2     | R <sub>28</sub>  | R-11    | S <sub>29</sub> |

| A-10    | F <sub>18</sub> | A-1     | INEXACT         | K-3     | R <sub>29</sub>  | R-10    | S <sub>30</sub> |

| B-8     | F <sub>19</sub> | A-2     | INVALID         | L-1     | R <sub>30</sub>  | P-10    | S <sub>31</sub> |

| B-9     | F <sub>20</sub> | B-2     | NAN             | K-1     | R <sub>31</sub>  | C-5     | UNDERFLOW       |

| A-7     | F <sub>21</sub> | G-1     | ŌĒ              | J-2     | RND <sub>0</sub> | G-2     | VCC             |

| A-8     | F <sub>22</sub> | F-1     | ONEBUS          | K-2     | RND <sub>1</sub> | G-3     | Vcc             |

| A-5     | F <sub>23</sub> | B-5     | OVERFLOW        | F-15    | S <sub>0</sub>   | H-1     | VCC             |

| B-7     | F <sub>24</sub> | E-15    | PROJ/AFF        | F-14    | S <sub>1</sub>   | H-2     | Vcc             |

| C-7     | F <sub>25</sub> | N-9     | R <sub>0</sub>  | G-14    | S <sub>2</sub>   | H-3     | Vcc             |

| A-6     | F <sub>26</sub> | R-8     | R <sub>1</sub>  | G-15    | S <sub>3</sub>   | J-3     | Vcc             |

| B-6     | F <sub>27</sub> | R-9     | R <sub>2</sub>  | J-14    | S <sub>4</sub>   | N-12    | Vcc             |

| C-6     | F <sub>28</sub> | N-8     | R <sub>3</sub>  | H-15    | S <sub>5</sub>   | N-13    | Vcc             |

| A-3     | F <sub>29</sub> | P-8     | R <sub>4</sub>  | K-15    | S <sub>6</sub>   | C-8     | Vcco            |

| A-4     | F <sub>30</sub> | P-7     | R <sub>5</sub>  | J-15    | S <sub>7</sub>   | C-9     | Vcco            |

| B-4     | F <sub>31</sub> | R-7     | R <sub>6</sub>  | K-13    | S <sub>8</sub>   | B-3     | ZERO            |

Note: Pin number D4 = Alignment Pin

$V_{CCO}$  and GNDO are power and ground pins for the output buffers.  $V_{CC}$  and GND are power and ground pins for the rest of the logic.

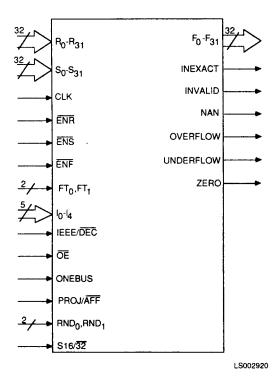

# LOGIC SYMBOL

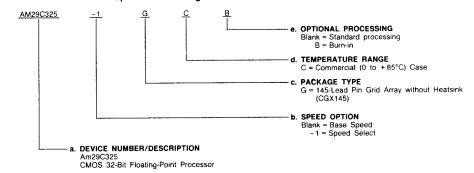

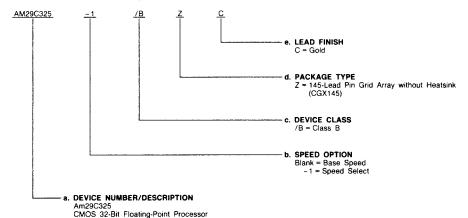

# ORDERING INFORMATION

# Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

# Valid Combinations AM29C325 GC, GCB AM29C325-1 GC

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# **MILITARY ORDERING INFORMATION**

# **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid C    | ombinations |

|------------|-------------|

| AM29C325   | /BZC        |

| AM29C325-1 | 7,620       |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

# Group A Tests

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

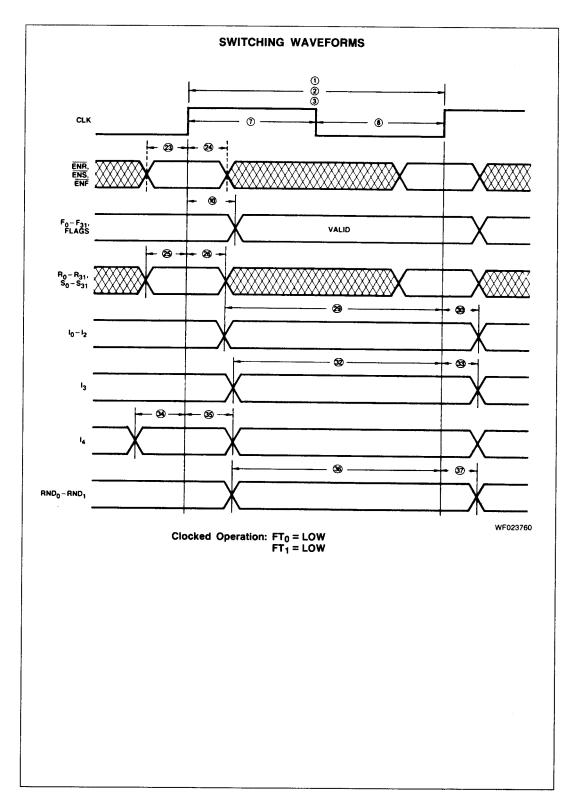

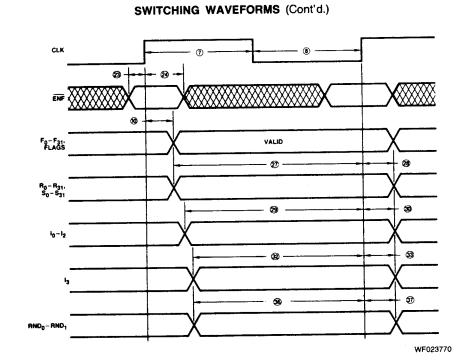

# CLK Clock (Input)

For the internal registers.

When ENF is LOW, register F is clocked on the LOW-to-HIGH transition of CLK. When ENF is HIGH, register F retains the previous contents.

ENR Register R Clock Enable (Input; Active LOW)

When ENR is LOW, register R is clocked on the LOW-to-HIGH transition of CLK. When ENR is HIGH, register R retains the previous contents.

ENS Register S Clock Enable (Input; Active LOW)

When ENS is LOW, register S is clocked on the LOW-to-HIGH transition of CLK. When ENS is HIGH, register S retains the previous contents.

F<sub>0</sub> - F<sub>31</sub> F Operand Bus (Output) F<sub>0</sub> is the least significant bit.

FT<sub>0</sub> Input Register Feedthrough Control (Input; Active HIGH)

When FT<sub>0</sub> is HIGH, registers R and S are transparent.

FT<sub>1</sub> Output Register Feedthrough Control (Input; Active HIGH)

When  $FT_1$  is HIGH, register F and the status flag register are transparent.

I<sub>0</sub> - I<sub>2</sub> Operation Select Lines (Input)

Used to select the operation to be performed by the ALU. See Table 1 for a list of operations and the corresponding codes.

13 ALU S Port Input Select (Input)

A LOW on I<sub>3</sub> selects register S as the input to the ALU S port. A HIGH on I<sub>3</sub> selects register F as the input to the ALU S port.

I<sub>4</sub> Register R Input Select (Input)

A LOW on I<sub>4</sub> selects  $R_0$ - $R_{31}$  as the input to register R. A HIGH selects the ALU F port as the input to register R.

IEEE/DEC IEEE/DEC Mode Select (Input)

When IEEE/DEC is HIGH, IEEE mode is selected. When IEEE/DEC is LOW. DEC mode is selected.

INEXACT Inexact Result Flag (Output; Active HIGH)

A HIGH indicates that the final result of the last operation was not infinitely precise, due to rounding.

INVALID Invalid Operation Flag (Output; Active HIGH)

A HIGH indicates that the last operation performed was invalid; e.g.,  $\infty$  times 0.

#### NAN Not-a-Number Flag (Output; Active HIGH)

A HIGH indicates that the final result produced by the last operation is not to be interpreted as a number. The output in such cases is either an IEEE Not-a-Number (NAN) or a DEC-reserved operand.

OE Output Enable (Input; Active LOW)

When  $\overline{\text{OE}}$  is LOW, the contents of register F are placed on F<sub>0</sub>-F<sub>31</sub>. When  $\overline{\text{OE}}$  is HIGH, F<sub>0</sub>-F<sub>31</sub> assume a high-impedance state.

# ONEBUS Input Bus Configuration Control (Input)

A LOW on ONEBUS configures the input bus circuitry for two-input bus operation. A HIGH on ONEBUS configures the input bus circuitry for single-input bus operation.

OVERFLOW Overflow Flag (Output; Active HIGH)

A HIGH indicates that the last operation produced a final result that overflowed the floating-point format.

PROJ/AFF Projective/Affine Mode Select (Input)

Choice of projective or affine mode determines the way in which infinities are handled in IEEE mode. A LOW on PROJ/AFF selects affine mode; a HIGH selects projective mode.

R<sub>0</sub> - R<sub>31</sub> R Operand Bus (Input) R<sub>0</sub> is the least significant bit.

RND<sub>0</sub>, RND<sub>1</sub> Rounding Mode Selects (Input)

$\mbox{RND}_0$  and  $\mbox{RND}_1$  select one of four rounding modes. See Table 5 for a list of rounding modes and the corresponding control codes.

S<sub>0</sub>-S<sub>31</sub> S Operand Bus (Input)

So is the least significant bit.

S16/32 16- or 32-Bit I/O Mode Select (Input)

A LOW on S16/ $\overline{32}$  selects the 32-bit I/O mode; a HIGH selects the 16-bit I/O mode. In 32-bit mode, input and output buses are 32 bits wide. In 16-bit mode, input and output buses are 16 bits wide, with the least and most significant portions of the 32-bit input and output words being placed on the buses during the HIGH and LOW portions of CLK, respectively.

UNDERFLOW Underflow Flag (Output; Active HIGH)

A HIGH indicates that the last operation produced a rounded result that underflowed the floating-point format.

ZERO Zero Flag (Output; Active HIGH)

A HIGH indicates that the last operation produced a final result of zero.

# **Definition of Terms**

# Affine Mode

One of two modes affecting the handling of operations on infinities — see the **Operations with Infinities** section under **Operations in IEEE Mode**.

# **Biased Exponent**

The true exponent of a floating-point number, plus a constant. For IEEE floating-point numbers, the constant is 127; for DEC floating-point numbers, the constant is 128. See also **True Exponent**.

# Bus

Data input or output channel for the floating-point processor.

# **DEC-Reserved Operand**

A DEC floating-point number that is interpreted as a symbol and has no numeric value. A DEC-reserved operand has a sign of 1 and a biased exponent of 0.

#### **Destination Format**

The format of the final result produced by the floating-point ALU. The destination format can be IEEE floating point, DEC floating point, or integer.

#### Final Result

The result produced by the floating-point ALU.

### Fraction

The 23 least-significant bits of the mantissa.

#### Infinitely Precise Result

The result that would be obtained from an operation if both exponent range and precision were unbounded.

#### Input Operands

The value or values on which an operation is performed. For example, the addition 2 + 3 = 5 has input operands 2 and 3.

#### Mantissa

The portion of a floating-point number containing the number's significant bits. For the floating-point number 1.101  $\times$  2<sup>-3</sup>, the mantissa is 1.101.

#### NAN (Not-a-Number)

An IEEE floating-point number that is interpreted as a symbol and has no numeric value. A NAN has a biased exponent of  $255_{10}$  and a non-zero fraction.

#### Port

Data input or output channel for the floating-point ALU.

# **Projective Mode**

One of two modes affecting the handling of operations on infinities — see the **Operations with Infinities** section under **Operation in IEEE Mode**.

#### Rounded Result

The result produced by rounding the infinitely precise result to fit the destination format.

#### True Exponent (or Exponent)

Number representing the power of two by which a floating-point number's mantissa is to be multiplied. For the floating-point number  $1.101 \times 2^{-3}$ , the true exponent is -3.

# **FUNCTIONAL DESCRIPTION**

# Architecture

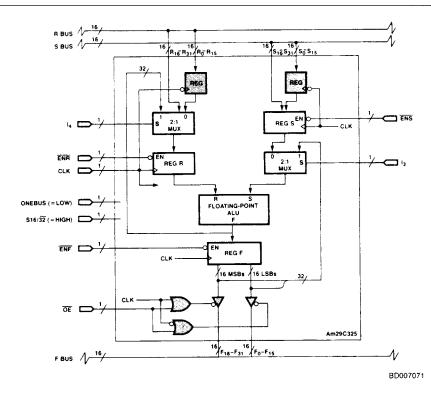

The Am29C325 comprises a high-speed, floating-point ALU, a status flag generator, and a 32-bit data path.

# Floating-Point ALU

The floating-point ALU performs 32-bit floating-point operations. It also performs floating-point-to-integer conversions, integer-to-floating-point floating-point conversions, and conversions between the IEEE and DEC formats. The ALU has two 32-bit input ports, R and S, and a 32-bit output port, F.

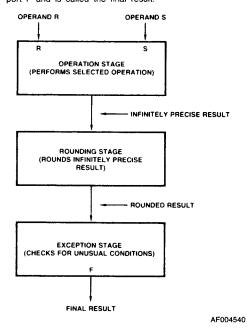

Conceptually, the process performed by the ALU can be divided into three stages (see Figure 1). The operation stage performs the arithmetic operation selected by the user; the output of this section is referred to as the infinitely precise result of the operation. The rounding stage rounds the infinitely precise result to fit in the destination format; the output of this stage is called the rounded result. The last stage checks for exceptional conditions. If no exceptional condition is found, the rounded result is passed through this stage. If some exceptional condition is found (e.g., overflow, underflow, or an invalid operation), this section may replace the rounded result with another output, such as  $+\infty$ ,  $-\infty$ , a NAN, or a DEC-

reserved operand. The output of this last stage appears on port F and is called the final result.

Figure 1. Conceptual Model of the Process Performed by the Floating-Point ALU

The ALU performs one of eight operations; the operation to be performed is selected by placing the appropriate control code on lines  $I_0$ – $I_2$ . Table 1 gives the control codes corresponding to each of the eight operations.

The floating-point addition operation (R PLUS S) adds the floating-point numbers on ports R and S and places the floating-point result on port F. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the addition is performed in IEEE floating-point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the addition is performed in DEC format.

The floating-point subtraction operation (R MINUS S) subtracts the floating-point number on port S from the floating-point number on port R and places the floating-point result on port F. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the subtraction is performed in IEEE floating-point point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the subtraction is performed in DEC format.

The floating-point multiplication operation (R TIMES S) multiplies the floating-point numbers on ports R and S and places the floating-point result on port F. In IEEE mode (IEEE/DEC = HIGH) the multiplication is performed in IEEE floating-point format; in DEC mode (IEEE/DEC = LOW) the multiplication is performed in DEC format.

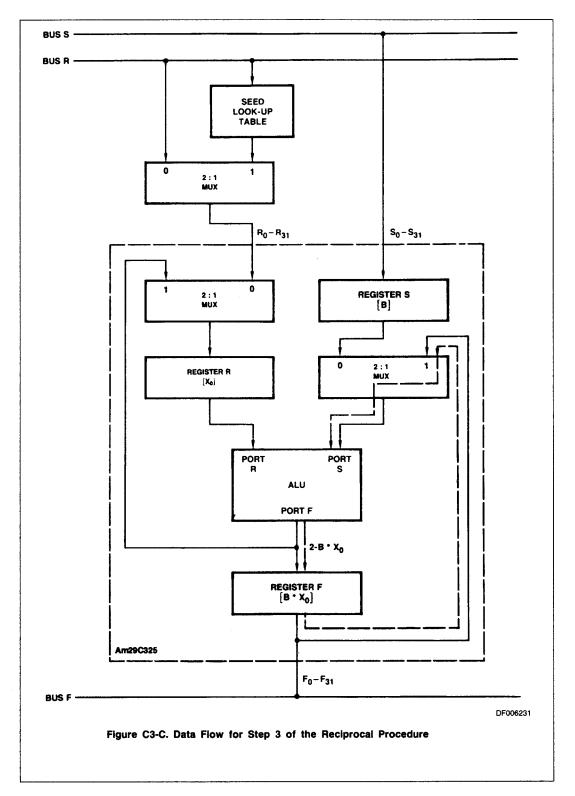

The floating-point constant subtraction (2 MINUS S) operation subtracts the floating-point value on port S from 2 and places the result on port F. The operand on port R is not used in this operation; its value will not affect the operation in any way. In IEEE mode (IEEE/DEC = HIGH) the operation is performed in IEEE floating-point format; in DEC mode (IEEE/DEC = LOW) the operation is performed in DEC format. This operation is

used to support Newton-Raphson floating-point division; a description of its use appears in **Appendix C.**

The integer-to-floating-point conversion (INT-TO-FP) operation takes a 32-bit, two's complement integer on port R and places the equivalent floating-point value on port F. The

operand on port S is not used in this operation; its value will not affect the operation in any way. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the result is delivered in IEEE format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the result is delivered in DEC format.

TABLE 1. ALU OPERATION SELECT

| 12 | 11 | lo | Operation                                        | Output Equation                  |

|----|----|----|--------------------------------------------------|----------------------------------|

| 0  | 0  | 0  | Floating-point addition (R PLUS S)               | F = R + S                        |

| 0  | 0  | 1  | Floating-point subtraction (R MINUS S)           | F = R - S                        |

| 0  | 1  | 0  | Floating-point multiplication (R TIMES S)        | F = R * S                        |

| 0  | 1  | 1  | Floating-point constant subtraction (2 MINUS S)  | F = 2 - S                        |

| 1  | 0  | 0  | Integer-to-floating-point conversion (INT-TO-FP) | F (floating-point) = R (integer) |

| 1  | 0  | 1  | Floating-point-to-integer conversion (FP-TO-INT) | F (integer) = R (floating-point) |

| 1  | 1  | 0  | IEEE-TO-DEC format conversion (IEEE-TO-DEC)      | F (DEC format) = R (IEEE format) |

| 1  | 1  | 1  | DEC-TO-IEEE format conversion (DEC-TO-IEEE)      | F (IEEE format) = R (DEC format) |

The floating-point-to-integer conversion (FP-TO-INT) operation takes a floating-point number on port R and places the equivalent 32-bit, two's complement integer value on port F. The operand on port S is not used in this operation; its value will not affect the operation in any way. In IEEE mode (IEEE/DEC = HIGH) the operand on port R is interpreted using the IEEE floating-point format; in DEC mode (IEEE/DEC = LOW) it is interpreted using the DEC floating-point format.

The IEEE-to-DEC conversion operation (IEEE-TO-DEC) takes an IEEE-format floating-point number on port R and places the equivalent DEC-format floating-point number on port F. The operand on port S is not used in this operation; its value will not affect the operation in any way. The operation can be performed in either IEEE mode (IEEE/DEC = HIGH) or DEC mode (IEEE/DEC = LOW).

The DEC-to-IEEE conversion operation (DEC-TO-IEEE) takes a DEC-format floating-point number on port R and places the equivalent IEEE-floating-point number on port F. The operand on port S is not used in this operation; its value will not affect the operation in any way. The operation can be performed in either IEEE mode (IEEE/DEC = HIGH) or DEC mode (IEEE/DEC = LOW).

# Status Flag Generator

The status flag generator controls the state of six flags that report the status of floating-point ALU operations. The flags indicate when an operation is invalid (e.g.,  $\infty$  times 0) or when an operation has produced an overflow, an underflow, a non-numerical result (e.g., a NAN- or DEC-reserved operand), an inexact result, or a result of zero. The flags represent the status of the most recently performed operation. Flag status is stored in the flag status register on the LOW-to-HIGH transition of CLK. When the output register feedthrough control FT1 is HIGH, the flag status register is made transparent.

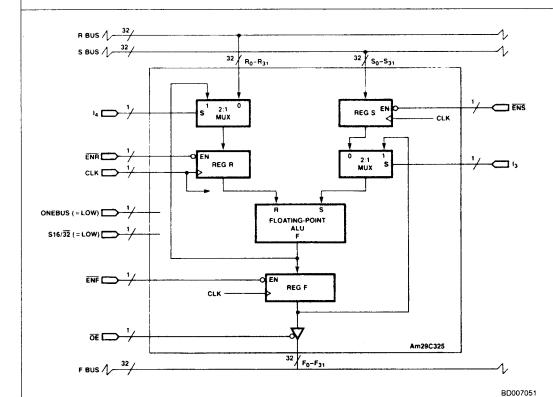

# Data Path

The 32-bit data path consists of the R and S input buses; the F output bus; data registers R, S, and F; the register R input multiplexer; and the ALU port S input multiplexer.

Input operands enter the floating-point processor through the 32-bit R and S input buses, R $_0$ -R $_{31}$  and S $_0$ -S $_{31}$ . Results of operations appear on the 32-bit F bus, F $_0$ -F $_{31}$ . The F bus assumes a high-impedance state when output enable  $\overline{OE}$  is HIGH

The R and S registers store input operands; the F register stores the final result of the floating-point ALU operation. Each register has an independent clock enable (ENR, ENS, and ENF). When a register's clock enable is LOW, the register stores the data on its input at the LOW-to-HIGH transition of CLK; when the clock enable is HIGH, the register retains its current data. All data registers are fully edge-triggered — both the input data and the register enable need only meet modest setup and hold time requirements. Registers R and S can be made transparent by setting FT0, the input register feed-through control, HIGH. Register F can be made transparent by setting FT1, the output register feedthrough control, HIGH.

The register R input multiplexer selects either the R input bus or the floating-point ALU's F port as the input to register R. Selection is controlled by  $I_4 - a$  LOW selects the R input bus; a HIGH selects the ALU F port. The ALU port S input multiplexer selects either register S or register F as the input to the floating-point ALU's S port. Selection is controlled by  $I_3 - a$  LOW selects register S; a HIGH selects register F.

Data selected by  $I_3$  and  $I_4$  is described in Table 2. When registers R and S are transparent (FT $_0$  = HIGH), multiplexer select  $I_4$  must be kept LOW, so that the register R input multiplexer selects  $R_0$ -R $_3$ 1. When register F is transparent (FT $_1$  = HIGH), multiplexer select  $I_3$  must be kept LOW, so that the ALU port S input multiplexer selects register S.

TABLE 2. MUX SELECT

| l <sub>3</sub> | Data selected for floating-point ALU S port |

|----------------|---------------------------------------------|

| 0              | Register S                                  |

| 1              | Register F                                  |

| 14             | Data selected for register R input          |

| 0              | R bus                                       |

| 1              | Floating-point ALU port F                   |

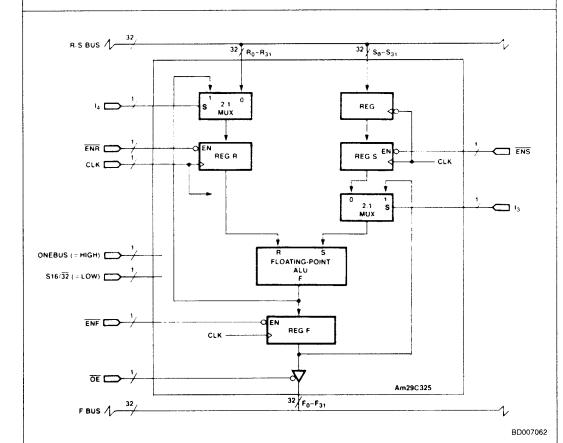

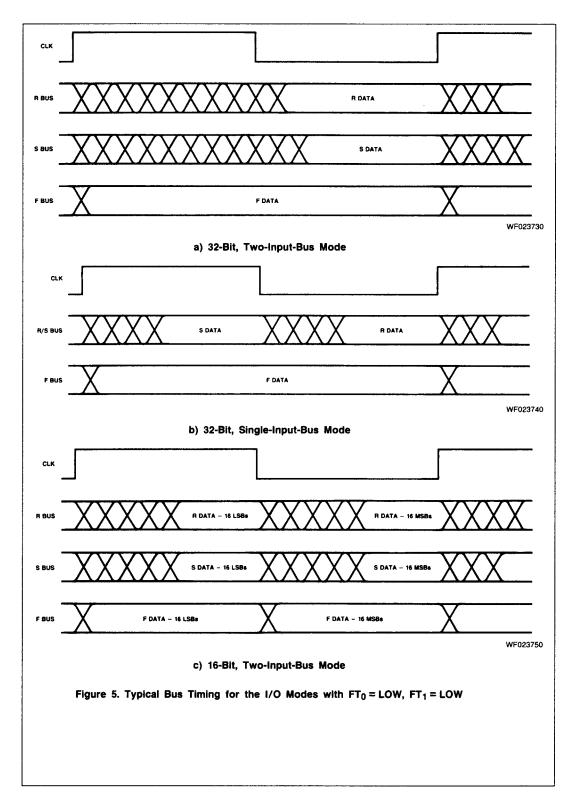

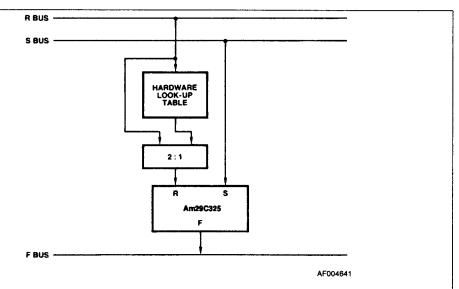

# I/O Modes

The Am29C325 datapath can be configured in one of three I/O modes: a 32-bit, two-input bus mode; a 32-bit, single-input bus mode; and a 16-bit, two-input bus mode. These modes affect only the manner in which data is delivered to and taken from the Am29C325; operation of the floating-point ALU is not altered. The I/O mode is selected with the ONEBUS and S16/32 controls. Table 3 lists the control codes needed to invoke each I/O mode.

TABLE 3. I/O MODE SELECTION

| S16/32 | ONEBUS | I/O Mode                         |

|--------|--------|----------------------------------|

| 0      |        | 32-bit, two-input-bus mode       |

| 0      | 1      | 32-bit, single-input-bus mode*   |

| 1      |        | 16-bit, two-input-bus mode*      |

| 1      | 1      | Illegal I/O mode selection value |

<sup>\*</sup>FT0 must be held LOW in this mode (see text).

# 32-Bit, Two-Input Bus Mode

In this I/O mode, the R and S buses are configured as independent 32-bit input buses, and the F bus is configured as a 32-bit output bus. Figure 2 is a functional block diagram of the Am29C325 in this I/O mode.

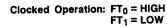

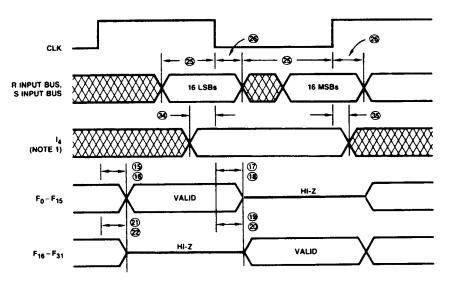

R and S operands are taken from their respective input buses and clocked into the R and S registers on the LOW-to-HIGH transition of CLK. Register F is also clocked on the LOW-to-HIGH transition of CLK. Figure 5a depicts typical I/O timing in this mode.

Figure 2. Functional Block Diagram for the 32-Bit, Two-Input Bus Mode

2-14

# 32-Bit, Single-Input Bus Mode

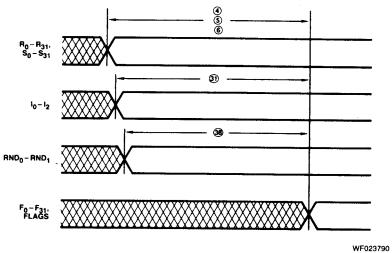

In this I/O mode, the R and S buses are connected to a single 32-bit multiplexed input data bus; the F bus is configured as an independent 32-bit output bus. Figure 3 is a functional block diagram of the Am29C325 in this I/O mode. Note that both the R and S bus lines must be wired to the input bus.

R and S operands are multiplexed onto the input bus by the host system. The S operand is clocked from the input bus into a temporary holding register on the HIGH-to-LOW transition of CLK and is transferred to register S on the LOW-to-HIGH

transition of CLK. The R operand is clocked from the input bus into register R on the LOW-to-HIGH transition of CLK. Register F is clocked on the LOW-to-HIGH transition of CLK. Figure 5b depicts typical I/O timing in this mode.

When placed in this I/O mode, the data path will not function properly if the R and S registers are made transparent. Therefore, input register feedthrough control FT<sub>0</sub> must be held LOW in this mode.

Figure 3. Functional Block Diagram for the 32-Bit, Single-Input Bus Mode

Am29C325

2-15

# 16-Bit, Two-Input Bus Mode

In this I/O mode, the R and S buses are configured as independent 16-bit input buses, and the F bus is configured as a 16-bit output bus. Figure 4 is a functional block diagram of the Am29C325 in this I/O mode. Note that the 16 least significant bits (LSBs) and 16 most significant bits (MSBs) of the R, S, and F buses must be wired to their respective system buses in parallel.

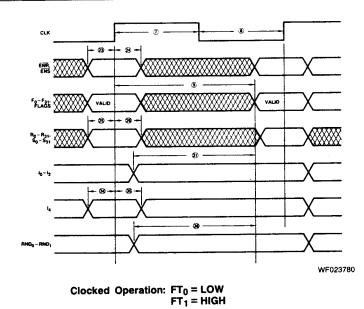

Thirty-two-bit operands are passed along the 16-bit data buses by time-multiplexing the 16 LSBs and 16 MSBs of each 32-bit word. For the R input bus, the host system multiplexes the 16 LSBs and 16 MSBs of the R operand onto the 16-bit R bus. The 16 LSBs of the R operand are stored in a temporary holding register on the HIGH-to-LOW transition of CLK. The 16 MSBs are clocked into register R on the LOW-to-HIGH transition of CLK; at the same time, the 16 LSBs are transferred from the temporary holding register to register R. Transfer of data from the S input bus to the S register takes place in a similar fashion. Register F is clocked on the LOWto-HIGH transition of CLK. Circuitry internal to the Am29C325 multiplexes data from register F onto the 16-bit output bus by enabling the 16 LSBs of the F output bus when CLK is HIGH and enabling the 16 MSBs of the F output bus when CLK is LOW. Figure 5c depicts typical I/O timing in this mode.

When placed in this I/O mode, the data path will not function properly if the R and S registers are made transparent. Therefore, input register feedthrough control FT<sub>0</sub> must be held LOW in this mode. Caution must also be taken in controlling the register R input multiplexer control line, I<sub>4</sub>, in this I/O mode. I<sub>4</sub> should be changed only when CLK is HIGH, in

addition to meeting the setup and hold time requirements given in the **Switching Characteristics** section.

#### Operation in IEEE Mode

When input signal IEEE/DEC is HIGH, the IEEE mode of operation is selected. In this mode the Am29C325 uses the floating-point format set forth in the IEEE Proposed Standard for Binary Floating-Point Arithmetic, P754. In addition, the IEEE mode complies with most other aspects of single-precision floating-point operation outlined in the proposed standard — differences are discussed in **Appendix A**.

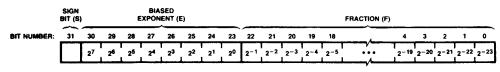

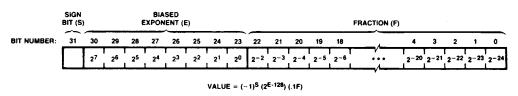

#### **IEEE Floating-Point Format**

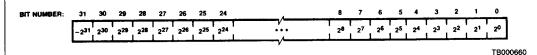

The IEEE single-precision floating-point word is 32 bits wide and is arranged in the format shown in Figure 6. The floating-point word is divided into three fields: a single-bit sign, an 8-bit biased exponent, and a 23-bit fraction.

The sign bit indicates the sign of the floating-point number's value. Non-negative values have a sign of 0; negative values, a sign of 1. The value zero may have either sign.

The biased exponent is an 8-bit unsigned integer field representing a multiplicative factor of some power of two. The bias value is 127. If, for example, the multiplicative factor for a floating-point number is to be 2<sup>a</sup>, the value of the biased exponent would be a +127; "a" is called the true exponent.

The fraction is a 23-bit unsigned fraction field containing the 23 LSBs of the floating-point number's 24-bit mantissa. The weight of fraction's MSB is 2<sup>-1</sup>; the weight of the LSB is 2<sup>-23</sup>.

Figure 4. Functional Block Diagram for the 16-Bit, Two-Input Bus Mode

A floating-point number is evaluated or interpreted per the following conventions:

```

let s = sign bit e = biased exponent f = fraction if e = 0 and f = 0...value = (-1)^{S*}(0) ( + 0, -0) if e = 0 and f \neq 0...value = denormalized number if 0 < e < 255...value = (-1)^{S*}(2^{e-127})^{*}(1.f) (normalized number) if e = 255 and f = 0...value = (-1)^{S*}(\infty) (+ \infty, -\infty) if e = 255 and f \neq 0...value = not-a-number (NAN)

```

**Zero:** The value zero can have either a positive or negative sign. Rules for determining the sign of a zero produced by an operation are given in the **Sign Bit** section.

**Denormalized Number:** A denormalized number represents a quantity with magnitude less than 2<sup>-126</sup> but greater than zero.

**Normalized Number:** A normalized number represents a quantity with magnitude greater than or equal to  $2^{-126}$  but less than  $2^{128}$ .

# Example 1:

The number + 3.5 can be represented in floating-point format as follows:

$$+3.5 \approx 11.1_2 \times 2^0$$

= 1.11<sub>2</sub> x 2<sup>1</sup>

$$sign = 0$$

biased exponent =

$$1_{10} + 127_{10} = 128_{10}$$

=  $10000000_2$

Concatenating these fields produces the floating-point word  $40600000_{16}. \\$

VALUE = (-1)S (2E-127) (1.F)

TR000640

Figure 6. IEEE Mode Single-Precision Floating-Point Format

#### Example 2:

The number -11.375 can be represented in floating-point format as follows:

$$-11.375 = -1011.011_2 \times 2^0$$

= -1.011011<sub>2</sub> x 2<sup>3</sup>

sign = 1

biased exponent =  $3_{10} + 127_{10} = 130_{10}$ =  $10000010_2$

Concatenating these fields produces the floating-point word C1360000<sub>16</sub>.

Infinity: Infinity can have either a positive or negative sign. The way in which infinities are interpreted is determined by the state of the projective/affine mode select, PROJ/AFF.

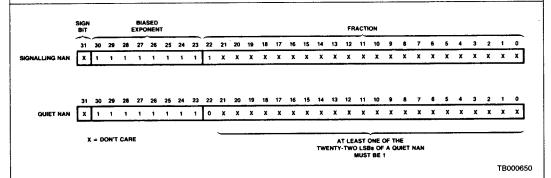

**Not-a-Number:** A not-a-number, or NAN, does not represent a numeric value but is interpreted as a signal or symbol. NANs are used to indicate invalid operations and as a means of passing process status information through a series of calculations. NANs arise in two ways: 1) they can be generated by the Am29C325 to indicate that an invalid operation has taken place (e.g.,  $\infty$  x 0), or 2) be provided by the user as an input operand. There are two types of NANs, signalling and quiet (see Figure 7 for formats).

# **IEEE Mode Integer Format**

Integer numbers are represented as 32-bit, two's complement words (Figure 8 depicts the integer format). The integer word can represent a range of integer values from  $-2^{31}$  to  $2^{31}-1$ .

Figure 7. Signalling and Quiet NAN Formats

Figure 8, 32-Bit Integer Format

### **Operations**

All eight floating-point ALU operations discussed in the Functional Description section can be performed in IEEE mode. Various exceptional aspects of the R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, INT-TO-FP, and FP-TO-INT operations for this mode are described below. The IEEE-TO-DEC and DEC-TO-IEEE operations are discussed separately in the IEEE-TO-DEC AND DEC-TO-IEEE Operations section.

Operations with NANs: NANs arise in two ways: 1) they can be generated by the Am29C325 to indicate that an invalid operation has taken place (e.g., ∞ x 0), or 2) be provided by the user as an input operand. There are two types of NANs, signalling and quiet (see Figure 7 for formats).

Signalling NANs set the invalid operation flag when they appear as an input operand to an operation. They are useful for indicating uninitialized variables, or for implementing user-

designed extensions to the operations provided. The ALU never produces a signalling NAN as the final result of an operation.

Quiet NANs are generated for invalid operations. When they appear as an input operand, they are passed through most operations without setting the invalid flag, the floating-point-to-integer conversion operation being the exception.

The sign of any input operand NAN is ignored. All quiet NANs produced as the final result of an operation have a sign of 0.

When a NAN appears as an input operand, the final result of the operation is a quiet NAN that is created by taking the input NAN and forcing bit 22 LOW and bit 21 HIGH. If an operation has two NANs as input operands, the resulting quiet NAN is created using the NAN on the R port.

When a quiet NAN is produced as the final result of an invalid operation whose input operand or operands are not NANs, the resulting NAN will always have the value 7FA00000<sub>16</sub>.

The NAN flag will be HIGH whenever an operation produces a NAN as a final result.

#### Example 1:

Suppose the floating-point addition operation is performed with the following input operands:

R port: 3F800000<sub>16</sub> (1.0\*2<sup>0</sup>) S port: 7FC12345<sub>16</sub> (signalling NAN)

Result: The signalling NAN on the S port is converted to a quiet NAN by forcing bit 22 LOW and bit 21 HIGH. The operation's final result will be 7FA12345<sub>16</sub>. Since one of the two input operands is a signalling NAN, the invalid flag will be HIGH; the NAN flag will also be HIGH.

# Example 2:

Suppose the floating-point multiplication operation is performed with the following input operands:

R port: FFF11111<sub>16</sub> (signalling NAN) S port: 7FC22222<sub>16</sub> (quiet NAN)

Result: Since both input operands are NANs, the NAN on the R port is chosen for output. In addition to forcing bit 22 LOW, the sign bit (bit 31) is set LOW (bit 21 is already HiGH, and need not be changed). The operation's final result will be 7FB11111<sub>16</sub>. Since one of the two input operands is a signalling NAN, the invalid flag is HIGH; the NAN flag will also be HIGH.

### Example 3:

Suppose the floating-point subtraction operation is performed with the following input operands:

R port: FF800001<sub>16</sub> (quiet NAN) S port: 7F800000<sub>16</sub> (+∞)

Result: To create the final result, the quiet NANs sign bit (bit 31) is forced LOW and bit 21 is forced HIGH (bit 22 is already LOW, and need not be changed). The final result will be 7FA00001<sub>16</sub>. The NAN flag will be HIGH.

Operations with Denormalized Numbers: The proposed IEEE standard incorporates denormalized numbers to allow a means of gradual underflow for operations that produce nonzero results too small to be expressed as a normalized floating-point number. The Am29C325 does not support gradual underflow. If a floating-point operation produces a non-zero rounded result that is not large enough to be expressed as a normalized floating-point number, the final

result will be a zero of the same sign; the inexact, underflow, and zero flags will be HIGH. If an input operand is a denormalized number, the floating-point ALU will assume that operand to be a zero of the same sign.

Operations Producing Overflows: If an operation has a finite input operand or operands and if the operation produces a rounded result that is too large to fit in the destination format, the operation is said to have overflowed.

A floating-point overflow occurs if an R PLUS S, R MINUS S, R TIMES S, or 2 MINUS S operation with finite input operand(s) produces a result which, after rounding, has a magnitude greater than or equal to 2<sup>128</sup>. Positive or negative infinity will appear as the final result if the rounded result is positive or negative, respectively, and the overflow and inexact flags will be HIGH.

Integer overflow occurs when the floating-point-to-integer conversion operation attempts to convert a number which, after rounding, is greater than  $2^{31}$  – 1 or less than  $-2^{31}$ . The final result will be quiet NAN 7FA00000<sub>16</sub>, and the invalid operation and NAN flags will be HIGH. Note that the overflow and inexact flags remain LOW for integer overflow.

Operations Producing Underflows: If an operation produces a floating-point rounded result having a magnitude too small to be expressed as a normalized floating-point number but greater than zero, that operation is said to have underflowed. Underflow occurs when an R PLUS S, R MINUS S, or R TIMES S operation produces a result which, after rounding, has a magnitude in the range:

$$0 < \text{magnitude} < 2^{-126}$$

.

In such cases, the final result will be +0 (00000000<sub>16</sub>) if the rounded result is non-negative and -0 (80000000<sub>16</sub>) if the rounded result is negative. The underflow, inexact, and zero flags will be HIGH.

Underflow does not occur if the destination format is integer. If the infinitely precise result of a floating-point-to-integer conversion has a magnitude greater than 0 and less than 1 but the rounded result is 0, the underflow flag remains LOW.

**Operations with Infinities:** In most cases, positive and negative infinity are valid inputs for the R PLUS S, R MINUS S, R TIMES S, and 2 MINUS S operations. Those cases for which infinities are not valid inputs for these operations are listed in Table 4.

Infinities in IEEE mode can be handled either as projective or affine. The projective mode is selected when PROJ/ĀFF is HIGH; the affine mode is selected when PROJ/ĀFF is LOW. The only differences between the modes that are relevant to Am29C325 operation occur during the addition and subtraction of infinities:

| Operation   | Affine<br>Mode | Projective Mode                                                            |

|-------------|----------------|----------------------------------------------------------------------------|

| (+∞) + (+∞) | Output +∞      | Output 7FA00000 <sub>16</sub><br>(quiet NAN), set invalid and<br>NAN flags |

| (-∞) + (-∞) | Output -∞      | Output 7FA00000 <sub>16</sub><br>(quiet NAN), set invalid and<br>NAN flags |

| (+∞) – (–∞) | Output +∞      | Output 7FA00000 <sub>16</sub><br>(quiet NAN), set invalid and<br>NAN flags |

| (-∞) - (+∞) | Output ~∞      | Output 7FA00000 <sub>16</sub><br>(quiet NAN), set invalid and<br>NAN flags |

2-20 Am29C325

If an R PLUS S, R MINUS S, or 2 MINUS S operation has infinity as an input operand or operands, the final result, if valid, is presumed to be exact. For example, adding  $+\infty$  and 2.0 will produce a final result of  $+\infty$ ; since the result is considered exact, the inexact flag remains LOW.

Invalid Operations: If an input operand is invalid for the operation to be performed, that operation is considered invalid. When an invalid operation is performed, the floating-point ALU produces a quiet NAN as the final result and the invalid operation flag goes HIGH. Table 4 lists the cases for which the invalid flag is HIGH in IEEE mode and the final results produced for these operations.

TABLE 4. IEEE MODE INVALID OPERATIONS

| Operation                          | Input Operand                                                     | Final Result                          |

|------------------------------------|-------------------------------------------------------------------|---------------------------------------|

| R PLUS S                           | or $(-\infty) + (-\infty)$                                        | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R PLUS S                           | $(+\infty) + (+\infty)$<br>or $(-\infty) + (-\infty)$ (Note 1)    | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R MINUS S                          | or $(-\infty) - (-\infty)$                                        | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R MINUS S                          | $(+\infty) - (-\infty)$<br>or $(-\infty) - (+\infty)$ (Note 1)    | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R TIMES S                          | (+0) * (+∞)<br>or (+0) * (-∞)<br>or (-0) * (+∞)<br>or (-0) * (-∞) | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R PLUS S<br>R MINUS S<br>R TIMES S | R or S is a signalling<br>NAN                                     | (Note 2)                              |

| 2 MINUS S                          | S is a signalling NAN                                             | (Note 2)                              |

| FP-TO-INT                          | R is a signalling or quiet NAN                                    | (Note 2)                              |

| FP-TO-INT                          | $R > 2^{31} - 1$<br>or $R < -(2^{31})$                            | 7FA00000 <sub>16</sub><br>(quiet NAN) |

Notes: 1. These cases are invalid in projective mode only.

Results for these operations are described in the Operations with NANs section.

# The Sign Bit

For most floating-point operations, the sign bit of the final result is unambiguous; i.e., there is only one sign bit value that yields a numerically correct result. Operations that produce an infinitely precise result of zero, however, present a problem, as the IEEE floating-point format allows for representation of both +0 and -0. The following rules can be used to determine the signs of zero produced in such cases.

**R PLUS S:** The operations +x + (-x) and -x + (+x) produce a final result of zero; the sign of the zero is dependent on the rounding mode:

Operations +0 + (-0) and -0 + (+0) produce a result of 0, with the sign of the result determined by the table above.

The operation +0 + (+0) produces a final result of +0; the operation -0 + (-0) produces a final result of -0.

**R MINUS S:** The operations +x - (+x) and -x - (-x) produce a final result of zero; the sign of the zero is dependent on the rounding mode:

| Rounding Mode    | Sign of Result |

|------------------|----------------|

| Round to nearest | 0              |

| Round toward -∞  | 1              |

| Round toward +∞  | 0              |

| Round toward 0   | 0              |

Operations +0 - (+0) and -0 - (-0) produce a result of 0, with the sign of the result determined by the table above.

The operation +0-(-0) produces a final result of +0; the operation -0-(+0) produces a final result of -0.

R TIMES S: The sign of any multiplication result other than a NAN is the exclusive OR of the signs of the input operands. Therefore, if x is non-negative,

- +0 times +x produces a final result of +0,

- +0 times -x produces a final result of -0,

- -0 times +x produces a final result of -0,

- -0 times -x produces a final result of +0.

**2 MINUS S:** If S equals 2, the final result is -0 for the round toward  $-\infty$  mode and +0 for all other rounding modes.

#### Rounding

Rounding is performed whenever an operation produces an infinitely precise result that cannot be represented exactly in the destination format. For example, suppose a floating-point operation produces the infinitely precise result:

# 1.10101010101010101010101\01 x 2<sup>3</sup>.

In this example, the fraction portion of the mantissa has 25 bits; the IEEE floating-point format can accommodate only 23. The backslash (\) in the mantissa represents the boundary between the first 23 bits of the fraction and any remaining bits. Rounding is the process by which this result is approximated by a representation that fits the destination format.

There are four rounding modes in IEEE mode: 1) round to nearest, 2) round toward  $+\infty$ , 3) round toward  $-\infty$ , and 4) round toward 0. The rounding mode is chosen using the rounding mode select lines, RND<sub>0</sub> and RND<sub>1</sub>. Table 5 lists the select states needed to obtain the desired rounding mode.

TABLE 5. ROUNDING MODE SELECT

| Rounding Mode    | Sign of Final Result | RND <sub>1</sub> | RND <sub>0</sub> | Rounding Mode    |

|------------------|----------------------|------------------|------------------|------------------|

| Round to nearest | 0                    | 0                | 0                | Round to nearest |

| Round toward -∞  | 1                    | 0                | 1                | Round toward -∞  |

| Round toward +∞  | 0                    | 1                | 0                | Round toward +∞  |

| Round toward 0   | 0                    | 1                | 1                | Round toward 0   |

Round to Nearest: In this rounding mode the infinitely precise result of an operation is rounded to the closest representation that fits in the destination format. If the infinitely precise result is exactly halfway between two representations, it is rounded to the representation having an LSB of zero. Rounding is performed both for floating-point and integer destination formats.

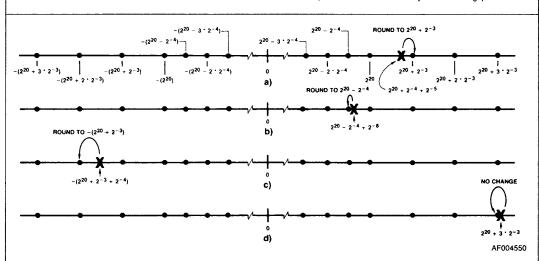

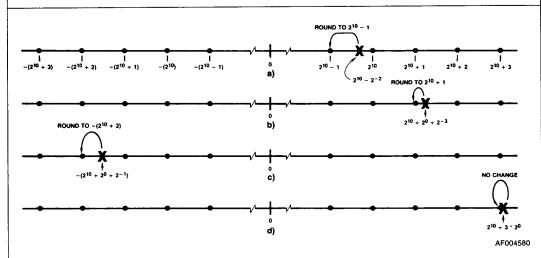

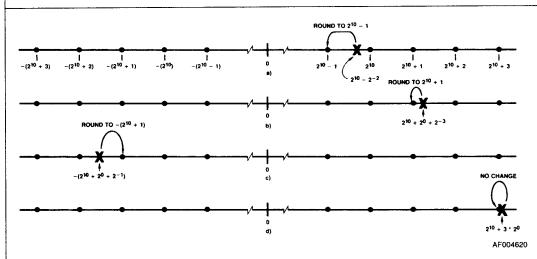

Figure 9 illustrates four examples of the round-to-nearest process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

#### Example 1:

In Figure 9(a), the infinitely precise result of an operation is:  $2^{20} + 2^{-4} + 2^{-5} = 1.00000000000000000000011 \times 2^{20}$

The result is rounded to the closest representable floatingpoint value,

$$2^{20} + 2^{-3} = 1.000000000000000000001 \times 2^{20}$$

#### Example 2:

In Figure 9(b), the infinitely precise result of an operation is:  $2^{20} - 2^{-4} + 2^{-8} =$

This result is rounded to the closest representable floatingpoint value,

#### Example 3:

In Figure 9(c), the infinitely precise result of an operation is:

$$-(2^{20} + 2^{-3} + 2^{-4})$$

= -1.00000000000000000000000001\1 x 2<sup>20</sup>

This result is exactly halfway between two representable floating-point values. Accordingly, it is rounded to the closest representation with an LSB of zero, or

# Example 4:

In Figure 9(d), the infinitely precise result of an operation is:

This result can be represented exactly in the floating-point format, and is left unaltered by the rounding process.

Figure 9. Floating-Point Rounding Examples for Round-to-Nearest Mode

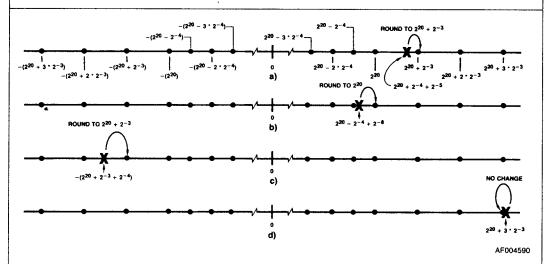

Figure 10 illustrates four examples of the round-to-nearest process for operations having an integer destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be represented exactly in the integer format.

# Example 1:

In Figure 10(a), the infinitely precise result of an operation is:

The result is rounded to the closest representable integer value.

$$2^{10} = 00...010000000000$$

# Example 2:

In Figure 10(b), the infinitely precise result of an operation is:

$$2^{10} + 2^{0} + 2^{-3} = 00...01000000001.001$$

This result is rounded to the closest representable integer value.

$$2^{10} + 2^0 = 00...010000000001$$

# Example 3:

In Figure 10(c), the infinitely precise result of an operation is:

$$-(2^{10} + 2^0 + 2^{-1}) = -11...1011111111110.1$$

This result is exactly halfway between two representable integer values. Accordingly, it is rounded to the closest representation with an LSB of zero, or

# Example 4:

In Figure 10(d), the infinitely precise result of an operation is:

$$2^{10} + 3^{*}2^{0} = 00...010000000011$$

This result can be represented exactly in the integer format and is left unaltered by the rounding process.

Figure 10. Integer Rounding Examples for Round-to-Nearest Mode

Round Toward - : In this rounding mode the result of an operation is rounded to the closest representation that is less than or equal to the infinitely precise result and which fits the destination format. Rounding is performed both for floatingpoint and integer destination formats.

Figure 11 illustrates four examples of the round toward -∞ process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

#### Example 1:

In Figure 11(a), the infinitely precise result of an operation is:

This result cannot be represented exactly in floating-point format and is rounded to the next-smaller floating-point representation:

### Example 2:

In Figure 11(b), the infinitely precise result of an operation is:

$$2^{20} - 2^{-4} + 2^{-8} =$$

1.11111111111111111111111\0001 x 2<sup>19</sup>

This result cannot be represented exactly in floating-point format and is rounded to the next-smaller floating point representation:

### Example 3:

In Figure 11(c), the infinitely precise result of an operation is:

$$-(2^{20} + 2^{-3} + 2^{-4})$$

$$-(2^{20} + 2^{-3} + 2^{-4}) =$$

-1.0000000000000000000001\1 x 2<sup>20</sup>

This result cannot be represented exactly in floating-point format and is rounded to the next-smaller floating-point representation.

#### Example 4:

In Figure 11(d), the infinitely precise result of an operation is:  $2^{20} + 3^2 - 3^2 = 1.00000000000000000000011 \times 2^{20}$

This result can be represented exactly in the floating-point format and is left unaltered by the rounding process.

Figure 11. Floating-Point Rounding Examples for Round Toward -∞ Mode

Figure 12 illustrates four examples of the round toward  $-\infty$  process for operations having an integer destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be exactly represented in the integer format.

# Example 1:

In Figure 12(a), the infinitely precise result of an operation is:  $2^{10}-2^{-2}=00...001111111111111111$

The result is rounded to the next-smaller representable integer value,

$$2^{10} - 2^0 = 00...0011111111111$$

# Example 2:

In Figure 12(b), the infinitely precise result of an operation is:  $2^{10} + 2^0 + 2^{-3} = 00...01000000001.001$

This result is rounded to the next-smaller representable integer value,

$$2^{10} + 2^0 = 00...010000000001$$

# Example 3:

In Figure 12(c), the infinitely precise result of an operation is:

$$-(2^{10} + 2^0 + 2^{-1}) = 11...1011111111110.1$$

This result is rounded to the next-smaller representable integer value:

$$-(2^{10} + 2^{*}2^{0}) = 11...1011111111110$$

# Example 4:

In Figure 12(d), the infinitely precise result of an operation is:

$$2^{10} + 3^{*}2^{0} = 00...010000000011$$

This result can be represented exactly in the integer format and is unaltered by the rounding process.

Figure 12. Integer Rounding Examples for Round Toward -∞ Mode

Round Toward +∞: In this rounding mode the result of an operation is rounded to the closest representation that is greater than or equal to the infinitely precise result and which fits the destination format. Rounding is performed both for floating-point and integer destination formats.

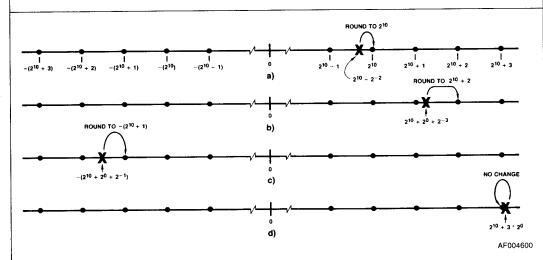

Figure 13 illustrates four examples of the round toward  $+\infty$  process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

#### Example 1:

This result cannot be represented exactly in floating-point format and is rounded to the next-larger floating-point representation:

$$2^{20} + 2^{-3} = 1.0000000000000000000001 \times 2^{20}$$

# Example 2:

In Figure 13(b), the infinitely precise result of an operation is:

This result cannot be represented exactly in floating-point format and is rounded to the next-larger floating point representation:

# Example 3:

In Figure 13(c), the infinitely precise result of an operation is:

$$-(2^{20} + 2^{-3} + 2^{-4}) =$$

This result cannot be represented exactly in floating-point format and is rounded to the next-larger floating-point representation.

$$-(2^{20} + 2^{-3}) = -1.00000000000000000001 \times 2^{20}$$

#### Example 4

In Figure 13(d), the infinitely precise result of an operation is:  $2^{20} + 3^2 - 3 = 1.0000000000000000011 \times 2^{20}$ .

This result can be represented exactly in the floating-point format — no rounding takes place.

Figure 13. Floating-Point Rounding Examples for Round Toward +∞ Mode

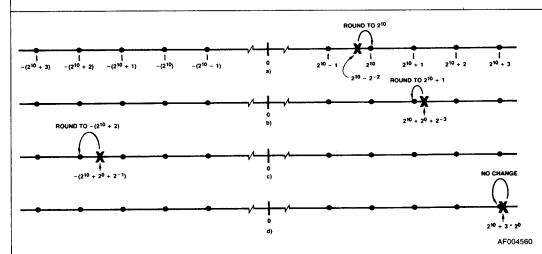

Figure 14 illustrates four examples of the round toward  $+\infty$  process for having an integer destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be exactly represented in the integer format.

# Example 1:

In Figure 14(a), the infinitely precise result of an operation is:

$$2^{10} - 2^{-2} = 00...0011111111111111111$$

The result is rounded to the next-larger representable integer value,

$$2^{10} = 00...010000000000$$

# Example 2:

In Figure 14(b), the infinitely precise result of an operation is:  $2^{10} + 2^0 + 2^{-3} = 00...01000000001.001$  This result is rounded to the next-larger representable integer value,

$$2^{10} + 2 \cdot 2^{0} = 00...010000000010$$

# Example 3:

In Figure 14(c), the infinitely precise result of an operation is:

$$-(2^{10} + 2^0 + 2^{-1}) = 11.1011111111110.1$$

This result is rounded to the next-larger representable integer value:

$$-(2^{10} + 2^0) = 11...10111111111110$$

# Example 4:

In Figure 14(d), the infinitely precise result of an operation is:

$$2^{10} + 3 \times 2^{0} = 00...010000000011$$

This result can be represented exactly in the integer format — no rounding takes place.

Figure 14. Integer Rounding Examples for Round Toward +∞ Mode

**Round Toward 0:** In this rounding mode the result of an operation is rounded to the closest representation whose magnitude is less than or equal to the infinitely precise result and which fits the destination format. Rounding is performed both for floating-point and integer destination formats.

Figure 15 illustrates four examples of the round toward 0 process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

#### Example 1:

In Figure 15(a), the infinitely precise result of an operation is:  $2^{20} + 2^{-4} + 2^{-5} =$

1.000000000000000000000000\11 x 2<sup>20</sup>

This result cannot be represented exactly in floating-point format and is rounded to:

Example 2:

In Figure 15(b), the infinitely precise result of an operation is:  $2^{20} - 2^{-4} + 2^{-8} =$

1.11111111111111111111111111\001 x 2<sup>19</sup>

This result cannot be represented exactly in floating-point format and is rounded to:

# Example 3:

In Figure 15(c), the infinitely precise result of an operation is:

$$-(2^{20} + 2^{-3} + 2^{-4}) =$$

-1.000000000000000000001\1 x 2<sup>20</sup>

This result cannot be represented exactly in floating-point format and is rounded to:

$$-(2^{20} + 2^{-3}) = -1.000000000000000000001 \times 2^{20}$$

# Example 4:

In Figure 15(d), the infinitely precise result of an operation is:  $2^{20} + 3^*2^{-3} = 1.0000000000000000111 \times 2^{20}$

This result can be represented exactly in the floating-point format and is unaffected by the rounding process.

Figure 15. Floating-Point Rounding Examples for Round Toward 0 Mode

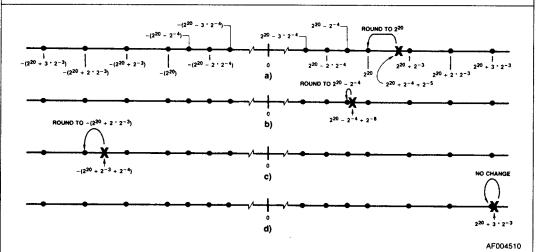

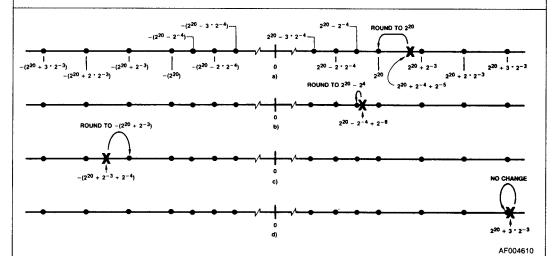

Figure 16 illustrates four examples of the round toward 0 process for operations having an integer destination format. The infinitely precise result of an operation is represented by an "X" on the number line; the black dots on the number line indicate those values that can be exactly represented in the integer format.

# Example 1:

In Figure 16(a), the infinitely precise result of an operation is:

The result is rounded to:

$$2^{10} - 2^0 = 00...0011111111111$$

# Example 2:

In Figure 16(b), the infinitely precise result of an operation is:

$$2^{10} + 2^{0} + 2^{-3} = 00...010000000001.001$$

The result is rounded to:

$$2^{10} + 2^0 = 00...010000000001$$

#### Example 3:

In Figure 16(c), the infinitely precise result of an operation is:

The result is rounded to:

$$-(2^{10} + 2^0) = 11...1011111111111$$

# Example 4:

In Figure 16(d), the infinitely precise result of an operation is:

$$2^{10} + 3*2^{0} = 00...010000000011$$

This result can be represented exactly in the integer format and is unaffected by the rounding process.

Figure 16. Integer Rounding Examples for Round Toward 0 Mode

# Flag Operation

The Am29C325 generates six status flags to monitor floatingpoint processor operation. The following is a summary of flag conventions in IEEE mode:

Invalid Operation Flag: The invalid operation flag is HIGH when an input operand is invalid for the operation to be performed. Table 4 lists the cases for which the invalid operation flag is HIGH in IEEE mode and the corresponding final result. In cases where the invalid operation flag is HIGH, the overflow, underflow, zero, and inexact flags are LOW; the NAN flag will be HIGH.

**Overflow Flag:** The overflow flag is HIGH if an R PLUS S, R MINUS S, R TIMES S, or 2 MINUS S operation with finite input operand(s) produces a result which, after rounding, has a magnitude greater than or equal to  $2^{128}$ . The final result will be  $+\infty$  or  $-\infty$ .

**Underflow Flag:** The underflow flag is HIGH if an R PLUS S, R MINUS S, or R TIMES S operation produces a result which, after rounding, has a magnitude in the range:  $0 < magnitude < 2^{-126}$ .

The final result will be +0 (00000000<sub>16</sub>) if the rounded result is non-negative and -0 (80000000<sub>16</sub>) if the rounded result is negative.

Inexact Flag: The inexact flag is HIGH if the final result of an R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, INT-TO-FP, or FP-TO-INT operation is not equal to the infinitely precise result. Note that if the underflow or overflow flag is HIGH, the inexact flag will also be HIGH.

Zero Flag: The zero flag is HIGH if the final result of an operation is zero. For operations producing an IEEE floating-point number, the flag accompanies outputs +0 (000000000<sub>16</sub>) and -0 (80000000<sub>16</sub>). For operations producing an integer, the flag accompanies the output 0 (00000000<sub>16</sub>).

NAN Flag: The NAN flag is HIGH if an R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, or FP-TO-INT operation produces a NAN as a final result.

# Operation in DEC Mode

When input signal IEEE/DEC is LOW, the DEC mode of operation is selected. In this mode the Am29C325 uses the single-precision floating-point format (floating F) set forth in

Digital Equipment Corporation's VAX Architecture Manual. In addition, the DEC mode complies with most other aspects of single-precision floating-point operation outlined in the manual — differences are discussed in **Appendix B**.

# **DEC Floating-Point Format**

The DEC single-precision floating-point word is 32 bits wide and is arranged in the format shown in Figure 17. The floating-point word is divided into three fields: a single-bit sign, an 8-bit biased exponent, and a 23-bit fraction.

The sign bit indicates the sign of the floating-point number's value. Non-negative values have a sign of 0, negative values a sign of 1.

The biased exponent is an 8-bit unsigned integer field representing a multiplicative factor of some power of two. The bias value is 128. If, for example, the multiplicative factor for a floating-point number is to be  $2^a$ , the value of the biased exponent would be a + 128; "a" is called the true exponent.

The fraction is a 23-bit unsigned fractional field containing the 23 LSBs of the floating-point number's 24-bit mantissa. The weight of this field's MSB is  $2^{-2}$ ; the weight of the LSB is  $2^{-24}$ .

A floating-point number is evaluated or interpreted per the following conventions:

let s = sign bit

e = biased exponent

f = fraction

if e=0 and s=0...value=0if e=0 and s=1...value=DEC-reserved operand if  $0 < e \le 255...value=(-1)^{S*}(2^{e-128})^*(.1f)$ (normalized number)

Zero: The value zero always has a sign of zero.

**DEC-Reserved Operand:** A DEC-reserved operand does not represent a numeric value but is interpreted as a signal or symbol. DEC-reserved operands are used to indicate invalid operations and operations whose results have overflowed the destination format. They may also be used to pass symbolic information from one calculation to another.

**Normalized Number:** A normalized number represents a quantity with magnitude greater than or equal to  $2^{-128}$  but less than  $2^{127}$ .

#### Example 1:

The number + 3.5 can be represented in floating-point format as follows:

$$+3.5 = 11.1_2 \times 2^0$$

= .111<sub>2</sub> x 2<sup>2</sup>

sign = 0

biased exponent =  $2_{10} + 128_{10} = 130_{10}$ =  $10000010_2$

Concatenating these fields produces the floating-point word 416000016.

#### Example 2:

The number -11.375 can be represented in floating-point format as follows:

$$-11.375 = -1011.011_2 \times 2^0$$

= -.1011011<sub>2</sub> x 2<sup>4</sup>

sign = 1

biased exponent =  $4_{10} + 128_{10} = 132_{10}$ =  $10000100_2$

Concatenating these fields produces the floating-point word C2360000<sub>16</sub>.

### **DEC Mode Integer Format**

DEC mode integer format is identical to that of the IEEE mode. Integer numbers are represented as 32-bit, two's complement words (Figure 8 depicts the integer format). The integer word can represent a range of integer values from  $-2^{31}$  to  $2^{31}$  – 1.

#### Operations

All eight floating-point ALU operations discussed in the **General Description** section can be performed in DEC mode.

TB000671

Figure 17. DEC-Mode Floating-Point Format

Various exceptional aspects of the R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, INT-TO-FP, and FP-TO-INT operations for this mode are described below. The IEEE-TO-DEC and DEC-TO-IEEE operations are discussed separately in the IEEE-TO-DEC and DEC-TO-IEEE Operations section.

Operations with DEC-Reserved Operands: DEC-reserved operands arise in two ways: 1) they can be generated by the Am29325 to indicate that an invalid operation or floating-point

overflow has taken place, or 2) be provided by the user as an input operand.

When a DEC-reserved operand appears as an input operand, the final result of the operation is the same DEC-reserved operand. If an operation has two DEC-reserved operands as inputs, the DEC-reserved operand on the R port becomes the final result.

The NAN flag will be HIGH whenever an operation produces a DEC-reserved operand as a final result.

# Example 1:

Suppose the floating-point addition operation is performed with the following input operands:

R port: 40800000<sub>16</sub> (0.1\*2<sup>1</sup>)

S port: 8001234516 (DEC-reserved operand)

Result: This operation produces the DEC-reserved operand on the S port, 80012345<sub>16</sub>, as the final result. The NAN flag will be HIGH.

#### Example 2:

Suppose the floating-point multiplication operation is performed with the following input operands:

R port: 80765432<sub>16</sub> (DEC-reserved operand) S port: 80000001<sub>16</sub> (DEC-reserved operand)

Result: Since both input operands are DEC-reserved operands, the operand on the R port, 80765432<sub>16</sub>, is the final result of the operation. The NAN flag will be HIGH.

**Operations Producing Overflows:** If an operation produces a rounded result that is too large to fit in the the destination format, that operation is said to have overflowed.

A floating-point overflow occurs if an R PLUS S, R MINUS S, R TIMES S, or 2 MINUS S operation with finite input operand(s) produces a result which, after rounding, has a magnitude greater than or equal to 2<sup>127</sup>. The final result in such cases will be DEC-reserved operand 800000001<sub>6</sub>; the overflow, inexact, and NAN flags will be HIGH.

Integer overflow occurs when the ''floating-point-to-integer'' conversion operation attempts to convert to integer a floating-point number which, after rounding, is greater than  $2^{31}\,$  – 1 or less than  $-2^{31}\,$ . The final result in such cases will be DEC-reserved operand  $80000000_{16}$ ; the invalid operation flag will be HIGH. Note that the overflow and inexact flags remain LOW for integer overflow.

Operations Producing Underflows: If an operation produces a floating-point result which, after rounding, has a magnitude too small to be expressed as a normalized floating-point number but greater than 0, that operation is said to have underflowed. Underflow occurs when an R PLUS S, R MINUS S, or R TIMES S operation produces a result which, after rounding, has the magnitude:

$0 < \text{magnitude} < 2^{-128}$ .

The final result in such cases will be 0 (0000000016). The underflow, inexact, and zero flags will be HIGH.

Underflow does not occur if the destination format is integer. If the infinitely precise result of a floating-point-to-integer conversion has a magnitude greater than 0 and less than 1 but the rounded result is 0, the underflow flag remains LOW.

Invalid Operations: If an input operand is invalid for the operation to be performed, that operation is considered invalid. There is only one invalid operation in DEC mode: performing a floating-point-to-integer conversion on a value too large to be converted to an integer. In this case, the final result will be DEC-reserved operand 8000000016, and the invalid operation and NAN flags will be HIGH.

# Sign Bit

For all operations producing a DEC floating-point result, the sign bit of the final result is unambiguous; i.e., there is only one sign bit value that yields a numerically correct result.

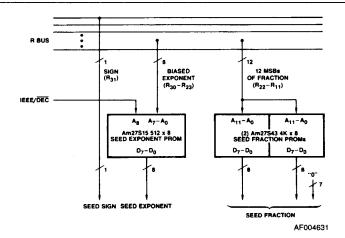

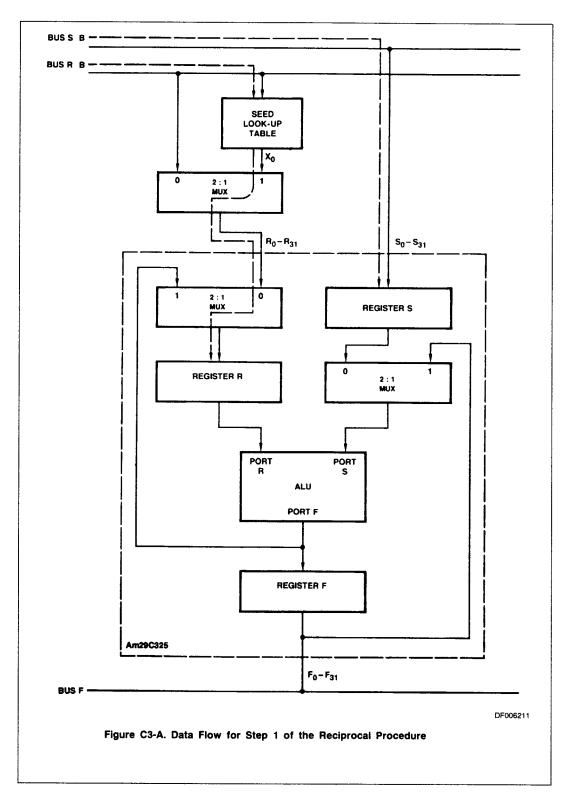

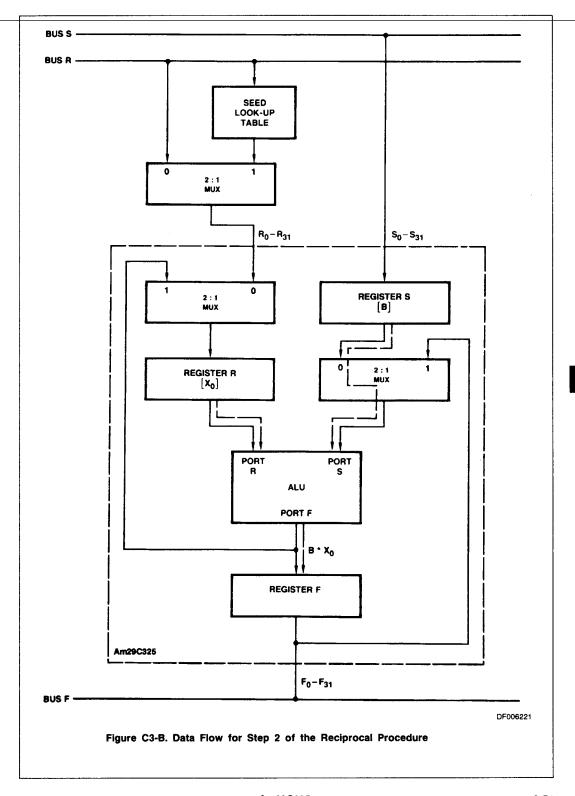

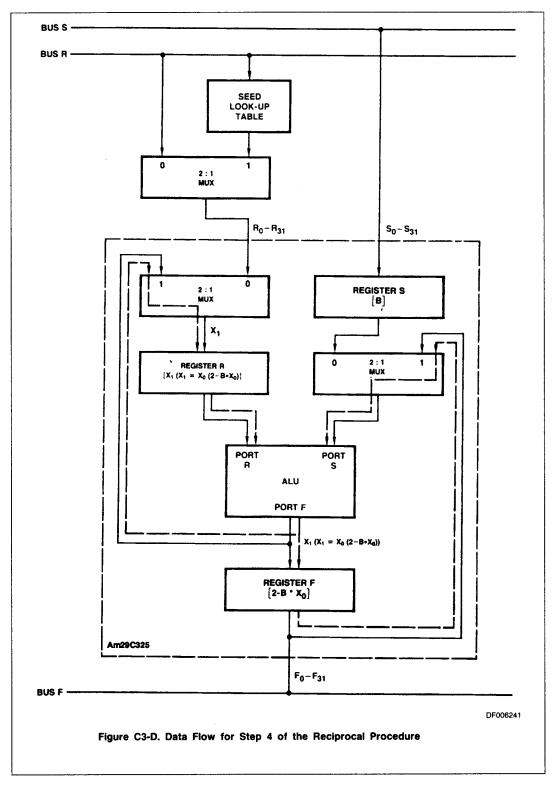

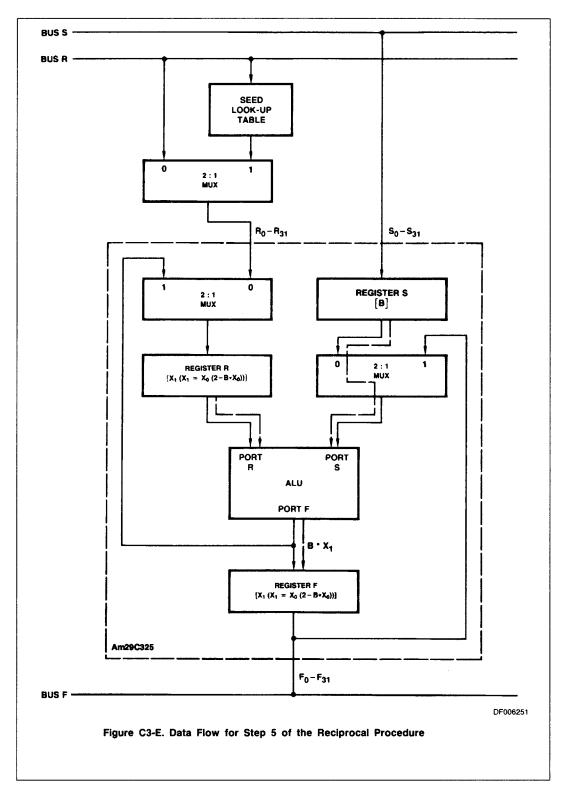

#### Rounding