# IBW ®

## IBM Packet Routing Switch Serial Interface Converter

## **Datasheet**

© Copyright International Business Machines Corporation 1999, 2000, 2001

All Rights Reserved

Printed in the United States of America April 2001

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM IBM Logo

i960 is a trademark of Intel Corporation in the United States and/or other countries. For a complete list of Intel Trademarks see www.intel.com/tradmarx.htm.

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

prssi.03title.fm April 23, 2001

## **Contents**

| List of Figures                                                  | 7  |

|------------------------------------------------------------------|----|

| List of Tables                                                   | 9  |

| 1. General Information                                           | 11 |

| 1.1 Features                                                     | 11 |

| 1.2 Description                                                  | 11 |

| 1.3 Ordering Information                                         |    |

| 1.4 Conventions and Notation                                     |    |

| 2. Converter Ingress and Egress Data Flow                        | 13 |

| 2.1 Ingress Data Flow                                            | 13 |

| 2.1.1 Ingress PE Interface                                       |    |

| 2.1.2 Ingress Packet Reshuffling                                 | 14 |

| 2.1.3 Ingress Receive FIFO                                       | 14 |

| 2.1.4 Ingress DASL Interface                                     | 14 |

| 2.1.5 DASL Port Serializer                                       | 14 |

| 2.2 Egress Data Flow                                             | 14 |

| 2.2.1 DASL Port Deserializer                                     | 14 |

| 2.2.2 Egress DASL Interface                                      |    |

| 2.2.3 Egress Transmit FIFO                                       |    |

| 2.2.4 Egress Path Selection                                      |    |

| 2.2.5 Egress Transmit Framing                                    |    |

| 2.2.6 Egress PE Interface                                        |    |

| 2.3 Converter Flow Control                                       |    |

| 2.3.1 System-Level Flow Control                                  |    |

| 2.3.2 Link-Level Flow Control                                    |    |

| 2.3.3 Converter Configurations                                   |    |

| 2.3.4 Latency                                                    |    |

| 2.4 Switch Flow Control                                          |    |

| 2.4.1 Latency                                                    |    |

| 2.4.2 Threshold Setting                                          |    |

| 2.4.3 Flow Control Violation                                     | 30 |

| 3. Functional Description                                        | 31 |

| 3.1 Data Interface Between the Converter and the Protocol Engine | 32 |

| 3.2 Functional Overview                                          | 32 |

| 3.2.1 Ingress Interface                                          | 33 |

| 3.2.2 Egress Interface                                           |    |

| 3.2.3 TXFULL Timing Restriction                                  |    |

| 3.2.4 Timing for TXFULL Deasserted                               | 38 |

|      | 3.3 Packet Reshuffling                                                   | . 39 |

|------|--------------------------------------------------------------------------|------|

|      | 3.3.1 Ingress Receive Logical Unit Framing                               |      |

|      | 3.3.2 Nested TxPause Extraction                                          |      |

|      | 3.3.3 Ingress Packets for IBFC                                           |      |

|      | 3.3.4 Egress Packet Formatter                                            |      |

|      | 3.3.5 Egress Packets for OBFC                                            | . 46 |

|      | 3.4 Packet Buffering                                                     | . 47 |

|      | 3.4.1 X and Y Path Receive FIFO (RXFIFO)                                 | . 47 |

|      | 3.4.2 X and Y Path Transmit FIFO (TXFIFO)                                | . 47 |

|      | 3.5 Path Selection Block                                                 | . 48 |

|      | 3.6 Interfacing the DASL Macro                                           | . 49 |

|      | 3.6.1 Ingress DASL Interface                                             | . 49 |

|      | 3.6.2 Egress DASL Interface                                              | . 50 |

|      | 3.6.3 Switch In-Band Output Queue Grant Information                      | . 53 |

|      | 3.6.4 Converter Switch Interface                                         |      |

|      | 3.7 Grant Control Generation                                             | 54   |

|      | 3.7.1 Per Priority Side-Channel Modes                                    |      |

|      | 3.7.2 Shared Memory Bits                                                 | . 55 |

|      | 3.7.3 Parity                                                             | . 55 |

|      | 3.7.4 Memory Grant                                                       | . 55 |

|      | 3.8 Egress and Ingress Interface Diagnostic Functions                    | . 56 |

|      | 3.8.1 Loopbacks                                                          |      |

|      | 3.9 Clock Generator Description                                          | . 59 |

|      | 3.9.1 Converter Internal Clock Description                               |      |

|      | 3.9.2 Converter External Traffic                                         |      |

|      | 3.10 Converter Reset Scheme Description                                  | . 61 |

|      | 3.10.1 Reset Strategy                                                    |      |

|      | 3.10.2 Power-On Reset Procedure                                          |      |

|      | 3.10.3 Path Reset                                                        | . 62 |

|      | 3.10.4 PLL Reset                                                         | . 63 |

|      | 3.10.5 Ingress/Egress Interface Reset                                    | . 63 |

|      | 3.11 Microprocessor Interface Description                                | . 63 |

|      | 3.11.1 Processor Interface Lines                                         | . 64 |

|      | 3.11.2 Processor Interface I/O Line Descriptions                         | . 64 |

|      | 3.11.3 32-Bit Mode Processor Interface Timing                            |      |

|      | 3.11.4 8-Bit Mode Processor Interface Timing                             | . 66 |

| 4 1  | Davieteva                                                                | 67   |

| 4. 1 | Registers                                                                |      |

|      | 4.1 Error Detection, Reporting, and Interrupt Registers                  |      |

|      | 4.2 Register Definitions                                                 |      |

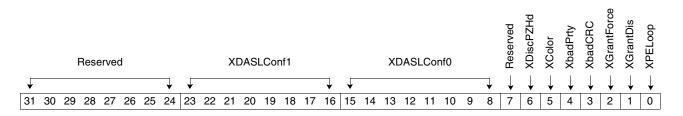

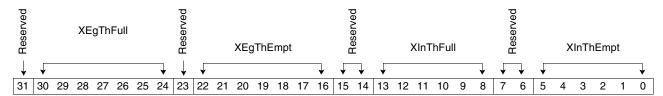

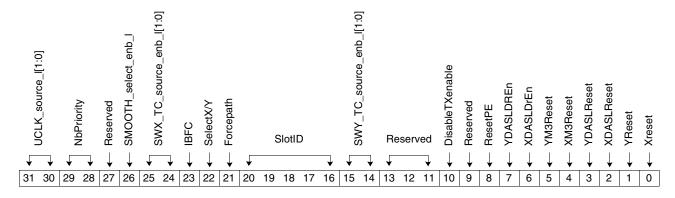

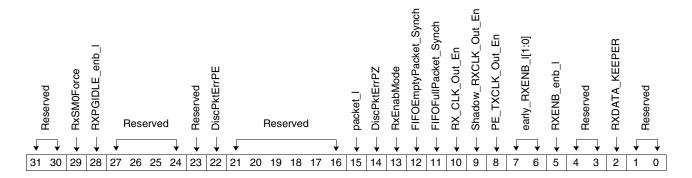

|      | 4.2.1 Setup_1_X_PATH Register                                            |      |

|      | 4.2.2 Setup_2_X_PATH Register                                            |      |

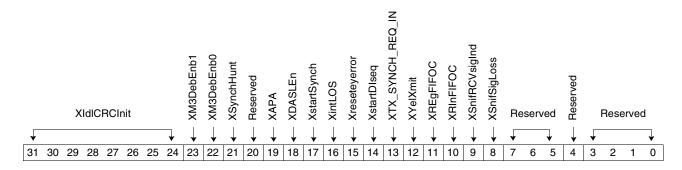

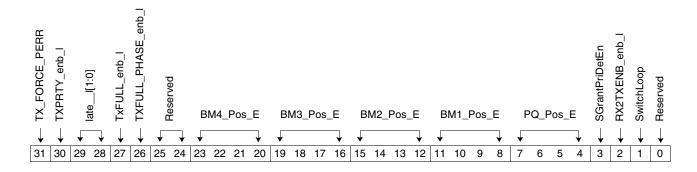

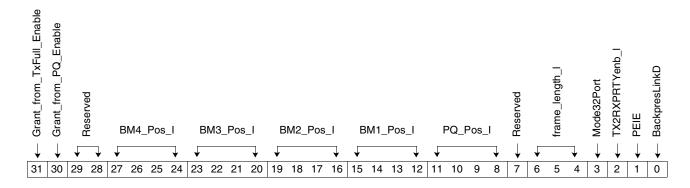

|      | 4.2.3 Control_X_PATH Register                                            |      |

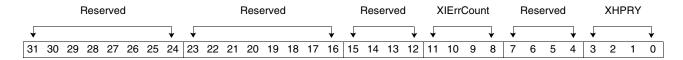

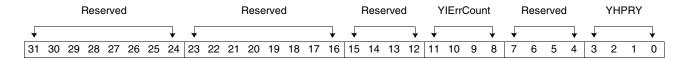

|      | 4.2.4 X Plane Egress Parity and CRC_Error_Count_X Register               |      |

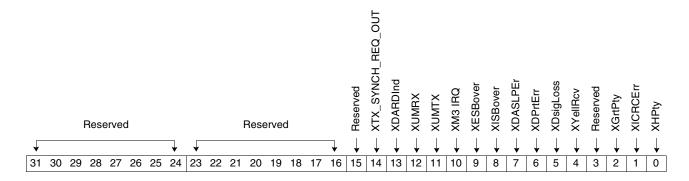

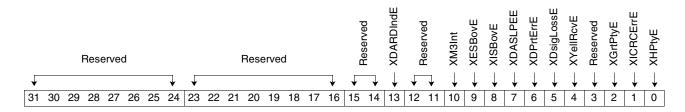

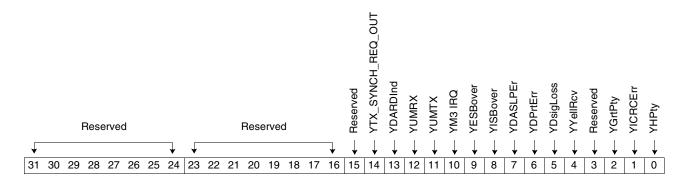

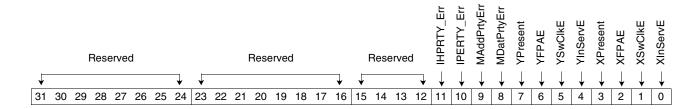

|      | 4.2.5 X Plane Event 1 Register (Event_1_X)                               |      |

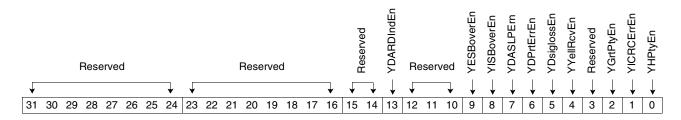

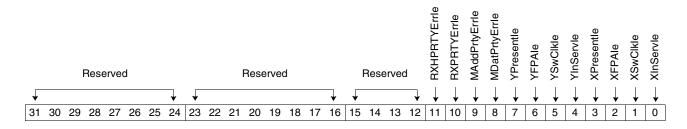

|      | 4.2.6 X Plane Event 1 Checker Enable Register (Event_1_Checker_Enable_X) |      |

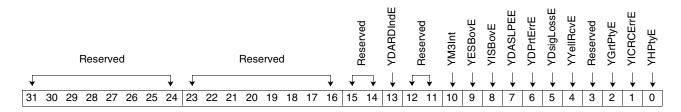

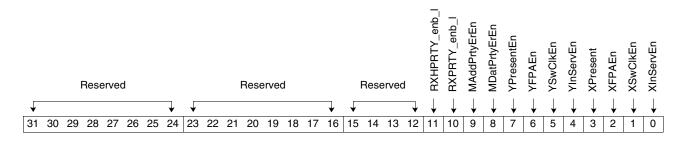

|      | 4.2.7 Interrupt_Enable_X Register                                        |      |

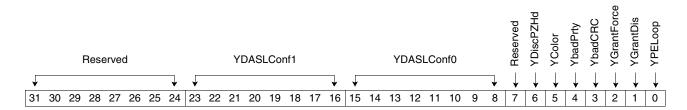

|      | 4.2.8 Setup_1_Y_PATH Register4.2.9 Setup_2_Y_PATH Registers              |      |

|      | 7.2.3 JULUP 4 I I A III I I I I I I I I I I I I I I                      | . 04 |

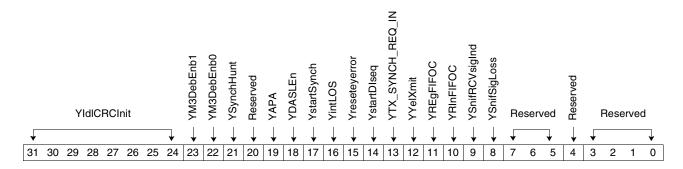

| 4.2.10 Control_Y_PATH Register                                        | 85           |

|-----------------------------------------------------------------------|--------------|

| 4.2.11 Y Plane Egress Parity and CRC_Error_Count_Y Register           | 88           |

| 4.2.12 Y Plane Event 1 Register (Event_1_Y)                           |              |

| 4.2.13 Y Plane Event 1 Checker Enable Register (Event_1_Checker_l     | Enable_Y) 91 |

| 4.2.14 Interrupt_Enable_Y Register                                    | 92           |

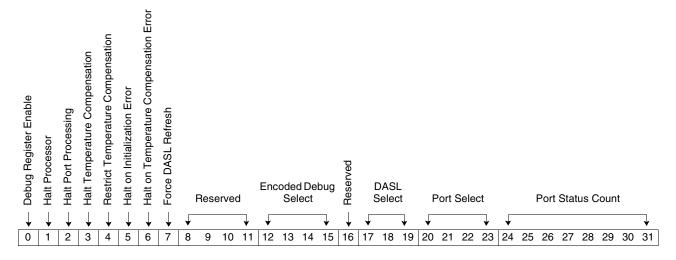

| 4.2.15 DASL_M3_Picocode_X Register                                    | 93           |

| 4.2.16 SDC Controller X Register (SDC_Debug_CNTL_X)                   | 95           |

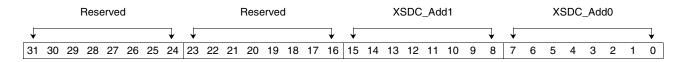

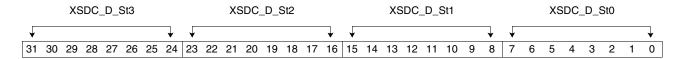

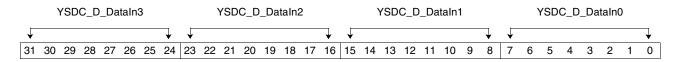

| 4.2.17 SDC Data In X Bus Register (SDC_Debug_Data_In_X)               | 96           |

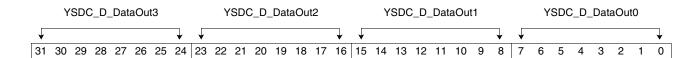

| 4.2.18 SDC Data Out X Bus Register (SDC_Debug_Data_Out_X)             | 97           |

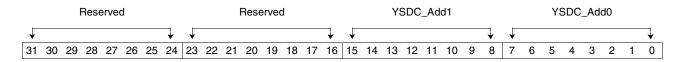

| 4.2.19 SDC Address X Bus Register (SDC_Debug_Data_Address_X)          | 97           |

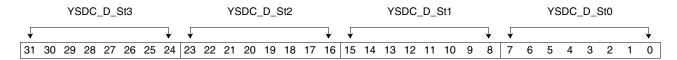

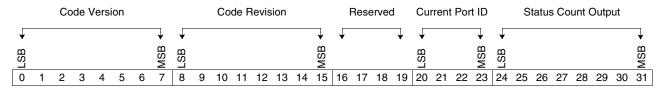

| 4.2.20 SDC Status X Register (SDC_Status_Reg_X)                       |              |

| 4.2.21 DASL_M3_Picocode_Y Register                                    |              |

| 4.2.22 SDC Controller Y Register (SDC_Debug_CNTL_Y)                   | 100          |

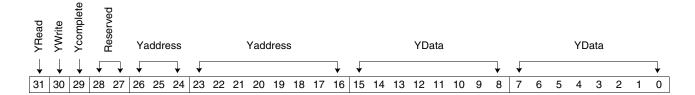

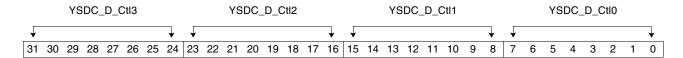

| 4.2.23 SDC Data In Y Bus Register (SDC_Debug_Data_In_Y)               | 100          |

| 4.2.24 SDC Data Out Y Bus Register (SDC_Debug_Data_Out_Y)             | 101          |

| 4.2.25 SDC Address Y Bus Register (SDC_Debug_Data_Address_Y)          | 101          |

| 4.2.26 SDC Status Y Register (SDC_Status_Reg_Y)                       |              |

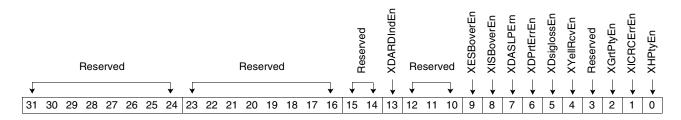

| 4.2.27 Event_2_Checker_Enable_X_and_Y Register                        | 103          |

| 4.2.28 Event_2_Interrupt_Enable_X_and_Y Register                      | 104          |

| 4.2.29 Event_2_X_and_Y Register                                       | 105          |

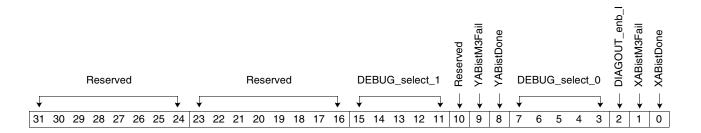

| 4.2.30 ABIST Failure Test_Status_X_Y Register                         | 107          |

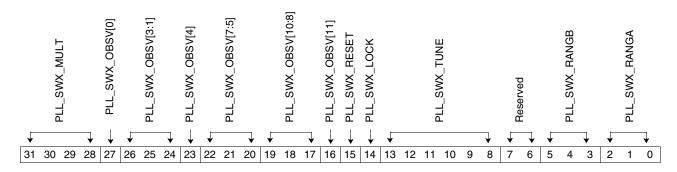

| 4.2.31 Switch_X_PLL Setting Register                                  | 108          |

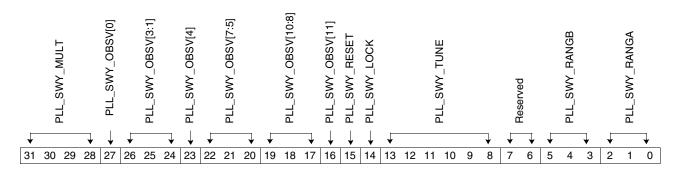

| 4.2.32 Switch_Y_PLL Setting Register                                  | 109          |

| 4.2.33 Chip_ID Register                                               |              |

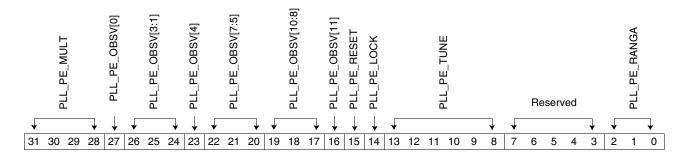

| 4.2.34 Protocol Engine PLL Setting Register (PE_PLL Register)         | 111          |

| 4.2.35 Common_Control Register                                        | 112          |

| 4.2.36 Interrupt_Register_Indirection Register                        |              |

| 4.2.37 Ingress PE Setting Register (Ingress_PE_Interface [IPI] - Rece |              |

| 4.2.38 Egress PE Setting Register (Egress_PE_Interface [EPI] - Trans  | smit) 118    |

| 4.2.39 Common PE Setting Register (PE_Common)                         |              |

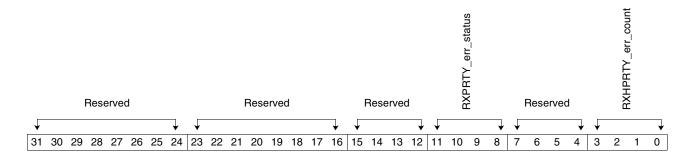

| 4.2.40 Ingress Parity Error Count Register (PARITY_Error_count)       | 122          |

| 5. Data-Aligned Synchronous Link (DASL)                               | 123          |

| 5.1 General Description                                               |              |

| 5.2 Resets                                                            |              |

| 5.2.1 SDC_RESET (M3 Reset)                                            |              |

| 5.2.2 CORE_RESET (DASL Reset)                                         |              |

| 5.3 Picocode Download                                                 |              |

| 5.3.1 Picocode Write                                                  |              |

| 5.3.2 Picocode Read                                                   |              |

| 5.4 SDC_INTERRUPT Signal                                              |              |

| 5.5 SDC Debug Interface                                               |              |

| · · · · · · · · · · · · · · · · · · ·                                 |              |

| 5.6 Status Register                                                   |              |

| ·                                                                     |              |

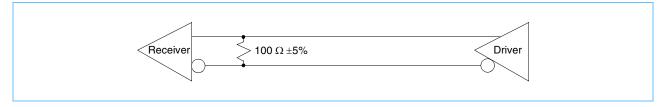

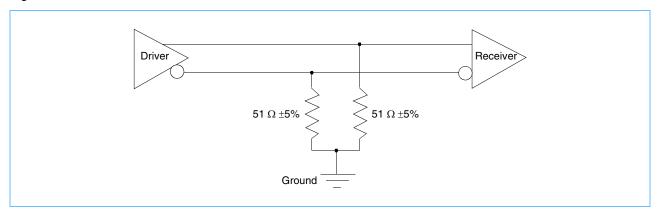

| 5.8 Line Termination                                                  |              |

| 5.8.1 DASL and SYS_CLK                                                | 131          |

| 6. Phase-Locked Loop (PLL)                                           | 133 |

|----------------------------------------------------------------------|-----|

| 6.1 PLL Configuration                                                | 133 |

| 6.2 PLL RESET                                                        | 133 |

| 6.3 PLL_RANGE and PLL_MULT                                           | 133 |

| 6.4 PLL_Tune                                                         | 133 |

| 6.5 PLL_LOCK                                                         |     |

| 6.6 PLL Settings                                                     |     |

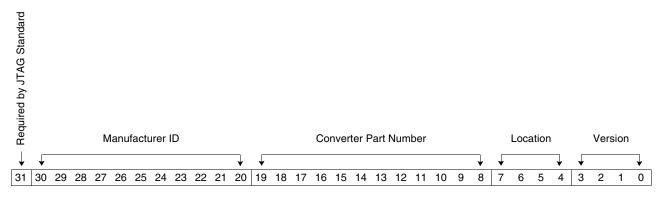

| 7. JTAG Description                                                  | 137 |

| 8. I/O Signal Definitions                                            | 139 |

| 8.1 Signal Descriptions                                              |     |

| 8.2 I/O Timing                                                       | 152 |

| 8.2.1 AC Parameter Characteristics                                   |     |

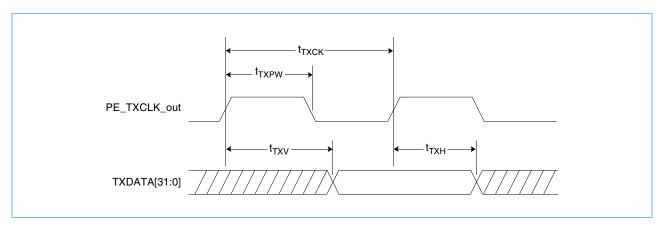

| 8.2.2 Protocol Engine (UTOPIA-3-Like) Interface AC Ratings, Transmit | 154 |

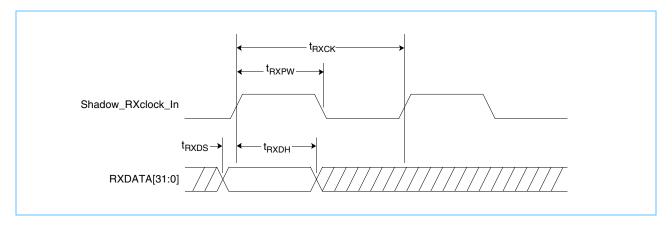

| 8.2.3 Protocol Engine (UTOPIA-3-Like) Interface AC Ratings, Receive  |     |

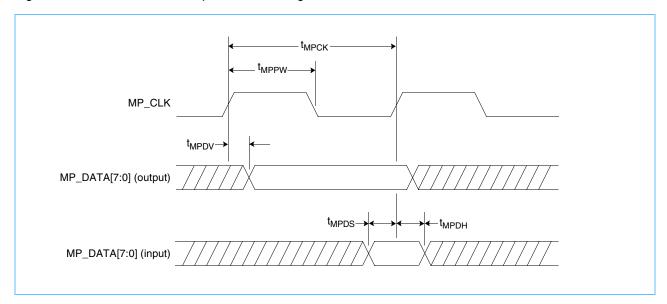

| 8.2.4 Microprocessor Interface AC Ratings                            | 155 |

| 9. Electrical Specifications                                         | 157 |

| 9.1 Power Sequencing                                                 | 157 |

| 9.2 Recommended Operating Conditions                                 | 158 |

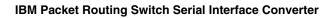

| 10. Pin Assignments                                                  | 161 |

| 10.1 Power Signals                                                   |     |

| 11. Packaging Information                                            | 173 |

| 12. Glossary                                                         | 175 |

| 13. Revision Log                                                     | 179 |

## **List of Figures**

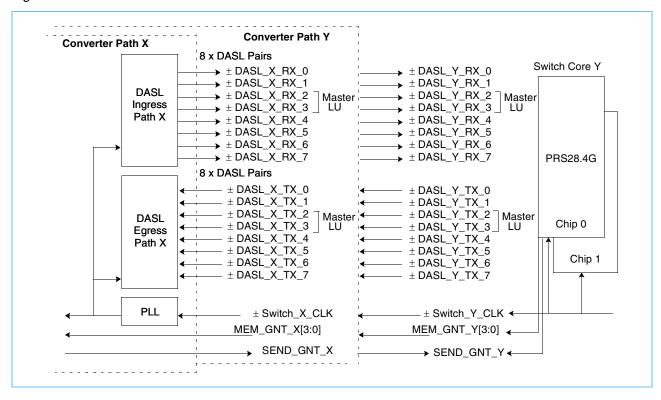

| Figure 1-1. Overall Switch Subsystem Configuration                                                                                | 12 |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

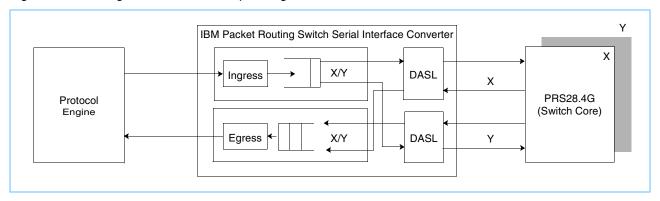

| Figure 2-1. Converter Data Flow                                                                                                   | 13 |

| Figure 2-2. Flow Control Overview                                                                                                 | 16 |

| Figure 2-3. System-Level Flow Control                                                                                             | 17 |

| Figure 2-4. Timing of OBFC Grant Control Signaling                                                                                | 18 |

| Figure 2-5. Egress Data Packet Header                                                                                             | 19 |

| Figure 2-6. Shared Memory Flywheel Operation With Forced Memory 0                                                                 | 21 |

| Figure 2-7. Ingress TxPause Flow Control Insertion                                                                                | 22 |

| Figure 2-8. IBFC Output Queue Grant Latency                                                                                       | 23 |

| Figure 2-9. IBFC Memory Grant Latency                                                                                             | 24 |

| Figure 2-10. OBFC Output Queue Grant Latency                                                                                      | 24 |

| Figure 2-11. OBFC Memory Grant Latency                                                                                            | 25 |

| Figure 2-12. TxPause Latency                                                                                                      | 26 |

| Figure 2-13. Force Shared Memory 0 Latency                                                                                        | 27 |

| Figure 2-14. Ingress Data Latency                                                                                                 | 28 |

| Figure 2-15. Egress Data Latency                                                                                                  | 28 |

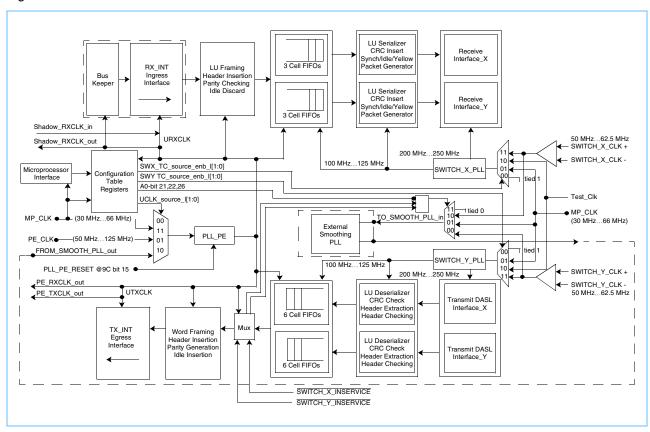

| Figure 3-1. Converter Functional Block Diagram                                                                                    | 31 |

| Figure 3-2. Bit and Byte Notation                                                                                                 | 32 |

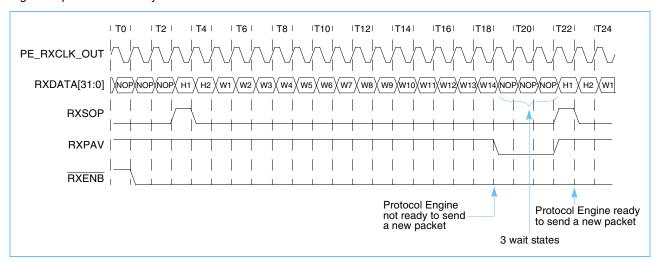

| Figure 3-3. Ingress Timing for RXENB Deasserted by Converter for One Clock Cycle                                                  | 34 |

| Figure 3-4. Ingress Timing for RXENB Deasserted by Converter When the RxEnabMode Bit of the Ingress_PE_Interface Register is High | 35 |

| Figure 3-5. Ingress Timing for RXPAV Deasserted by Protocol Engine for One Clock Cycle                                            | 35 |

| Figure 3-6. Ingress Timing for RXPAV Deasserted by Protocol Engine for Three Clock Cycles                                         | 35 |

| Figure 3-7. Ingress Timing for Back-to-Back Packets From Protocol Engine                                                          | 36 |

| Figure 3-8. Egress Timing for Back-to-Back Packets                                                                                | 37 |

| Figure 3-9. TXFULL Timing Restriction                                                                                             | 38 |

| Figure 3-10. Timing for TXFULL Deasserted by PE More Than Four Clock Cycles Before the End of the Current Idle                    | 38 |

| Figure 3-11. Timing for TXFULL Deasserted by PE Less Than Four Clock Cycles Before the End of the Current Idle                    | 39 |

| Figure 3-12. Switch Packet Qualifier Bit Reshuffling                                                                              |    |

| Figure 3-13. Path Selection                                                                                                       |    |

| Figure 3-14. Converter Interface Lines                                                                                            |    |

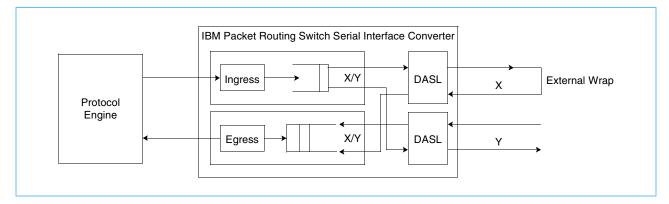

| Figure 3-15. Configuration in Normal Operating Mode                                                                               |    |

| Figure 3-16. Protocol Engine Loopback Through Path X or Path Y                                                                    |    |

| Figure 3-17. Protocol Engine External Loopback Through Path X                                                                     |    |

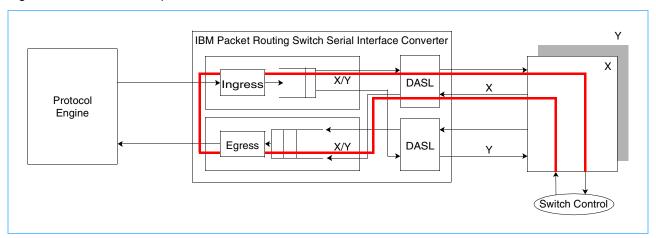

| Figure 3-18. Switch X Loopback                                                                                                    |    |

| Figure 3-19. Clock Distribution                                                                                                   |    |

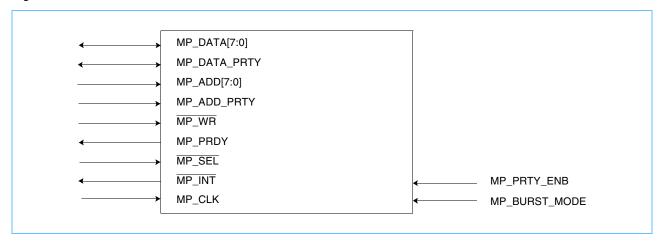

| Figure 3-20. Converter Processor Interface Lines64                    |

|-----------------------------------------------------------------------|

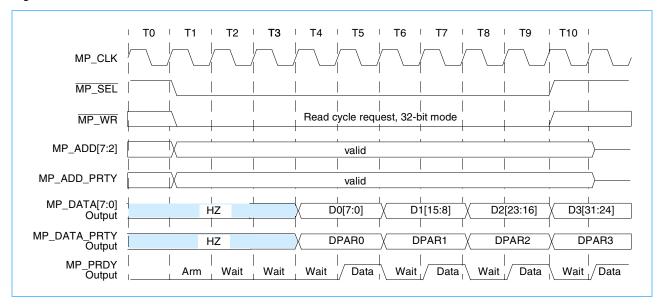

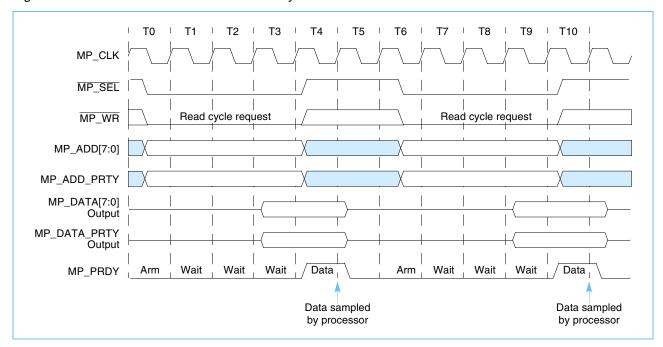

| Figure 3-21. Processor Read Access in 32-Bit Burst Mode               |

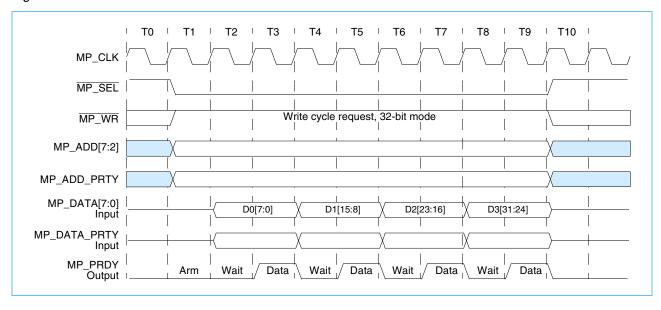

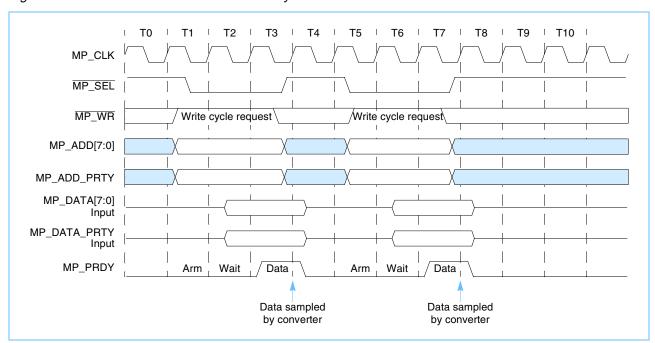

| Figure 3-22. Processor Write Access in 32-Bit Burst Mode              |

| Figure 3-23. Processor Read Access in 8-Bit Byte Mode                 |

| Figure 3-24. Processor Write Access in 8-Bit Byte Mode                |

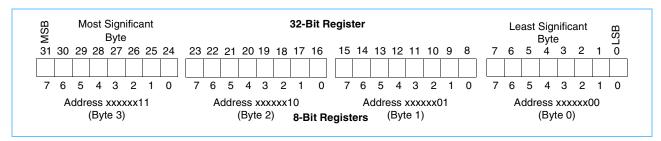

| Figure 4-1. Individual Register Mapping67                             |

| Figure 4-2. Register Addressing                                       |

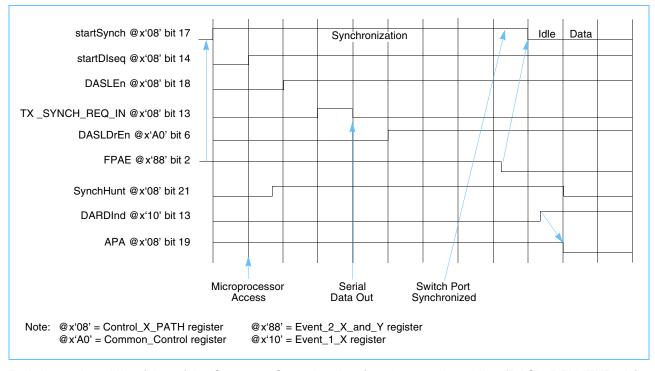

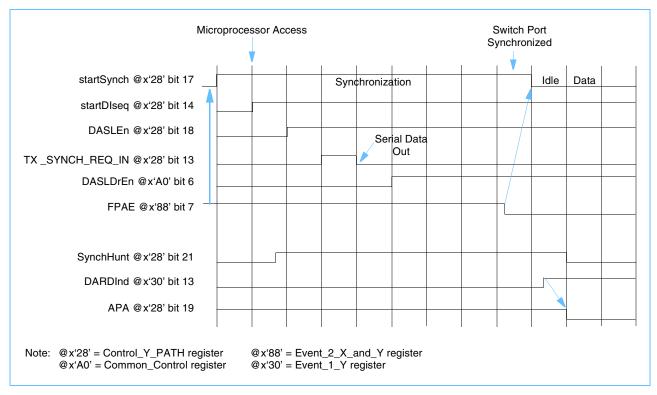

| Figure 4-3. DASL Interface and DASL Startup Sequence Path X80         |

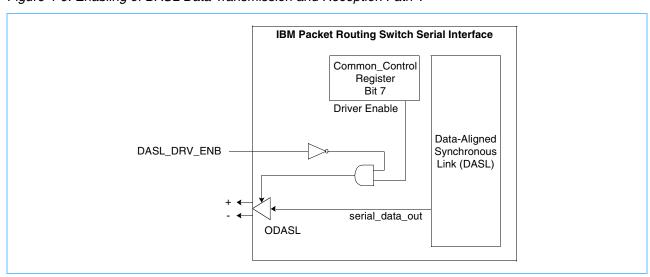

| Figure 4-4. Enabling of DASL Data Transmission and Reception Path X80 |

| Figure 4-5. DASL Interface and DASL Startup Sequence Path Y87         |

| Figure 4-6. Enabling of DASL Data Transmission and Reception Path Y87 |

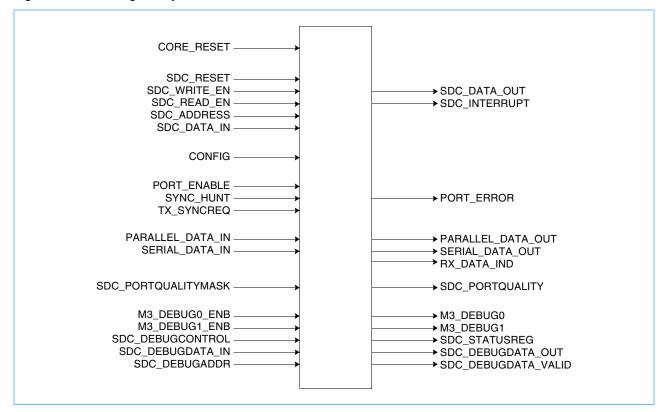

| Figure 5-1. Data-Aligned Synchronous Interface Lines                  |

| Figure 5-2. Switch Fabric DASL Port Synchronization Sequence          |

| Figure 5-3. DASL Termination                                          |

| Figure 5-4. Clock Termination                                         |

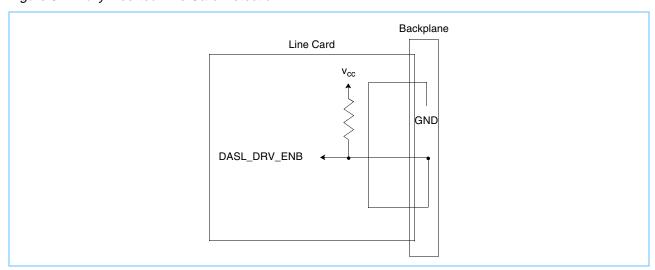

| Figure 8-1. Fully Inserted Line Card Detection                        |

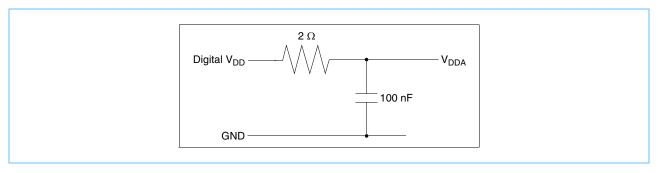

| Figure 8-2. V <sub>DDA</sub> Filtering145                             |

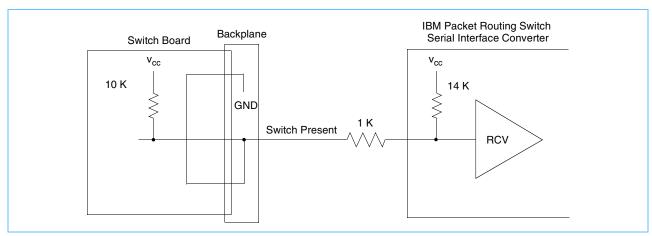

| Figure 8-3. Switch Present Detection                                  |

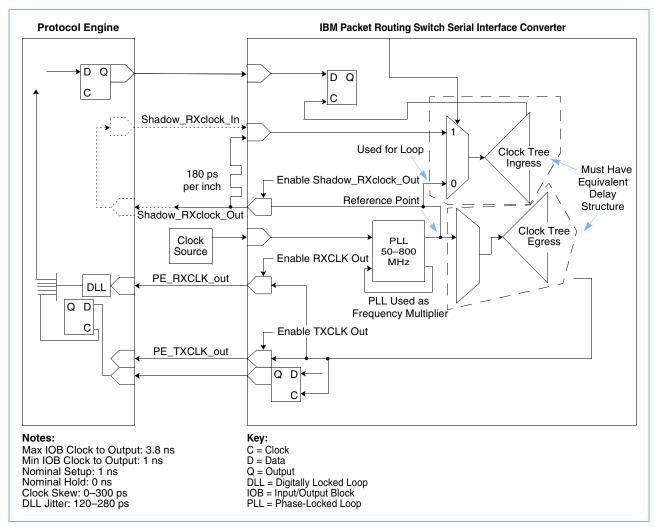

| Figure 8-4. Options for Ingress UTOPIA-3-Like Interface Clocking      |

| Figure 8-5. AC Parameter Transmit Timing                              |

| Figure 8-6. AC Parameter Receive Timing                               |

| Figure 8-7. AC Parameter Microprocessor Timing                        |

| Figure 10-1. Pinout                                                   |

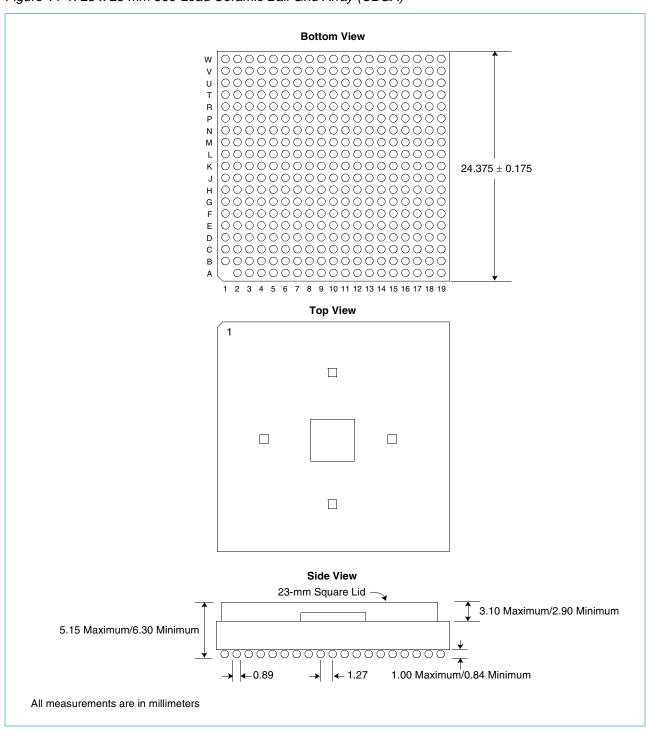

| Figure 11-1. 25 x 25 mm 360-Lead Ceramic Ball Grid Array (CBGA)       |

## **List of Tables**

| Table 2-1. Flow Control Configurations                                       | 22  |

|------------------------------------------------------------------------------|-----|

| Table 3-1. Ingress I/O Pin Descriptions                                      | 34  |

| Table 3-2. Egress I/O Pin Descriptions                                       | 37  |

| Table 3-3. Packet Qualifier Byte for Ingress Idle Packet                     | 43  |

| Table 3-4. Packet Qualifier Byte for Ingress Data Packet                     | 43  |

| Table 3-5. Packet Qualifier Byte for Ingress Data Packet                     | 44  |

| Table 3-6. Packet Qualifier Byte for Egress Idle Packet                      | 45  |

| Table 3-7. Packet Qualifier Byte for Egress Data Packet                      | 45  |

| Table 3-8. Packet Qualifier Byte for Egress Data Packet                      | 47  |

| Table 3-9. Output Queue Grant Bit Map Fields                                 | 53  |

| Table 3-10. Selecting the Signal That Appears on the TO_SMOOTH_PLL_IN Signal | 59  |

| Table 3-11. External Clock Descriptions                                      | 60  |

| Table 4-1. Register Map                                                      | 69  |

| Table 5-1. Internal DASL Signal Interface Descriptions                       | 124 |

| Table 6-1. PRS28.4G PLL Settings                                             | 134 |

| Table 6-2. PE PLL Programming Examples                                       | 135 |

| Table 7-1. Supported JTAG Instructions                                       | 137 |

| Table 7-2. JTAG Compliance Pattern                                           | 138 |

| Table 8-1. Test Signals                                                      | 139 |

| Table 8-2. JTAG Interface External Signals                                   | 141 |

| Table 8-3. Processor Interface Signals                                       | 141 |

| Table 8-4. Converter Signals                                                 | 142 |

| Table 8-5. PE Interface Receive Signals                                      | 143 |

| Table 8-6. PE Interface Transmit Signals                                     | 143 |

| Table 8-7. External Clocking/PLL Signals                                     | 144 |

| Table 8-8. Back-Pressure Serial Link Signals                                 | 145 |

| Table 8-9. Miscellaneous External Signals                                    | 146 |

| Table 8-10. Spare Signals Used to Carry Additional DC Voltages               | 147 |

| Table 8-11. External Debugging Signals                                       |     |

| Table 8-12. DBG_SELECT Bus Definition                                        | 148 |

| Table 8-13. Protocol Engine (UTOPIA-3-Like) Interface AC Ratings, Transmit   | 154 |

| Table 8-14. Protocol Engine (UTOPIA-3-Like) Interface AC Ratings, Receive    | 155 |

| Table 8-15. Microprocessor Interface AC Ratings                              | 155 |

| Table 9-1. Absolute Maximum Ratings                                          | 157 |

| Table 9-2. LVCMOS-Compatible I/Os                                            |     |

| Table 9-3. LVTTL-Compatible I/Os                                             | 158 |

| Table 9-4. Recommended Operating Conditions for All I/Os                     |     |

| Table 9-5. Power Dissipation                                                 | 159 |

| Table 10-1. Signal Pins Sorted by Signal Name                                          | 162 |

|----------------------------------------------------------------------------------------|-----|

| Table 10-2. Signal Pins Sorted by Grid Location                                        | 166 |

| Table 10-3. Ground Signal Pin Locations                                                | 170 |

| Table 10-4. V <sub>DD1</sub> (2.5 V) Signal Pin Locations                              | 170 |

| Table 10-5. V <sub>DD2</sub> - V <sub>DD5</sub> (1.5 V and 3.3 V) Signal Pin Locations | 171 |

#### 1. General Information

#### 1.1 Features

- Companion to IBM Packet Routing Switch PRS28.4G and IBM Packet Routing Switch PRS64G

- Support for internal (8-port) and external (16-port) switch speed expansion mode

- Proprietary 440 Mbps and 500 Mbps, eight high-speed transceiver logic (HSTL) pair, dataaligned synchronous link (DASL) switch interface

- 3.52 Gbps aggregate throughput per speed expanded port

- 32-bit ingress/egress protocol engine (PE) interface bus (UTOPIA-3-like bus)

- Implements switch plane redundancy system architecture with two independent paths

- Three-packet ingress and six-packet egress shared buffers

- · Up to four priority levels in packet handling

- In-band flow control (IBFC) via packet header information

- Out-of-band flow control (OBFC) to the PE through an external serial bus

- Programmable packet length of 64 to 80 bytes

- Link-liveness yellow packet insertion

- 8-bit processor interface, with bursting option

- Internal array built-in self test (ABIST)

- IEEE 1149.1 standard boundary scan to facilitate circuit board testing

- 1.5 V differential inputs/outputs (I/Os) for dataaligned synchronous links

- 2.5 V supply voltage (3.3 V-tolerant I/Os) and 3.3 V low-voltage transistor-transistor logic (LVTTL) for the other signal I/Os

- 25 × 25 mm 360-lead ceramic ball grid array (CBGA) package

- IBM complementary metal-oxide semiconductor (CMOS) 6 SF SA-12E technology

## 1.2 Description

The IBM Packet Routing Switch Serial Interface Converter (the converter) is a companion device to the IBM Packet Routing Switch PRS28.4G and the IBM Packet Routing Switch PRS64G (the switch). It connects the switch's serial link to a Protocol Engine (PE) on a 32-bit interface bus. The converter attaches to a switch port operating at up to 4 Gbps in speed expansion mode, wired on eight DASL pairs running at up to 500 Mbps per pair.

No synchronization is required between input ports. However, packets on a given port are always received or transmitted at a fixed interval equal to the packet length. The converter ingress/egress packet length is programmable from 64 to 80 bytes in increments of four bytes. Input/output packets to

and from the switch are mapped into blocks of four logical units (LUs), each of which consists of 16 to 20 bytes depending on the packet length.

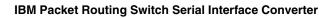

The converter is composed of two fully independent data paths (X and Y) to provide a resilient switch fabric. These paths are clocked, reset, and controlled independently to support independent activation and deactivation of each switch plane.

Ingress traffic (packets received from a PE interface bus) is routed to both X and Y path switch planes, thereby duplicating packets on both planes. Egress traffic (packets received from switch plane X or Y) is routed to a bus. See Figure 1-1.

Figure 1-1. Overall Switch Subsystem Configuration

## 1.3 Ordering Information

| Part Number  | Description                                          |

|--------------|------------------------------------------------------|

| IBM3229P2035 | IBM Packet Routing Switch Serial Interface Converter |

#### 1.4 Conventions and Notation

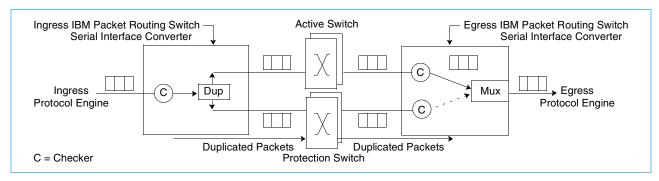

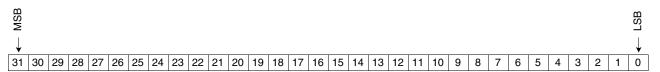

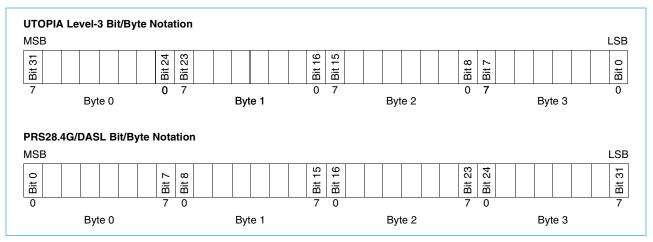

In this document, with the exception of Section 5, Data-Aligned Synchronous Link (DASL), bit notation is non-IBM, meaning that bits and bytes are numbered in descending order from left to right. Thus, for a four-byte word, bit 31 is the most significant bit (MSB) and bit 0 is the least significant bit (LSB).

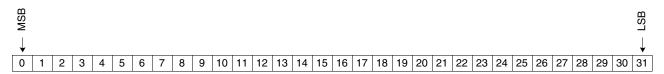

In Section 5, Data-Aligned Synchronous Link (DASL), standard IBM notation is used, meaning that bits and bytes are numbered in ascending order from left to right. Thus, for a four-byte word, bit 0 is the MSB and bit 31 is the LSB.

DASL uses a big-endian architecture, that is, the left-most bytes (those with a lower address) are most significant. (In little-endian architectures, the right-most bytes are most significant.)

Notation for bit encoding is as follows:

- Hexadecimal values are preceded by x and enclosed in single quotation marks. For example: x'0B00'.

- Binary values appear in single quotation marks. For example: '1010'.

The use of overbars, for example DDEL OUT, designates signals that are active low.

General Information prssi.03.fm

Page 12 of 180

April 23, 2001

## 2. Converter Ingress and Egress Data Flow

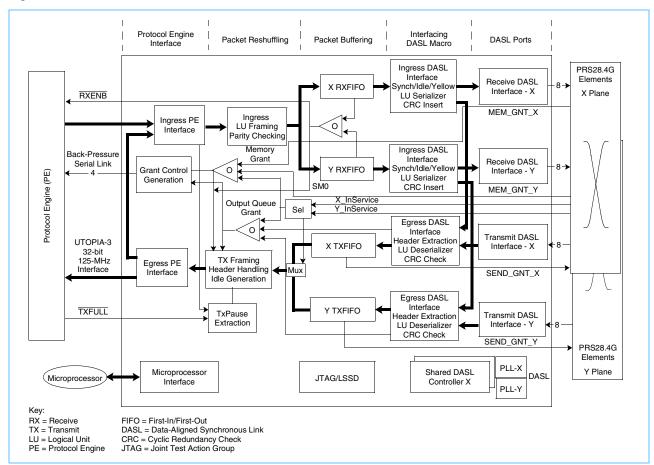

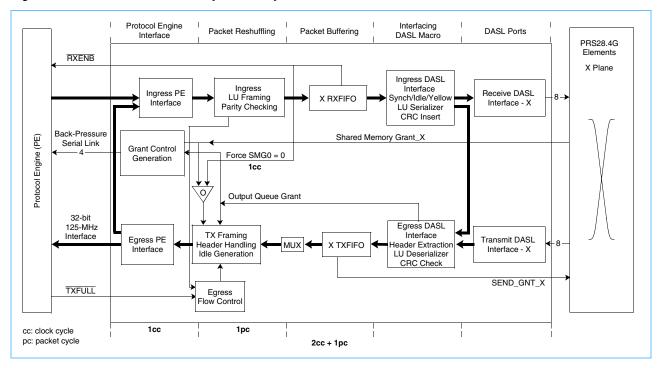

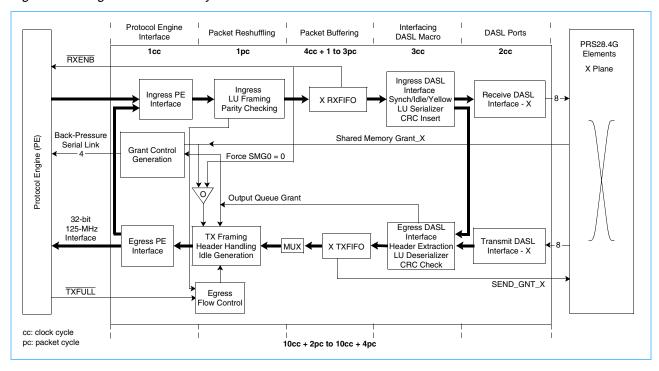

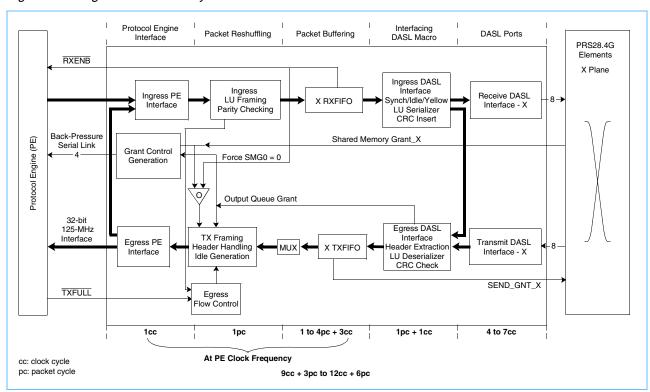

The ingress block is the receive path between the Protocol Engine (PE) and the rest of the IBM Packet Routing Switch Serial Interface Converter logic. The egress block is the transmit path between the converter transmit logic and the PE. This section provides an overview of the functions implemented in the converter ingress and egress data flows. Some functions are duplicated to support two IBM Packet Routing Switch PRS28.4G planes (see Figure 2-1).

Figure 2-1. Converter Data Flow

## 2.1 Ingress Data Flow

## 2.1.1 Ingress PE Interface

The converter connects to the PE via a 32-bit bus. Ingress data packets are simultaneously routed to path X and path Y. Idle packets are inserted in the word stream when there is no data to transfer and are used to maintain a synchronous packet operation in the ingress PE interface. Idle packets are identified by a bit in the packet qualifier byte. A Receive Start of Packet (RXSOP) signal synchronized with the data packet is used to delineate packets.

Combined with the RXPRTY signal issued from the PE, the ingress interface checks the parity coherency on each incoming 32-bit word on RXDATA. A specific bit in the configuration table registers can be set so that each parity error issued from the parity checker is reported.

RXPRTY\_error assertion, controlled by the configuration table, indicates that the cell currently pushed into the ingress reshuffling buffer will be optionally ignored and will not be sent to the ingress first-in/first-out (FIFO). Cells that are pushed into the ingress receive FIFOs (X/Y RXFIFOs) are always error-free and can be processed by the data flow.

#### 2.1.2 Ingress Packet Reshuffling

The ingress logical unit (LU) framing block maps incoming data packets into the switch LUs by moving the five bytes (the packet qualifier and the bit map fields) selected from the configuration register into the master LU, which becomes the switch header information field. The framing block also extracts the in-band flow control (IBFC) information, discards idle packets, and performs parity checking on the switch header.

#### 2.1.3 Ingress Receive FIFO

The ingress RXFIFOs provide packet synchronization between the 50- to 125-MHz PE interface and the 110- to 125-MHz switch core interface.

#### 2.1.4 Ingress DASL Interface

The Ingress DASL Interface (IDI) sends packets continuously. Synchronization packets are sent during the DASL synchronization sequence. Data or idle packets are sent once the data mode is active. Yellow packets are requested through the configuration table. When the LU serializer is filled with a yellow packet, the incoming data packet is buffered while the yellow packet is sent. When there is no data packet to be transmitted to the switch core, the IDI inserts an idle packet, computes the inter idle Cyclic Redundancy Check (CRC) for each LU, and inserts it as the last byte of each LU.

#### 2.1.5 DASL Port Serializer

The IDI feeds the DASL port serializer with packets compatible with the switch LU format. (The 16- to 20-byte LU width is set in the configuration register.) The DASL port serializer performs a multibit serialization for each LU. Each serial DASL interface line represents a nibble of the LU so that there are two data-aligned synchronous links per byte. The converter provides a total of eight serial links per port (one for each 4-bit nibble) representing a 32-bit wide word.

## 2.2 Egress Data Flow

#### 2.2.1 DASL Port Deserializer

The egress DASL performs 32-bit descrialization on incoming data and builds LUs for the Egress DASL Interface (EDI). It continuously monitors signal quality on the incoming high-speed serial link and performs continuous bit-positioning adjustment on the incoming data to maintain synchronization.

#### 2.2.2 Egress DASL Interface

The DASL's receive data indicator line triggers the LU deserializer logic block, which receives a continuous stream of packets. Packet length is programmable from 64 to 80 bytes and is mapped on four-byte word boundaries. Therefore, a new packet is received from the DASL every 16 to 20 cycles.

The LU deserializer extracts the switch packet header from the master LU to determine packet type (idle or data) and priority. Idle packets are discarded. Data packets are forwarded (in LU format) to the egress buffer interface. The LU deserializer checks the LU CRC after each idle cell, the parity on the switch header, and the type of packet. When an error or yellow packet is detected, and the checker is enabled, the corresponding converter interrupt line is asserted.

#### 2.2.3 Egress Transmit FIFO

The egress FIFO interface ignores any idle packets issued from the switch. Only data packets are pushed into the transmit FIFOs (TXFIFOs) for a further word-formatting packet operation. The TXFIFOs provide packet synchronization between the 110- to 125-MHz converter and the 50- to 110-MHz Protocol Engine.

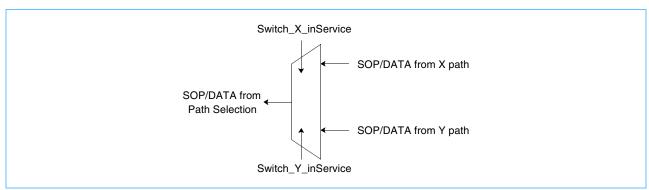

### 2.2.4 Egress Path Selection

The egress path selection multiplexes packets coming from the X and Y paths to the egress PE interface bus. The data is selected from the path in service through two interface lines (X\_InService and Y\_InService) received from the switch core.

#### 2.2.5 Egress Transmit Framing

The packet formatter translates custom-formatted packet LUs, reversing the operation performed in the ingress path. Header byte swapping moves the header bytes back to their original position. The converter simultaneously takes and moves the latest available output queue grant (OQG) flow control data from the EDI into the corresponding byte positions that were used for output port addressing in the ingress path. The most recent shared memory grant and the OQG priority (related to the bit map field's OQG) are both stored in the packet qualifier byte that is sent to the PE so it can perform virtual output queuing scheduling for the ingress packets. Idle packets are also generated and sent to the PE in order to maintain continuous flow control information.

#### 2.2.6 Egress PE Interface

The egress PE interface connects the converter to the PE's 32-bit bus. Data and idle packet transfer is controlled by egress transmit framing. The egress PE interface monitors the behavior of TXFULL, controls TXENB accordingly, and generates the Transmit Start of Packet (TXSOP) signal to the PE. A parity bit covering a 32-bit word can be generated according to a dedicated bit in the configuration table registers.

#### 2.3 Converter Flow Control

The PRS28.4G is a shared output buffer switch. In the switch subsystem architecture, the input adapter provides a multiple input queuing structure with one queue per output adapter and per priority. From an architecture standpoint, this queuing structure is a virtual extension of the switch shared output queue and is generally known as virtual output queuing (VOQ).

From a queuing standpoint, the converter does not perform any VOQ; it simply provides a unique ingress FIFO queue and a unique egress FIFO queue. From a throughput standpoint, the converter is nonblocking with regard to the switch. Contrarily, the Protocol Engine (PE), which is attached to the switch through the converter, usually has a lower throughput capacity, thus providing a switch speedup factor at the system level.

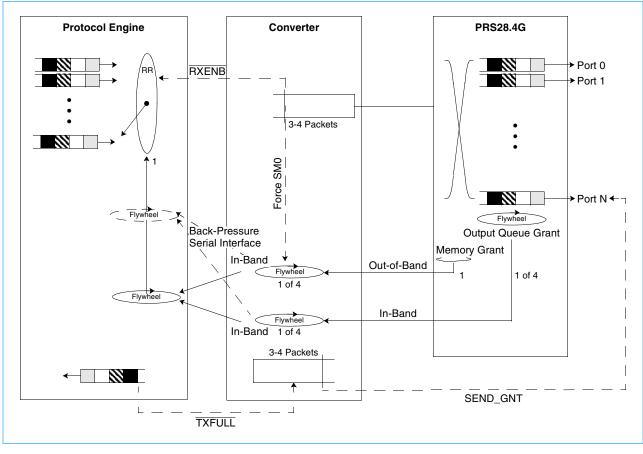

Consequently, this architecture requires two levels of flow control: system-level flow control between the switch (multiple queuing structure) and the PE (VOQ structure), and link-level flow control between the converter and the PE. Additional flow control exists between the converter and the switch. Figure 2-2 is an overview of the two levels of flow control.

PRS28.4G **Protocol Engine** Converter Virtual Converter Output Interface Queueing Ingress FIFO Link-Level Flow Control **Master Grants** Shared Memory Relay System-Level Flow Control Distributed Queueing Output Queue Grants PΕ Converter Egress Interface Buffer Egress FIFO Link-Level Flow Control Send Grants Send Grant Aggregation

Figure 2-2. Flow Control Overview

### 2.3.1 System-Level Flow Control

System-level flow control regulates the ingress traffic from the PE to the switch (see Figure 2-3).

Figure 2-3. System-Level Flow Control

System-level flow control is the flow control issued by the switch towards the VOQ entity. The latter is usually implemented in the PE, which is attached to the switch by means of the converter. System-level flow control information is composed of switch shared memory occupancy information and switch output queue occupancy information. The converter does not process this information, but transparently relays it to the PE.

The converter provides two relay modes: one consists of mapping the flow control into the header of the egress packets, the other consists of mapping the flow control onto a dedicated bus—the selective backpressure bus. Note that the two modes are mutually exclusive.

#### 2.3.1.1 Out-of-Band Flow Control (OBFC)

Flow control information from the switch is mapped on the back-pressure interface—a dedicated serial bus made up of four signals. The per-port grant and shared memory grant information from the switch plane in service are combined and passed via the back-pressure interface to the attached protocol engine. Back-pressure signaling consists of shared memory and per-port back-pressure information for up to four priority levels. The four shared memory priorities are always reported, while the number of per-port priorities reported is a function of the converter configuration in either the 16- or 32-port mode.

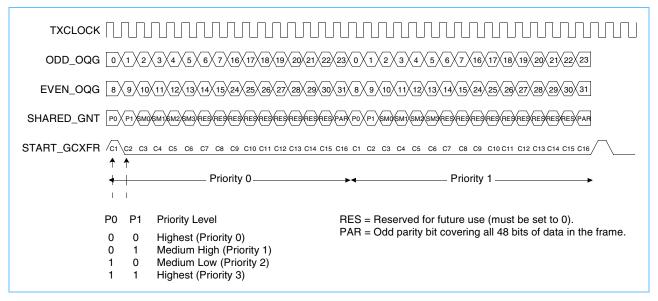

An example of the back-pressure bus timing is given in Figure 2-4. In this example, the converter is configured for two priorities only.

Figure 2-4. Timing of OBFC Grant Control Signaling

The framing of the back-pressure serial link is independent of the length of the LU; therefore, it repeats every 16 TXCLOCK (UTXCLK) cycles, providing the latest information about the output queue grant and memory grant status.

#### 2.3.1.2 In-Band Flow Control (IBFC)

Flow control information from the switch is mapped into the header of the egress packets. In this mode, the converter generates a continuous packet flow towards the PE, transmitting idle packets in the absence of any data traffic. This continuous packet flow constantly refreshes the flow control information in the PE.

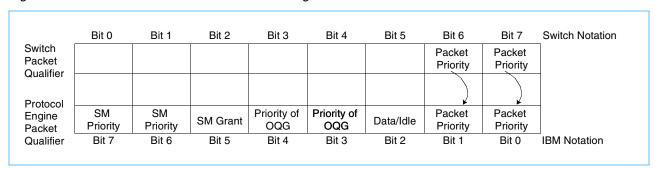

#### Mapping in the Packet Header

- Bits 6 and 7 of the packet qualifier (PQ) encode the priority for which master grant information is relayed. The bit encoding is as follows:

- 00 high priority

- 01 medium-high priority

- 10 medium-low priority

- 11 low priority

- Bit 5 of the PQ is the shared memory grant (master grant) information:

- 0 hold (grant off)

- 1 grant on

- Bits 3 and 4 of the PQ encode the priority for which output queue grant (OQG) information is relayed. The bit encoding is as follows:

- 00 high priority

- 01 medium-high priority

- 10 medium-low priority

- 11 low priority

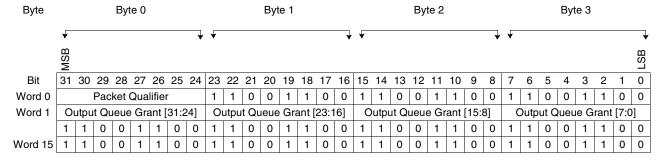

The bit map bytes in the egress packets contain the OQG information. There are four bit map bytes for a  $32 \times 32$  switch and two bit map bytes for a  $16 \times 16$  switch.

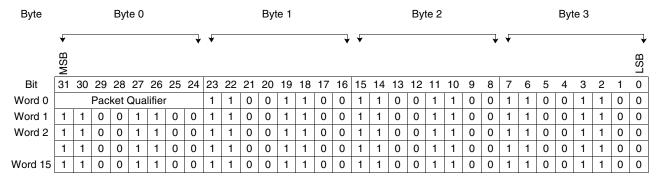

The packet qualifier map in Figure 2-5 demonstrates the mapping of packet priorities from the switch packet qualifier byte into the PE packet qualifier. Because only one 2-bit packet priority can be transferred per byte, and there are up to four priority levels, four packets are required to fully refresh the priority information into the PE. With regard to latency, in the worst case of four priorities, up to four consecutive packets are necessary to provide the PE with a complete view of the switch queuing status.

Figure 2-5. Egress Data Packet Header

|                               | Bit 0                 | Bit 1                 | Bit 2    | Bit 3           | Bit 4           | Bit 5     | Bit 6              | Bit 7              | Switch Notation   |

|-------------------------------|-----------------------|-----------------------|----------|-----------------|-----------------|-----------|--------------------|--------------------|-------------------|

| Switch<br>Packet<br>Qualifier |                       |                       |          |                 |                 |           | Packet<br>Priority | Packet<br>Priority |                   |

|                               |                       |                       |          |                 |                 |           |                    |                    |                   |

| Protocol<br>Engine<br>Packet  | Nested SM<br>Priority | Nested SM<br>Priority | SM Grant | Priority of OQG | Priority of OQG | Data/Idle | Packet<br>Priority | Packet<br>Priority |                   |

| Qualifier                     | Bit 7                 | Bit 6                 | Bit 5    | Bit 4           | Bit 3           | Bit 2     | Bit 1              | Bit 0              | UTOPIA-3 Notation |

#### 2.3.2 Link-Level Flow Control

Link-level flow control regulates the transfer of packets at the PE-converter interface. It allows the converter to stop transmission of packets from the PE when its ingress FIFO reaches a programmable threshold. Similarly, it allows the PE to stop transmission of packets from the converter when its buffering system becomes congested. In turn, this can trigger flow control from the converter to the switch.

Link-level flow control can use either the UTOPIA-3-like flow control signals or in-band procedures in which flow control information is conveyed in the packets transferred at the interface. As detailed hereafter, using an in-band scheme for the link-level flow control requires that the converter be configured in IBFC (system-level in-band flow control) mode.

## 2.3.2.1 Out-of-Band Link-Level Flow Control (OBLC)

#### PE to Converter Flow

When its ingress FIFO reaches the programmable almost full threshold, the converter requests the PE to stop packet transmission by means of the RXENB signal. When requested to stop data packet transmission, the PE can still transmit idle packets on the interface. RXENB operation is described in Section 3.2, Functional Overview, on page 32.

**Note:** This flow control mechanism is rarely used in normal configuration in which the throughput of the PE is lower than the capacity of the converter-switch link capacity. This mechanism is used primarily when the PE throughput is higher than the converter-switch link capacity minus the rate of the generated yellow packets.

#### Converter to PE Flow

When the PE becomes congested, it can stop packet transmission from the converter by means of the TXFULL/TXPAV signal. TXFULL/TXPAV operation is described in Section 3.2.

**Note:** This flow control mechanism is generally used in normal configuration in which the throughput of the PE is lower than the capacity of the converter-switch link capacity. Controlling the egress flow in the converter can cause the egress FIFO to overflow, which triggers the SEND\_GNT signal in the converter to stop packet transmission from the switch.

## 2.3.2.2 In-Band Link-Level Flow Control (IBLC)

#### PE to Converter Flow

Instead of using the UTOPIA-3 RXENB signal to perform link-level flow control, the converter can alter the content of the switch system-level flow control that it relays to the PE in the packet header. While congested, the converter reports a "grant-off" (grant value is '0') for the master grant of the highest priority in the continuous egress packet flow (see Figure 2-6). This has two implications:

- · The converter must be configured in the IBFC mode, and

- During the congestion phase, cyclical reporting of the master grants (from highest to lowest priority) is stopped and only the master grant of the highest priority is reported to the PE (forced "off"). When the congestion has passed, the converter resumes master grant cyclical reporting, reporting the first master grant that would have been reported if no congestion had occurred. In other words, the cyclical counter in the converter does not stop during the congestion phase. The cyclical reporting of the OQG is also maintained during congestion.

**Normal Shared Memory Status Flywheel** SM3 Period SM0 Period P0 P2 SM1 Period SM2 Period **Congested Shared Memory Status Flywheel** SM0 Period SM1 Period P0 SM0 Period SM0 Period

Figure 2-6. Shared Memory Flywheel Operation With Forced Memory 0

#### Converter to PE Flow

Instead of using the UTOPIA-3 TXFULL/TXPAV signal, the PE can perform link-level flow control by setting the four TxPause bits defined in the packet qualifier of the ingress packets to '0' (see Figure 2-7). This inband mechanism requires a continuous ingress packet flow for uninterrupted flow control; therefore, the PE must insert idle packets in the absence of any data packet. If any of the four TxPause bits are not at '0', the converter will not perform flow control.

**Data Packets** LU0 PQ1 BM1 РЗ P7 P11 P15 P19 P23 P27 P31 P35 P39 P43 P47 P51 P55 P52 P56 P12 P16 P20 P24 P36 P44 P48 P0 P4 P28 P40 LU1 BM2 P8 P32 ВМЗ P13 P17 P21 P29 P37 LU2 P1 P5 P9 P25 P33 P41 P45 P49 P53 P57 LU3 P2 BM4 P6 P10 P14 P18 P22 P26 P30 P34 P38 P42 P46 P50 P54 P58 C10 C11 C12 C13 C14 C15 C16 C1 C2 СЗ C4 C5 C6 C7 C8 C9 Packet <sup>1</sup>Packet Qualifier Byte (PQ) TxPause Bit 0 Backup Bit 2 Bit 3 **Priority Bits** Idle Packet 0 0 0 0 Highest Red (active) 0 0 Medium High 1 1 Red (backup) 0 1 0 Medium Low Blue (unfiltered) 1 1 Lowest **Idle Packets for** LU0 PQ<sup>2</sup> CC **In-Band Flow Control** (Must be discarded after use) LU1 CC LU2 CC LU3 CC xPause TxPause xPaus <sup>2</sup>Packet Qualifier Byte (PQ) 0 0 0 Bit 3 0 0 Highest 0 Medium High 0 1 0 0 Medium Low 0 0 1 0 TxPause Lowest 0 0 1 ΑII 1 1 1 1 None 0 0 0

Figure 2-7. Ingress TxPause Flow Control Insertion

## 2.3.3 Converter Configurations

Table 2-1 summarizes the various flow control configurations.

Table 2-1. Flow Control Configurations

| Link-Level              | In-B                                                                | and Flow Control (IB                   | FC) <sup>1</sup>                                                                   | Out-of-Band Flow Control (OBFC)                                           |                                |                         |  |

|-------------------------|---------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------|-------------------------|--|

| Flow                    | System-Level<br>Flow Control                                        | Link-Level F                           | low Control                                                                        | System-Level                                                              | Link-Level Flow Control        |                         |  |

|                         |                                                                     | Protocol Engine                        | Converter                                                                          | Flow Control                                                              | Protocol Engine                | Converter               |  |

| IBLC                    | Switch SMG and<br>OQG mapped in<br>packet header;<br>cycling scheme | TxPause bits = '0000' in packet header | SMG of highest pri-<br>ority forced to '0';<br>cycling scheme<br>disrupted for SMG |                                                                           | Not Applicable                 |                         |  |

| OBLC                    | Switch SMG and<br>OQG mapped in<br>packet header;<br>cycling scheme | UTOPIA signal:<br>TXFULL/TXPAV         | UTOPIA signal:<br>RXENB                                                            | Switch SMG and<br>OQG mapped in<br>dedicated back-<br>pressure serial bus | UTOPIA signal:<br>TXFULL/TXPAV | UTOPIA signal:<br>RXENB |  |

| Continuous packet flow. |                                                                     |                                        |                                                                                    |                                                                           |                                |                         |  |

#### 2.3.4 Latency

This section provides the latencies for the flow control procedures described above and for the data path. Figure 2-8 through Figure 2-15 must be taken into account in the system design (for example, threshold setting, etc.).

## 2.3.4.1 System-Level Flow Control

In-Band Flow Control (IBFC)

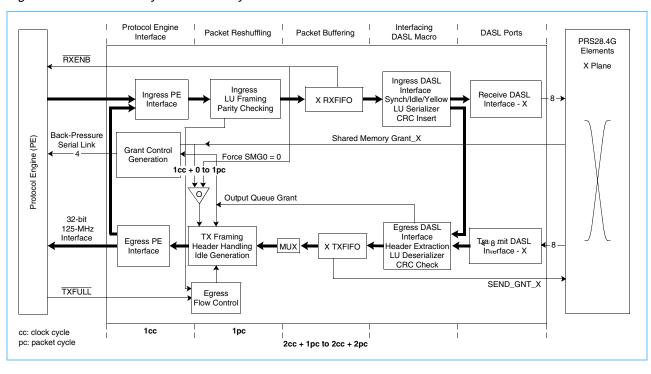

Figure 2-8. IBFC Output Queue Grant Latency

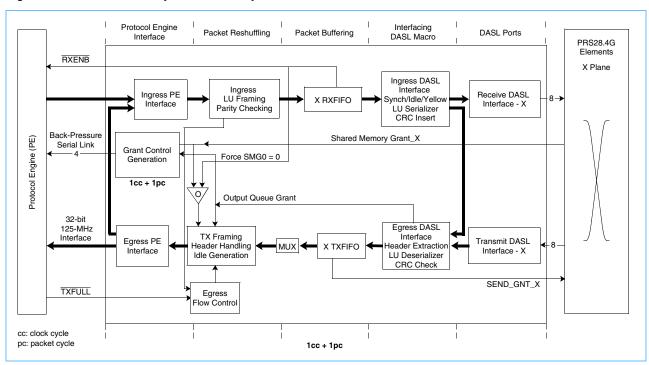

Figure 2-9. IBFC Memory Grant Latency

#### Out-of-Band Flow Control (OBFC)

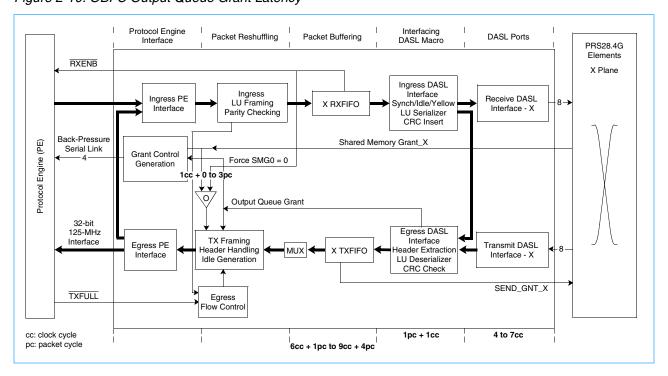

Figure 2-10. OBFC Output Queue Grant Latency

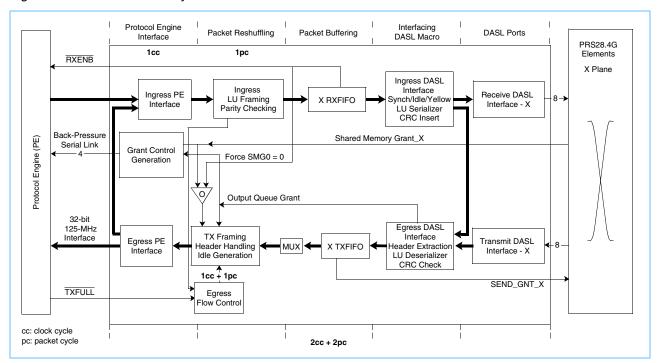

Figure 2-11. OBFC Memory Grant Latency

## 2.3.4.2 Link-Level Flow Control

In-Band Link-Level Flow Control (IBLC)

Figure 2-12. TxPause Latency

Figure 2-13. Force Shared Memory 0 Latency

## Out-of-Band Link-Level Flow Control (OBLC)

See Section 3.2, Functional Overview, on page 32 for a discussion of the UTOPIA-3-like interface timing.

#### 2.3.4.3 Data Path

Figure 2-14. Ingress Data Latency

Figure 2-15. Egress Data Latency

#### 2.4 Switch Flow Control

#### 2.4.1 Latency

The latency within the PRS28.4G is:

Minimum: 3.4 LU size Maximum: 4.6 LU size

Latency is measured from the LU first byte in to the LU first byte out. The latency figures above include both the DASL receive (RX) and transmit (TX) latencies.

The total latency of the switch port grant and memory grant flow control loops is the minimum/maximum across all possible phase relationships of input and output packet boundaries. The "loop" includes the following steps:

- 1. Updating the switch port fill

- 2. Updating the switch memory fill

- 3. Comparing the fill to a threshold

- 4. Resynchronizing to a grant coding scheme

- 5. Propagating grants to the attached device

- 6. Propagating a packet to the switch

Once the packet is in the switch core, the average latency delay (not including the DASL latency) is:

- Once a packet is in the input controller and its arrival changes the memory grant information, the MEM\_GNT[3:0] pins are updated in [±1 LU Size] + [±4 Byte Clocks].

- Once a packet is in the input controller and its arrival changes the OQG information, the in-band OQG information appears in [±2 LU Size] + [±NbOfPriorities × LU Size].

DASL latency adds 4- to 7-byte clock cycles on ingress and a 2-byte clock cycle on egress.

The switch output port scheduling is not packet synchronized, so the output ports do not send the Transmit Start-of-Packet (TXSOP) signal at the same time. The TXSOP signals are shifted by one clock cycle. The output ports do not send the OQG information for the same priority at the same time, either. The output ports operate independently.

If an entering packet changes a grant status, then it takes at least *P* clock cycles (*P* ranging from 1 to 16) to align the output packet boundary, and may require the entry of another four packets (if using four priorities) before a packet carrying the priority of the updated grant enters. At the switch output port, the packet that forced the change triggers the start of the first packet that contains the updated grant. Therefore, the latency between a queue threshold being exceeded and the OQG information for that queue being sent out on all packets for all output ports is:

Minimum: P + 16Maximum: P + 64

## 2.4.2 Threshold Setting

The shared memory thresholds within the switch must be set to low sharing and, consequently, the output queue thresholds must be set to their lowest thresholds (that is, priority 3 set to 16 packets, priority 2 set to 32 packets, priority 1 set to 48 packets, and priority 0 set to 64 packets).

The PRS28.4G Shared Memory Threshold Registers 0 and 1 must be set according to the complete flow control loop: Converter + Protocol Engine + Switch Flywheel.

#### 2.4.3 Flow Control Violation

For operation with the converter, the switch flow control check, bit 10 of the PRS28.4G Mode Register, must be disabled.

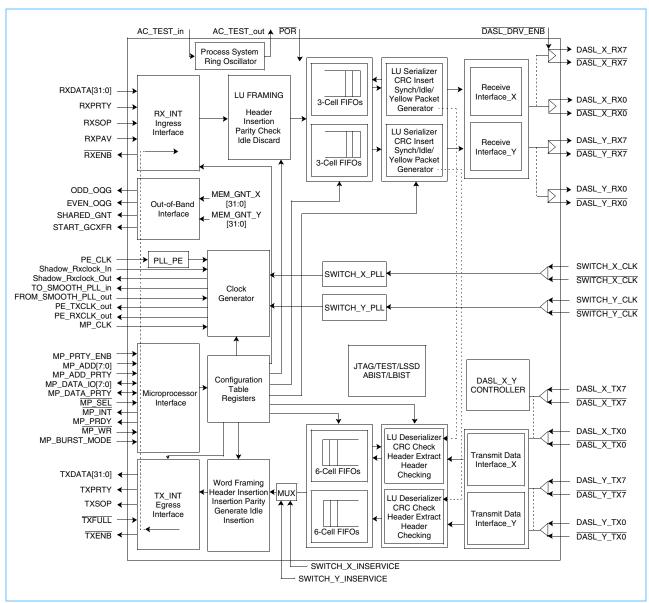

## 3. Functional Description

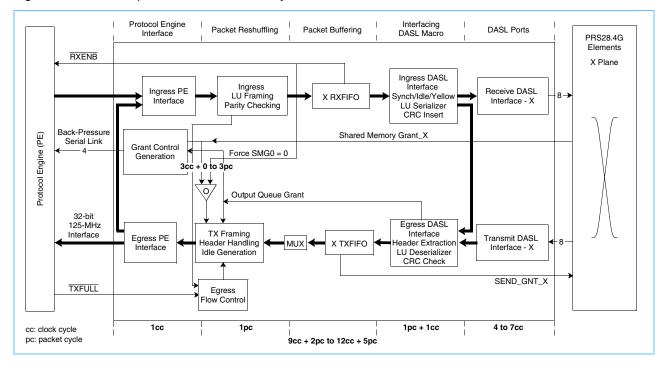

This section describes each functional block (see Figure 3-1) of the IBM Packet Routing Switch Serial Interface Converter (the converter). The description is by layer and covers both the ingress and the egress functions because, in general, they are completely symmetrical.

Figure 3-1. Converter Functional Block Diagram

The ingress block is the receive path between the Protocol Engine (PE) and the rest of the converter logic. The egress block is the transmit path between the converter transmit logic and the PE.

The timing on the UTOPIA-3 interface is the same for out-of-band flow control (OBFC) and for in-band flow control (IBFC) modes. When operating in IBFC mode, the UTOPIA-3 flow control signals (RXENB at ingress and TXFULL at egress) are not normally used because the packet header carries all of the required information. However, if the PE performs OBFC, UTOPIA-3 signals can be used for performing the link-level flow control. In IBFC, idle packets flow through the interface to maintain a continuous stream of flow control information.

## 3.1 Data Interface Between the Converter and the Protocol Engine

UTOPIA-3 bit/byte notation is used throughout the PE interface description. After byte formatting (which reshuffles the byte position to match the PRS28.4G DASL interface), the switch DASL bit/byte notation is used. See Figure 3-2.

Figure 3-2. Bit and Byte Notation

#### 3.2 Functional Overview

The converter ingress and egress interfaces are consistent with a subset of the UTOPIA-3 specifications:

- Single physical layer (PHY) interface mode (connection between one converter and one protocol engine).

- Typical operating clock range is 100 to 111 MHz to match the switch clock rate (up to 111 MHz), but an interface clock rate as low as 50 MHz is supported.

- Only 32-bit data paths.

- Packet format is 64 to 80 bytes (programmed in the converter during configuration).

- Only packet-level handshake mode (use of signals RXPAV in receive path and TXPAV in transmit path).

- RXENB and TXENB signals cannot be used to perform flow control at an octet level, which is allowed in UTOPIA-2 specifications. Each packet transfer initiated in either the ingress or egress direction will continue to flow until the current packet transfer is completed, eliminating the ability to insert wait states during the current packet transfer.

Functional Description

Page 32 of 180

- The assertion of the RXENB signal depends only on the ingress FIFO filling status and so may be asserted while the RXPAV signal is deasserted.

- Wait state insertion on the bus is only allowed between transmission of two different packets.

- All input and output signals are latch-bound, meaning that inputs are clocked directly into latches and outputs emerge directly from latches. Therefore, a device (either the PE or the converter) responds in not less than two clock cycles after the initiating signal is sent across the interface.

- All output signals are generated and all input signals are sampled on low-to-high clock transitions.

- All signals are active high, unless the signal name has an overbar  $(\overline{xxx})$ .

## 3.2.1 Ingress Interface

#### 3.2.1.1 Bus Protocol

The ingress block is the receive path between the PE and the converter. The PE sends data to the converter according to the following protocol:

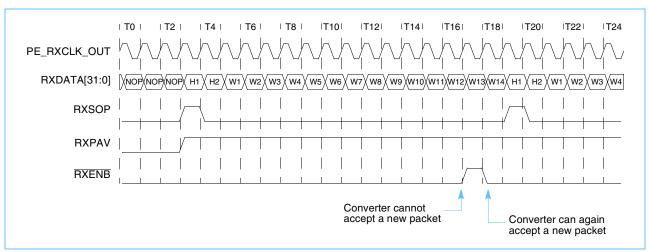

- The converter provides the receive clock signal, PE\_RXCLK\_OUT.

- The PE asserts the RXPAV signal when it is ready to send at least one complete packet on the bus.

- The converter asserts the RXENB signal when it is ready to receive at least one complete packet.

- Receive packet transfer can start once the PE detects RXENB asserted while asserting RXPAV.

- The assertion of the RXSOP signal during one clock cycle indicates the start of a receive packet transfer.

- RXDATA[31:0] is transferred on each low-to-high clock transition, and the first data word of the packet is transferred simultaneously with the RXSOP signal.

- The converter deasserts the RXENB signal two clock cycles before the end of the current packet transfer if it cannot accept an immediate transfer of the subsequent packet from the PE.

This protocol applies when a user wishes to use OBLC procedures. If IBLC is used, there is no need for using the RXENB and RXPAV signals because all of the flow control is performed in band (through the packet header). Also under IBFC, if there is no data packet to be sent by the PE, the PE inserts an idle packet that is then discarded by the converter.

Table 3-1. Ingress I/O Pin Descriptions

| Pin Name     | Туре                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE_RXCLK_OUT | Output                    | Receive Clock is issued from two clock domains:  At power-on reset (POR), it is connected to the microprocessor clock until the POR is completed.  After POR is completed, it is generated by either the smooth Phase-Locked Loop (PLL) clock out (derived from the Switch_X_PLL or Switch_Y_PLL configuration register) or by an externally provided clock (e.g., the 50- to125-MHz PE clock).  The PE_RXCLK_OUT source is selected according to the programming of the "PE_RXCLK_OUT_source_[[1:0]" bits in the configuration table registers.                                                                 |

| RXDATA[31:0] | Input                     | Receive Data is transferred from the PE to the converter on a 32-bit word basis.  LSB RXDATA[0]  MSB RXDATA[31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXPRTY       | Input                     | Receive Data Parity bit is the odd parity bit over the 32 RXDATA bits. The parity check mode is enabled or disabled by the RXPRTY_enb_l bit in the configuration table registers.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXPAV        | Input<br>(active<br>high) | The PE asserts Receive Packet Available when at least one complete packet is ready to be transmitted on the bus. The signal remains asserted during the current packet transfer (packet-level handshake) and indicates, in the cycle following the last word of the current packet, if there is (RXPAV asserted) or is not (RXPAV deasserted) a new packet to transfer. RXPAV must be asserted when operating in IBFC mode.                                                                                                                                                                                      |

| RXSOP        | Input<br>(active<br>high) | The PE asserts Receive Start of Packet for one clock cycle when it starts a packet transfer to indicate the packet's first 32-bit data word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RXENB        | Output<br>(active<br>low) | The converter asserts Receive Enable to indicate its readiness to receive at least one complete packet. The signal remains asserted during the transfer of the current packet (packet-level handshake) and, two cycles before the end of the current packet transfer, indicates whether it is (RXENB asserted) or is not (RXENB deasserted) ready to receive a new complete packet. As this signal is pipelined, the PE will respond at least two clock cycles after the RXENB is asserted or deasserted. The behavior of RXENB depends on the value of the RxEnabMode bit of the Ingress_PE_Interface register. |

## 3.2.1.2 Ingress Operation and Timing

Figure 3-3. Ingress Timing for RXENB Deasserted by Converter for One Clock Cycle

Ingress Operation for 64-Byte Packet Flow Control with the RxEnabMode Bit of the Ingress\_PE\_Interface Register at '0'

Functional Description prssi.03.fm Page 34 of 180 April 23, 2001

Figure 3-4. Ingress Timing for RXENB Deasserted by Converter When the RxEnabMode Bit of the Ingress\_PE\_Interface Register is High

Figure 3-5. Ingress Timing for RXPAV Deasserted by Protocol Engine for One Clock Cycle Ingress Operation for 64-Byte Packet Flow Control

Figure 3-6. Ingress Timing for RXPAV Deasserted by Protocol Engine for Three Clock Cycles Ingress Operation for 64-Byte Packet Flow Control

Figure 3-7. Ingress Timing for Back-to-Back Packets From Protocol Engine Receive Operation for 64-Byte Back-to-Back Packets

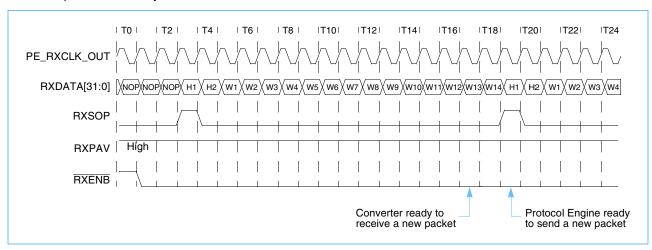

#### 3.2.2 Egress Interface

#### 3.2.2.1 Bus Protocol

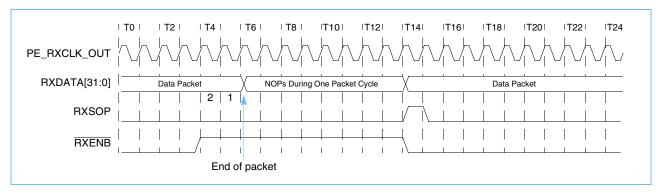

The egress block is the transmit path between the converter and the PE. The converter sends data to the PE according to the following protocol:

- The converter provides the transmit clock signal, PE\_TXCLK\_OUT.

- The PE asserts the TXPAV signal when it is ready to receive at least one packet from the converter.

- When the converter is ready to send at least one packet on the bus and the PE has asserted the TXPAV signal, the converter starts the transfer by simultaneously asserting the TXSOP and TXENB signals.

- TXDATA[31:0] is transferred on each low-to-high clock transition, and the first data word of the packet is transferred simultaneously with the TXSOP signal.

- The PE deasserts the TXPAV signal at least four cycles before the end of the current packet transfer if it cannot accept an immediate transfer of the subsequent packet from the converter.

This protocol applies when a user wishes to use OBLC procedures. Under IBFC and IBLC operation, there is no need for using TXENB/TXFULL (TXPAV) protocols because all of the flow control is performed in band (through the packet header). Also under IBFC, if there is no data packet to be sent by the converter, the converter inserts an idle packet that is then discarded by the PE.

Functional Description prssi.03.fm Page 36 of 180 April 23, 2001

Table 3-2. Egress I/O Pin Descriptions

| Pin Name        | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE_TXCLK_OUT    | Output | Transmit Clock is issued from two clock domains:  At POR, it is connected to the microprocessor clock until the POR is completed.  After the POR is completed, it is generated by either the smooth PLL clock out (derived from the Switch_X_PLL or Switch_Y_PLL configuration register) or by an externally provided clock (e.g., the 50- to125-MHz PE clock).  The PE_TXCLK_OUT source is selected according to the programming of the "PE_TXCLK_OUT_source_ [1:0]" bits in the configuration table registers.                                                                                                                                                                                                                         |

| TXDATA[31:0]    | Output | Transmit Data is transferred from the converter to the PE on a 32-bit word basis.  MSB TXDATA[31]  LSB TXDATA[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TXPRTY          | Output | Transmit Data Parity bit is the odd parity bit over the 32 TXDATA bits. The parity check mode is enabled and disabled by the TXPRTY_enb_l bit in the configuration table registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TXPAV<br>TXFULL | Input  | These are two names for the same signal.  The PE asserts Transmit Packet Available/TXFULL to an appropriately high level when it is ready to receive at least one complete packet. During a packet transfer, the PE has at least four cycles before the end of the current packet transfer to assert TXPAV if it can accept immediate transfer of the subsequent packet or to deassert TXPAV if it cannot.  When the converter detects TXPAV deasserted, it may only transmit four more 32-bit data words to the PE. It is recommended that the PE keep TXPAV signal asserted until four cycles before the end of the packet transfer.  TXPAV and TXFULL lines have the same timing.  TXPAV asserted is equivalent to TXFULL deasserted. |

| TXSOP           | Output | The converter asserts Transmit Start of Packet for one clock cycle when it starts a packet transfer to indicate the packet's first 32-bit data word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TXENB           | Output | The converter asserts Transmit Enable to indicate that valid 32-bit data words are on the bus. When TXPAV is asserted during a packet transfer (at least four clock cycles before the end of the current packet transfer), the converter indicates, one clock cycle after the last word of the current packet, whether it is (TXENB asserted) or is not (TXENB deasserted) ready to send a new complete packet. When TXPAV is deasserted during a packet transfer (at least four clock cycles before the end of the current packet transfer), TXENB is deasserted four clock cycles afterwards to stop the transfer.                                                                                                                     |

## 3.2.2.2 Egress Operation and Timing

Figure 3-8. Egress Timing for Back-to-Back Packets

Transmit Operation for 64-Byte Back-to-Back Packet Transmission

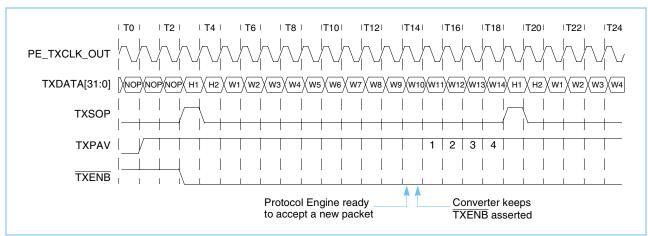

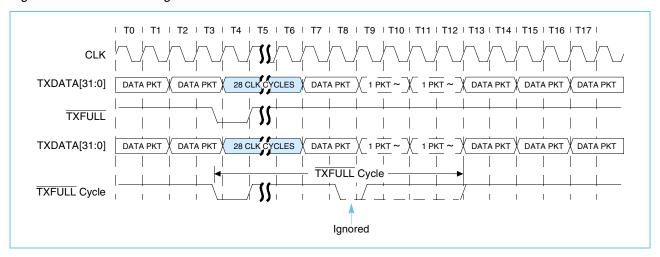

## 3.2.3 TXFULL Timing Restriction

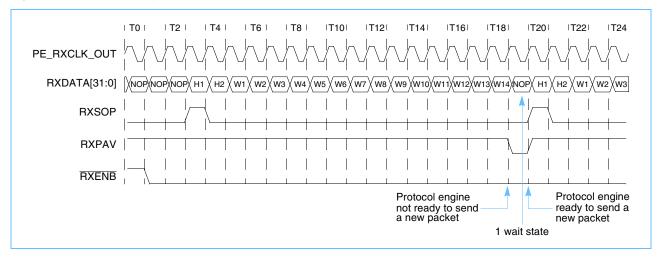

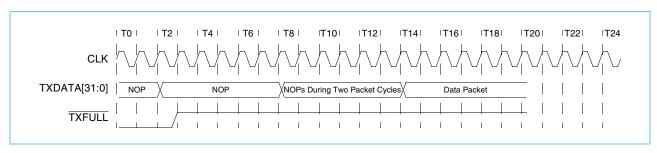

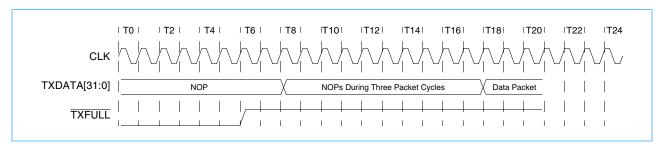

When the PE asserts TXFULL to stop the flow of packets, its effect is extended for 2 packet cycles from the end of the current packet. After the first packet following the deassertion of TXFULL by the PE, the converter inserts two empty slots of idle (no data) before traffic resumes. If the PE reasserts TXFULL upon the reception of the first packet during the TXFULL cycle, it will be ignored until the end of the complete cycle. See Figure 3-9.

Figure 3-9. TXFULL Timing Restriction

## 3.2.4 Timing for TXFULL Deasserted

If the PE deasserts TXFULL more than four clock cycles before the end of the current idle packet, the converter will transmit the packets after a wait of two packet cycles (see Figure 3-10). If the PE deasserts TXFULL less than four clock cycles before the end of the current idle packet, the converter will transmit the packets after a wait of three packet cycles (see Figure 3-11).

Figure 3-10. Timing for TXFULL Deasserted by PE More Than Four Clock Cycles Before the End of the Current Idle Packet

Functional Description prssi.03.fm Page 38 of 180 April 23, 2001

Figure 3-11. Timing for TXFULL Deasserted by PE Less Than Four Clock Cycles Before the End of the Current Idle Packet

## 3.3 Packet Reshuffling

### 3.3.1 Ingress Receive Logical Unit Framing

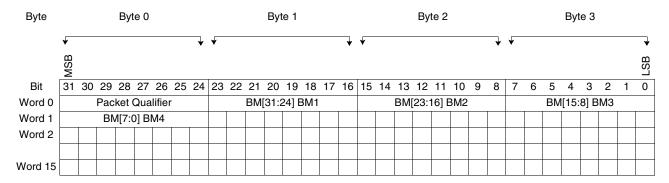

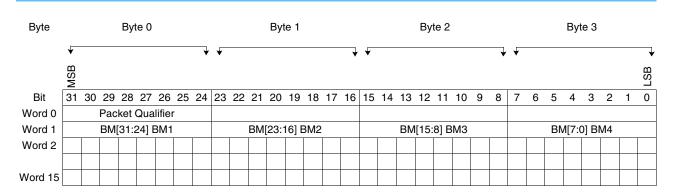

The ingress LU formatter is the interface between the PE interface logic and the ingress FIFO (RXFIFO) that translates various types of ingress packet formats into the switch LU format as defined in the converter configuration registers.

Data inputs are in a four-byte format. The ingress LU formatter extracts TxPause flow control information from the incoming packet qualifier byte. The incoming packet is comprised of 16 to 20 32-bit words. Packet reshuffling stores the packet in the switch format in four LUs that, when fully assembled, are forwarded to the RXFIFO.

The ingress LU formatter:

- Discards idle packets (IBFC mode only)

- Extracts send grant flow control information from the incoming packet qualifier byte (IBFC mode only)

- Modifies the packet qualifier byte into switch format and computes the associated parity (IBFC mode only)

- Changes the position of the bit map bytes in the packet header

- Recognizes any bus parity error reported on the PE interface signal RXPRTY\_error

- Rejects the forwarding of a packet to the RXFIFOs in the event of any bus or header error (depending on the configuration register setting)

- Checks switch header parity bit in the packet qualifier byte (OBFC mode only)

## 3.3.1.1 Header Byte Reshuffling

The header bytes are moved according to the content of the "byte positioning in LU formatter" configuration fields. These allow any byte contained in the first four words of a packet to be moved to any other byte position in the master LU.

## 3.3.1.2 Input/Output Packet Format

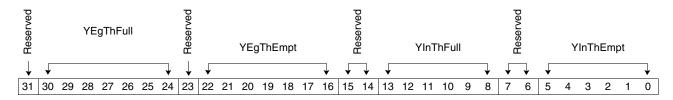

The following tables highlight the position of the different information fields in an incoming packet. All bytes in the first four words of a packet can be repositioned in the switch header according to the formatter field in the configuration registers. The data source is based on a word/byte coordinate in a nibble. The first two bits correspond to the word selection; the last two bits correspond to the byte selection.