June 1990

#### Distinctive Features.

- VME 1210 provides two device chip set for slot 1 master bus controller and single level arbiter

- VME 1220 provides two device chip set for non-slot 1 master bus controller

- Integrates 48ma and 64ma **VMEbus** signals:AS\*,DS0\*,DS1\*,WRITE\*,BR\*,BBSY\*

- Integrates input hysteresis buffers

- Supports Release When Done (RWD) and Release On Request (ROR) protocols

- · Supports address pipelining, block transfers, and early BBSY\* release

- Available in Commercial, Industrial and Military temperature ranges

#### Programmable Version Available

If the VME 1210/1220 does not match the requirements of the design, a programmable version is available (the PLX 464) which allows the user to customize all inputs. outputs and logic. Programming is performed using industry standard tools such as ABEL<sup>tm</sup> and CUPL<sup>tm</sup> software and commonly available PLD programming hardware. Contact PLX for a data sheet on the PLX 464 and other PLX products.

#### **Applications**

- VMEbus masters residing in slot 1 boards (VME 1210)

- VMEbus masters residing in non-slot 1 boards (VME 1220)

#### General Description

The VME 1210: The VME 1210 is comprised of the VME 1210A and the VME 1210B for slot 1 applications. The devices are CMOS and packaged in 24 pin 300 mil wide DIPs or 28 pin J-type LCCs. The VME 1210A provides bus requesting, local arbitration, and single level system arbitration. The VME 1210B functions as the VMEbus controller. The requester initiates a VMEbus request from the local master's bus request for a data or interrupt cycle. The bus controller controls the bus after initiation of a bus cycle and relinquishes the bus at the end of the bus cycle. The bus controller supervises the handshaking between the local master CPU and the slave modules.

The VME 1220: The VME 1220 is comprised of the VME 1220A and the VME 1220B for non-slot 1 applications. The devices are CMOS and packaged in 24 pin 300 mil wide DIPs or 28 pin J-type LCCs. The VME 1220A provides bus requesting and local arbitration. The VME 1220B functions as the VMEbus controller. The requester initiates a VMEbus request from the local master's bus request for a data or interrupt cycle. The bus controller controls the bus after initiation of a bus cycle and relinquishes the bus at the end of the bus cycle. The bus controller supervises the handshaking between the local master CPU and the slave modules.

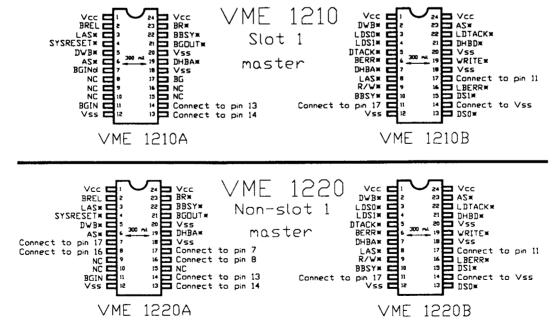

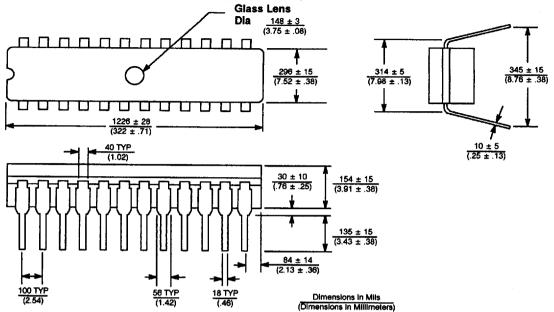

Figure 1. Pinout of VME 1210/1220 (DIPs)

Patent Pending ABEL is a trademark of Data I/O Corp. CUPL is a trademark of Logical Devices, Inc.

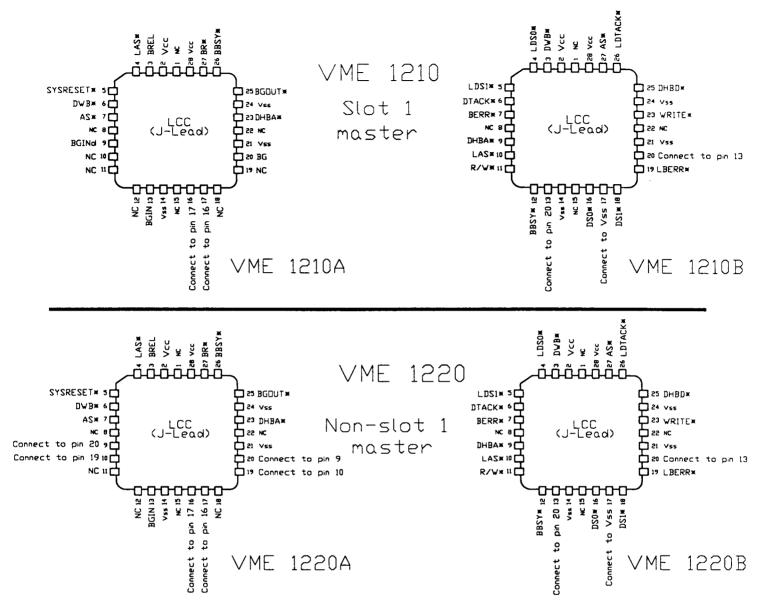

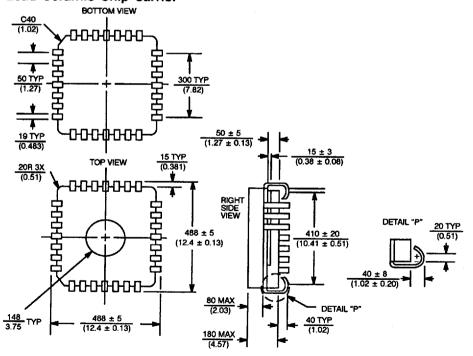

Figure 2. Pinout of VME 1210/1220 (LCCs)

# Pin Description

# **VME 1210A**

| Pin #<br>LCC  | Pin #<br>DIP | Signal    | Туре | Function                                                            |  |

|---------------|--------------|-----------|------|---------------------------------------------------------------------|--|

| 3             | 2            | BREL      | 1    | Active high; Bus release signal indicating BBSY* can be released.   |  |

| 4             | 3            | LAS*      | l    | Active low; Address strobe from local master.                       |  |

| 5             | 4            | SYSRESET* | I    | Active low; VMEbus System Reset.                                    |  |

| 6             | 5            | DWB*      | I    | Active low; Device wants bus, local master requests control of bus. |  |

| 7             | 6            | AS*       | 1    | Active low; VMEbus Address Strobe.                                  |  |

| 9             | 7            | BGINd     | 1    | Active high; Delayed BG output via delay line.                      |  |

| 10            | 8            | NC        | I    | No Connect.                                                         |  |

| 11            | 9            | NC        | ı    | No Connect.                                                         |  |

| 12            | 10           | NC        | 1    | No Connect.                                                         |  |

| 13            | 11           | BGIN      | Ī    | Active high; Inverted VMEbus Bus Grant In signal, BGIN*.            |  |

| 14,21,<br>24  | 12,18,<br>20 | Vss       |      | Chip Ground                                                         |  |

| 16            | 13           | -         | 0    | Connect to Pin 14 (DIP) or Pin 17 (LCC).                            |  |

| 17            | 14           | •         | 1    | Connect to Pin 13 (DIP) or Pin 16 (LCC).                            |  |

| 18            | 15           | NC        | 0    | No Connect.                                                         |  |

| 19            | 16           | NC        | 0    | No Connect.                                                         |  |

| 20            | 17           | BG        | 0    | Active high; Bus grant output from arbiter.                         |  |

| 23            | 19           | DHBA*     | 0    | Active low; Device has bus address, address buffer enable.          |  |

| 25            | 21           | BGOUT*    | 0    | Active low; VMEbus Bus Grant Out signal.                            |  |

| 26            | 22           | BBSY*     | 1/0  | Active low, 48 mA open collector; VMEbus Bus Busy signal.           |  |

| 27            | 23           | BR*       | 0    | Active low, 48 mA open collector; VMEbus Bus Reque signal.          |  |

| 2,28          | 1,24         | Vcc       |      | +5 V Chip Power                                                     |  |

| 1,8,<br>15,22 | -            | NC        | -    | No Connect.                                                         |  |

# **Pin Description**

**VME 1220A**

| Pin #<br>LCC  | Pin #<br>DIP | Signal    | Туре | Function                                                            |  |

|---------------|--------------|-----------|------|---------------------------------------------------------------------|--|

| 3             | 2            | BREL      | 1    | Active high; Bus release signal indicating BBSY* can be released.   |  |

| 4             | 3            | LAS*      | -    | Active low; Address strobe from local master.                       |  |

| 5             | 4            | SYSRESET* | 1    | Active low; VMEbus System Reset.                                    |  |

| 6             | 5            | DWB*      | i    | Active low; Device wants bus, local master requests control of bus. |  |

| 7             | 6            | AS*       | 1    | Active low; VMEbus Address Strobe.                                  |  |

| 9             | 7            | -         | 1    | Connect to pin 17 (DIP) or pin 20 (LCC).                            |  |

| 10            | 8            | -         | ı    | Connect to pin 16 (DIP) or pin 19 (LCC).                            |  |

| 11            | 9            | NC        | 1    | No Connect.                                                         |  |

| 12            | 10           | NC        | 1    | No Connect.                                                         |  |

| 13            | 11           | BGIN      | ı    | Active high; Inverted VMEbus Bus Grant In signal, BGIN*.            |  |

| 14,21,<br>24  | 12,18,<br>20 | Vss       |      | Chip Ground.                                                        |  |

| 16            | 13           | -         | 0    | Connect to Pin 14 (DIP) or Pin 17 (LCC).                            |  |

| 17            | 14           | <u>-</u>  | 1    | Connect to Pin 13 (DIP) or Pin 16 (LCC).                            |  |

| 18            | 15           | NC        | 0    | No Connect.                                                         |  |

| 19            | 16           | -         | 0    | Connect to pin 8 (DIP) or pin 10 (LCC).                             |  |

| 20            | 17           | -         | 0    | Connect to pin 7 (DIP) or pin 9 (LCC).                              |  |

| 23            | 19           | DHBA*     | 0    | Active low; Device has bus address, address buffer enable.          |  |

| 25            | 21           | BGOUT*    | 0    | Active low; VMEbus Bus Grant Out signal.                            |  |

| 26            | 22           | BBSY*     | 1/0  | Active low, 48 mA open collector; VMEbus Bus Busy signal.           |  |

| 27            | 23           | BR*       | 0    | Active low, 48 mA open collector; VMEbus Bus Request signal.        |  |

| 2,28          | 1,24         | Vcc       |      | +5 V Chip Power                                                     |  |

| 1,8,<br>15,22 | -            | NC        | -    | No Connect.                                                         |  |

# Pin Description

# VME 1210B and VME1220B

| Pin #<br>LCC  | Pin #<br>DIP | Signal  | Туре | Function                                                                                                                                     |  |

|---------------|--------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3             | 2            | DWB*    | 1    | Active low; Device wants bus, local master wants control of VMEbus.                                                                          |  |

| 4             | 3            | LDS0*   | I    | Active low; Lower data strobe from local master.                                                                                             |  |

| 5             | 4            | LDS1*   | 1    | Active low; Upper data strobe from local master.                                                                                             |  |

| 6             | 5            | DTACK*  | ľ    | Active low; VMEbus Data Transfer Acknowledge, data is valid during a read cycle or data has been accepted from the bus during a write cycle. |  |

| 7             | 6            | BERR*   | 1    | Active low; VMEbus Error signal.                                                                                                             |  |

| 9             | 7            | DHBA*   | I    | Active low; Device has bus address, address buffer enable.                                                                                   |  |

| 10            | 8            | LAS*    | ı    | Active low; Address strobe from local master.                                                                                                |  |

| 11            | 9            | R/W*    | 1    | Active high/low; Read or write cycle from local master.                                                                                      |  |

| 12            | 10           | BBSY*   | 1    | Active low; VMEbus Busy, local master controls bus.                                                                                          |  |

| 13            | 11           | •       | 1    | Connect to pin 17 (DIP) or pin 20 (LCC).                                                                                                     |  |

| 14,21,<br>24  | 12,18,<br>20 | Vss     |      | Chip Ground.                                                                                                                                 |  |

| 16            | 13           | DS0*    | 0    | Active low; 64ma VMEbus lower Data Strobe signal, indicates valid data on bus.                                                               |  |

| 17            | 14           | -       | 1    | Connect to Vss.                                                                                                                              |  |

| 18            | 15           | DS1*    | 0    | Active low; 64ma VMEbus upper Data Strobe signal, indicates valid data on bus.                                                               |  |

| 19            | 16           | LBERR*  | 0    | Active low; Open collector signal, bus error to local master.                                                                                |  |

| 20            | 17           | -       | 0    | Connect to pin 11 (DIP) or pin 13 (LCC).                                                                                                     |  |

| 23            | 19           | WRITE*  | 0    | Active low; 48ma VMEbus Write signal, indicates bus read or write cycle.                                                                     |  |

| 25            | 21           | DHBD*   | 0    | Active low; Device has bus data, data buffer enable.                                                                                         |  |

| 26            | 22           | LDTACK* | 0    | Active low; Open collector signal, data acknowledge to local master.                                                                         |  |

| 27            | 23           | AS*     | 0    | Active low; 64mA VMEbus Address Strobe signal, indicates valid address on bus.                                                               |  |

| 2,28          | 1,24         | Vcc     |      | +5 V Chip Power                                                                                                                              |  |

| 1,8,<br>15,22 | -            | NC      | -    | No Connect.                                                                                                                                  |  |

#### Detailed Description\_

The VME 1210/1220 initiates, executes, and terminates VMEbus data transfer cycles. The VME 1210 integrates a single level system arbiter to function as a slot 1 master. The VME 1220 handles local bus arbitration to function as a non-slot 1 master. The following section describes how the VME 1210/1220 performs in a data transfer cycle.

### Initiating a Bus Request

The local master (CPU, DMA controller, or interrupt handler for example) can initiate a bus request by asserting DWB\* and LAS\*. After receiving DWB\* and LAS\* asserted, the VME 1210/1220 will drive BR\* (VMEbus request signal) low provided that the VME 1210/1220 itself is not driving BBSY\* low. Note that BR\* may be connected to any arbitration level (0-3).

#### **Arbitration**

The VME 1210 integrates a single level system arbiter. The arbiter monitors the local master's bus request or other master's bus requests via BR\*. If the bus is free, BBSY\* is high, the arbiter will assert a bus grant, BG, which is connected to the BGIN input of the local arbiter. The VME 1210 suppresses the BBSY\* glitch.

If the user implements the non-slot 1 VME 1220, the VME 1220A daisy chains the VMEbus grants. The daisy chained BGIN\* from the adjacent master must be inverted and connected to the BGIN input of the VME 1220A's local arbiter. The local arbiters of both the VME 1210A and VME 1220A function in the same manner.

After the VME 1210 asserts BGIN, or receives BGIN from the daisy chain in the case of the VME 1220, the local arbiter portion of the modules arbitrates between DWB\* and BGIN. If DWB\* wins the arbitration (i.e. DWB\* occurs before BGIN) then the VME 1210/1220 will drive BBSY\* low, signifying that the local master has won and now controls the bus. If, however, BGIN wins the arbitration, then the VME 1210/1220 will drive BGOUT\*, which passes the bus grant down the daisy chain to the adjacent master in the system.

The VME 1210A/20A delay samples the asynchronous inputs, BGIN and DWB\*. The VME 1210A requires an external delay line for the synchronization between the output of BG and the input of BGINd. This delay line is also used to meet the 90ns minimum assertion time required for BBSY\*. The VME 1220A does not require an external delay line under some conditions since the time delay is integrated internally (see note in Timing Specifications).

#### **Data Transfer**

The local master does not access the bus until the previous master has relinquished control of the bus. This occurs when AS\*, DTACK\* and BERR\* are deasserted. The bus controller function of the VME 1210/1220 then controls the proper sequencing of the address and data buffer enable signals and strobe signals. The VME 1210/1220 ensures that the

VMEbus minimum address and data set up times of 35ns are met. DSO\* and DS1\* are not asserted until both the data buffer enable signal, DHBD\*, and the address strobe, AS\*, are active.

Two separate address and data enable signals are used to support address pipelining. The VME protocol provides for strobing of address and data separately to improve data transfer rates. The master can broadcast the address of the next cycle while the data transfer of the current cycle is occurring. Under these conditions, DHBA\* is enable as soon as AS\* is disabled. The address for the next cycle can be broadcast while DTACK\* and DSn\* are still low from the current data cycle. When DTACK\* goes high, signifying the end of the current data cycle, DHBD\* enables the data buffers for the next data cycle.

For block transfer cycles, the VME 1210/1220 holds AS\* low and the data strobes, DSO\* and DS1\*, and DTACK\* will strobe after every read or write. The block move cycle will continue as long as DWB\*, LAS\* and AS\* are active.

For a Read-Modify-Write cycle, AS\* will be kept low for two data cycles, a read cycle followed by a write cycle. Again, the cycle will be negated through DWB\*, LAS\* and AS\* de-assertion.

WRITE\* is latched during block moves and address pipelining to hold its level. WRITE\* meets the VMEbus minimum hold time of 10ns.

#### **Bus Release**

The VME 1210/1220 supports release when done (RWD), release on request (ROR), and early BBSY\* release protocols via the bus release signal, BREL.

For RWD operation, BREL will be held low during the data transfer cycle. At the end of the cycle, when the local master wants to release the bus, BREL is asserted thus releasing BBSY\*.

For ROR operation, the external release on bus request logic can be tied to BREL. An external bus request will assert BREL to release BBSY\* at the end of the current data transfer. If no bus requests are pending, then BREL can be kept de-asserted and the local master can maintain BBSY\* low to perform continuous VMEbus data transfer cycles.

For early BBSY\* release operation, BREL is asserted always. BBSY\* will be negated immediately after BGIN is negated by the system arbiter. This allows for overlapping of the next bus arbitration with the current VMEbus data transfer.

With address pipelining and continual single cycling, BREL must be held de-asserted until the final data transfer. BREL can be asserted anytime after the local master asserts LAS\* for the last data transfer.

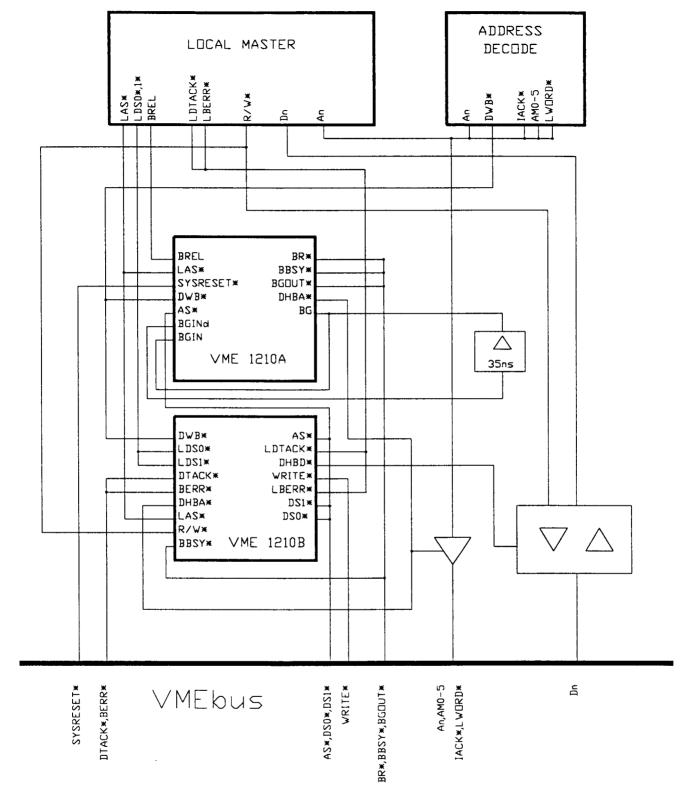

Figure 3. VME 1210 Configuration (Slot 1 master)

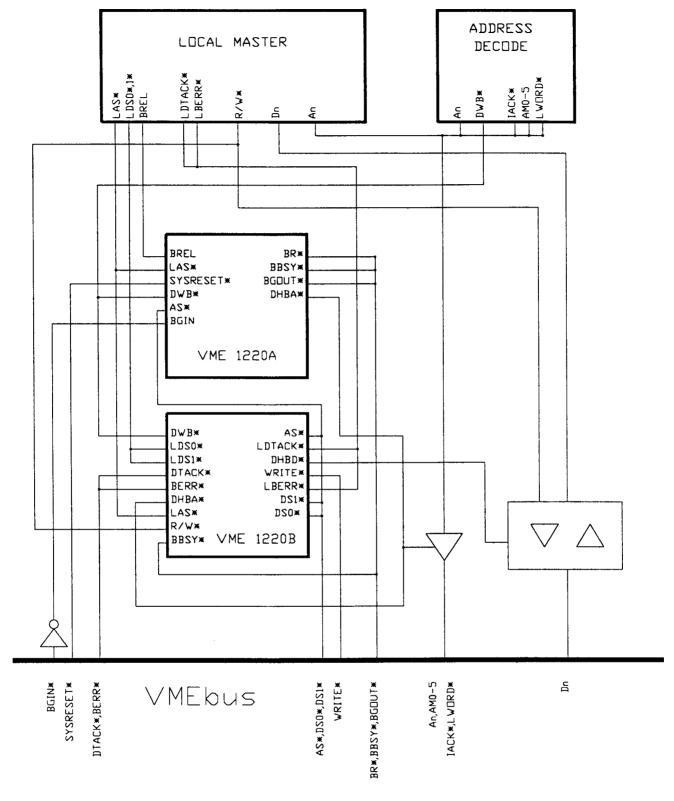

Figure 4. VME 1220 Configuration (Non-slot 1 master)

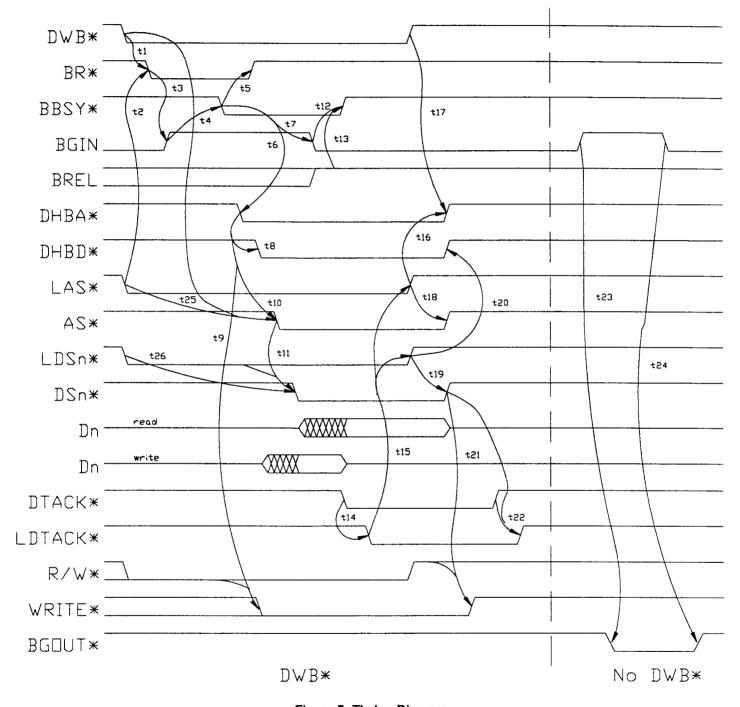

# VME 1210/1220 Timing Waveforms

Figure 5. Timing Diagram

**Timing Specifications**

| Timing     |                                      | Max. Time(<br>otherwise | ns) unless<br>specified |                                                                                                                    |

|------------|--------------------------------------|-------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| Parameters | Signals                              | C-45                    | M-65                    | Description                                                                                                        |

| t1         | DWB* to BR* asserted                 | 90                      | 130                     | If DWB* is asserted after LAS*                                                                                     |

| t2         | LAS* to BR* asserted                 | 90                      | 130                     | If LAS* is asserted after DWB*                                                                                     |

| 13         | BR* to BG asserted                   | 0                       | 0                       | VME 1210 only when internal BR* generate (BG connected to BGIN)                                                    |

|            |                                      | 45                      | 65                      | VME 1210 only when external BR* received (BG connected to BGIN)                                                    |

|            |                                      | System arbiter time     | System arbiter Time     | VME 1220 only                                                                                                      |

| t4         | BGIN to BBSY* asserted               | 125                     | 185                     | VME 1210 only, includes delay line: 55ns for M-65, 45ns for M-55, 35ns for C-45, 40ns for C-35, 60ns for C-25 part |

|            |                                      | 135                     | 195                     | VME 1220 only                                                                                                      |

| t5         | BBSY* to BR* negated                 | 45                      | 65                      |                                                                                                                    |

| t6         | BBSY* to DHBA* asserted              | 45                      | 65                      |                                                                                                                    |

| t7         | BBSY* to BGIN negated                | 45 max                  | 65                      | VME 1210 only                                                                                                      |

|            |                                      | 35 min                  | 55 min                  |                                                                                                                    |

|            |                                      | System arbiter time     | System arbiter time     | VME 1220 only                                                                                                      |

| t8         | DHBA* to DHBD* asserted              | 45                      | 65                      |                                                                                                                    |

| t9         | DHBA* to WRITE* asserted             | 45                      | 65                      | Conditional upon R/W* value                                                                                        |

| t10        | DHBA* to AS* asserted                | 90<br>70 (min.)         | 130                     | Ensures 35ns minimum address to AS* and data to DSn* set up times                                                  |

| t11        | AS* to DSn* asserted                 | 45                      | 65                      |                                                                                                                    |

| t12        | BGIN to BBSY* negated                | 80 max                  | 120 max                 | VME 1210 only;                                                                                                     |

|            |                                      | 70 min                  | 110 min                 | VME 1210 only; t7min + t12min ≥ 90 ns min<br>BBSY* assertion                                                       |

|            |                                      | 135 max                 | 195 max                 | VME 1220 only                                                                                                      |

|            |                                      | 105 min                 | 165 min                 | VME 1220 only. (see note below)                                                                                    |

| t13        | BREL to BBSY* negated                | 45                      | 65                      | Valid only when BREL is asserted after BGIN is negated                                                             |

| t14        | DTACK* to LDTACK* asserted           | 45                      | 65                      |                                                                                                                    |

| t15        | LDTACK* to LAS*/LDSn* negated        | @ Local master          | @ Local master          | Local master's time to negate strobes                                                                              |

| t16        | LAS* to DHBA* negated                | 45                      | 65                      | If DWB* already negated                                                                                            |

| t17        | DWB* to DHBA* negated                | 45                      | 65                      | If LAS* already negated                                                                                            |

| t18        | LAS* to AS* negated                  | 50                      | 72                      |                                                                                                                    |

| t19        | LDSn* to DSn* negated                | 50                      | 72                      |                                                                                                                    |

| 120        | LDSn* to DSn* negated                | 50                      | 72                      |                                                                                                                    |

| t21        | DSn* to WRITE* negated               | 45                      | 65                      | Ensures 10ns hold time                                                                                             |

| t22        | DSn*/DTACK* to LDTACK*<br>negated    | 45                      | 65                      | Earliest negation of DSn* or DTACK* cause LDTACK* to be negated.                                                   |

| t23        | BGIN to BGOUT* asserted              | 90                      | 130                     | VME 1220 only                                                                                                      |

|            |                                      | 25+d,35+d,45+d          | 55+d,65+d               | VME 1210 only                                                                                                      |

| t24        | BGIN to BGOUT* negated               | 45                      | 65                      |                                                                                                                    |

| 125        | Latest of LAS*/DWB* to AS* asserted  | 135                     | 195                     | Assertion time when already have bus (BBSY* asserted).                                                             |

| t26        | Latest of DHBD*/LDS* to DS* asserted | 45                      | 65                      | Assertion time when already have bus (BBSY* asserted)                                                              |

### Note:

<sup>1.</sup> BBSY\* is guaranteed to be asserted for a minimum of 90 ns in the VME 1210A devices and the C-45 device of the VME 1220A, even if BGIN is negated immediately after BBSY\* is asserted. For the C-35 and C-25 VME 1220A devices, the sum of the system arbiter "BBSY\* asserted to BGIN\* negated" time and the t12 minimum time on the VME 1220A must be greater than 90 ns. Generally, this time will be taken up completely by the system arbiter time, however, if not, a delay line can be connected between pins 8 and 16 (DIP) or pins 10 and 19 (LCC) on the VME 1220A device to guarantee the 90 ns minumum. For example, if the system arbiter "BBSY\* asserted to BGIN\* negated" time was 35ns (min), no delay line would be needed for the C-35 VME 1220A device, since 35 + 75 > 90. However, a 10 ns delay line would be required for the C-25 VME 1220A.

## Absolute Maximum Ratings \_\_\_\_\_

# Storage Temperature -65°C to +150°C Ambient Temperature with Power Applied -55°C to +125°C Supply Voltage to Ground (pin 24 to pins 12, 18, & 20 DIP) -0.5V to +7.0V DC Voltage to Outputs in High Z State -0.5V to +7.0V UV Exposure -7000 Wsec/cm² DC Programming Voltage -14.0V

## Operating Ranges\_

|            | Ambient<br>Temperature | Supply Voltage<br>(Vcc) |

|------------|------------------------|-------------------------|

| Commercial | 0°C to +70°C           | 5V ± 5%                 |

| Industrial | -40°C to +85°C         | 5V ± 10%                |

| Military   | -55°C to +125°C        | 5V ± 10%                |

# Electrical Characteristics Tested over Operating Range\_

| Parameter       | Description                  | Test Conditions                                                            |                                                                        |                  | Min | Max        | Units  |

|-----------------|------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|------------------|-----|------------|--------|

| V <sub>OH</sub> | Output HIGH Voltage          | $V_{\infty}$ =Min,<br>$V_{IN}$ = $V_{IH}$ or $V_{IL}$                      | I <sub>OH</sub> = -3.0mA                                               |                  | 2.4 |            | V      |

|                 |                              |                                                                            | Pins (1210A/1220A),<br>16,17,<br>19,21 (DIP)<br>I <sub>OL</sub> = 24mA | (COM'L)<br>(MIL) |     | 0.5<br>0.6 | V<br>V |

| V <sub>OL</sub> | Output LOW Voltage           | $V_{\infty}$ =Min,<br>$V_{\text{IN}}$ = $V_{\text{IH}}$ or $V_{\text{IL}}$ | Pins (1210A/1220A)<br>13,15<br>22,23 (DIP)<br>I <sub>OL</sub> = 48mA   | (COM'L)<br>(MIL) |     | 0.5<br>0.6 | V      |

|                 |                              |                                                                            | Pins (1210B/1220B),<br>16,17,<br>19,21 (DIP)<br>I <sub>OL</sub> = 48mA | (COM'L)<br>(MIL) |     | 0.5<br>0.6 | V      |

|                 |                              |                                                                            | Pins (1210B/1220B)<br>13,15<br>22,23 (DIP)<br>I <sub>OL</sub> = 64mA   | (COM'L)<br>(MIL) |     | 0.5<br>0.6 | V<br>V |

| V <sub>IH</sub> | Input HIGH Level             |                                                                            |                                                                        |                  | 2.0 |            | ٧      |

| V <sub>IL</sub> | Input LOW Level              |                                                                            |                                                                        |                  |     | 0.8        | ٧      |

| l <sub>ix</sub> | Input Leakage Current        | V <sub>SS</sub> <= V <sub>IN</sub> <= V <sub>CC</sub> ,                    | V <sub>cc</sub> = Max                                                  |                  | -10 | 10         | μА     |

| l <sub>oz</sub> | Output Leakage Current       | V <sub>cc</sub> = Max, V <sub>ss</sub> <=                                  | · V <sub>OU</sub> T <= V <sub>CC</sub>                                 |                  | -40 | 40         | μА     |

| I <sub>sc</sub> | Output Short Circuit Current | V <sub>cc</sub> = Max, V <sub>out</sub> = 0.5V                             |                                                                        |                  | -30 | -90        | mA     |

| I <sub>cc</sub> | Power Supply Current         | V <sub>CC</sub> = Max, V <sub>IN</sub> = 0                                 | GND Outputs Open (CO                                                   | M'L)             |     | 80         | mA     |

|                 |                              | V <sub>CC</sub> = Max, V <sub>IN</sub> = 0                                 | GND Outputs Open (MIL                                                  | _)               |     | 90         | mA     |

## Capacitance (sample tested only)\_\_\_

| Parameter        | Test Conditions                    | Pins<br>(DIP)         | Тур | Units |

|------------------|------------------------------------|-----------------------|-----|-------|

|                  |                                    | 2-11,14               | 5   | pF    |

| C <sub>IN</sub>  | $V_{IN} = 2.0V @ f = 1 MHz$        | 13,15-17,<br>19,21-23 | 10  | pF    |

| C <sub>out</sub> | V <sub>IN</sub> = 2.0V @ f = 1 MHz | 13,15-17,<br>19,21-23 | 10  | pF    |

## Hysteresis.

| Parameter        | Description                                     | Тур | Units |  |

|------------------|-------------------------------------------------|-----|-------|--|

| V <sub>T+</sub>  | Positive-going threshold                        | 1.5 | V     |  |

| V <sub>T</sub> . | Negative-going threshold                        | 1.3 | V     |  |

| $\Delta V_{T}$   | Hysteresis (V <sub>T+</sub> - V <sub>T-</sub> ) | 0.2 | V     |  |

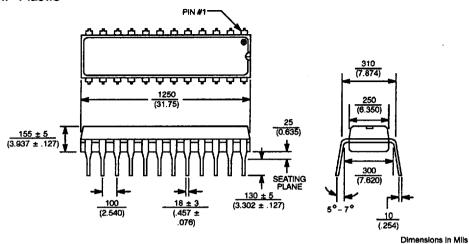

# Packaging Information...

The devices are available in a 24 pin slimline DIP (300 mil wide) or 28 pin LCC.

See PLX 448 or PLX 464 data sheets for package dimensions.

Contact PLX for further packaging information.

PLX reserves the right to make changes in its product without notice. For further information on specifications, contact PLX directly.

# T-46-19-09 PLX 464

# 24-Lead Ceramic Dual In-line Package (CERDIP)

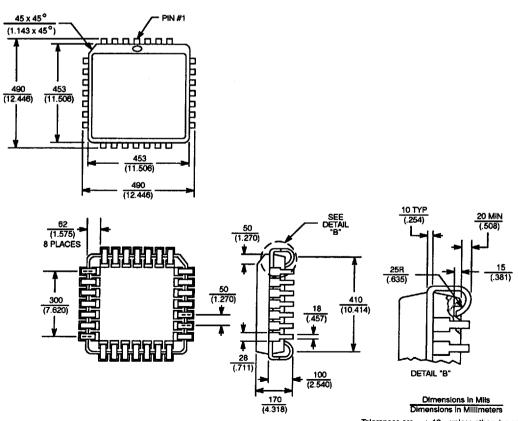

# 28-Pin J Lead Ceramic Chip Carrier

T-46-19-09 -

#### 24-Pin DIP Plastic

Dimensions in Millimeters

Tolerances are  $\pm 10$  unless otherwise specified  $(\pm 0.254)$

#### 28-Pin LCC Plastic

Tolerances are  $\pm 10$  unless otherwise specified  $(\pm 0.254)$