# **Signetics**

# SCN2653/SCN68653 Polynomial Generator Checker (PGC)

**Product Specification**

### **Microprocessor Products**

### DESCRIPTION

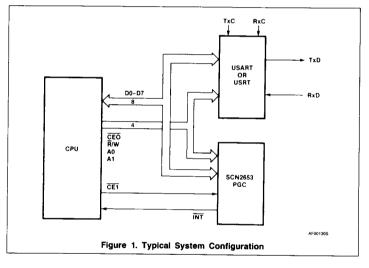

The Signetics SCN2653/68653 Polynomial Generator Checker (PGC) is a polynomial generator checker/character comparator circuit that complements a receiver/transmitter (R/T or USART/USRT/UART) in the support of character oriented data link controls. Table 1 defines many of the more commonly used PGC terms and abbreviations.

Parallel data characters transferred between the CPU and R/T are monitored by the PGC which performs block check character (BCC) and parity (VRC) generation/checking, single character detection, and two character sequence detection. Since the PGC operates on parallel characters, the data transmission format may be serial (synchronous or asynchronous) or parallel.

There are four modes of BCC accumulation and each mode can select one of three polynomials to compute the BCC. In the BISYNC normal and transparent modes, the PGC determines which characters are to be accumulated and which characters are to be excluded from the accumulation. The block terminating characters and the initiation and termination of BISYNC transparent text can be detected and an interrupt generated. The single interrupt output represents the inclusive OR of four maskable status conditions.

In the automatic accumulation mode, all characters are accumulated while the single accumulate mode requires a specific accumulation command for each character to be accumulated.

Character accumulation control and character comparisons are facilitated by a character class array which places each of 128 characters into one of four character classes. The four classes are normal, SYN/BISYNC not included, block terminating character (BTC)/search character (SC), and secondary search character (SSC).

### **FEATURES**

- Parallel Block Check Character accumulation/checking: CRC-16, CRC-12. LRC-8

- BISYNC normal and transparent modes

- Automatic or single character accumulation modes

- Character detection up to 128 characters

- Two character sequence detection; examples: DLE-STX, ACKO, ACK1, WACK, RVI, DISC, WBT

- 6, 7, or 8-bit characters

- VRC generation/checking on data bus

- Four maskable interrupt conditions

- Four classes of characters

- Internal power-on reset

- Maximum character accumulation rate of 500kHz (4Mbps)

- Directly compatible with Signetics SCN2651, SCN2652 and SCN2661

- No system clock required

- TTL compatible inputs and outputs

- Single 5V supply

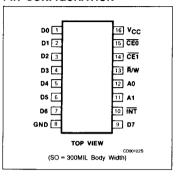

- 16-pin dual in line package

### **APPLICATIONS**

- Character oriented data link control:

- dedicated to one USART/USRT

- multiplexed among several USART/USRTs

- Automated BISYNC with 2661 (minimal software intervention)

- BCC and VRC generation/ detection on a block of memory or peripheral data

- Programmable character array comparator

### PIN CONFIGURATION

# SCN2653/SCN68653

### ORDERING INFORMATION

| PACKAGES           | $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to +70°C |

|--------------------|-----------------------------------------------------|

| Ceramic DIP        | SCN2653AC4l16                                       |

| Plastic DIP        | SCN2653AC4N16                                       |

| Small Outline (SO) | SCN2653ACD16                                        |

### NOTE

SCN68653 is identical to SCN2653. Order using numbers shown above.

### **BLOCK DIAGRAM**

### PIN DESCRIPTION

| MNEMONIC               | PIN NO. | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub><br>GND | 16<br>8 |      | +5V: Power supply Ground                                                                                                                                                                                                                                                                                                                                                                             |

| A1-A0                  | 11,12   | 1    | Address Lines: Used to select internal PGC registers or character class array.                                                                                                                                                                                                                                                                                                                       |

| R/W                    | 13      | 1    | Read/Write: Read command when low, write command when high.                                                                                                                                                                                                                                                                                                                                          |

| CE0                    | 15      | 1    | Chip Enable: Connected to chip enable input of a receiver/transmitter (R/T) circuit. It is used to strobe data being transferred between the CPU and the R/T into the PGC character register.                                                                                                                                                                                                        |

| CE1                    | 14      | 1    | Chip Enable: Used in conjunction with the $\overline{R}/W$ signal to enable the transfer of data between the PGC and the CPU or DMA controller and to initialize the PGC registers.                                                                                                                                                                                                                  |

| D7-D0                  | 9,7-1   | 1/0  | Data Bus: 8-bit 3-State bidirectional bus used to transfer data to or from the PGC via CE0 or CE1. All data, mode words, command words, and status information are transferred on this bus. D0 is the least significant bit; D7 is the most significant bit.                                                                                                                                         |

| ĪNT                    | 10      | 0    | Interrupt: Open drain active low interrupt output that signals the CPU that one or more maskable conditions are true: BCC error, VRC error, BTC/SC detect, SSC detect. The true conditions can be determined by reading the status register which in turn deactivates $\overline{\text{INT}}$ . A power on, clear BCC, or master reset command causes $\overline{\text{INT}}$ to be inactive (high). |

# SCN2653/SCN68653

Additional PGC applications include off-line R/T operation where the BCC is generated on data not sent to the R/T, BCC multiplexing by sharing the PGC among several R/Ts and reading/writing the partial BCC accumulation on a character by character basis, VRC generation/checking on characters appearing on a bidirectional data bus, and programmable character comparisons or searches.

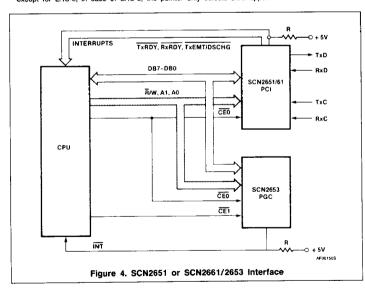

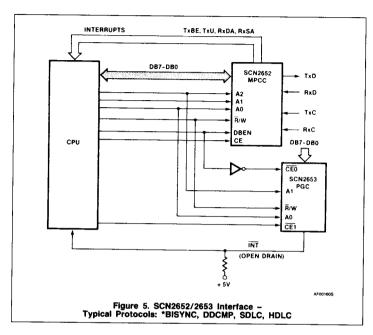

PGC operation is half duplex (either receive or transmit, one way or two way alternate). Full duplex (two way simultaneous) is achieved by using two PGCs. The device is directly compatible with the Signetics SCN2651 Programmable Communications interface (PCI) and SCN2661 Enhanced Programmable Communications interface (EPCI). When used in BISYNC modes with the SCN2661, software requirements are minimized by the SCN2653-SCN2661 control character comparisons, character sequence comparisons, and automatic DLE insertion/detection

Other bus oriented R/Ts can be interfaced to the PGC with a minimum of external circuitry. See Figure 1 for a typical system configuration.

This NMOS LSI circuit is TTL compatible, operates from a single + 5V supply and is contained in a 16 pin dual in line package.

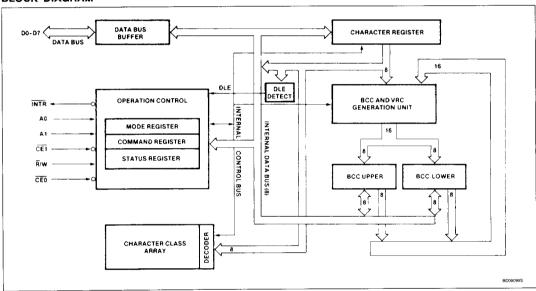

### **BLOCK DIAGRAM**

The PGC consists of the following six major sections: the operation control, character class array, DLE ROM, character register, BCC and parity generators, and BCC registers. These sections communicate with each other via an internal data bus and an internal control bus. The internal data bus interfaces to the CPU data bus via a data bus buffer.

### Operation Control Unit

This functional block stores configuration and operation instructions from the CPU and generates appropriate signals to control the device operation. It also contains read and write circuits to permit communications between the CPU and the PGC registers via the data bus. The mode, command, and status registers are in this logic block.

### Character Register

Characters to be considered for BCC generation, parity generation and checking, or character comparisons are loaded into this register by either ĈEŌ or ĈET. This register serves as an input to the BCC and VRC generator, where the accumulation and parity generation takes place. The character register also serves as the input for character class array and DLE comparisons.

Table 1. Glossary

| TERM/ABBREVIATION | DEFINITION                                                |

|-------------------|-----------------------------------------------------------|

| BCC               | Block check character                                     |

| BTC               | Block terminating character                               |

| SC                | Search character                                          |

| SSC               | Second search character (preceded by DLE)                 |

| CRC-16            | $X^{16} + X^{15} + X^2 + 1$ divisor, dividend pre-cleared |

| CRC-12            | $X^{12} + X^{11} + X^3 + X^2 + X + 1$ divisor, dividend   |

|                   | pre-cleared                                               |

| LRC-8             | Horizontal parity on least significant 7 bits;            |

|                   | vertical parity on most significant bit                   |

| VRC               | Vertical redundancy check (character parity)              |

| R/T               | Receiver/transmitter circuit. Also known as               |

|                   | USART/USRT/UART/PCI/MPCC                                  |

| BISYNC            | IBM binary synchronous communications (BSC),              |

|                   | ANSI X3.28, ISO 1745                                      |

| MSB               | Most significant bit                                      |

| LSB               | Least significant bit                                     |

| Rx                | Receive                                                   |

| Tx                | Transmit                                                  |

### Character Class Array

This 128  $\times$  2 array holds the character class associated with each of 128 possible 7-bit characters. The array is zero after a master reset. When the character class array is loaded (see PGC Addressing), the character on the data bus is placed in the class specified by the contents of command register bits CR2 and CR3. The PGC uses these two command bits to represent four different character classes. These are:

- Normal class (included in the accumulation)

- SYN character/BISYNC not included class

- 3. Block terminating character/search class

Second search character class (preceded by DLE)

These encoded character classes are used by the PGC:

- To control the BCC accumulation of associated characters in BISYNC modes only. BCC accumulation in automatic or single accumulation modes is carried out independent of the character classes.

- To detect characters and two character sequences in all modes of accumulation and to set the control character detect bits in the status register.

It should be noted that any number of characters (up to 128 for CRC-16 or LRC-8; up to 64 for CRC-12) can be put into any one class.

# SCN2653/SCN68653

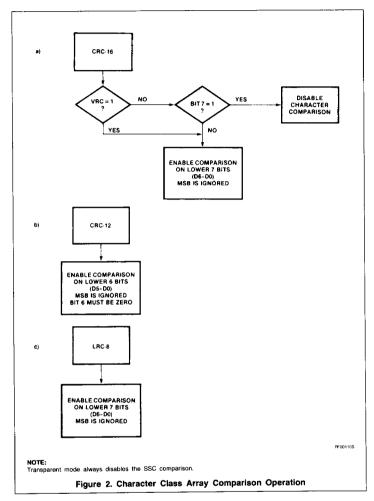

If VRC is specified along with CRC-16 then the least significant 7 bits of the character are used for character array comparison. If VRC is not enabled, but CRC-16 is, the MSB of the character then determines whether a character comparison is to take place. If the MSB is 0, the comparison takes place; if the MSB is 1, the comparison does not take place and the character is processed as though it were in the normal class. This enables the PGC to detect all communication control characters and DLE-SSC sequences.

Only the first 64 locations of the array are accessed if CRC-12 is selected. The user should right justify each six bit character (D0-

D5) to be written into the character class array. Bit 6 must be zero.

If VRC is enabled, the generated parity becomes the most significant bit of the character to be compared. VRC is not allowed in BISYNC transparent mode.

The method in which the character register contents is compared against the character class array depends on the BCC polynomial chosen. Figure 2 illustrates the comparison process.

### **DLE Read Only Memory**

The DLE characters are stored internally and are selected by the error polynomial as follows:

CRC-12: 01 1111

LCR-8 or CRC-16:

No VRC or odd VRC: 0001 0000 Even VRC: 1001 0000

### **BCC and Parity Generator**

This functional block performs all the necessary computation to generate and update the BCC accumulation on a character by character busis. It contains the three generator polynomials (CRC-16, CRC-12, and LRC-8) that can be selected to compute the BCC. This block also checks and generates odd or even parity for 7-bit (ASCII) characters.

### **BCC Registers**

This block consists of two 8-bit registers (BCC upper and BCC lower) which contain the high and low order bytes of the BCC accumulation. The result of the accumulation from the BCC and parity generator is stored in these registers. A recirculating register address pointer is initialized by a power on, master reset, or clear BCC command. The pointer alternately selects BCC upper and lower on successive BCC register accesses for CRC-16 or CRC-12. For LRC-8, BCC upper is always selected.

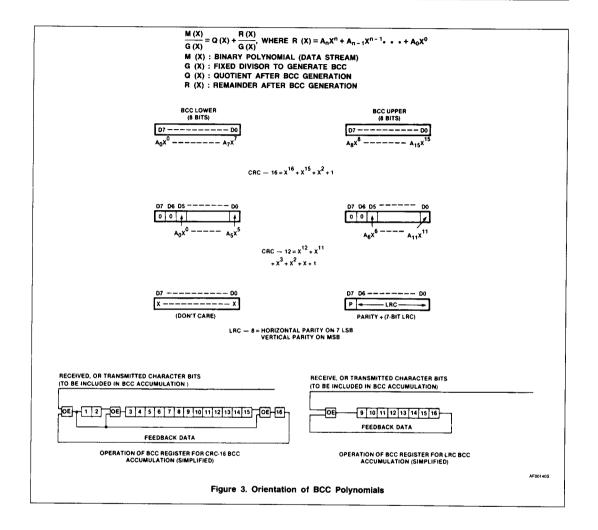

BCC upper and lower are cleared by a clear BCC or master reset command. The highest term of the BCC polynomial is always represented by bit 0 of BCC upper; the lowest term is always represented by bit 7 of BCC lower (see Figure 3, Orientation of BCC Polynomials.)

The length of the block check character depends on the error checking polynomial that is selected. If LRC-8 is chosen, the BCC result is stored entirely in BCC upper. The BCC lower remains unchanged from previous setting. Both BCC registers are used when CRC-16 is specified. When CRC-12 is selected, the block check character is 12 bits long. The six least significant bits of the BCC are stored in the least significant bits of the BCC lower. The remaining upper six bits of the BCC are stored in least significant bits of BCC upper. The two most significant bits in each BCC register are filled with zero.

The BCC register(s) are read by the CPU after the last data character is transmitted. They can then be sent to the R/T to complete a transmitted block of data. These registers are read and loaded when one PGC is time-shared by several R/Ts. Refer to Applications Information—Multiplexed PGC.

### PGC Addressing

All internal registers and the character class array are selected by the unique address codes shown in Table 2.

# SCN2653/SCN68653

# SCN2653/SCN68653

Table 2. Address Codes

| ſ | CE0 | CE1 | <b>A</b> 1 | A0 | R/W | FUNCTION                                                  |

|---|-----|-----|------------|----|-----|-----------------------------------------------------------|

| Ī | 0   | 0   | Х          | Х  | Х   | Operation not guaranteed                                  |

| 1 | 0   | 1   | 0          | 0  | 0   | If MR2 = 0 load data bus into character register          |

| - |     |     |            |    |     | if MR2 = 1 PGC not selected <sup>1</sup>                  |

|   | 0   | 1   | 0          | 0  | 1   | If MR2 = 1 load data bus into character register          |

|   |     |     |            |    |     | If MR2 = 0 PGC not selected <sup>1</sup>                  |

|   | 0   | 1   | 0          | 1  | X   | PGC not selected <sup>1</sup>                             |

|   | 0   | 1   | 1          | 0  | X   | PGC not selected <sup>1</sup>                             |

| ļ | 0   | 1   | 1          | 1  | X   | PGC not selected <sup>1</sup>                             |

| Ì | 1   | 0   | 0          | 0  | 0   | Read character register                                   |

|   | 1   | 0   | 0          | 0  | 1   | Load data bus into character register if MR1,0            |

|   |     |     |            |    |     | ≠00 <sup>2</sup> ; write character class array using CR3, |

|   |     |     |            |    |     | CR2 class code if MR 1,0 = 003, 4                         |

| - | 1   | 0   | 0          | 1  | 0   | Read Status register                                      |

| 1 | 1   | 0   | 0          | 1  | 1   | Write command register                                    |

| 1 | 1   | 0   | 1          | 0  | 0   | Read mode register                                        |

|   | 1   | 0   | 1          | 0  | 1   | Write mode register                                       |

|   | 1   | 0   | 1          | 1  | 0   | Read BCC upper/lower <sup>5</sup>                         |

|   | 1   | 0   | 1          | 1  | 1   | Write BCC upper/lower <sup>5</sup>                        |

| - | 1   | 1   | X          | X  | X   | PGC not selected <sup>1</sup>                             |

### NOTES:

- 1. Data bus is 3-State.

- 2. Character will not be accumulated unless MR3 = 1.

- 3. Character will not be accumulated even if MR3 = 1.

- The mode bits MR1 and MR0 are cleared to 00 by power-on-reset, master reset, or by loading the mode register bits MR1 and MR0.

- Recirculating internal pointer selects BCC upper on first access, BCC lower on next access for all BCCs except for LRC-8; in case of LRC-8, the pointer only selects BCC upper.

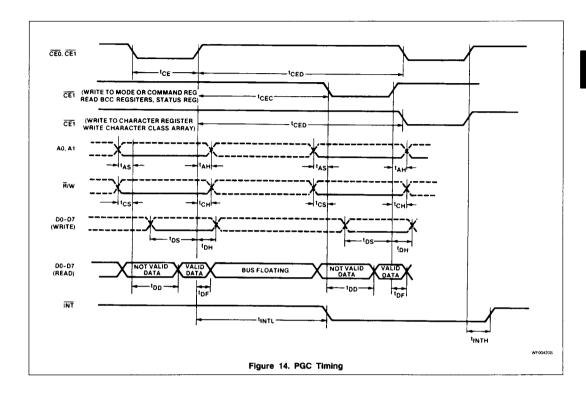

# INTERFACE SIGNALS AND TIMING

PGC data transfers are controlled by A1, A0, and R/W which must be stable prior to the active low going chip enable pulse.  $\overline{\text{CEO}}$  is used for PGC monitoring of data transfers between a CPU/DMA controller and a R/T;  $\overline{\text{CET}}$  is used for direct CPU-to-PGC transfers. MR3 must be set prior to loading the character register in order to accumulate or compare characters via  $\overline{\text{CET}}$ . The active low (leading) edge of chip enable initiates a PGC read/write cycle; the rising (trailing) edge ends the cycle and also serves as a write strobe.

When loading the character, mode, or command register, the data bus is strobed into the selected register on the trailing (rising) edge of the appropriate  $\overline{\text{CE}}$ . When writing into the character class array, the data on the bus (the special character) is placed in the class specified by command register bits CR3 and CR2

Characters are transferred into the character register when  $\overline{CE0}$  is active (low) depending on the state of MR2 and the  $\overline{R}/W$  input. Characters (from the R/T are loaded into the character register when in receive mode (MR2 = 0 and  $\overline{R}/W = 0$ ) while CPU/DMA characters are loaded into the character register when in transmit mode (MR2 = 1 and  $\overline{R}/W = 1$ ). The time between consecutive chip enables is given by  $t_{CEC}$  or  $t_{CED}$ .

The open drain active low interrupt signal  $(\overline{\text{INT}})$  goes active whenever one or more of four maskable status conditions (SR0-SR3) are true ( = 1). A status read deactivates  $\overline{\text{INT}}$ .

The same techniques used in interfacing the SCN2651 PCI to 8-bit microprocessors can be used to interface the SCN2653 PGC (consult Application Note M22). Note that when addressing the R/T's holding registers, the PGC pins must have A1, A0 = 00 and that the address and  $\overline{R}/W$  signals must be stable (set up) prior to the active low chip enable. When using the SCN2651 or SCN2661 as the R/T, the PGC's A1, A0,  $\overline{R}/W$ , and  $\overline{CEO}$  are directly connected to comparable SCN2651 or SCN2661 signals. Schematics of an SCN2653 monitoring data transfers to/from the Signetics SCN2651/2661 and SCN2652 are shown in Figures 4 and 5.

An alternate interfacing technique is to treat the PGC as an independent peripheral device. This necessitates a write character register instruction after the CPU reads or writes a character to or from the R/T.

11 1

# SCN2653/SCN68653

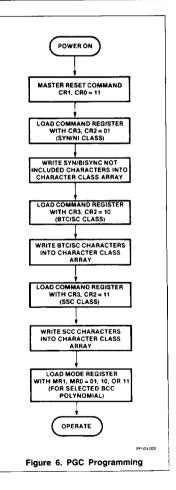

### **PGC PROGRAMMING**

The PGC operational mode must be initially programmed by the CPU (see Figure 6). The mode register, command register and character class array should be written into, after a power-on-reset or a master reset command. The character class array should be programmed only for the classes pertinent to the application. After a master reset, the character class array is zero which places all characters in the normal class (included in the BCC accumulation).

### **OPERATION**

The PGC should be initially configured by the CPU (via  $\overline{CE1}$ ) prior to systems operation. This is done by loading the mode register.

command register and character class array (see PGC PROGRAMMING). Characters may then be loaded into the character register for BCC accumulation, VRC generation/checking, BTC/SC and DLE-SSC comparisons. See Table 3 for a summary of BCC accumulation modes.

BCC accumulation depends on the mode selected.

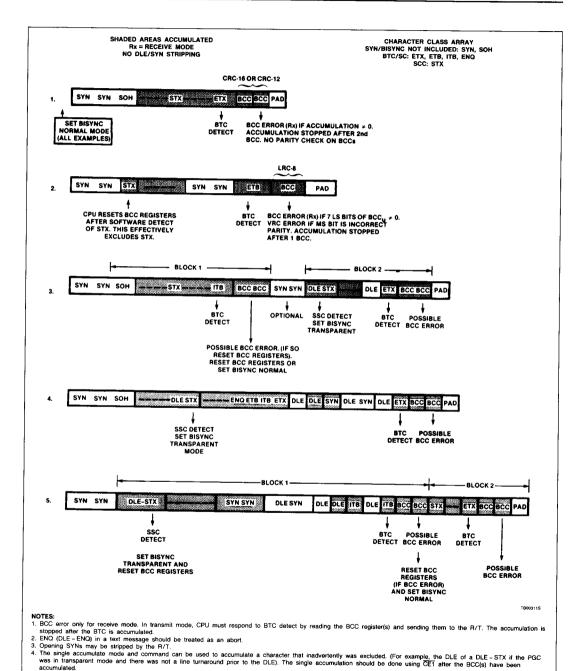

### **BISYNC Normal**

in BISYNC normal mode, all characters loaded into the character register are accumulated except those in the SYN/BISYNC not included class. During receive (MR2 = 0), a BTC/SC match will cause the BCC accumulation to stop after the next one (LRC-8) or two (CRC-12 or CRC-16) characters have been accumulated. At that time, if the BCC accu-

mulation does not equal zero, the BCC error bit (SR0) will be set and int will go active if the corresponding mask bit (CR4) is enabled (= 1). In transmit (MR2 = 1), the BCC accumulation is automatically stopped once the BTC/SC character has been accumulated. The CPU must read the BCC upper and BCC lower (CRC-12 or CRC-16) register(s) and transmit them to the R/T.

Note that the received BCCs are not subject to VRC if CRC-16 is selected. If LRC-8 is selected, the received BCC is subject to VRC. An incorrect result will set the VRC error bit (SR1). After its accumulation, the least significant 7 bits of BCC upper are checked and a non-zero result will set the BCC error bit (SR0). BCCs are not checked against the character class array nor are they compared to the DLE ROM.

Second search character (SSC) detection is enabled so that a DLE-STX or two character communication control sequence can be detected.

### **BISYNC Transparent**

BISYNC transparent mode should be used for data blocks beginning with DLE-STX if the DLEs are transferred between CPU and R/T (CEO) or CPU and PGC (CET), i.e., DLEs are not stripped. VRC should be disabled in this mode. Characters excluded from the BCC accumulation are the first DLE of a DLE-non SYN sequence pair and the DLE-SYN sequence if not preceded by an odd number of DLEs. For example, consider the following transparent mode character string:

| DLE          | DLE SYN      | DLE     | DLE     |

|--------------|--------------|---------|---------|

| ↑<br>exclude | ↑<br>include | 1       | 1       |

| exclude      | both         | exclude | include |

| DLI          | ESYN         | DLE     | ETX     |

|              | <b>1</b>     | 1       | 1       |

|              | clude<br>oth | exclude | include |

# SCN2653/SCN68653

Table 3. Summary of BCC Accumulation Modes

| ACCUMULATION MODES                      | START<br>ACCUMULATION                                                                                                                       | STOP<br>ACCUMULATION                                                                                                                          | CHARACTERS EXCLUDED FROM ACCUMULATION                                                                                                                                                                   |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BISYNC normal and<br>BISYNC transparent | Clear BCC registers command<br>Mode register is loaded with<br>BISYNC or automatic mode<br>Start accumulation command<br>Load BCC registers | After BTC has been detected<br>and received BCC is<br>accumulated<br>After transmitted BTC has<br>been accumulated<br>Single mode is selected | SYN/BISYNC not included class in normal mode DLE-SYN/not included class and first DLE of a DLE non SYN pair in transparent mode. These characters are not excluded if preceded by an odd number of DLEs |

| Automatic                               | Same as above                                                                                                                               | Single mode selected                                                                                                                          | None                                                                                                                                                                                                    |

| Single                                  | Start accumulation command                                                                                                                  | After each character has been accumulated                                                                                                     | Up to user who must generate start accumulation command for each character to be included                                                                                                               |

In receive and transmit modes, the termination of BCC accumulation works exactly as in BISYNC normal, except that the BTC/SC must be immediately preceded by an odd number of DLEs to be identified as a BTC/ SC.

Second search character detection is not enabled in BISYNC transparent.

After a BTC/SC class character is detected by the PGC when receiving in either BISYNC mode, the following one or two characters are accumulated (depending on LRC-8 or CRC-12/16, respectively) and the PGC will automatically stop further accumulation. However, the PGC can continue the accumulation if a start accumulate command is issued or either BISYNC mode is loaded into the mode register. The start accumulate command should be given to the PGC before loading the character that follows the detected BTC/SC. This procedure enables a special search character to be detected (the BTC/SC detect bit (SR2) will be set and an interrupt generated if CR6 = 1) with the BCC accumulation continuing (see Figures 7 and 8).

### **Automatic Accumulate**

All characters loaded into the character register are accumulated, BTC/SC and SSC detection is enabled. The BCC accumulation is not automatically terminated. (The CPU must use single accumulate mode to stop the accumulation). When in receive mode, the BCC error bit (SR0) is set/reset after accumulating each character so that the CPU must examine this bit after the last character is accumulated. SR0 = 0 if the accumulated remainder in the BCC register(s) is zero; otherwise SR0 = 1. Examples of use of automatic accumulate mode usage include an R/T (SCN2651/SCN2661) in transparent DLE/SYN strip mode and asynchronous/ synchronous/parallel DDCMP.

### Single Accumulate

All characters for which a start accumulate command (CR1, CR0 = 01) is given are accumulated and compared against the character class array. If not given, the BCC accumulation is not updated and BTC/SC and SCC detection is disabled. Operation in this mode is otherwise identical to automatic accumulate.

Single accumulate mode can be used to selectively accumulate characters under CPU control or to accumulate characters that were unintentionally excluded in one of the other modes.

# Polynomial Selection and DLE Comparison

The BCC polynomial may be CRC-16, CRC-12 or LRC-8. The cyclic redundancy check (CRC) is generated by dividing the binary value of a character in the character register by the selected polynomial. The quotient is discarded and the remainder is used as the BCC (two 6-bit characters for CRC-12, two 8-bit characters for CRC-16). CRC-16 uses all 8 bits of each BCC register. CRC-12 uses the least significant 6 bits of the BCC registers. The two most significant bits of the BCC registers are cleared to zero whenever CRC-12 is selected (see Figure 3).

When the PGC is in receive mode (MR2 = 0), the received BCC will be accumulated. The result will be zero for an error free message.

TT TT

# SCN2653/SCN68653

Figure 7. Examples - Bisync Text Message BCC Accumulation

## SCN2653/SCN68653

- 1. BCC accumulation should be ignored for control messages. This can be effected by single accumulate mode without single accumulate commands

- 2. Characters programmed as SSCs should be the binary equivalent of the second character of the DLE-SSC sequence.

Figure 8. Examples - Bisync Control Messages

CRC-12 is used with 6-bit codes. The internal 6-bit transcode DLE character hex 1F is selected by CRC-12. VRC should be disabled (MR4 = 0) for CRC-12 operation. The two most significant bits of the character register are ignored when compared to the internal 6bit DLE. When the character is checked against the character class array, the MSB is ignored and the next MSB (bit 6) is assumed to be zero. If CRC-12 is specified, the user must write to the character class array with bit 6 cleared.

CRC-16 or LRC-8 implies the use of ASCII or EBCDIC although any 7-bit plus parity or 8-bit no parity code may be used (with DLE = hex 10 or hex 90). The DLE character compare is on an 8-bit basis with the generated parity (if VRC is enabled) as the MSB. When the character is compared against the character class array, the MSB is not used. This may result in a false BTC or SSC detection if there is a VRC error. However, the VRC error bit (SR1) will be set under that condition.

The LRC-8 is generated by the exclusive OR of the 7 least significant bits of the character register and the BCC upper. The most significant bit of the LRC-8 check character is a vertical odd/even parity bit (MR5 = 0/1), which is generated on the least significant bits of that character. The selection of LRC-8 implies VRC is enabled and that only the BCC upper is used for the BCC accumulation. The BCC lower remains unchanged from previous settina.

### **VRC Generation and Detection**

Parity (VRC) is enabled by MR4 and specified as odd or even by MR5. VRC should be disabled when in BISYNC transparent mode and whenever CRC-12 or CRC-16 (EBCDIC) is selected as the BCC polynomial. MR4 = 1 enables VRC generation and detection for both receive and transmit operations. Characters loaded into the character register will have VRC generated on the least significant 7 bits with the generated parity bit written into the character register MSB. If the generated parity does not match the MSB of the loaded character, the VRC error bit (SR1) is set and INT asserted if the corresponding mask bit was enabled (CR5 = 1). Thus, if 7-bit characters are to be transmitted with VRC, CR5 should be zero and SR1 ignored. 8-bit characters with a VRC bit in the MSB position are parity checked by the PGC in both transmit (to R/T) and receive (from R/T) modes, i.e., the PGC operates as a data bus parity checker.

### CHARACTER CLASSES

### Normal (Included in the Accumulation)

Any character that belongs to this class is normal data, i.e., the character is not a communication control or other special character. Characters in this class are always accumulated in BISYNC, automatic and single accumulation modes.

### SYN Character/BISYNC Not Included

SYN characters are never accumulated in BISYNC normal accumulation mode. In BI-SYNC transparent accumulation mode. the DLE-SYN character pair is not accumulated, but a SYN not preceded by a DLE is accumulated. (DLE is implied as an odd number of

### **Block Termination Character** (BTC)/Search Character (SC)

BTC/SC characters have two functions in the PGC: termination of BCC accumulation and character detection. In BISYNC transparent mode, a BTC/SC must be preceded by an odd number of DLEs to be recognized.

### Termination of BCC Accumulation

In BISYNC normal and transparent accumulation modes, the PGC will stop the accumulation upon the detection of the BTC/SC character. Examples of BTCs are ETX, ETB, ITB, FNO

In receive mode, the accumulation is stopped after the following one (LRC-8) or two (CRC-12, CRC-16) character(s) have been accumulated. In transmit mode, the accumulation is stopped after the BTC/SC character has been accumulated. The BTC/SC character is always accumulated in all of the accumulation modes.

### Character Detection

BTC/SC characters will be detected in any of the four accumulation modes when that character is being accumulated. The BTC/SC status bit (SR2) is set on detection. Since detection also stops BISYNC BCC accumulation, the BISYNC accumulation must be restarted if the character is not a BTC. This can be effected by loading BISYNC mode into the mode register or generating a start accumulation command.

December 12, 1986

11 1

# SCN2653/SCN68653

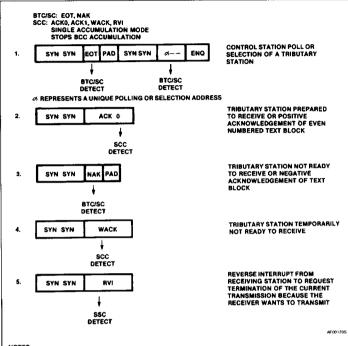

# Second Search Character Class (SSC)

Control functions in character oriented data link control procedures can be represented by a sequence of two characters, the first character being a DLE. Examples include ACKO, ACK1, WACK, RVI, DISC, WBT and the initiation of transparent text (DLE-STX).

The PGC will detect such sequences, except in BISYNC transparent mode, when an SSC class character is being accumulated after being immediately preceded by an odd number of DLEs. Under those conditions, the SSC status bit (SR3) will be set.

The SSC character is always accumulated in all of the accumulation modes.

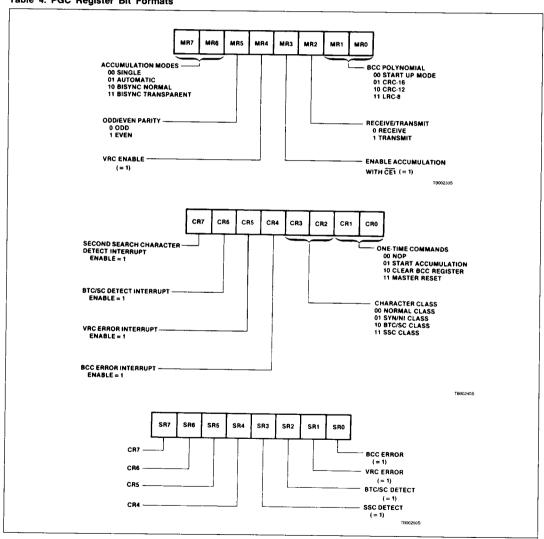

### REGISTER BIT DESCRIPTION

The operation of the PGC is determined by programming the mode register and the command register. The status register provides feedback on potential interrupt conditions. Formats of these registers are shown in Table 4.

Table 4. PGC Register Bit Formats

# SCN2653/SCN68653

Table 5. BCC Accumulation by Character Class

| CR3 | CR2 | CLASS                      | BISYNC<br>NORMAL | BISYNC<br>TRANSPARENT                            | AUTOMATIC<br>ACCUM | SINGLE<br>ACCUM |

|-----|-----|----------------------------|------------------|--------------------------------------------------|--------------------|-----------------|

| 0   | 0   | Normal                     | Yes              | Yes                                              | Yes                | Yes             |

| 0   | 1   | SYN/BISYNC<br>not included | No               | Yes, unless preceded by<br>an odd number of DLEs | Yes                | Yes             |

| 1   | 0   | BTC/SC                     | Yes              | Yes                                              | Yes                | Yes             |

| 1   | 1   | SSC*                       | Yes              | Yes                                              | Yes                | Yes             |

NOTE:

'Preceded by DLE

### **Mode Register**

The mode register defines general PGC operation characteristics. MR1 and MRO = 00 permit the character class array to be programmed. These bits will be zero after a power on or master reset command. After the character class array is programmed, these bits should be set to 01,10, or 11 to select the CRC-16, CRC-12 or LRC-8 polynomials.

MR2( $Tx/\overline{R}x$ ) determines whether or not the PGC is to generate (Tx) or generate and check (Rx) the BCC. It is used with  $\overline{R}/W$  to determine if the data bus is to be loaded into the character register when  $\overline{CE0}$ ,  $\overline{CE1}$ , A1, A0 = 0100

If MR2 = 1: 1) the PGC will generate the BCC but will never set the BCC error bit (SR0). 2) If the  $\overline{R}/W$  pin is high when  $\overline{CEO}$ ,  $\overline{CE1}$ , A1, A0 = 0100, then the data bus will be loaded into the character register. If  $\overline{R}/W$  is low under these conditions, the PGC is not selected.

If MR2 = 0: 1) the PGC will accumulate the BCC and set the BCC error bit (SR0) when appropriate. 2) If the  $\overline{R}/W$  pin is low when  $\overline{CE0}$ ,  $\overline{CE1}$ , A1, A0 = 0100, then the data bus will be loaded into the character register. If  $\overline{R}/W$  is high under these conditions, the PGC is not selected.

MR3 is a CE1 accumulate/compare enable bit. If MR3 = 0, characters loaded into the character register by CET are not accumulated, checked against the character class array, or compared to the DLE ROM. Parity will be generated and checked if VRC is enabled (MR4 = 1). The primary use of MR3 = 0 is to generate parity on a 7-bit character which is to be transmitted to an R/T. The CPU loads the character register with the 7-bit character and reads the 8-bit VRC generated character via CE1. This 8-bit character is then transferred to the R/T via CEO. Another application of MR3 = 0 is for a CPU to interleave parity checking on memory data (CE1) with on line R/T data transfer (CEO).

If MR3 = 1, characters loaded into the character register by  $\overline{\text{CE1}}$  will be accumulated (according to the BCC accumulation mode selected) and compared against the character class array and DLE ROM. This bit setting should be used when the CPU/DMA control-

Table 6. BTC/SC and SSC Detection Conditions

| CLASS  | BISYNC | BISYNC      | AUTO  | SINGLE |

|--------|--------|-------------|-------|--------|

|        | NORMAL | TRANSPARENT | ACCUM | ACCUM  |

| BTC/SC | Yes    | Yes*        | Yes   | Yes †  |

| SSC    | Yes    | No          | Yes   | Yes †  |

### NOTES

- \* Only if immediately preceded by an odd number of DLEs.

- + Start accumulate command necessary for detection.

ler sends data characters to be accumulated or compared to the PGC and the R/T is inactive (off line). If the R/T were active, then a DLE or BTC loaded into the character register via CEO would cause incorrect accumulation and character comparisons if the next character was loaded via CE1.

MR4 is a VRC enable bit. If MR4 = 1, VRC is enabled as odd/even by MR5. VRC is generated on the 7 LS bits of the character and the MS bit is checked against the generated parity. If not equal, SR1 is set. If MR4 = 0, VRC is not enabled. MR4 = 0 is used for BISYNC transparent mode with ASCII code, and for both BISYNC modes for EBCDIC and SRT

MR5 is an odd/even VRC bit. If MR5 = 1, the total number of 1 bits in the character including the parity bit is even. If MR5 = 0, the total number of bits is odd. This bit is ignored if MR4 = 0.

MR7, MR6 select the BCC accumulation mode. These modes have been previously discussed in the operation section.

### Command Register

The command register contains four interrupt enables, a 2-bit character class code used when programming the character class array, and 2 bits that specify three one time commands and a NOP.

CR1, CR0 = 00 is a NOP. This bit setting is used when changing CR7-CR2 without affecting any of the 3 one time commands.

CR1, CR0 = 01 is a start BCC accumulation command. In single accumulation mode, the character accumulated is the character that is in the character register at the time the command is given. The accumulation stops immediately after the character has been accumulated. If the command is given in

either of the BISYNC or automatic accumulation modes, it enables the PGC to accumulate the BCC starting with the next character loaded into the character register. This is a means of restarting a BISYNC normal accumulation after detection of a BTC/SC that is not a valid BTC (example; CR, LF, TAB). In all accumulation modes, a previously detected DLE will not be cancelled by this command.

CR1, CR0 = 10 is a clear BCC registers command. Both BCC registers are cleared along with the associated internal pointer and SR0-SR3. The pointer points to BCC upper. INT is forced high. This command permits BCC accumulation, starting with the next character loaded into the character register in BISYNC or auto modes. Single accumulate mode requires a start BCC accumulation command.

CR1, CR0 = 11 is a master reset command. All internal registers (except the character register), the internal pointer, and the entire character class array are cleared. INT is forced high.

CR3 and CR2 are used for programming the character class array. During a write character class array instruction, the character corresponding to the 7 LS bits of the data bus is placed in the class contained in CR3 and CR2. The encoded character classes control the accumulation of the associated character as shown in Table 5.

Detection operates under the conditions shown in Table 6.

CR7, CR6, CR5, CR4 are interrupt enables that individually enable/disable INT when the corresponding status register condition is true (set). Each bit is set in order to enable INT upon the condition. Each bit is reset to disable INT upon the condition. The state of

# SCN2653/SCN68653

these bits may be read via the status register (SR7, SR6, SR5, SR4).

The corresponding status bits (SR3, SR2, SR1, SR0) are set independent of the interrupt enables. The bit assignments are:

CR4-BCC error interrupt enable

CR5-VRC error interrupt enable

CR6-BTC/SC detect interrupt enable

CR7-DLE-SSC detect interrupt enable

### Status Register

This register reflects the status of the 4 conditions that are potential interrupt (INT) sources and the 4 interrupt enables in the command register. A status register read clears SR0, SR1, SR2, SR3 and deactivates INT. These bits are also cleared by a master reset or clear BCC command.

SR0 is a BCC error bit. This bit can only be set in receive mode (MR2 = 0). In BISYNC normal and BISYNC transparent modes, SR0 will be set/reset once the accumulation has been stopped by the detection of the BTC/SC character and accumulation of the BCC(s).

In automatic and single accumulate modes, SR0 is set/reset after each character in the character register has been accumulated.

The rules for the detection of a BCC error are: SR0 = 1 LRC-8: 7 least significant bits

of BCC upper ≠ 0 CRC-12, CRC-16: BCC upper or BCC lower ≠ 0

SR0 = 0 LRC-8: 7 least significant bits of BCC upper = 0 CRC-12, CRC-16: BCC upper and BCC lower = 0

SR1 is a VRC error bit. When set, this bit reports a character parity error (on receive or transmit) when parity is enabled (MR4 = 1). Parity is odd/even as specified by MR5. The parity bit will be regenerated in the character register.

SR2 is a BTC/SC detect bit. When set, this bit indicates the character being accumulated is of the BTC/SC class for BISYNC normal, automatic and single accumulate modes. In

BISYNC transparent mode, the BTC/SC character being accumulated must be immediately preceded by an odd number of DLEs for this bit to be set.

SR3 is a DLE SSC detect bit. This bit can only be set when in BISYNC normal, auto, or single accumulated modes. When set, it indicates that the character being accumulated is of the SSC class when that character was immediately preceded by an odd number of DLEs.

SR7, SR6, SR5, SR4 are interrupt enables. These 4 bits reflect the state of the interrupt enable command bits CR7, CR6, CR5, and CR4, as follows:

SR4-BCC error

SR5-VRC error

SR6-BTC/SC detect

SR7-SSC detect

# APPLICATIONS INFORMATION Dedicated PGC

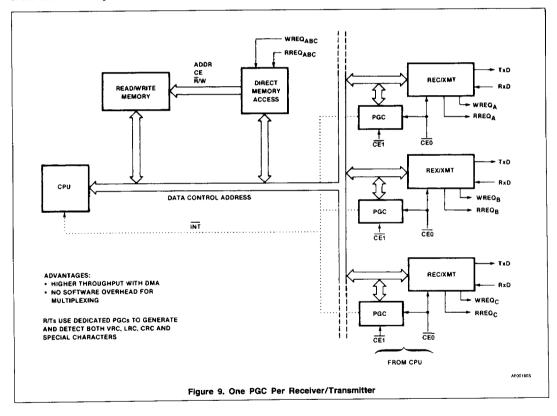

The most efficient use of the 2653 is to dedicate one to each R/T for two way alternate (half duplex) operation or two to each R/T for two way simultaneous (full duplex) operation (see Figure 9). The CPU configures each PGC (using CE1) by initializing the the mode register, command register, and character class array. Data transfers to or from the R/T can then be on a DMA basis with each receiver holding register ready signal used as a read request (RREQ) and each transmit holding register available signal used as a write request (WREQ) to the DMA controller. The CPU needs only to respond to enable interrupts from each of the PGCs. The individual INT outputs can be wire-OR'd into single CPU interrupt (INTRPT) with one pull up resistor. Each PGC in this system has a unique address that is decoded into the respective chip enables.

The CPU or DMA controller could send a block of memory data to the PGC to be error checked without sending that data to the R/T. In that case,  $\overline{\text{CE1}}$  is used.

### Multiplexed PGC

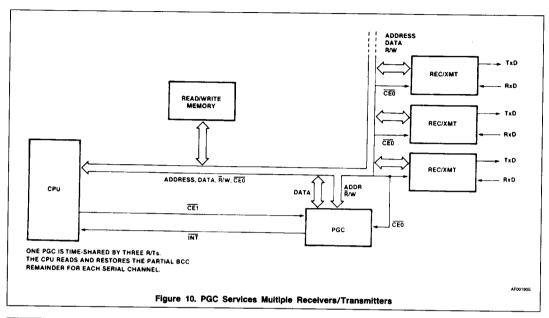

One PGC may be time-shared among a few R/Ts if the CPU saves and restores the mode register and partial BCC result in the BCC registers. These registers are accessed via CE1. There must be a separate save area for each R/T (serial channel) and a channel pointer indicating the last R/T that transferred or received a data character (see Figure 10).

The loading of the BCC registers will clear SR0-SR3 and all previously detected special characters, i.e., DLE, BTC/SC, BCC (BISYNC modes). The BCC accumulation will start again when the next character is loaded into the character register in all accumulation modes except single. That mode requires a start accumulation command.

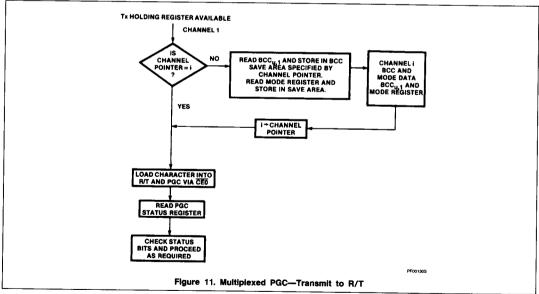

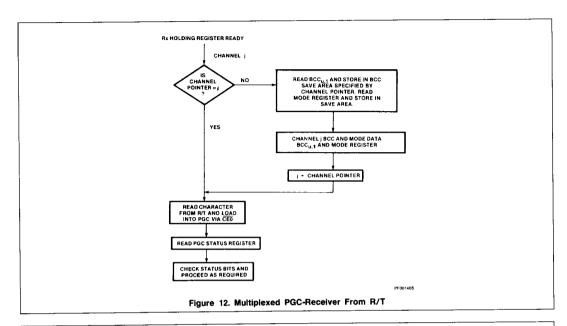

Figures 11 and 12 represent software flow diagrams for transmit and receive service requests. Note that interrupts from all other R/Ts must be masked during a read or write to the BCC registers so as not to affect the internal BCC address pointer. It is recommended that all R/T interrupts be masked while servicing an interrupt that accesses any PGC register.

### **BISYNC Operation**

Table 7 is a concise listing of SCN2651/ SCN2661 operating modes with recommended corresponding SCN2653 BCC accumulation modes.

### **Character Comparator**

The PGC can be used as a programmable data bus character comparator which monitors data bus transfers (CPU ↔ peripheral, CPU ↔ CPU, CPU ↔ memory, memory ↔ peripheral (via DMA)). The user selectively loads the character class array with BTC/SC and SSC characters to be compared. Status bits will be set and an interrupt can be generated upon SC and DLE-SSC detection. A match on one to 128 different characters or DLE-SSC sequences can be programmed.

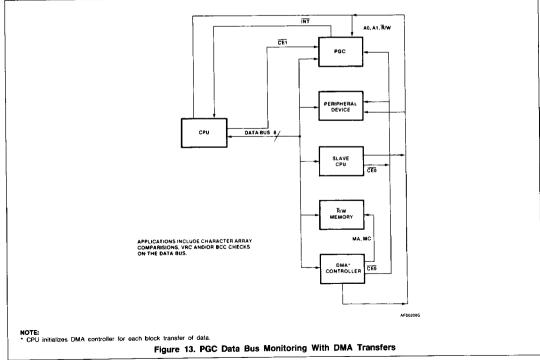

Figure 13 depicts an arrangement where the DMA controller or slave CPU handles data bus transfers, the PGC interrogates the data bus, and the host CPU responds to PGC interrupts.

# SCN2653/SCN68653

Table 7. BISYNC (ANSI 3.28, ISO 1745) Modes for SCN2651/SCN2661 and SCN2653

| SCN2651/SCN2661                   | SCN2653                           |

|-----------------------------------|-----------------------------------|

| OPERATING MODES                   | BCC ACCUMULATION MODE             |

| Sync normal non-strip             | BISYNC normal                     |

| Sync transparent non-strip        | BISYNC transparent                |

| Normal SYN/DLE strip <sup>1</sup> | BISYNC normal                     |

| Transparent SYN/DLE strip1        | Automatic accumulate <sup>2</sup> |

| Async (with SYN/DLE characters)   | BISYNC normal                     |

### NOTES:

- CPU should switch to non-strip mode after BTC detect. Otherwise a received BCC could be inadvertently stripped.

- 2. SSC detect should be ignored.

# SCN2653/SCN68653

# SCN2653/SCN68653

11111

# SCN2653/SCN68653

### ABSOLUTE MAXIMUM RATINGS1

| SYMBOL | PARAMETER                                        | RATING       | UNIT |

|--------|--------------------------------------------------|--------------|------|

| TA     | Operating ambient temperature <sup>2</sup> range | 0 to +70     | °C   |

| TSTG   | Storage temperature range                        | -65 to +150  | °C   |

|        | All voltages with respect to ground <sup>3</sup> | -0.5 to +6.0 | V    |

### NOTES:

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operation sections of this specification is not implied.

- 2. For operating at elevated temperatures the device must be derated based on + 150°C maximum junction temperature.

- 3. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. However, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

# DC ELECTRICAL CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{CC} = 5V \pm 5\%$

| SYMBOL                             | PARAMETER              | TEST CONDITIONS                                          |     |             |          |      |

|------------------------------------|------------------------|----------------------------------------------------------|-----|-------------|----------|------|

|                                    |                        |                                                          | Min | Тур         | Max      | UNIT |

| Input voltag                       | e                      |                                                          |     | <del></del> | L        | I    |

| V <sub>IL</sub><br>V <sub>IH</sub> | Low<br>High            |                                                          | 2   |             | 0.8      | ٧    |

| Output volta                       | ge                     |                                                          |     |             | L,       | L    |

| V <sub>OL</sub><br>V <sub>OH</sub> | Low<br>High            | $I_{OL} = 2.2 \text{mA}$<br>$I_{OH} = -400 \mu \text{A}$ | 2.4 | 0.25<br>2.8 | 0.45     | ٧    |

| l <sub>IL</sub>                    | Input load current     | V <sub>IN</sub> = 0 to 5.5V                              |     |             | 10       | μΑ   |

| Output leaka                       | ge current             |                                                          |     |             |          |      |

| lro<br>Iro                         | Data bus<br>Open drain | V <sub>OUT</sub> = 4.0V<br>V <sub>OUT</sub> = 4.0V       |     |             | 10<br>10 | μΑ   |

| lcc                                | Power supply current   |                                                          |     | 45          | 75       | mA   |

# AC ELECTRICAL CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{CC} = 5.0 V \pm 5\%^{1}$ , 2, 3

| SYMBOL                       | PARAMETER                       | LIN  | NITS |      |

|------------------------------|---------------------------------|------|------|------|

|                              | PANAMETER                       | Min  | Max  | UNIT |

| t <sub>CE</sub>              | Chip enable pulse width         | 250  |      | ns   |

| t <sub>CED</sub>             | Chip enable period D            | 1750 |      | ns   |

| t <sub>CEC</sub> 4           | Chip enable period C            | 1750 |      | ns   |

| t <sub>AS</sub>              | Address setup                   | 10   |      | ns   |

| t <sub>AH</sub>              | Address hold                    | 10   |      | ns   |

| tcs                          | Control setup                   | 10   |      | ns   |

| t <sub>CH</sub>              | Control hold                    | 10   |      | ns   |

| t <sub>DS</sub> 5            | Data setup                      | 150  |      | ns   |

| t <sub>DH</sub>              | Data hold                       | 15   |      | ns   |

| t <sub>DD</sub> 6            | Data delay time for read        |      | 200  | ns   |

| t <sub>DF</sub> <sup>6</sup> | Data bus floating time for read | 1    | 100  | ns   |

| t <sub>INTL</sub> 7          | Interrupt low delay             |      | 1600 | ns   |

| t <sub>INTH</sub> 7          | Interrupt high delay            |      | 600  | ns   |

- 1. Parameters are valid over operating temperature range unless otherwise specified.

- 2. All voltage measurements are referenced to ground. All time measurements are at 50% level for inputs and at the 0.8V or 2V level for outputs. Input levels for testing are 0.45V and 2.4V.

- 3. Typical values are at +25°C, typical supply voltages and typical processing parameters.

- 4. t<sub>CEC</sub> = 600ns during PGC initialization when no BCC accumulation is in progress.

- 5.  $t_{DS}$  = 50ns whenever  $\overline{CE0}$  is used.

- 6. Test conditions: C<sub>L</sub> = 150pF.

- 7. INT is an open drain output.

# SCN2653/SCN68653