U<sub>L</sub>

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

# 6 DECADE PREDETERMINING UP/DOWN COUNTER

#### **FEATURES:**

- +4.75V to +15V (Vss VDD)

- · Preset, Presignal and Mainsignal Store

- DC to 250kHz Count Frequency

- Fully Synchronous Operation

Three Comparators with Output Flags

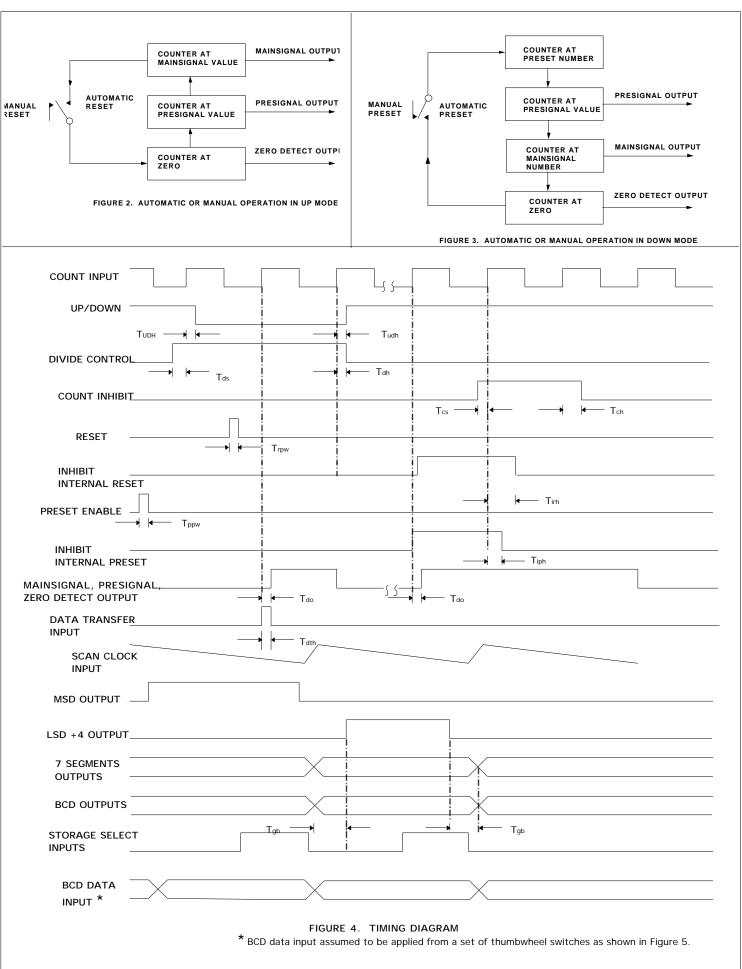

Automatic or Manual Preset/Reset Control

- Thumbwheel Interface for Storage Selects

- · Prescale on Count Input Selectable

- Count Inhibit

- Up/Down Control

- Scan Rate up to 150kHz

- Scan Oscillator has Override Capability

- Blanking Override for Decimal Point Operaton

- Multiplexed 7 Segment and BCD Data Output

- Output latches

- Reset

- · Hysteresis on Count Input

- CMOS Type Noise Immunity on all other inputs

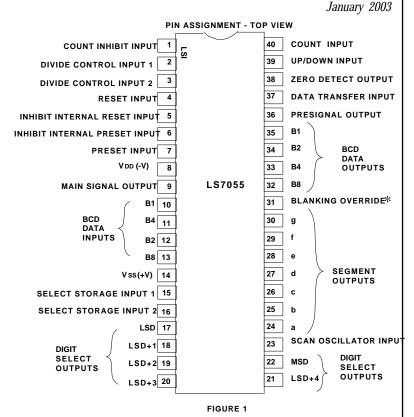

- LS7055, LS7056 (DIP) See Figure 1

#### **DESCRIPTION:**

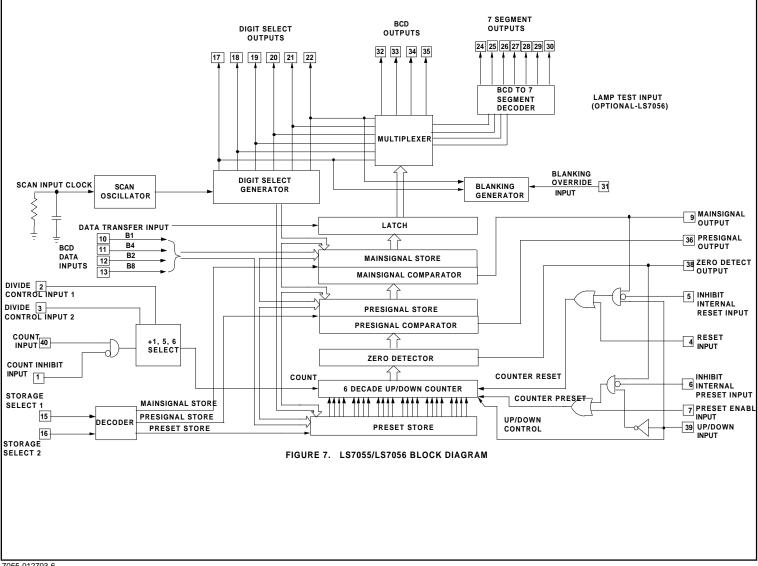

The LS7055/LS7056 is a MOS synchronous 6 decade Up/Down counter. The circuit includes storages and comparators, zero detect, automatic presetting and resetting, output latches, multiplexed output BCD and seven segment data. Thumbwheel switches can be used to provide BCD data to the storage networks in the circuit.

# COUNT (Pin 40)

Counter operates at speeds up to 250kHz and advances on the positive edge of the input count pulse.

#### UP/DOWN (Pin 39)

Counter operates in up or down mode. A high input causes the counter to operate in the up mode while a low input causes it to operate in the down mode.

# **COUNT INHIBIT (Pin 1)**

A high input inhibits counting and the counter remains at its last count. A low input enables counting.

#### **DATA TRANSFER INPUT** (Pin 37)

A high input allows the seven segment display and BCD data to follow the count (the internal latches become transparent). A low input prevents updating of the latches as the count advances and the seven segment display and BCD data outputs remain fixed.

#### **RESET** (Pin 4)

A high input resets and holds all counter stages at zero. A low input allows counter operation.

<sup>\*</sup> OPTIONAL CHOICE-LAMP TEST (SPECIFY LS7056)

# **INHIBIT INTERNAL RESET** (Pin 5)

A high input prevents the automatic reset of the counter to zero when in the up mode and when the counter reaches the number in the main signal store.

# PRESET (Pin 7)

A high level presets the BCD counter to the number set in the preset store. A low input allows counter operation.

# **INHIBIT INTERNAL PRESET (Pin 6)**

A high input prevents the automatic preset of the counter to the number set in preset store when in the down mode and the counter reaches zero.

#### **SELECT STORAGE OF DATA INPUTS** (Pins 15, 16)

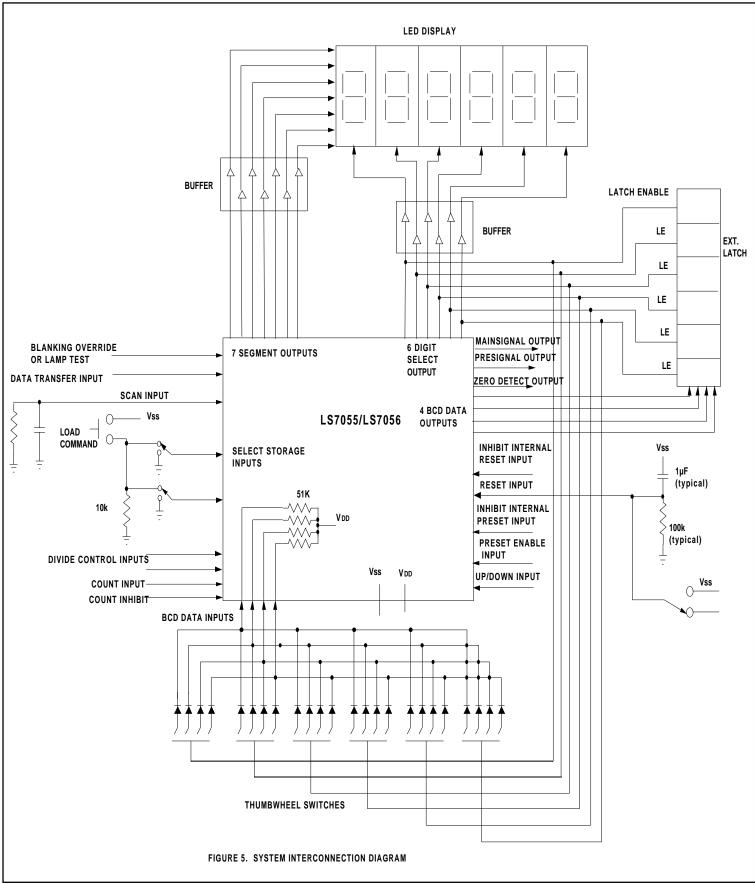

Two inputs which allow BCD data to be stored in either the preset, presignal or main signal store. The proper method for loading the stores is depicted in Figure 4.

| PIN 15 | PIN16 | STORAGE      |

|--------|-------|--------------|

| 0      | 0     | No Selection |

| 1      | 0     | Presignal    |

| 0      | 1     | Main Signal  |

| 1      | 1     | Preset       |

#### **BCD DATA INPUTS** (Pins 10, 11, 12, 13)

Four inputs containing BCD data which are applied to either the preset, presignal or main signal stores one decade at a time. This data can be provided by a set of thumbwheel switches which are driven by the digit select outputs. Referring to Figure 4, the BCD data inputs have built in pull down resistors (typically 51k Ohms).

### **DIVIDE CONTROL** (Pin 2, Pin 3)

Two inputs for selection to divide the count input by either 5, 6 or 1.

| PIN 2 | PIN 3 |             |

|-------|-------|-------------|

| 0     | 0     | Divide by 5 |

| 1     | 0     | Divide by 6 |

| 1     | 1     | Divide by 1 |

### MAIN SIGNAL OUTPUT (Pin 9)

An internal comparator provides a high level output when the number set into the main signal store is reached by the counter. In the automatic mode and with the Up/Down control in the up position, the counter is reset to zero and the main signal output is typically a 2.5 µs wide pulse. In the manual mode (inhibit internal reset is high) the output remains high until the next count input or a reset is applied.

### PRESIGNAL OUTPUT (Pin 36)

The presignal comparator provides a high level output when the number set into the presignal storage is reached. The output remains high until the next count input or a reset or preset is applied.

### **SCAN CLOCK INPUT (Pin 23)**

A DC to 150kHz oscillator input port for driving the internal scan counter is provided. Up to 150kHz may be used when demultiplexilng BCD data using the digit select outputs. The frequency of the oscillator is determined by an external RC network as shown in Figure 4. Table 1 indicates several frequencies and their associated RC networks. The oscillator can be overridden using an external driver. Table 2 indicates the external drive requriements. When displaying, leading zero blanking and unblanking on LSD is provided.

# BLANKING OVERRIDE (LS7055 only) (Pin 31)

On circuits with this option, unblanking can be made to occur on any digit by connecting that digit select output to the unblanking input. Since the input has an internal pull down resistor, it can be left floating when not in use.

### LAMP TEST (LS7056 only) (Pin 31)

A high input will cause the seven segment outputs to provide all 8's to a display (BCD outputs are not affected).

#### **ZERO DETECT OUTPUT (Pin 38)**

A high output occurs whenever the counter is at zero. In the automatic mode and with the Up/Down input in the down mode, the counter presets to the number in the preset store and the zero detect output is typically a 1.5 µs pulse. In the manual mode (inhibit internal preset is high), the counter remains at zero until a preset or a count input pulse is applied.

# **DIGIT SELECT OUTPUTS** (Pins 17, 18, 19, 20, 21, 22)

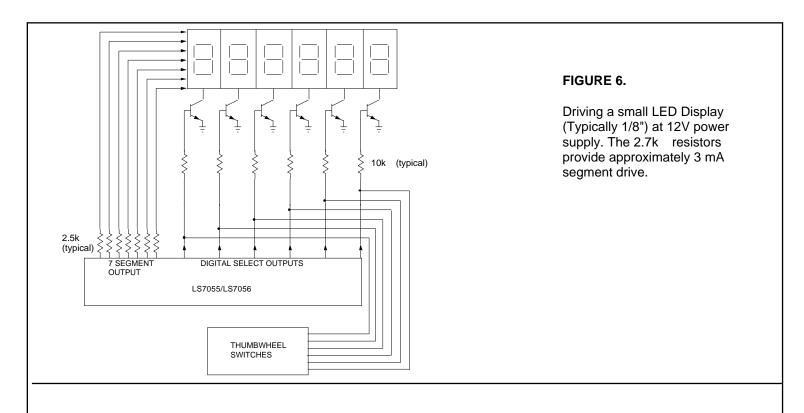

Six positive outputs for digit identification. The outputs occur sequentially going from MSD to LSD and can be applied directly to thumbwheel switches. They must be buffered before being applied to the seven segment displays either by a CMOS or transistor buffer as shown in Figure 5. Figure 3 indicates the timing relationship between the digit select outputs and the BCD data outputs.

SEVEN SEGMENT OUTPUTS (Pins 24, 25, 26, 27, 28, 29, 30) Capable of sourcing current into the base of a common emitter NPN transistor for interfacing to a seven segment display. Small displays needing an average current of 0.5 mA can be interfaced to the circuit without external transistors. A typcial example of a 12V circuit is shown in Figure 5.

### **BCD OUTPUTS** (Pins 32, 33, 34, 35)

Four outputs corresponding to the BCD data stored in the latches. The outputs can be demultiplexed using the circuitry shown in Figure 4. As can be seen from the timing diagram of Figure 3, the BCD data output and seven segment outputs are completely stable during the positive digit select outputs.

#### **POWER-ON-RESET**

An external RC network applied to the reset input as shown in Figure 4 can be used to reset the counter to zero upon application of power. The preset input must be held low at this time. The RC time constant should be larger than the power supply rise time. For example, a 100k  $\,$  resistor and a 0.1  $\mu F$  capacitor could be used if the power supply rise time was 5 ms.

# **POWER SUPPLIES**

The circuit operates over the range of +4.75V to +15V. At +4.75V, the inputs are TTL and CMOS compatible (external pull-up resistors must be provided on any input which does not pull up to Vss) when using TTL inputs. At +15V, inputs are CMOS compatible. All outputs are CMOS compatible from +4.75V to +15V.

#### TABLE 1

Typical resistor/capacitor values for the scan oscillator

| RESISTOR | CAPACITOR | TYPICAL FREQUENCY |

|----------|-----------|-------------------|

| 12k      | 1000pF    | 100kHz            |

| 100k     | 1000pF    | 10kHz             |

| 1.0M     | 1000pF    | 1kHz              |

# TABLE 2

Driver Requirements for Overriding Scan Oscillator Input

| Power Supply (V) | Sink Current | Source Current |

|------------------|--------------|----------------|

| 5                | 1.0mA        | 0              |

| 10               | 4.5mA        | 0              |

| 15               | 10.0mA       | 0              |

### **MAXIMUM RATINGS**

# DYNAMIC ELECTRICAL CHARACTERISTICS

$(VDD = VGG = 0V, Vss = +4.75 \text{ to } +15V, -25^{\circ}C \quad TA \quad +70^{\circ}C$ unless otherwise specified.)

| PARAMETER                | SYMBOL | VALUE       | UNITS |

|--------------------------|--------|-------------|-------|

| Storage Temperature      | Tstg   | -65 to +150 | °C    |

| Operating Temperature    | TA     | -25 to +70  | °C    |

| Voltage (any pin to Vss) | Vmax   | -30 to +0.5 | V     |

| DC FI | FCTRICAL | CHARACTERISTICS |

|-------|----------|-----------------|

DC ELECTRICAL CHARACTERISTICS (VDD = VGG = 0V, Vss = +4.75 to +15V, -25°C TA +70°C unless otherwise specified.)

| otnerwise specified.)                                                                                                                                                                                      |                                          |                                                                   |                          |                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------|--------------------------|--------------------------|

| PARAMETER  Quescent Supply Current  (All Input Pins Tied to Vss)  (All Output Pins Left Open)                                                                                                              | SYM<br>-                                 | MIN<br>-                                                          | MAX<br>-                 | UNITS<br>-               |

| Vss = 4.75V<br>Vss = 15V<br>Input Capacitance All Inputs<br>Hysteresis On Count Input<br>Noise Immunity All Other Inputs                                                                                   | IDD<br>IDD<br>Cin<br>VNL<br>VNH          | -<br>-<br>-<br>30%(Vss - Vdd)<br>30%(Vss - Vdd)<br>30%(Vss - Vdd) | 20<br>25<br>10<br>-<br>- | mA<br>mA<br>pF<br>V<br>V |

| Output Levels All Outputs (All Output Pins Left Open)  7 Segment Output Current                                                                                                                            | Vol<br>Voh                               | -<br>Vss - 1                                                      | 0.5<br>-                 | V<br>V                   |

| Source Current Vss = 4.75V, VouT = 0.7V, 70°C Vss = 4.75V, VouT = 0.7V, 25°C Vss = 10V, VouT = 7V, 25°C Vss = 15V, VouT = 13V, 70°C Note: Limit Segment Source Curr                                        | ISEG<br>ISEG<br>ISEG<br>ISEG             | 0.3<br>0.4<br>2.0<br>3.0<br>4.5mA max.                            | -<br>-<br>-              | mA<br>mA<br>mA           |

| Sink Current (Vout = 0.4V)<br>Vss = 4.75V, 25°C<br>Vss = 10V, 25°C<br>Vss = 15V, 25°C<br>Vss = 15V, 70°C                                                                                                   | ISEG<br>ISEG<br>ISEG                     | -21<br>-17<br>-15<br>-10                                          | -<br>-<br>-              | μΑ<br>μΑ<br>μΑ<br>μΑ     |

| BCD, Zero Detect, Mainsignal an Source Current  Vss = 4.75V, Vout = 4.5V, 70°C  Vss = 4.75V, Vout = 4.5V, 25°C  Vss = 10V, Vout = 9.0V, 25°C  Vss = 15V, Vout = 13V, 25°C  Note: Limit Segment Source Curr | Iон<br>Iон<br>Iон<br>Iон                 | 0.10<br>0.13<br>0.7<br>2.5                                        | -<br>-<br>-<br>-         | mA<br>mA<br>mA           |

| Sink Current (VOUT = 0.4V)<br>Vss = 4.75V, 25°C<br>Vss = 10V, 25°C<br>Vss = 15V, 25°C<br>Vss = 15V, 70°C                                                                                                   | lol<br>lol<br>lol                        | -7.5<br>-6.0<br>-5.5<br>-4.0                                      | -                        | μΑ<br>μΑ<br>μΑ<br>μΑ     |

| Digit Select Output Current Source Current Vss = 4.75V, Vout = 4.5V, 70°C Vss = 4.75V, Vout = 4.5V, 25°C Vss = 10V, Vout = 9V, 25°C Vss = 15V, Vout = 13.5V, 70°C Note: Limit digit select current to      | lон<br>loн<br>loн<br>loн<br>loн<br>10mA. | 0.28<br>0.35<br>2.0<br>7.0                                        | -<br>-<br>-              | mA<br>mA<br>mA           |

| Sink Current (VOUT = 0.4V)<br>Vss = 4.75V, 25°C<br>Vss = 10V, 25°C<br>Vss = 15V, 25°C<br>Vss = 15V, 70°C                                                                                                   | lol<br>lol<br>lol                        | -15<br>-12<br>-11                                                 |                          | μΑ<br>μΑ<br>μΑ<br>μΑ     |

| PARAMETER                                                                  | SYM          | MIN    | MAX | UNITS    |

|----------------------------------------------------------------------------|--------------|--------|-----|----------|

| Count Input Frequency                                                      | _            | ъ0     | 050 |          |

| Vss = 4.75V                                                                | Fc           | DC     | 250 | kHz      |

| Vss = 10V                                                                  | Fc           | DC     | 175 | kHz      |

| Vss = 15V                                                                  | Fc           | DC     | 125 | kHz      |

| Pulse Width                                                                | Тан.         | 2      |     |          |

| Vss = 4.75V                                                                | Tcw          | 2      | -   | μs       |

| Vss = 10V                                                                  | Tcw<br>Tcw   | 2.8    | -   | μs       |

| Vss = 15V                                                                  |              | 4      | -   | μs       |

| Rise Time<br>Fall Time                                                     | Tcr<br>Tcf   | -      |     | μs       |

|                                                                            |              | -      | 100 | µs<br>   |

| Scan Input Frequency                                                       | Fsc          | DC     | 100 | kHz      |

| Divide Control<br>Set-Up Time                                              | Tds          | 2      |     | ш        |

| Hold Time                                                                  | Tdh          | 8      | -   | μs       |

|                                                                            |              | -      |     | μs       |

| Reset Pulse Width** Reset                                                  | Trpw         | 2      | -   | μs       |

| Set Up Time                                                                | Trs          | 0      | _   | ш        |

| Hold Time                                                                  | Trh          | 6      | _   | µs<br>µs |

| Inhibit Internal Reset                                                     |              | U      |     | μο       |

| Set Up Time                                                                | Tis          | 0      | _   | μs       |

| Hold Time*                                                                 | Tirh         | 3      | _   | μs       |

| Preset Pulse Width**                                                       | Tppw         | 2      | _   | μs       |

| Preset Enable                                                              | ippw         | 2      |     | μο       |

| Set Up Time                                                                | Tips         | 0      | _   | μs       |

| Hold Time*                                                                 | •            |        | -   | •        |

|                                                                            | Tiph         | 6      |     | μs       |

| Data Transfer Pulse Width**                                                | Tdtw         | 2      | -   | μs       |

| Data Transfer                                                              | T-14-        | 0      |     |          |

| Set Up Time                                                                | Tdts<br>Tdth | 0<br>6 | -   | μs       |

| Hold Time                                                                  | rum          | O      | -   | μs       |

| Up/Down                                                                    | Tuds         | 0      |     |          |

| Set Up Time<br>Hold Time                                                   | Tuds         | 10     | -   | μs       |

| Count Inhibit                                                              | Tuu          | 10     | -   | μs       |

| Set Up Time                                                                | Tcs          | 2      | _   | II.C     |

| Hold Time                                                                  | Tch          | 10     | -   | μs       |

| Data Outputs (CL = 10pF)                                                   | 1011         | 10     | _   | μs       |

| Rise Time                                                                  | Tdr          | _      | 1.0 | μs       |

| Fall Time                                                                  | Tui          |        | 1.0 | μο       |

| Vss = 4.75V                                                                | Tdf          | _      | 2.0 | μs       |

| Vss = 10V                                                                  | Tdf          | _      | 3.0 | μS       |

| Vss = 15V                                                                  | Tdf          | -      | 4.0 | μS       |

|                                                                            |              |        | -   |          |

| Digit Select Outputs Guard Band Time                                       |              |        |     |          |

| within 7 segment & BCD outputs                                             | Tgb          | 0.5    | -   | μs       |

| See Figure 3                                                               | -            |        |     | •        |

| Main Cianal President 75 Date                                              |              |        |     |          |

| Main Signal, Presignal, Zero Detect Outputs delay with respect to positive |              |        |     |          |

| edge of Count Input                                                        | Tdo          | _      | 3   | μs       |

| oago or obuilt iliput                                                      | 1 40         |        | J   | μυ       |

Set-Up and Hold times are defined with respect to positive edge of count input except where indicated by asterisks.

The information included herein is believed to be accurate and reliable. However, LSI Computer Systems, Inc. assumes no responsibilities for inaccuracies, nor for any infringements of patent rights of others which may result from its use.

<sup>\*</sup> Indicates a hold time which must last for at least one whole count cycle plus 5µs past the next positive edge of count input.

<sup>\*\*</sup> Reset, Preset and Data Transfer Pulse Width is as specified except if applied when a count input is going positive. In that case the set-up and hold times govern.