#### **Features**

- Provides DTMF high and low group filtering

- Hard-limiting on filter outputs

- 6 pole bandpass high and low group filters

- 40 dB (typ) Intergroup attenuation

- Dial tone suppression

- +5 to +12V single supply operation

- Logical powerdown

- Uses inexpensive 3.58 MHz crystal

- Wide dynamic range 30dB

## **Applications**

In DTMF Receivers For

- End-to-end signalling

- Control systems

- PABX

- Central Office

- Mobile Radio

- Key systems

- Tone to pulse converters

## Description

The Mitel MT8865 contains both the high group and low group filtering and comparator functions required to implement a Dual Tone Multi Frequency tone receiver using a Mitel DTMF Digital Detector (i.e., Mitel MT8860). Switched capacitor techniques are used to implement the filters and the device is fabricated using Mitel's double poly ISO2-CMOS high density technology. The filter clocks are

derived from an on-chip oscillator requiring only a low cost TV crystal as external components. The MT8865 offers single supply operation over a wide supply voltage range and incorporates a logical power down facility.

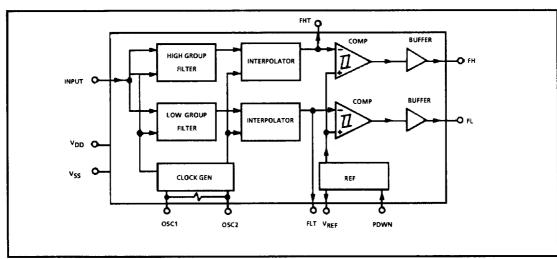

Fig. 1 Functional Block Diagram

## **Absolute Maximum Ratings\***

|   | Paramet                           | er                                               | Symbol                               | Min                   | Max                   | Units    |

|---|-----------------------------------|--------------------------------------------------|--------------------------------------|-----------------------|-----------------------|----------|

| 1 | V <sub>DD</sub> - V <sub>SS</sub> |                                                  |                                      |                       | 15                    | V        |

| 2 | Voltage on any pin except OS      | 1, OSC2                                          |                                      | V <sub>EE</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V        |

| 3 | Max. Current at any pin           |                                                  | l <sub>1</sub>                       |                       | 10                    | mA       |

| 4 | Storage Temperature               | C Package<br>E Package                           | T <sub>STG</sub><br>T <sub>STG</sub> | - 65<br>- 65          | + 150<br>+ 125        | °C       |

| 5 | Power Dissipation                 | C Package <sup>®</sup><br>E Package <sup>®</sup> | P <sub>D</sub>                       |                       | 850<br>400            | mW<br>mW |

<sup>\*</sup>Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

## **Recommended Operating Conditions** - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

|   | , Parameter             | Sym             | Min  | Typ | Max | Units | Test Conditions |

|---|-------------------------|-----------------|------|-----|-----|-------|-----------------|

| 1 | DC Power Supply Voltage | V <sub>DD</sub> | 4.75 |     | 13  | V     |                 |

| 2 | Operating Temperature   | To              | -40  |     | +85 | °C    |                 |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

### DC Electrical Characteristics - Voltages are with respect to ground (V<sub>SS</sub>), T<sub>A</sub> = 25°C, f<sub>c</sub> = 3.579545 MHz unless otherwise stated.

|    |             | Characteristics                               | Sym                                | Min         | Тур        | Max        | Units    | Test Conditions                                                     |

|----|-------------|-----------------------------------------------|------------------------------------|-------------|------------|------------|----------|---------------------------------------------------------------------|

| 1  |             | Operating Supply Voltage                      | V <sub>DD</sub>                    | 4.75        |            | 13         | V<br>V   | $V_{DD} = 5V$<br>$V_{DD} = 12V$                                     |

| 2  | S           | Operating Supply Current                      | I <sub>DD</sub>                    |             | 1.2<br>5   | 3<br>10    | mA<br>mA | $V_{DD} = 5V$ , PDWN = $V_{SS}$<br>$V_{DD} = 12V$ , PDWN = $V_{SS}$ |

| 3  | U<br>P      | Standby Supply Current                        | I <sub>DDS</sub>                   |             | 70<br>300  | 100<br>500 | μA<br>μA | $V_{DD} = 5V$ , PDWN = $V_{DD}$<br>$V_{DD} = 12V$ , PDWN = $V_{DD}$ |

| 4  | P<br>L<br>Y | Operating Power Consumption Fig. 5(c)         | P <sub>O</sub>                     |             | 6<br>60    |            | mW<br>mW | $V_{DD} = 5V$ , PDWN = $V_{SS}$<br>$V_{DD} = 12V$ , PDWN = $V_{SS}$ |

| 5  |             | Standby Power Consumption C = 15 pF           | P <sub>S</sub><br>P <sub>S</sub>   |             | 0.5<br>1.5 |            | mW<br>mW | $V_{DD} = 5V$ , PDWN = $V_{DD}$<br>$V_{DD} = 12V$ , PDWN = $V_{DD}$ |

| 6  | !           | Low Level Input Voltage<br>PDWN & OSC1        | V <sub>IL</sub>                    |             |            | 1.5<br>3.5 | V<br>V   | $V_{DD} = 5V$ $V_{DD} = 12V$                                        |

| 7  | N P U       | High Level Input Voltage<br>PDWN & OSC1       | V <sub>IH</sub><br>V <sub>IH</sub> | 3.5<br>8.5  |            |            | V<br>V   | $V_{DD} = 5V$ $V_{DD} = 12V$                                        |

| 8  | 5           | Pull Down Sink Current<br>PDWN                | l <sub>iH</sub>                    |             | 3<br>12    | 6<br>24    | μA<br>μA | $V_{DD} = 5V$<br>$V_{DD} = 12V$                                     |

| 9  |             | Input Current<br>OSC1                         |                                    |             | ±2.5<br>±6 |            | μA<br>μA | $V_{DD} = 5V$ $V_{DD} = 12V$                                        |

| 10 | 0           | Low Level Output Voltage<br>FL, FH, OSC2      | V <sub>OL</sub>                    |             |            | 0.1<br>0.1 | V<br>V   | $V_{DD} = 5V$ , No Load<br>$V_{DD} = 12V$ , No Load                 |

| 11 | U<br>T<br>P | High Level Output Voltage<br>FL, FH, OSC2     | V <sub>OH</sub><br>V <sub>OH</sub> | 4.9<br>11.9 |            |            | V<br>V   | V <sub>DD</sub> = 5V, No Load<br>V <sub>DO</sub> = 12V, No Load     |

| 12 | U<br>T<br>S | Ouput Drive Current, FL, FH<br>N Channel Sink | lor<br>lor                         | 0.2<br>0.5  |            |            | mA<br>mA | $V_{DD} = 5V, V_{OL} = 0.4V$<br>$V_{DD} = 12V, V_{OL} = 1.2V$       |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing

<sup>&</sup>lt;sup>©</sup>Derate above 75 °C at 16 mW / °C. All leads soldered to board. <sup>®</sup>Derate above 25 °C at 6.3 mW / °C. All leads soldered to board.

# **DC Electrical Characteristics (Cont'd)** - Voltages are with respect to ground (V<sub>SS</sub>), T<sub>A</sub> = 25 °C, f<sub>C</sub> = 3.579545 MHz unless otherwise stated.

|    | _           | Characteristics                                  | Sym              | Min         | Тур | Max        | Units    | Test Conditions                                                |

|----|-------------|--------------------------------------------------|------------------|-------------|-----|------------|----------|----------------------------------------------------------------|

| 13 | 0           | Output Drive Current OSC2,<br>N Channel Sink     | l <sub>OL</sub>  | 0.1<br>0.25 |     |            | mA<br>mA | $V_{DD} = 5V, V_{OL} = .4V$<br>$V_{DD} = 12V, V_{OL} = 1.2V$   |

| 14 | T<br>P<br>U | Output Drive Current, FL, FH<br>P Channel Source | Іон<br>Іон       | 0.2<br>0.5  |     |            | mA<br>mA | $V_{DD} = 5V, V_{OH} = 4.6V$<br>$V_{DD} = 12V, V_{OH} = 10.8V$ |

| 15 | T<br>5      | Output Drive Current, OSC2,<br>P Channel Source  | Іон<br>Іон       | 0.1<br>0.25 |     |            | mA<br>mA | $V_{DD} = 5V, V_{OH} = 4.6V$<br>$V_{DD} = 12V, V_{OH} = 10.8V$ |

| 16 |             | Output Voltage, V <sub>Ref</sub>                 | V <sub>Ref</sub> | 2.3<br>5.4  |     | 2.6<br>6.2 | V        | $V_{DD} = 5V$ , No Load $V_{DD} = 12V$ , No Load               |

| 17 |             | Output Resistance, V <sub>Ref</sub>              | R <sub>OR</sub>  |             |     | 16<br>8    | kΩ<br>kΩ | $V_{DD} = 5V$ $V_{DD} = 12V$                                   |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

## AC Electrical Characteristics - Voltages are with respect to ground ( $V_{SS}$ ), $T_A = 25 \, ^{\circ}\text{C}$ , $f_c = 3.579545$ , $V_{DD} = 4.75 - 13V$ .

|    |                                                  | Characteristics                                              | Sym                                                        | Min          | Тур          | Max                               | Units         | Test Conditions                                |

|----|--------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|--------------|--------------|-----------------------------------|---------------|------------------------------------------------|

| 1  |                                                  | Dynamic Range                                                |                                                            | 30           |              | 36                                | dB            |                                                |

| 2  |                                                  | Valid Input Signal Levels<br>(Each tone of composite signal) |                                                            | 27.9<br>67.0 |              | V <sub>DD</sub> /2<br>883<br>2120 |               | $V_{DD} = 5V$ $V_{DD} = 12V$                   |

| 3  | F<br>ŀ                                           | Input Impedance                                              | Zi                                                         | 10           |              |                                   | MΩ            |                                                |

| 4  | Ĺ                                                | Passband Ripple                                              | Α <sub>V</sub>                                             |              | ±0.3         | ±1.0                              | dB            | See Note 1                                     |

| 5  | T<br>E                                           | Low Group Lower Limit<br>1dB Bandwidth Upper Limit           | f <sub>LL</sub><br>f <sub>LU</sub>                         | 958          | 670<br>990   | 684                               | Hz<br>Hz      |                                                |

| 6  | R                                                | High Group Lower Limit<br>1dB Bandwidth Upper Limit          | f <sub>HL</sub><br>f <sub>HU</sub>                         | 1660         | 1162<br>1740 | 1188                              | Hz<br>Hz      |                                                |

| 7  |                                                  | Intergroup Rejection<br>Low Group with High Tone             | IR <sub>L1209</sub><br>IR <sub>L1477</sub>                 | 34<br>36     | 45<br>40     |                                   | dB<br>dB      | 1209Hz - w.r.t. 770Hz<br>1477Hz - w.r.t. 770Hz |

| 8  | Intergroup Rejection<br>High Group with Low Tone |                                                              | IR <sub>H941</sub><br>IR <sub>H770</sub>                   | 38<br>36     | 50<br>40     |                                   | dB<br>dB      | 941Hz - w.r.t. 1336Hz<br>770Hz - w.r.t. 1336Hz |

| 9  |                                                  | Dial Tone Rejection<br>Low Group                             | DR <sub>L440</sub><br>DR <sub>L350</sub>                   | 40<br>28     | 60<br>30     |                                   | dB<br>dB      | 440Hz - w.r.t. 770Hz<br>440Hz - w.r.t. 770Hz   |

| 10 |                                                  | Dial Tone Rejection<br>High Group                            | DR <sub>H440</sub><br>DR <sub>H350</sub>                   | 52<br>50     | 60<br>55     |                                   | dB<br>dB      | 440Hz - w.r.t. 1336Hz<br>350Hz - w.r.t. 1336Hz |

| 11 |                                                  | FHT FLT Maximum Permissible Load                             | R <sub>LFT</sub>                                           | 250          |              | 1000                              | kΩ<br>pF      |                                                |

| 12 | L<br>I<br>M                                      | Output Rise Time FL, FH Output Fall Time FL, FH              | t <sub>TLHO</sub>                                          |              | 90<br>60     | 150<br>100                        | ns<br>ns      | 10% to 90% V <sub>DD</sub>                     |

| 13 | C                                                | Crystal/Clock Freq.<br>OSC1, OSC 2                           | f <sub>c</sub>                                             | 3.5759       | 3.5795       | 3.5831                            | MHz           |                                                |

| 14 | OCK                                              | Clock Rise Time Input Fall Time (OSC 1) Duty Cycle           | t <sub>LHCI</sub><br>t <sub>HLCI</sub><br>DC <sub>CI</sub> | 40           | 50           | 110<br>110<br>60                  | ns<br>ns<br>% | See Note 2                                     |

| 15 |                                                  | Clock Output OSC 2<br>Capacitive Load                        | C <sub>LOC</sub>                                           |              |              | 30                                | pF            | Unbalanced load<br>see Fig. 5                  |

| 16 |                                                  | Capacitance Any Input                                        | C <sub>I</sub>                                             |              | 5            | 7.5                               | pF            |                                                |

Note 1. Passband ripple measured with respect to a passband gain of 0 dB  $\pm$  1dB.

Note 2. 10% to 90% V<sub>DD</sub>. Externally Applied Clock.

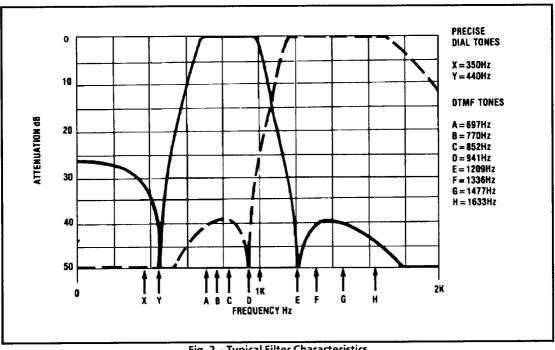

Fig. 2 - Typical Filter Characteristics

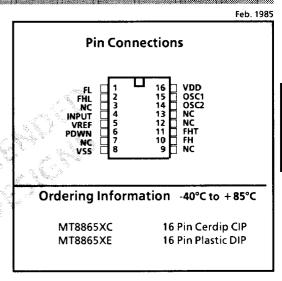

**Pin Description**

| Pin# | Name             | Description                                                                                                                           |

|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1    | FL               | Low Group Limiter Output.                                                                                                             |

| 2    | FLT              | Test Output. Monitors low group filter output. Decouple to V <sub>SS</sub> with 680pF capacitor.                                      |

| 3    | NC               | Not Connected.                                                                                                                        |

| 4    | INPUT            | Tone Signal Input (single ended).                                                                                                     |

| 5    | V <sub>Ref</sub> | Internal Reference. Can be used to bias input via 2M $\Omega$ resistor.                                                               |

| 6    | PDWN             | <b>Power Down Active High.</b> Internal pull down transistor. A high level signal powers down the device and inhibits the oscillator. |

| 7    | NC               | Not Connected.                                                                                                                        |

| 8    | Vss              | Negative (OV) Power Supply.                                                                                                           |

| 9    | NC               | Not Connected.                                                                                                                        |

| 10   | FH               | High Group Limiter Output.                                                                                                            |

| 11   | FHT              | <b>Test Output.</b> Monitors high group filter output. Decouple to V <sub>SS</sub> with 680pF capacitor.                              |

| 12   | NC               | Not Connected.                                                                                                                        |

| 13   | NC               | Not Connected.                                                                                                                        |

| 14   | OSC2             | Clock Output.                                                                                                                         |

| 15   | OSC1             | Clock Input. 3.579545 MHz crystal connected between this pin and OS2 completes the internal oscillator circuit.                       |

| 16   | VDD              | Positive Power Supply.                                                                                                                |

## **Functional Description**

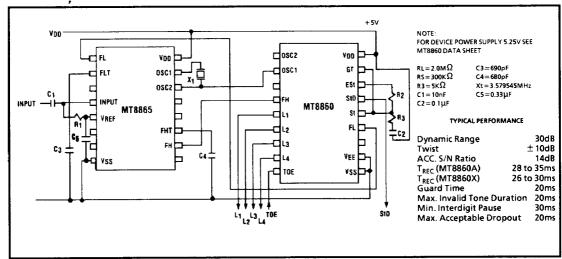

The MT8865 separates the high group and low group components of the dual tone signal and limits the resulting pair of sine waves, to produce square waves having the same frequencies as the individual input tones. These limited low group and high group tones appear at the FL and FH outputs respectively. To implement a complete DTMF receiver the FL and FH outputs are connected to the FL and FH inputs of the DTMF Digital Decoder (MT8860). See Fig. 3.

Separation of the low group and high group tones is achieved by applying the dual tone signal simultaneously to the inputs of two sixth order switched capacitor bandpass filters, the bandwidths

of which correspond to the bands enclosing the low group and high group tones. The frequency characteristic of each filter (see Fig. 2) also incorporates a notch at 440Hz to provide dial tone rejection. Each filter output is followed by a single order switched capacitor section which operates as an interpolator smoothing the signals prior to limiting. The limiting functions are performed by high gain comparators which are provided with hysteresis to prevent detection of unwanted low level signals and noise. The comparator outputs are buffered to drive the FL and FH output pins and detector device inputs. The MT8865 has a single ended input allowing connection either to a PCM decoder, radio receiver (Fig. 3) or via a differential buffer to a telephone line (Fig. 4). The signal input (Pin 4) should be biased at VDD/2. With the input

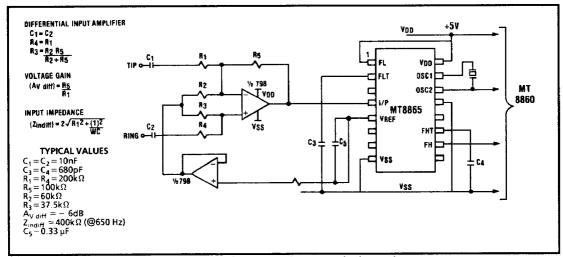

Fig. 3 - Connection Diagram for Single-Ended Input Receiver Using the MT8860 (5V Operation)

Fig. 4 - Circuit for Connection to a Telephone Line

capacitively coupled, this is achieved by connecting the signal input to  $V_{Ref}$  (Pin 5) via a  $2M\Omega$  resistor.

FLT and FHT allow the filter outputs to be monitored prior to limiting, and should each be decoupled to V<sub>SS</sub> by 680pF capacitors.

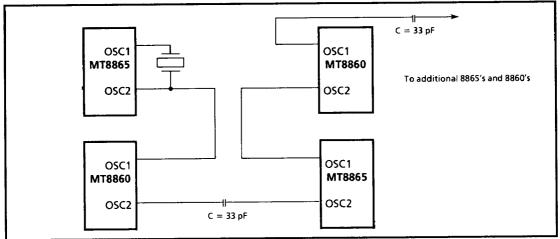

The MT8865 and its companion, the MT8860 DTMF decoder, can share a crystal by cascading the oscillator output (OSC2) to the adjacent device oscillator input (OSC1). The recommended circuit is shown in Figure 5.

Fig. 5 - Cascaded Oscillator Configuration