This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

# GEC PLESSEY

DS3107 2.2

# MV1443

# PCM TIMESLOT ZERO TRANSMITTER AND RECEIVER

The MV1443 combines the Timeslot Zero Transmitter and Receiver functions required by a 2.048Mbit 30 channel PCM transmission link operating in accordance with the appropriate CCITT Recommendations and forms part of the GPS 2Mbit PCM signalling series of devices. The circuit is fabricated in CMOS and operates from a single +5V supply with all inputs and outputs being TTL compatible.

The Timeslot Zero Transmitter half of the circuit is responsible for generating the timeslot zero synchronising word of a 2Mbit PCM link in accordance with CCITT Recommendation G.704. This function is performed by alternately generating sync frames, containing the CCITT Frame Alignment Signal, and non-sync frames containing user data bits.

The Timeslot Zero Receiver function searches for the CCITT Frame Alignment signal in the incoming data stream and when this is present the receiver synchronises itself to this pattern in accordance with the Frame Alignment strategy detailed in CCITT Recommendation G.732. Once frame alignment has been achieved the Timeslot Zero Receiver produces various timing outputs for the use of external circuitry and extracts the user data bits of timeslot zero.

#### FEATURES

- Single +5V supply.

- All Inputs and Outputs TTL compatible.

- Transmitter generates Frame Alignment Signal in accordance with CCITT Recommendation G.704.

- Enables access to User Data Bits of Timeslot Zero.

- Receiver Frame Synchronisation carried out in accordance with CCITT Recommendation G.732.

- Provides Alarm Outputs for Reception of Corrupted Alignment word and Loss of Frame Alignment.

- Extracts the International Spare Bits from Alternate Frames or from Frames 13 and 15 of the CCITT CRC multiframe.

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### **ELECTRICAL RATINGS**

| Supply Voltage | -0.5V to +7V       |

|----------------|--------------------|

| Input Voltage  | -0.5V to VDD +0.5V |

| Output Voltage | -0.5V to VDD +0.5V |

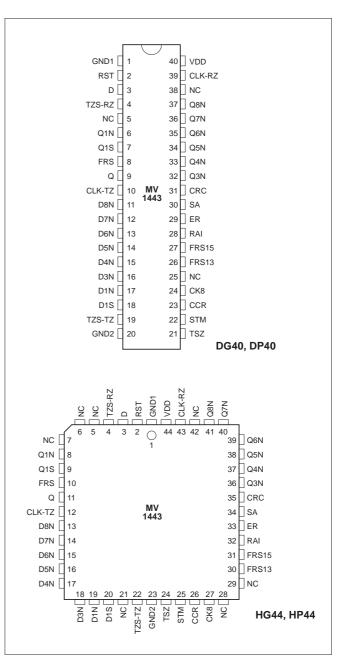

Fig. 1 Pin connections - top view

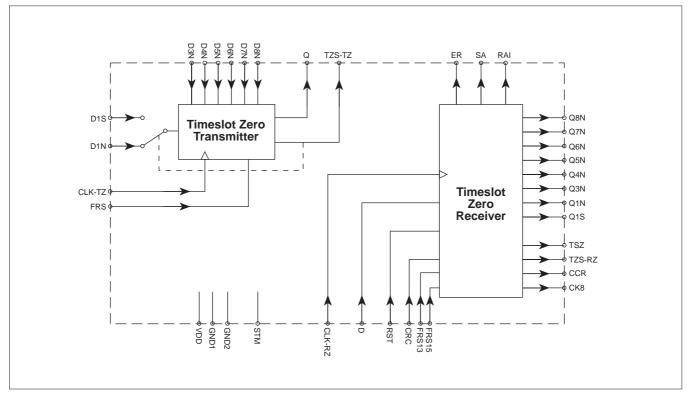

Fig. 2 Block diagram

#### FUNCTIONAL DESCRIPTION

The MV1443 combines the Timeslot Zero Transmitter and Receiver functions required by a 2.048Mbit 30 channel PCM transmission link operating in accordance with the appropriate CCITT Recommendations. The block diagram of the MV1443 is shown in Fig.2 and the function of each block is now described separately.

#### **Timeslot Zero Transmitter**

The Timeslot Zero Transmitter circuit generates the timeslot zero synchronising word required by a 2.048Mbit PCM link in accordance with CCITT Recommendation G.704. During alternate frames, denoted sync frames, the CCITT Frame Alignment Signal (FAS - 0011011) is combined with the International / CRC data bit input, D1S, for bit 1 and injected on to the PCM highway via the Q output. During the other interleaved frames, denoted non-sync frames, bit 2 of timeslot zero is set to '1' to avoid imitation of the FAS and this is combined with the second International / CRC data bit, D1N, for bit 1 and the user data bits, D3N-D8N, for bits 3 to 8, and again injected on to the PCM highway.

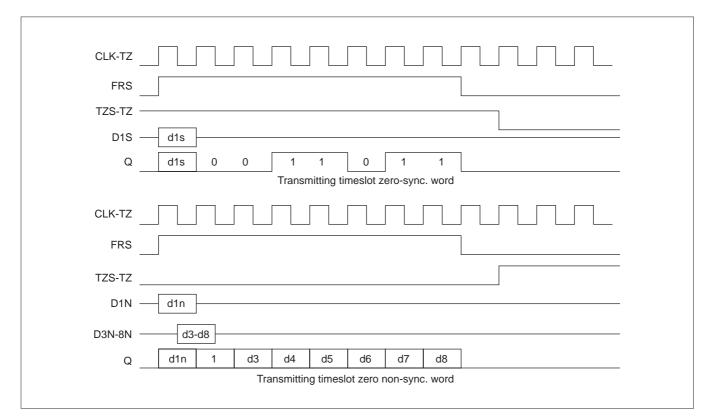

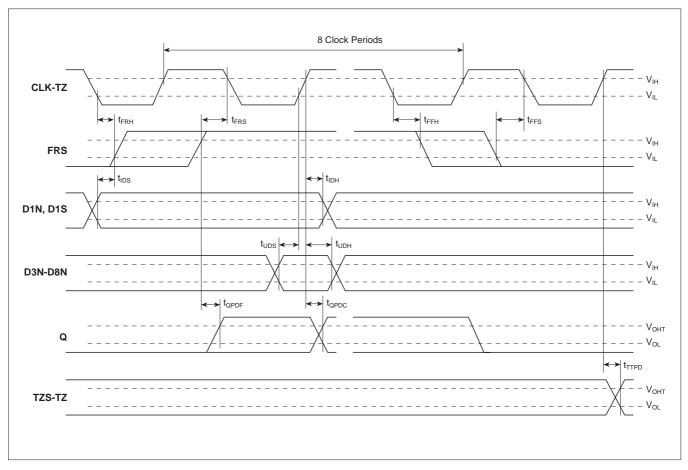

In order to perform this function the Timeslot Zero Transmitter requires 2 timing inputs in addition to the parallel data bit inputs, pins CLK-TZ and FRS. The CLK-TZ input is a 2.048MHz clock input whilst FRS is a high going pulse, 8 clock periods long, which is required to mask timeslot zero of each frame. In addition to the PCM data stream output the Timeslot Zero Transmitter produces a timing output, TZS-TZ, which changes state one clock period after the end of Timeslot Zero and is high during the transmission of timeslot zero of sync frames. The timing diagram of the Timeslot Zero Transmitter circuit is shown in Fig.3.

#### **Timeslot Zero Receiver**

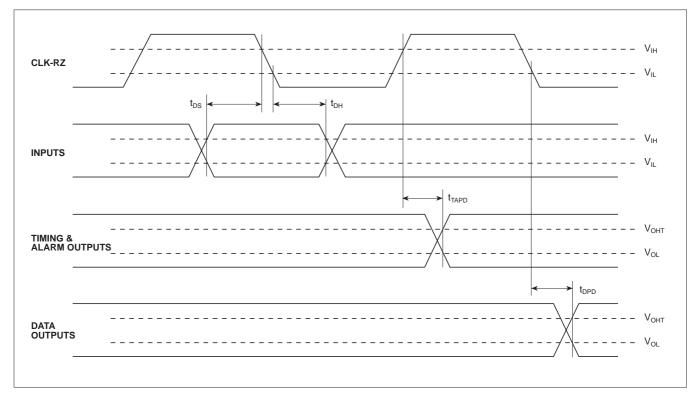

The Timeslot Zero Receiver circuit is responsible for searching for and locking on to the CCITT Frame Alignment Signal present in timeslot zero of the PCM data stream being clocked in to its D input. This process is carried out in accordance with the loss and recovery of frame alignment strategy described in CCITT Recommendation G.732. Once frame alignment has been achieved the Timeslot Zero Receiver circuit outputs various timing reference signals for the synchronisation of external circuitry. These timing outputs will all free run if frame synchronisation is subsequently lost. In addition, a control input, RST, may be used to reset this synchronisation process, forcing the receiver out of frame alignment.

The Timeslot Zero Receiver circuit produces 4 timing outputs for use by external circuitry if required. The first of these timing outputs is TSZ which is an 8 clock period long, high going pulse masking the position of timeslot zero, similar to the FRS input of the Timeslot Zero Transmitter, and facilitates the frame alignment of external circuitry. The second timing output, TZS-RZ, is a 4KHz signal which changes state once per frame, one clock period after the end of timeslot zero, and is high during sync frames to allow sync and non-sync frames to be distinguished. The third timing output, CCR, is a low going pulse, one clock period wide, occurring during 1 bit, timeslot 1 of sync frames. The final timing output, CK8, is an 8KHz signal going low at the end of bit 7 of each timeslot zero and high at the end of bit 7 in each timeslot 16.

In addition to these timing outputs, two alarm outputs are provided to indicate errors in the incoming data stream. The first of these alarms, ER, goes high for one frame following a sync frame in which a corrupted FAS was detected when the receiver is in sync. Three consecutive alarms of this type will put the receiver out of sync. The second alarm, SA, goes high to indicate that the Timeslot Zero Receiver is out of frame alignment.

In addition to the frame synchronisation process, the Timeslot Zero Receiver is also responsible for extracting the user data bits of non-sync words and the two International / CRC bits of timeslot zero. The user data bits present in bits 3 to 8 of timeslot zero of non-sync frames are extracted and output on the Q3N-Q8N parallel data outputs. The third bit of non-sync words, Q3N, is used as the remote alarm bit in 2Mbit PCM systems and a third alarm output, RAI, is derived from this bit. This alarm is a persistence checked version of Q3N

which goes high when two consecutive Q3N bits have been received high whilst the receiver is in sync. The Timeslot Zero Receiver also extracts the data present in bit 1 of timeslot zero under control of the CRC input. This input selects between CCITT CRC-4 and non-CRC-4 modes of operation. In non-CRC-4 mode, the international spare bits are extracted from bit 1 of all sync and non-sync frames and output on pins Q1S and Q1N respectively. In CRC-4 mode, these data outputs are extracted from bit 1 of frames 13 and 15 of the CCITT CRC-4 multiframe structure respectively. In order to accomplish this, two timing inputs, FRS13 and FRS15, are required in CRC-4 mode. These inputs are required to be high during bit 8 of the appropriate frame, low during bit 8 of any other non-sync frame and any state elsewhere. The timing diagrams for the Timeslot Zero Receiver are shown in Fig.4

Fig. 3 Timeslot zero transmitter timing

| к125µs<br>СLK-RZ                              |                                                                                                                                                                                    |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D d1s 0 0 1 1 0 1 1                           |                                                                                                                                                                                    |

| TSZ                                           |                                                                                                                                                                                    |

| TZS-RZ                                        |                                                                                                                                                                                    |

| СК8                                           |                                                                                                                                                                                    |

| CCR                                           |                                                                                                                                                                                    |

| Q1S                                           |                                                                                                                                                                                    |

| Q1N<br>Q3N-Q8N                                |                                                                                                                                                                                    |

| SYNC     NON-S       TSZ     FR1       TZS-RZ |                                                                                                                                                                                    |

| Q1S                                           | d1s                                                                                                                                                                                |

| M\                                            | /1443 extracting Signalling Data (CRC mode)                                                                                                                                        |

| TSZ                                           | NON     BAD     NON     BAD     NON     BAD       SYNC     SYNC     SYNC     SYNC     SYNC       WORD     WORD     WORD     WORD     WORD       Bit3 = 1     Bit3 = 1     Bit3 = 0 |

| TZS-RZ SA                                     |                                                                                                                                                                                    |

| ER                                            |                                                                                                                                                                                    |

| RAI                                           | MV1443 synchronisation process                                                                                                                                                     |

Fig. 4 Timeslot zero receiver timing

#### **PIN DESCRIPTIONS**

| Pin name                               | Pin Nu                           | mber                             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|----------------------------------------|----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DG40 HG44                              |                                  |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| GND1                                   | 1                                | 1                                | Digital Ground. 0V (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| RST                                    | 2                                | 2                                | Reset Input to Timeslot Zero Receiver. A logic high on this pin straddling a falling edge of CLK-RZ will reset the state machine of the Timeslot Zero Receiver, forcing it out of frame alignment.                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| D                                      | 3                                | 3                                | PCM Data Stream Input to Timeslot Zero Receiver. This pin is used to input the 2.048Mbit PCM data stream to the Timeslot Zero Receiver and it is this data stream which is searched for the Frame Alignment Signal. This input is latched by the falling edge of CLK-RZ.                                                                                                                                                               |  |  |  |  |  |  |

| TZS-RZ                                 | 4                                | 4                                | Timeslot Zero Sync Frame Output from Timeslot Zero Receiver. This 4KHz output changes state at the end of bit 1, timeslot 1 (Note 2) of every frame and is high during timeslot zero c sync frames.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Q1N                                    | 6                                | 8                                | International / CRC Data Bit Output of Timeslot Zero Receiver for Non-sync Frames. With CRC=0, this output latches data from bit 1, timeslot zero of non-sync frames. With CRC=1 this output latches data from bit 1, timeslot zero of frame 15 of the CRC-4 multiframe, under control of the FRS15 input. In either case this output changes state on the falling edge of CLK-RZ, half a clock period after the end of timeslot zero. |  |  |  |  |  |  |

| Q1S                                    | 7                                | 9                                | International / CRC Data Bit Output of Timeslot Zero Receiver for Sync Frames. With CRC=0, this output latches data from bit 1, timeslot zero of sync frames. With CRC=1, this output latches data from bit 1, timeslot zero of frame 13 of the CRC-4 multiframe, under control of the FRS13 input. In either case this output changes state on the falling edge of CLK-RZ, half a clock period after the end of timeslot zero.        |  |  |  |  |  |  |

| FRS                                    | 8                                | 10                               | Timeslot Zero Frame Sync Input of Timeslot Zero Transmitter. This input is required to be an 8 bit long, high going pulse masking timeslot zero. This input is latched by the falling edge of CLK-TZ although the first bit of timeslot zero is output asynchronously after the rising edge of FRS is detected.                                                                                                                        |  |  |  |  |  |  |

| Q                                      | 9                                | 11                               | Timeslot Zero Data Stream Output of Timeslot Zero Transmitter. The sync and signalling data words produced by the Timeslot Zero Transmitter are output on this pin in 8 bit bursts during timeslot zero. During any other timeslot this output is held low. Bit 1 appears immediately after the rising edges of CLK-TZ and FRS.                                                                                                        |  |  |  |  |  |  |

| CLK-TZ                                 | 10                               | 12                               | 2.048MHz Clock Input to Timeslot Zero Transmitter.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| D8N<br>D7N<br>D6N<br>D5N<br>D4N<br>D3N | 11<br>12<br>13<br>14<br>15<br>16 | 13<br>14<br>15<br>16<br>17<br>18 | User Data Bit Inputs to Timeslot Zero Transmitter. These 6 parallel data inputs are inserted<br>by the Timeslot Zero Transmitter into bits 8-3 of timeslot zero during non-sync words.<br>These inputs must be set up prior to the rising edge of CLK-TZ at the end of bit 1, timeslot<br>zero of non-sync frames.                                                                                                                     |  |  |  |  |  |  |

# PIN DESCRIPTIONS (continued)

| Pin name | Pin Number |      | Pin Description 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DG40 HC  |            | HG44 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| D1N      | 17         | 19   | International / CRC Data Bit Input to Timeslot Zero Transmitter for Non-Sync Frames.<br>The data on this pin is output on the Q pin during bit 1, timeslot zero of non-sync frames<br>and must be set up prior to the rising edge of FRS during non-sync frames.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| D1S      | 18         | 20   | International / CRC Data Bit Input to Timeslot Zero Transmitter for Sync Frames. The data on this pin is output on the Q pin during bit 1, timeslot zero of sync frames and mus be set up prior to the rising edge of FRS during sync frames.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| TZS-TZ   | 19         | 22   | Timeslot Zero Sync Frame Output from Timeslot Zero Transmitter. This 4KHz output changes state at the end of bit 1, timeslot 1 of every frame and is high during timeslot zero of sync frames.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GND2     | 20         | 23   | Digital Ground. 0V (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| TSZ      | 21         | 24   | Timeslot Zero Marker Output from Timeslot Zero Receiver. This timing output goes high for the 8 clock periods of timeslot zero and is low at all other times.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| STM      | 22         | 25   | Scan Path Test Global Mode Pin. A logic high on this pin configures the MV1443 in sca<br>test mode. For normal operation this pin should be tied low.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| CCR      | 23         | 26   | Channel Reset Timing Output from Timeslot Zero Receiver. This output pulses low for a single period during bit 1, timeslot 1 of sync frames.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| CK8      | 24         | 27   | 8KHz Clock Output from Timeslot Zero Receiver. This output goes low at the beginning of bit 8, timeslot 0 and high at the beginning of bit 8, timeslot 16.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| FRS13    | 26         | 30   | Frame 13 Marker Input to Timeslot Zero Receiver. This input is used by the Timeslot Zero Receiver operating in CRC-4 mode to reference the position of Frame 13. This input is required to be high during bit 8, Frame 13 of the CRC multiframe and low during bit 8 of all other non-sync frames.                                                                                                                                                                                                                  |  |  |  |  |  |

| FRS15    | 27         | 31   | Frame 15 Marker Input to Timeslot Zero Receiver. This input is used by the Timeslot Zero Receiver operating in CRC-4 mode to reference the position of Frame 15. This input is required to be high during bit 8, Frame 15 of the CRC multiframe and low during bit 8 of all other non-sync frames.                                                                                                                                                                                                                  |  |  |  |  |  |

| RAI      | 28         | 32   | Remote Alarm Indication Output of Timeslot Zero Receiver. This alarm output is<br>a persistence checked version of the Q3N output. When the receiver is in<br>sync this output will go high if 2 consecutive Q3N bits are received high. This output<br>changes state at the beginning of bit 1, timeslot 1 of non sync frames.<br>When the receiver is out of sync this output is forced low in the non-sync frame following<br>the last bad sync frame, and is held low until the receiver comes back in to sync. |  |  |  |  |  |

#### **PIN DESCRIPTIONS (continued)**

| Pin name Pin Number                    |                                  | mber                             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------------------------------|----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                        | DG40                             | HG44                             |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| ER                                     | 29                               | 33                               | Sync Word Error Output of Timeslot Zero Receiver. This alarm output goes high for<br>one frame immediately after detection of a bad timeslot zero frame alignment signal,<br>whilst the receiver is in sync. Three consecutive errors of this type will put the receiver<br>out of sync and the last ER pulse of this sequence will be longer than 256 periods if a<br>valid sync word is detected during the pulse. |  |  |  |  |

| SA                                     | 30                               | 34                               | Synchronisation Alarm Output from Timeslot Zero Receiver. This output is high whenever the receiver is out of sync and only changes state at the beginning of bit 1, timeslot 1 of sync frames.                                                                                                                                                                                                                      |  |  |  |  |

| CRC                                    | 31                               | 35                               | CRC-4 Mode Select Input to Timeslot Zero Receiver.<br>This input is used to control the extraction of the Q1N and Q1S data outputs from the<br>incoming PCM data stream. A logic high on this input selects CRC-4 mode of operation.                                                                                                                                                                                 |  |  |  |  |

| Q3N<br>Q4N<br>Q5N<br>Q6N<br>Q7N<br>Q8N | 32<br>33<br>34<br>35<br>36<br>37 | 36<br>37<br>38<br>39<br>40<br>41 | User Data Bit Outputs of Timeslot Zero Receiver. These 6 parallel data outputs are extracted from bits 3-8 of timeslot zero during non-sync frames. These outputs change state on the falling edge of CLK-RZ half a clock period after the end of timeslot zero.                                                                                                                                                     |  |  |  |  |

| CLK-RZ                                 | 39                               | 43                               | 2.048MHz Clock Input to Timeslot Zero Receiver.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| VDD                                    | 40                               | 44                               | Digital Supply Voltage. 5V                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

#### NOTES

1. In order to facilitate adequate supply decoupling, both digital ground pins should be connected to 0V.

2. The bits of a timeslot are numbered from 1 to 8 whereas the timeslots of a frame are numbered from 0 to 31 and the frames of a CCITT multiframe are numbered from 0 to 15.

3. All inputs except STM have 100K on-chip pull down resistors. The STM pin has neither pull-up nor pull-down resistor and should be tied to digital ground during normal operation.

# **ELECTRICAL CHARACTERISTICS**

#### **Test Conditions:**

Supply Voltage VDD = 5V  $\pm$  0.5V Ambient Temperature Tamb = -40°C to +85°C

| Characteristic            | Symbol           | Value      |     | Units    | Conditions |                             |

|---------------------------|------------------|------------|-----|----------|------------|-----------------------------|

|                           |                  | Min        | Тур | Max      |            |                             |

| Low Level Input Voltage   | V <sub>IL</sub>  | 0.0        |     | 0.8      | V          |                             |

| High Level Input Voltage  | V <sub>IH</sub>  | 2.0        |     | $V_{DD}$ | V          |                             |

| Low Level Output Voltage  | V <sub>OL</sub>  |            |     | 0.4      | V          | lsink=2mA                   |

| High Level Output Voltage | V <sub>OHT</sub> | 2.4        |     |          | V          | Isource=2mA                 |

|                           | V <sub>OHC</sub> | V—-<br>1.0 |     |          | V          | Isource=1mA                 |

| Input Leakage Current     | IIL              | -10        |     | 200      | uA         | $V_{IN}=V_{DD}$ or $V_{SS}$ |

| Input Capacitance         | C <sub>IN</sub>  |            | 5   |          | pF         | All Inputs                  |

| Output Capacitance        | C <sub>OUT</sub> |            | 5   |          | pF         | All Outputs                 |

#### **DYNAMIC CHARACTERISTICS**

| Characteristic                               | Symbol                           | Value |     |     | Units | Conditions                    |

|----------------------------------------------|----------------------------------|-------|-----|-----|-------|-------------------------------|

|                                              |                                  | Min   | Тур | Max |       |                               |

| CLOCK                                        |                                  |       |     |     |       |                               |

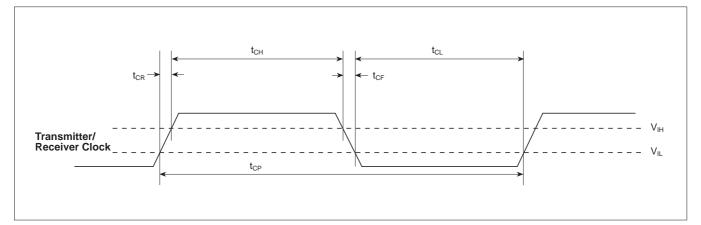

| Clock Period                                 | t <sub>CP</sub>                  | 400   |     |     | ns    | See Fig. 5                    |

| Clock Rise/Fall Time                         | $t_{\rm CR}^{}/t_{\rm CF}^{}$    |       |     | 20  | ns    | See Fig. 5                    |

| Clock High/LowTime                           | t <sub>CH</sub> /t <sub>CL</sub> | 150   |     |     | ns    | See Fig. 5                    |

| TRANSMITTER                                  |                                  |       |     |     |       |                               |

| FRS Rising Hold Time                         | t <sub>FRH</sub>                 | 50    |     |     | ns    | See Fig. 6                    |

| FRS Rising Setup Time                        | t <sub>FRS</sub>                 | 100   |     |     | ns    | See Fig. 6                    |

| FRS Falling Hold Time                        | t <sub>FFH</sub>                 | 100   |     |     | ns    | See Fig. 6                    |

| FRS Falling Setup Time                       | t <sub>FFS</sub>                 | 50    |     |     | ns    | See Fig. 6                    |

| International Data Bit<br>Setup Time         | t <sub>IDS</sub>                 | 50    |     |     | ns    | See Fig. 6                    |

| International Data Bit<br>Hold Time          | t <sub>iDH</sub>                 | 50    |     |     | ns    | See Fig. 6                    |

| User Data Setup Time                         | t <sub>uds</sub>                 | 50    |     |     | ns    | See Fig. 6                    |

| User Data Hold Time                          | t <sub>UDH</sub>                 | 50    |     |     | ns    | See Fig. 6                    |

| Q Propagation Delay<br>from FRS (bit 1, TS0) |                                  |       |     | 60  | ns    | See Fig. 6, Note 1.           |

| Q Propagation Delay<br>from CLK-RZ (bits 2-8 | t <sub>QPDC</sub>                |       |     | 60  | ns    | See Fig. 6, Note 1.           |

| TZS-TZ Propagation<br>Delay                  | t <sub>TTPD</sub>                |       |     | 60  | ns    | See Fig. 6, Note 1.           |

| RECEIVER                                     |                                  |       |     |     |       |                               |

| Data / Control Setup<br>Time                 | t <sub>DS</sub>                  | 50    |     |     | ns    | See Fig. 7, Note 2.           |

| Data / Control Hold<br>Time                  | t <sub>DH</sub>                  | 50    |     |     | ns    | See Fig. 7, Note 2.           |

| Timing / Alarm<br>Propagation Delay          | t <sub>TAPD</sub>                |       |     | 60  | ns    | See Fig. 7, Notes 1<br>and 3. |

| Data Outputs<br>Propagation Delay            | t <sub>DPD</sub>                 |       |     | 75  | ns    | See Fig. 7, Notes 1<br>and 4. |

#### NOTES

1. All output propagation delays are measured with a 50  $\!\mathrm{pF}$  load.

2. The Timeslot Zero Receiver Data / Control setup and hold time parameters,  $t_{_{DS}}$  and  $t_{_{DH}}$ , apply to the following inputs: D, RST, FRS13 and FRS15.

3. The Timeslot Zero Receiver Timing / Alarm Output propagation delay parameter applies to the following outputs: TSZ, TZS, CCR, CK8, ER, SA and RAI.

4. The Timeslot Zero Receiver Data Output propagation delay parameter applies to the following outputs: Q1S, Q1N, Q3N, Q4N, Q5N, Q6N, Q7N and Q8N.

Fig. 5 Clock Timing Parameters

Fig. 6 Timeslot Zero Transmitter Timing

Fig. 7 Timeslot Zero Receiver Timing

#### ORDERING INFORMATION

MV1443/IG/DGAS MV1443/IG/DPAS MV1443/IG/HGAS MV1443/IG/HPAS

#### HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000 Fax: (0793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O.Box 660017. 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel (408) 438 2900 Fax: (408) 438 5576

- CUSTOMER SERVICE CENTRES FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (3) 5276-5501 Fax: (3) 5276-5510 • NORTH AMERICA Integrated Circuits and Microwave Products, Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

- Hybrid Products, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061. • SOUTH EAST ASIA Singapore Tel: 2919291 Fax: 2916455

- SWEDEN Johanneshov Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon Tel: (0793) 518510 Fax : (0793) 518582

- These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1993 Publication No. DS3107 Issue No. 2.2 December 1993

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute and to ensure that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

# For more information about all Zarlink products visit our Web Site at

### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

#### TECHNICAL DOCUMENTATION - NOT FOR RESALE