## 1. OVERVIEW

The ALC simultaneously supports autonomous segmentation and reassembly of user data packets on up to 1024 virtual circuits (VCs).

User data packets are transferred to and from shared data structure memory using a high speed intelligent DMA controller with a 32 bit data bus.

Shared data structures are stored in SAR (Segmentation and Reassembly) memory which can be either dual port memory or a partition of system memory.

Packets for segmentation and packets being reassembled are stored in the SAR memory together with external data structures. These are accessed using the ALC's high speed intelligent DMA controller. non-demanding In applications, system memory can be used as SAR memory. When dual port memory is used the ALC's DMA controller has full access to the SAR memory bus. When system memory is used the DMA controller will negotiate access to a portion of the system bus bandwidth. The ALC provides the user with the facility to partition the shared data structures into dual port memory and user data into shared memory.

The DMA controller supports autonomous traffic shaping functions. Up to twelve different peak rate queues can be configured for packet segmentation. In addition each VC can be assigned to either 100%, 50% or 25% of the nominal peak rate.

In this way the user can select from one of 36 possible peak rates. Average rate

management is in accordance with either the single or double leaky bucket averaging algorithms.

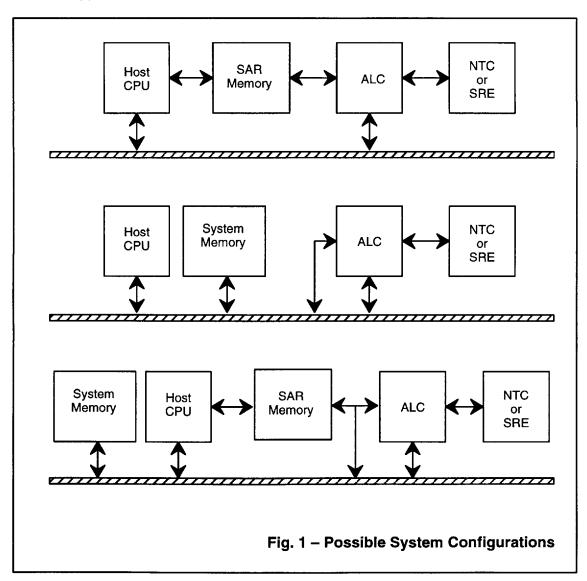

Fig. 1 shows three possible system configurations.

## **Adaptation Layer Support**

The ALC autonomously terminates the protocols involved in segmenting and reassembling data streams conforming to Adaptation Layer Types 3/4 and 5. AAL 3/4 and AAL 5 traffic can be handled simultaneously. Streaming and Message Modes as defined for AAL 3/4 and AAL5 are supported.

In Message Mode, the Convergence Sublayer payload (Service Data Unit) is considered to be the user data transmitted from or received into a single entity. A single entity being regarded as one user data buffer or linked chain of user data buffers.

In Streaming Mode, the Convergence Sublayer payload is considered to be the user data transmitted from or received into multiple entities separated in time. This allows a partial segmentation or reassembly. In Streaming Mode the chaining of buffers is not supported.

The ALC Device supports two transparent modes. In transparent payload mode the 48 byte ATM cell payload is received or transmitted transparently into or from SAR Memory. In transparent cell mode the ATM cell is received or transmitted transparently into or from SAR Memory.

## **System Configurations**

In adaptor card applications, the ALC interfaces to the Fujitsu MB86683 Network Termination Controller Device (NTC) (or compatible CCITT I.432 device) via a full duplex 8-bit wide UTOPIA compliant cell stream interface for connection to the transmission medium.

In Hub or Router applications, the ALC connects directly to the Fujitsu MB86680B Self-routing Switch Element (SRE) for autonomous routing. In this case a programmable Tag of 3 bytes must be appended to each cell.

Alternatively, it may be connected to a proprietary backplane architecture. To support this application the ALC can be configured to transmit and receive ATM cells with a four byte header minus the HEC field.

## 2. EXTERNAL INTERFACES

## 2.1 Logical Outline

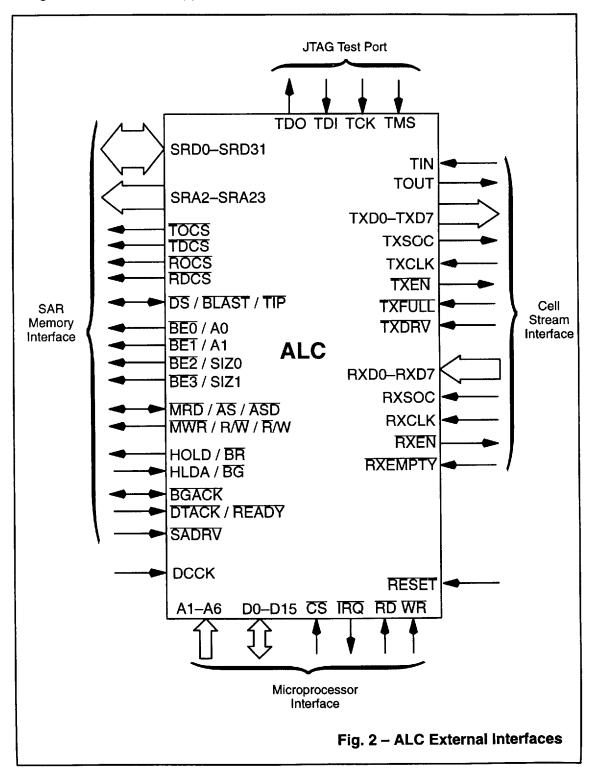

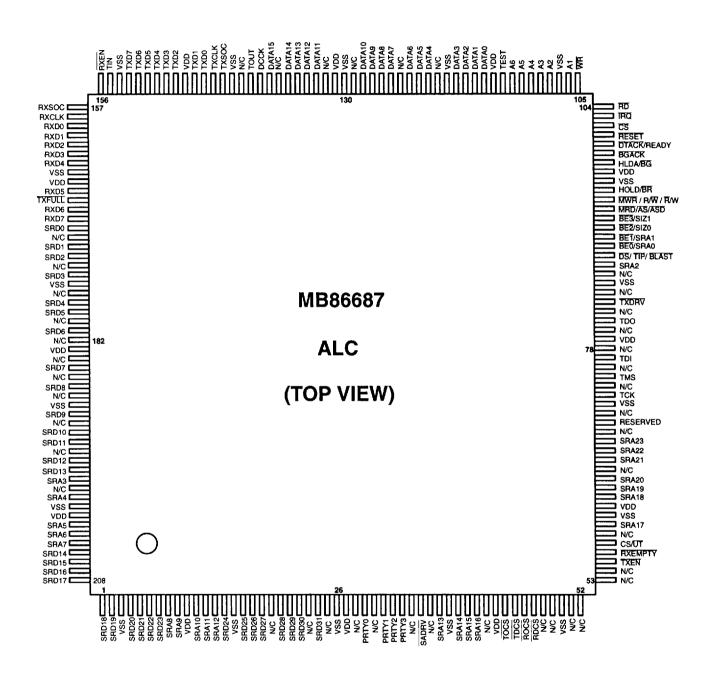

A logical view of the ALC's external pins is illustrated in Fig. 2, and a physical pin assignment is shown in Appendix F.

## 2.2 Detailed Description

## 2.2.1 SAR Memory Interface

This interface provides the ALC DMA controller with access to external dual port memory or shared access to system memory.

The interface comprises the following signals:

#### SRD0 - SRD31

Bi-directional SAR memory data bus.

#### SRA2 - SRA23

Most significant 22 bits of the SAR memory address bus. All bits are tri-state outputs.

#### SADRV

This input allows the SAR memory interface to be permanently driven.

#### BEO / SRAO

Multifunction tri-state output. Functions are as follows:

Intel mode:

BEO: Byte Enable 0 Enables data byte on SRD0 – SRD7,

Motorola mode

SRA0: SAR Memory Address bus bit 0.

#### BET / SRA1

Multifunction tri-state output. Functions are as follows:

Intel mode:

BET: Byte Enable 1 Enables data byte on SRD8 – SRD15. Motorola mode

SRA1: SAR Memory Address bus bit 1.

#### BE2 / SIZO

Multifunction tri-state output. Functions are as follows:

Intel mode:

BE2: Byte Enable 2 Enables data byte on SRD16 – SRD23,

Motorola mode SIZ0.

### BE3 / SIZ1

Multifunction tri-state output. Functions are as follows:

Intel mode:

BE3: Byte Enable 3 Enables data byte on SRD24 – SRD31,

Motorola mode SIZ1.

The coding of the SIZ signals has the following meaning:

| SIZ1 | SIZ0 | Meaning    |

|------|------|------------|

| 0    | 1    | Burst of 8 |

| 1    | 0    | Word       |

| 1    | 1    | Burst of 4 |

| 0    | 0    | Long Word  |

#### MRD / AS / ASD

Bi-function tri-state bi-directional signal. SAR memory read signal (Intel mode), SAR memory address strobe (Motorola mode). This signal is used as an input during Motorola mode bus arbitration and is the ASD signal in extended modes.

## MWR / R/W/ R/W

Multifunction tri-state output. SAR Memory write signal (Intel mode), SAR Memory read/write signal (Motorola modes) and read/write (Intel Extended mode).

### DS / BLAST / TIP

Multifunction tri-state output. Data Strobe in Motorola mode; BLAST (last in burst) in Intel extended mode; TIP (transmission in progress) in extended Motorola mode.

#### TOCS

Transmit Overhead Cycle Start output. This is asserted before any transmit cycle that is not a data cycle.

#### **TDCS**

Transmit Data Cycle Start output. This is asserted before a transmit data cycle.

### ROCS

Receive Overhead Cycle Start output. This is asserted before any receive cycle that is not a data cycle.

### **RDCS**

Receive Data Cycle Start output. This is asserted before a receive data cycle.

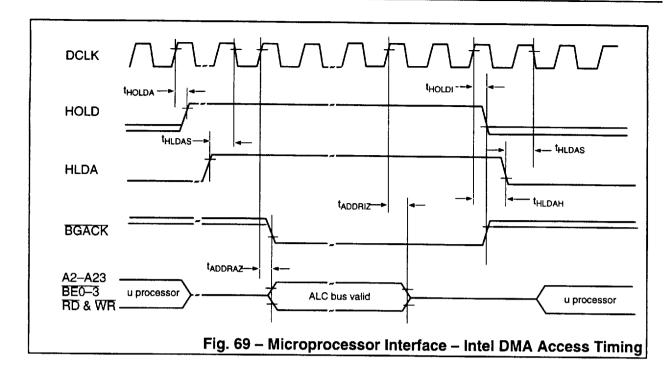

#### HOLD / BR

Tri-state Hold/Bus request output used to request bus access for ALC DMA controller.

### HLDA / BG

Hold/Bus Grant input used to pass control of the bus to the ALC DMA controller.

## **BGACK**

Bus Grant Acknowledge output indicates ALC DMA controller is assuming control of the bus.

#### READY / DTACK

Ready/Data Transfer Acknowledge input. In standard mode used to terminate DMA / DPR cycles. In FAST mode used to generate an ALC interrupt indicating memory access conflict.

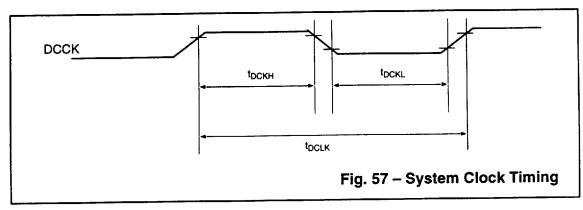

## DCCK, DMA CYCLE CLOCK

Clock input used to drive the ALC DMA cycles.

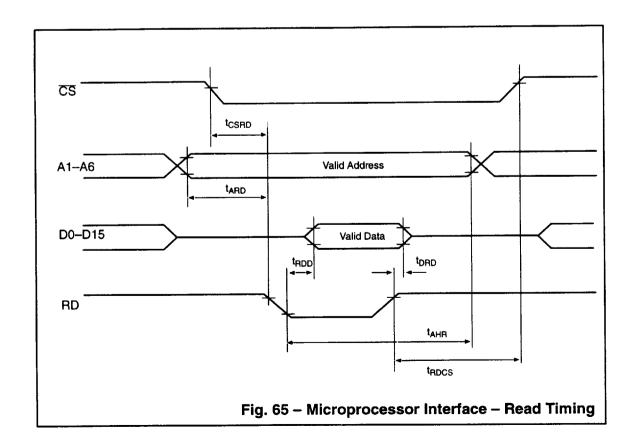

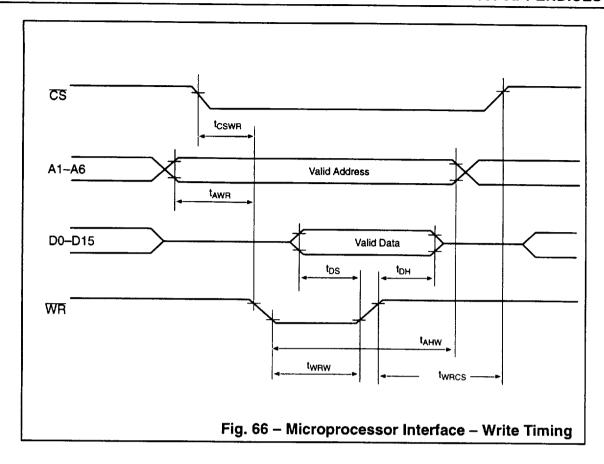

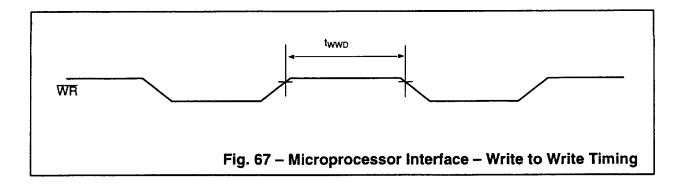

## 2.2.2 Microprocessor Interface

The microprocessor interface comprises the following signals:

#### A1-A6

Microprocessor address bus inputs.

#### DATA0-DATA15

Bi-directional microprocessor data bus signals DATA 0-15.

## CS

Microprocessor bus chip select input.

### RD

Microprocessor bus read input.

#### $\overline{\mathsf{WR}}$

Microprocessor bus write input.

## **IRQ**

Interrupt request output.

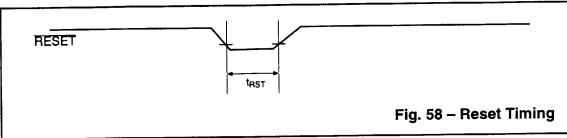

### RESET

ALC master reset input.

#### 2.2.3 Cell Stream Interface

This interface comprises the following signals:

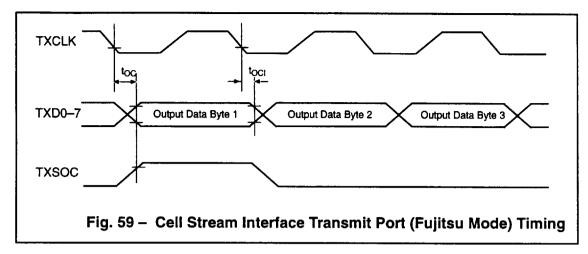

#### TXD0-TXD7

These tri-state output signals provide 8 bit parallel transmit data which is cell aligned and asynchronous. To enable daisy chaining of ALCs these signals are tri-state.

#### **TXSOC**

Transmit start of cell sync output. This tri—state output indicates that the first byte of an ATM cell or routing tag is available on the TXD0 — TXD7 data lines. The frequency of this signal depends on the cell transmission rate from the ALC. To enable daisy chaining this pin is tri-state.

#### **TXCLK**

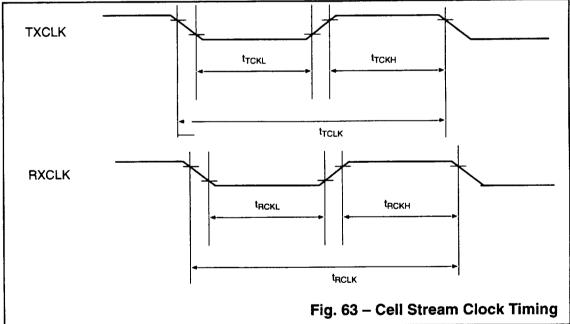

This input signal is used to clock transmit data out of the ALC. The signal can be of arbitrary frequency but should be sufficient to support the bandwidth specified by the ALC traffic shaping parameters. No phase relationship is assumed with RXCLK.

#### **TXEN**

This tri-state output signal is asserted in UTOPIA mode when the cell stream transmit is outputting valid data.

### **TXFULL**

This input is used in UTOPIA mode to halt the ALC transmit cell stream data.

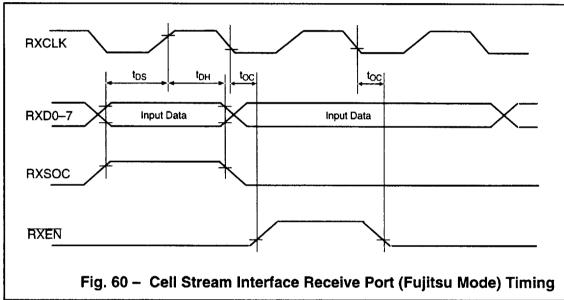

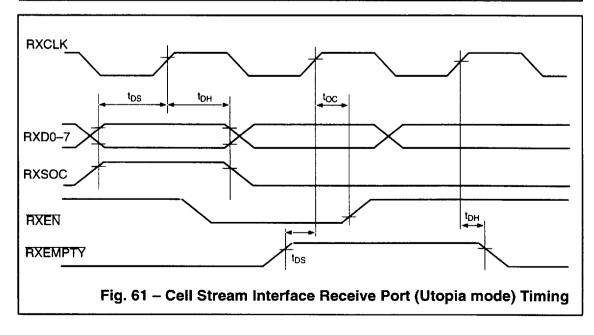

#### RXD0-RXD7

These 8 input pins provide the ALC with 8 bit parallel, cell aligned receive data.

#### **RXSOC**

Receive start of cell sync input. This signal indicates when the first byte of an ATM cell or routing tag is available on the RXD0 – RXD 7 pins.

#### **RXCLK**

This input signal is used to clock received data into the ALC. No phase relationship is assumed with TXCLK.

#### **RXEN**

This output signal is used in UTOPIA mode to control the flow of receive cells when using an external FIFO. The signal indicates that the ALC receive buffers are full.

## **RXEMPTY**

This input signal is used to control the flow of receive cells when using an external FIFO. The signal indicates that the FIFO is empty.

#### **TOUT**

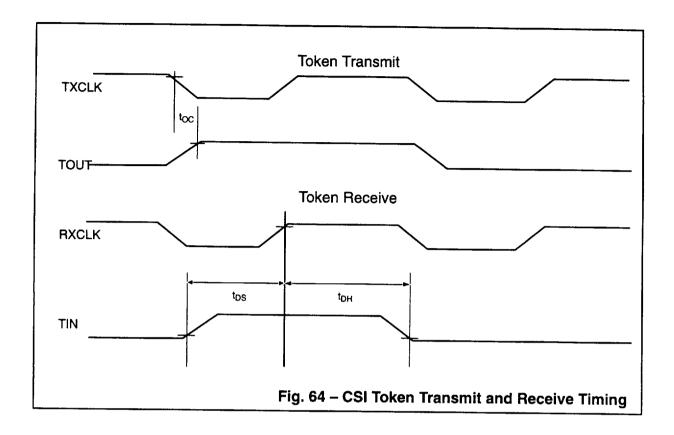

Token out output. This signal is used to enable daisy chaining. The ALC transmits a 'token' pulse on the falling edge of TXCLK to indicate that it has completed a cell transfer or has no data to transmit. The output is held low during cell transmission.

## TIN

Token In input. This input should be wired to the TOUT output of other ALC devices to form a daisy chain. If unused this pin should be pulled high.

### **TXDRV**

This input allows the ALC to permanently drive the transmit cell stream interface

## 2.2.4 JTAG Test Port

TCK

TDI

JTAG test clock input

JTAG test data input

**TMS**

**TDO**

JTAG test mode input

JTAG test data output

| SIGNAL        | PULL          | VALUE      | COMMENT                                                | $\neg$   |

|---------------|---------------|------------|--------------------------------------------------------|----------|

|               | The following | are essen  | tial for correct operation                             |          |

| BGACK         | High          | 2K7        | DMA mode                                               | $\sqcap$ |

|               | High          | 10K        | Dual Port Memory mode                                  |          |

| IRQ           | High          | 2K7        |                                                        |          |

| TXSOC         | Low           | 10K        | Only when TXDRV is not asserted                        |          |

| TXEN          | High          | 10K        | Only when TXDRV is not asserted                        |          |

| HOLD/BR       | Low           | 2K7        | Only in Intel DMA mode                                 |          |

|               | High          | 2K7        | Only in Motorola DMA mode                              |          |

| MRD/AS        | High          | 10K        | DMA mode                                               | *        |

|               | High          | 100K       | Dual Port Memory mode                                  |          |

| HLDA/BG       | High          | 10K        |                                                        |          |

| DS            | High          | 100K       |                                                        |          |

| -             | The following | are not es | sential, but are advisable                             |          |

| TXD0-7        | High/Low      | 100K       | Only when TXDRV is not asserted                        |          |

| SRD0-31       | High          | 100K       | Only when SADRV is not asserted                        |          |

| The following |               |            | ata bus can be guaranteed not to float<br>2v and 0.8v. |          |

| MWR/R/W       | High          | 100K       |                                                        | *        |

| BE0/A0        | High          | 100K       |                                                        | *        |

| BE1/A1        | High          | 100K       |                                                        | *        |

| BE2/SIZ0      | High          | 100K       |                                                        | *        |

| BE3/SIZ1      | High          | 100K       |                                                        | *        |

| A2-21         | High          | 100K       |                                                        | *        |

Note: \* – These signals are continuously driven when Dual Port Ram mode is selected or SADRV is asserted.

Table 1 - Pull Values

## 3. FUNCTIONAL DESCRIPTION

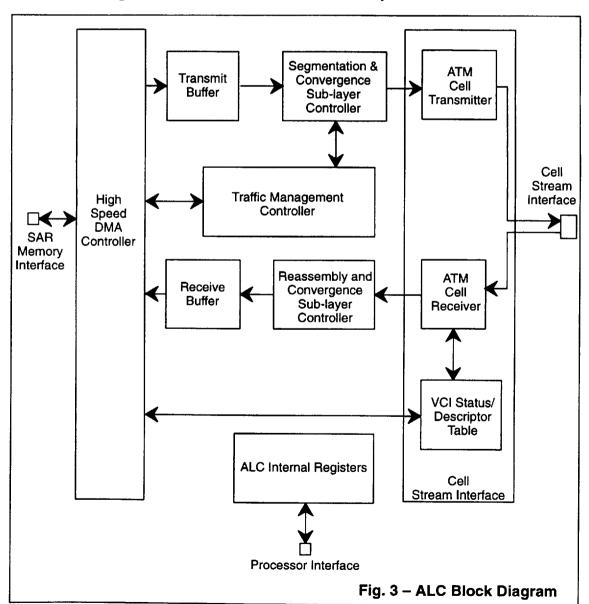

This section describes the behaviour of each major functional block within the ALC, as illustrated in Fig. 3. The descriptions in this section are from a user's perspective and are intended to give a detailed description of device functionality and modes of operation. The ALC comprises the following major components:

- High Speed DMA Controller,

- Traffic Management Controller,

- Transmit and Receive Buffers,

- Segmentation and Convergence Sub-layer Controller,

- Reassembly and Convergence Sub-layer Controller,

- Cell Stream Interface,

- Microprocessor Interface,

- Segmentation and Reassembly Memory Interface.

Edition 2.0 MB86687

## 3.1 DMA Controller and SAR Memory Interface

#### 3.1.1 General

The ALC contains an intelligent DMA Controller to manage the segmentation and reassembly of user data packets using the minimum of host processor intervention. Communication with the host processor is mainly through shared data structures in either dual port or system memory.

The system implications of a dual port or system memory approach are largely performance related.

#### 3.1.2 Shared Data Structures

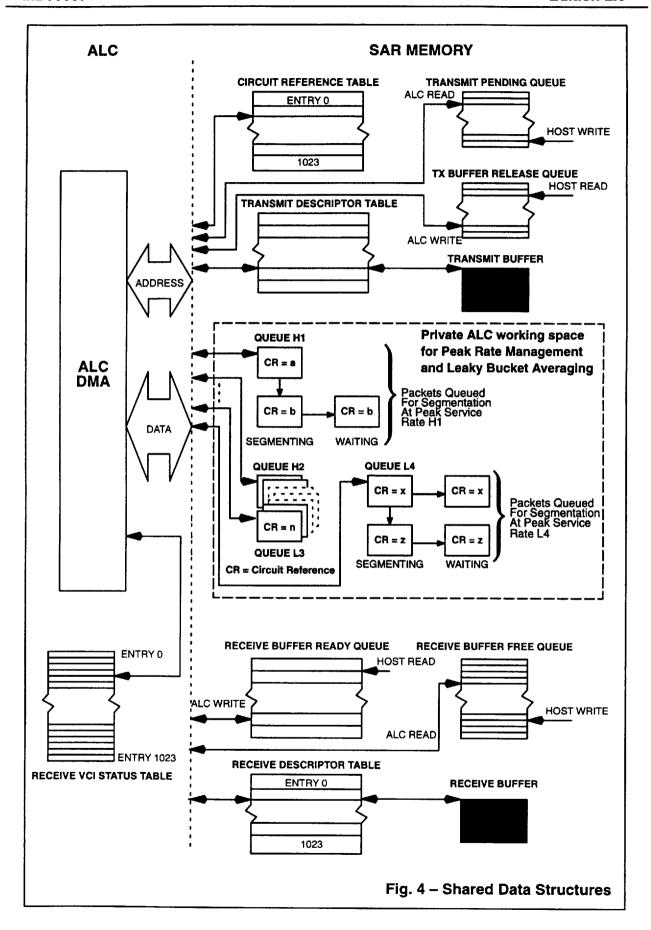

The shared data structures used to the control segmentation and reassembly of user data are shown in Fig. 4 on page 10. The transmit side is controlled via the Transmit Pending Queue, the Transmit Descriptor Table, the Circuit Reference Table and the Transmit Buffer Release Queue. The ALC uses reserved fields in the Transmit Descriptor to compose peak rate queues for segmentation at the specified peak rate and for leaky bucket averaging. The host can programme up to 12 peak rates for the ALC.

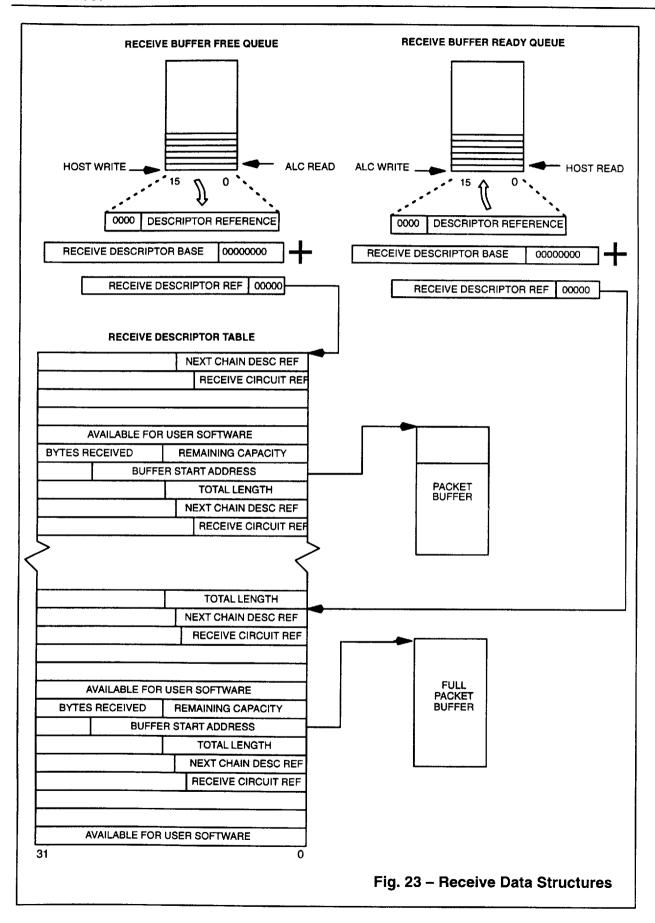

The receive side is controlled by the Receive Buffer Free Queue, the Receive Descriptor Table and the Receive Buffer Ready Queue. In addition the DMA Controller uses an internal RAM table, the Receive Status / Descriptor Table to store receive VCI status and descriptor identifiers. The purpose of each of these tables is described below.

#### 3.1.3 Transmit Data Structures

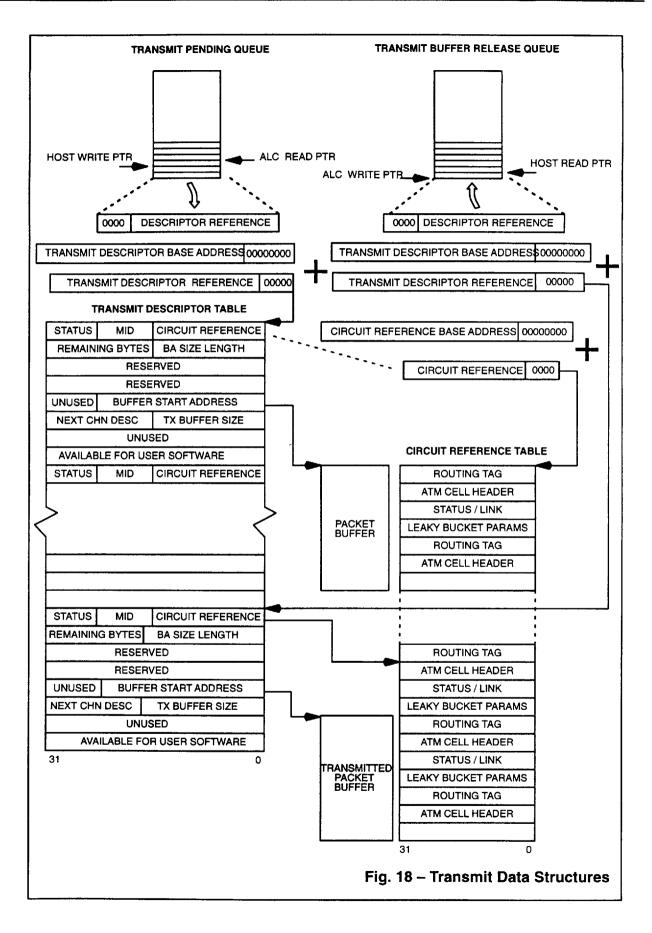

The host writes commands to the Transmit Pending Queue to instruct the ALC to queue a data packet for segmentation. The packet can be queued for transmission on one of 12 peak rate queues. Each Transmit Pending Queue entry contains a pointer to a Transmit Descriptor in the Transmit Descriptor Table.

The Transmit Descriptor Table is composed of up to 4096 descriptors. Each descriptor contains a pointer to data for segmentation. The reserved fields in the Transmit Descriptor are used by the ALC to construct queues of transmit packets for each selected peak rate. The Transmit Descriptor also contains a pointer to an entry in the Circuit Reference Table (CRT).

The CRT is composed of up to 1024 entries, one entry for each active Virtual Circuit. Each entry contains fields for the ATM cell header, an optional routing tag, and the leaky bucket parameters for the virtual circuit. The ALC reads the cell header and the leaky bucket parameters from the CRT each time a cell is segmented from a transmit buffer.

Management of the Peak Rate is handled segmentation queues autonomously by the ALC. The only host intervention required is on a per packet basis. To gueue a packet the host constructs the relevant descriptor and writes the pointer to the descriptor into the Transmit Pending Queue. Transmit descriptors are recovered by the host by reading the Transmit Buffer Release Queue.

Edition 2.0 MB86687

After a packet has been transmitted, the ALC will return the Transmit Descriptor used to the host via the Transmit Buffer Release Queue. Each entry in this queue contains a pointer to the relevant descriptor in the Transmit Descriptor Table.

## 3.1.4 Receive Data Structures

At the start of reassembly for each new packet the ALC finds a new Receive Descriptor (RD) by reading the Receive Buffer Free Queue. Each entry contains a pointer to a RD in the Receive Descriptor Table.

The Receive Descriptor Table is composed of up to 4096 RDs. Each RD contains a pointer to a receive buffer. The RD also contains fields to support receive buffer chaining and the received VCI or MID fields. A reserved field in the RD is used by the ALC to support a receive buffer ageing timeout.

After reception is complete, the ALC passes the receive descriptor to the host using the Receive Buffer Ready Queue. Each entry in the queue contains a pointer to the appropriate RD and the status of the receive buffer.

A more detailed description of the shared data structures is provided in Section 4, Developers Notes, of this datasheet.

## 3.1.5 Packet Segmentation

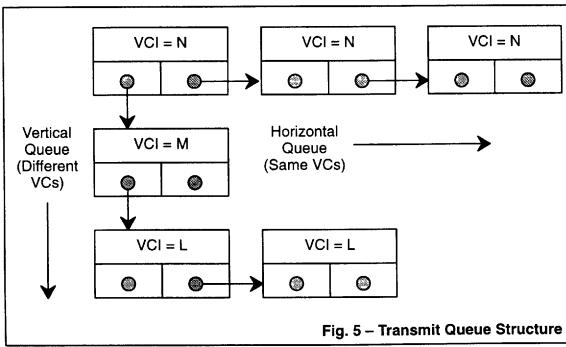

The DMA Controller is responsible for linking transmit descriptors into one of the 12 service rate queues. The queues are composed of a linked list of TDs. The structure of each of the service rate queues is shown in Fig. 5.

When the ALC reads a transmit packet command from the Transmit Pending Queue, it links the packet into the service rate queue specified in the appropriate Circuit Reference Table entry (see Fig. 20 on page 36).

Packets with the same circuit reference, ie same VPI/VCI or MID are queued horizontally. Packets with different circuit references for transmission on the same service rate queue are queued vertically. Horizontally queued packets will be serviced when the packet at the front of the queue is completed.

Each service rate queue is serviced vertically at the specified peak rate under the control of the Traffic Management Controller. A queue entry has been serviced when a complete SAR-PDU payload of either 44 or 48 bytes has been read from the packet. The queue has been serviced when each queue entry linked vertically has been serviced.

## **Message Mode Operation**

In Message Mode, the user data buffer associated with a Transmit Descriptor will contain the full CS-PDU payload to which the CS-PDU header and trailer will be added to terminate the protocol.

Alternatively, the CS-PDU payload may be spread across several user data buffers when the host passes a chain of TDs to the ALC. The CS-PDU header will be added to the first user data buffer in the chain. The ALC will work through the chain until the CHAIN END bit is cleared ( $\overline{\text{CE}} = 0$ ) and then the CS-PDU trailer will be added.

## **Streaming Mode Operation**

In Streaming Mode, a partial segmentation can be accomplished. This allows the user data unit to be partially received into SAR memory and for segmentation to commence before the whole unit is received.

Table 2 describes single buffer, chaining and streaming modes for the ALC. It should be noted that the transmit and receive sides work independently.

Transmit operation is controlled by the Transmit Descriptor on a packet by packet basis. The whole receive side is controlled by Control Register17 (see Fig. 40 in Appendix B.).

## 3.1.6 Packet Reassembly

The DMA Controller maintains the status of each receive connection using the internal Receive Descriptor / Status table. This table is accessible to the host for initialisation purposes, diagnostics and support for scatter/gather mode.

The host must activate each connection using the host access registers 57 to 59 (Fig. 55 & Fig. 56). The AAL type and ACT bits must be initialised to the required value.

### **Message Mode Operation**

In Message Mode, the user data buffer associated with a Receive Descriptor will contain the full reassembled CS-PDU payload.

If the size of this payload exceeds the buffer size the buffer will be returned to the host with a buffer overflow indication.

Alternatively, the CS-PDU payload may be spread across several user data buffers when the host programs the ALC for receive buffer chaining operation. The head of the chain of buffers will be passed back to the host when the end of message is received.

## **Streaming Mode Operation (PR)**

The size of the CS-PDU payload may be much greater than the size of one receive data buffer. In addition, the memory resource as a whole may be limited or the user may require that sections of the CS-PDU be forwarded to the host as soon as they fill each buffer.

This partial reassembly is accomplished by programming the ALC for streaming mode operation.

Buffer Chaining is not possible when the streaming mode register bit has been programmed.

|                             |     | MESSAG                                              | STREAMING MODE                                                             |                                                           |

|-----------------------------|-----|-----------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------|

| OPERATION                   | DIR | SINGLE BUFFER                                       |                                                                            |                                                           |

| Queue<br>Packet             | Tx  | M=0, CS=0, CE=0<br>Whole packet in<br>single buffer | M=0 CS 1st buffer=0 CS other buffers=1 CE last buffer=0 CE other buffers=1 | M=1, CS=0 in first<br>buffer<br>CE=0                      |

| Add buffers<br>via TPQ<br>* | Тх  | NA                                                  | NA                                                                         | M=1 in extra buffers<br>M=0 in last buffer<br>CE=0        |

| Release<br>buffer           | Тх  | When packet Tx complete                             | Released on a buffer<br>by buffer basis<br>(-> TRBQ)                       | Released on a buffer<br>by buffer basis<br>(-> TRBQ)      |

| Start<br>Re-assembly        | Rx  | BCHAIN=O,<br>SMODE=O<br>Get next BFQ entry          | BCHAIN=1,<br>SMODE=0<br>Get next BFQ entry                                 | BCHAIN=O,<br>SMODE=1<br>Get next BFQ entry                |

| Buffer full                 | Rx  | Error buffer overflow                               | Get next BFQ entry<br>Link buffers                                         | Get next BFQ entry<br>Release buffer to<br>host (-> RBRQ) |

| Packet<br>complete          | Rx  | Release buffer to host                              | Release first buffer<br>to host (-> RBRQ)<br>**                            | Release buffer to<br>host (-> RBRQ)                       |

#### Notes:

- \* In Transmit Streaming mode the host must queue all current packet buffers on any given circuit before starting a new packet.

- \*\* In Receive Chaining the host will be given the descriptor reference of the first buffer in the chain. The host must follow the chain until the condition V=0 is set in the descriptor.

Table 2 – Single Buffer, Chaining and Streaming Modes

## **Buffer Ageing Support**

Buffer Ageing support is programmed by setting bit D12 (BAS) in Register 17. If set, upon reassembling the first cell of a packet, the ALC stamps a time base in the RD.

On reassembly of further cells for the same packet, the ALC compares the time elapsed against the value programmed in Register 52 – Receive Buffer Timeout Counter Register.

If the difference is greater than the value in this register, the RD is returned to the Buffer Ready Queue with a code '1100' indicating Buffer Timed Out - Reassembly Aborted. The rest of the packet will be discarded by the ALC

For a greater time range, Register 51 – Receive Buffer Timeout Counter Period Register – can be programmed. This scales the DCCK used to increment the time base counter. For example, a DCCK at 25MHz provides a time range up to 170 seconds.

Buffer Ageing Support is only available in Message Non-Chaining mode.

## **Maximum Packet Length**

At the start of cell reassembly, the ALC compares the value of Bytes Received accumulated in the RD with the value programmed in Register 54 – Maximum Received Packet length Register.

If the register value is exceeded, the ALC writes out the RD to the Buffer Ready Queue with a code '1001' indicating Receive Maximum Length Exceeded.

For Message Chaining mode, the ALC compares the accumulated value of Bytes Received to date across the chain at the moment of adding a further RD to the chain.

Maximum Packet Length checking is not supported in Streaming mode

Edition 2.0 MB86687

# 3.2 Traffic Management Controller

The Traffic Management Controller is responsible for the following functions:

- Initiate periodic packet segmentation from one of the 12 Peak Rate Queues at intervals specified in the Queue Service Rate registers. The queues are grouped into three priority classes: high, medium and low, with 4 queues in each priority class.

- Manage total ALC peak transmission rate. If the total peak transmission rate exceeds a specified threshold, the traffic management controller will service the queues according to their priority until the total peak rate falls below the threshold. This feature can be used to ensure that the ALC will not exceed the negotiated quality of service for the overall link connection.

- Manage average rate shaping of transmit traffic on a per virtual circuit basis using the leaky bucket The algorithm. leaky bucket parameters for this are supplied from Circuit Reference Table referenced in the Transmit Descriptor.

- Manage average rate shaping on the total ALC transmission according to the leaky bucket algorithm. The leaky bucket parameters for this averaging are determined by the ALC Peak Cell Transmission and ALC Average Cell Transmission registers. This feature is also used to ensure that the ALC will not exceed the quality of service for the overall connection.

# 3.2.1 Peak Rate Queue Service Requests

The ALC peak rate queue service control logic is responsible for requesting the transmission of cells queued to the peak rate queues on a per virtual circuit basis. Twelve programmable counters are used to specify the peak transmission rate for each queue.

The twelve counter values are programmed using the Queue Service Rate Registers and enabled using the Queue Enable Registers. The counter is clock TXCLK (for TXCLK period, see Appendix NO TAG) which can be pre-scaled to increase it's dynamic range. The peak service rate value is used to determine the frequency of access to the respective peak rate queue. Each time the queue is accessed one cell may be transmitted for each queued entry (one per VC) if a leaky bucket token is available for that queue entry.

Each Circuit Reference Table contains a sub rate select field which can be used to further reduce the peak cell transmission rate to 50% or 25% of the nominal peak rate specified in the Queue Service Rate Register. This gives a total available range of 32 effective peak transmission rates for entries of each peak rate queue.

#### 3.2.2 Total ALC Peak Rate Control

The ALC contains link capacity control logic which is used to ensure that the overall ALC link transmission rate does not exceed a pre-programmed value as specified in the ALC Peak Cell Transmission Rate register.

If the overall required transmission rate exceeds this programmed value, the link capacity controller will mask the lower priority queues. This will cause cell transmission to cease on the low priority queues until the overall peak rate falls below the programmed total ALC value. Note that the queues are masked in the following priority: All four L queues followed by all four M queues.

# 3.2.3 Per VC Leaky Bucket Traffic Shaping

The leaky bucket algorithm is used to shape the transmit data characteristics on a per virtual circuit basis by controlling the average rate of cell transmission and the length of each burst of cells generated. The leaky bucket parameters are determined by the values in the Circuit Reference Table for each active VC. (See section NO TAG, Transmit Data Structures).

The parameters relevant to leaky bucket management are the user programmable parameters, Bucket Capacity M and the Bucket Utilization U.

The bucket capacity is used to calculate the maximum sustained burst of cells at the specified peak rate. The average rate of emptying the bucket is derived from the utilisation. The utilisation is expressed as a fraction of the peak rate. See section 4 on ALC configuration and control for full details.

Two modes of operation are supported: single leaky bucket mode and double leaky bucket mode.

In single leaky bucket mode, cells are transmitted in an initial burst as defined by M at the specified peak rate. The burst length may exceed the bucket capacity since tokens are added to the bucket at the same time as tokens are removed. Subsequent cells are transmitted at the average rate as tokens are added to the bucket.

In double leaky bucket mode, cell transmission will only occur in bursts at the peak rate when the bucket associated with that VC is full of tokens.

# 3.2.4 Total ALC Leaky Bucket Traffic Shaping

In addition to the traffic shaping applied to the traffic transmitted from each virtual circuit the ALC can manage both the peak and average transmission rate on the total ALC output traffic.

A total ALC Leaky bucket size is defined in the ALC Leaky Bucket Capacity Register. This capacity value is used in conjunction with the leaky bucket utilization to limit the ALC output burst length. The total ALC utilisation value is derived from the ALC Peak Cell Rate and ALC Average Cell Rate Register contents.

# 3.3 Segmentation and Convergence Sub-layer Controller

This block is responsible for managing the transmission of cells according to the specified Adaptation Layer protocol: AAL3/4 or AAL5.

## 3.3.1 SAR Sub-layer functions

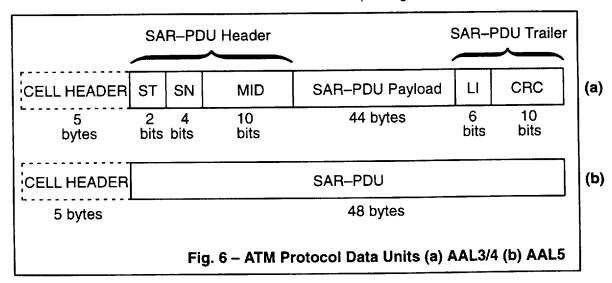

Fig. 6 shows the format of SAR Protocol Data Units (SAR-PDU) for AAL types 3/4 and 5. The following protocol actions are performed on each SAR-PDU for AAL 3/4:

- Preservation of SAR service data unit integrity through generation of the segment type field,

- Error Protection through Sequence Number and CRC generation,

- Multiplexing/Demultiplexing using the Multiplexing ID,

- Support of the Abort function.

The fields of AAL Type 3/4 are detailed in the following text.

## ST, Segment Type

The first SAR-FDU generated from a user data packet carries the Beginning of Message (BOM) code 10. Subsequent SAR-PDUs carries the (Continuation Of Message) COM code 00.

The final SAR-PDU carries the End of Message (EOM) code 01. SAR-PDUs which carry entire SAR-SDUs such as those defined for signalling carry the Single Segment Message (SSM) code 11.

## SN, Sequence Number

The four bits of this field are used for modulo 16 numbering of each SAR-PDU. The Sequence Number is set to zero at the start of each SAR-SDU.

## MID, Multiplexing Identification

This field is used for multiplexing multiple CS-PDU (Convergence Sub-layer Protocol Data Units) connections on a single ATM layer connection. When MID mode is selected, this field carries the MID specified in the Circuit Reference Table. The MID field is set to zero when multiplexing is not used.

## LI, Length Indicator

This field indicates the number of bytes contained in the SAR-PDU. The SAR-SDU bytes are left justified within the SAR-PDU payload field and remaining bytes will be set to 0.

## **CRC, Cyclic Redundancy Check**

This field contains the 10 bit CRC code. It is calculated (as defined in CCITT I.363 for AAL3/4) over the SAR-PDU including header, trailer, payload and length indication.

# 3.3.2 Convergence Sub-layer Functions

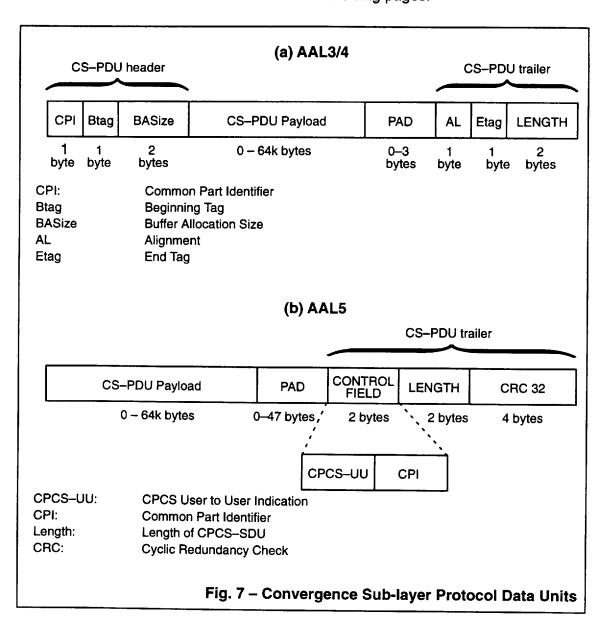

Fig. 7, below, shows how the user data is formatted in the convergence sub-layer before segmentation. The ALC maintains internal tables to manage AAL3/4 sequence numbers and AAL5 CRC results.

The fields of the CS-PDU header and trailer are listed and described on the following pages.

Edition 2.0 MB86687

### **AAL 3/4 HEADER AND TRAILER**

### **CPI, Common Part Identifier**

This field is coded to all zeros to indicate that the values in BASize and Length Fields are measured as unit multiples of bytes.

## BTAG, ETAG, Beginning & End Tags

These Fields are given the same modulo 256 value for each CS-PDU and incremented on successive CS-PDUs. The receiver will check that they are the same value on a CS-PDU to CS-PDU basis but will not check for incrementation over successive CS-PDUs.

### **BASize. Buffer Allocation Size**

This value will be the size of the CS-PDU payload when Message Mode Service is being run. In Streaming Mode this value may be greater than or equal to the CS-PDU payload size. Its purpose is to inform the receiving entity of the buffering required to accommodate the transmitted data.

### AL, Alignment

No information is conveyed by this field. It merely provides 32 bit alignment in the CS-PDU trailer. The Pad field has the effect of making the CS-PDU an integral multiple of 4 bytes.

#### Length

Length of CS-PDU payload.

### PAD, Padding Field

This field complements the CPCS-PDU to an integral multiple of 4 bytes and conveys no information.

#### **AAL 5 TRAILER**

For AAL 5 the CS-PDU has no header. The trailer is derived from the data structure and the 32 bit CRC stored in the convergence sub-layer table. The fields of the CS-PDU trailer are listed below.

## PAD, Padding Field

The purpose of the PAD bytes is to align the CS-PDU trailer into the last 8 bytes of a SAR-PDU. If this calculation results in the transmission of an extra cell it is not transmitted back to back with the previous SAR-PDU, as this would compromise the transmission rate and the Traffic Management Controller parameters.

#### Control Field

The Control Field comprises 2 fields shown in Fig. 7. These fields are:

- CPCS-UU

- This field is used to transparently transfer CPCS user to user information.

- CPI

This field is used to align the CPCS\_PDU to 64 bits and should be coded as zero.

#### Lenath

Length of CS-PDU payload.

### CRC. Cyclic Redundancy Check

The CRC field is filled with the value of a CRC calculation (as defined in CCITT I.363 for AAL 5) which is performed over the entire contents of the CS-PDU. This includes the payload, the PAD field, and the first four bytes of the trailer. The initial CRC remainder is preset to all ones before generation and checking.

## 3.3.3 Error Recovery & Notification

The ALC provides provisions for sending SAR-U-ABORT ATM Cells in streaming mode in accordance with the selected protocol. In accordance with AAL5 protocol the ABORT SAR-PDU is defined as SDU=1, LENGTH FIELD coded to zero and CRC32 correct. In accordance with AAL3/4 protocol the ABORT SAR-PDU is defined by ST=EOM, payload coded to zero, and LI = 63. The CRC-10 and MID field must be valid.

## 3.3.4 Transparent Modes

## **Transparent Cell Mode**

In this mode the host provides cells of 52 bytes (4 header and 48 data) in a transmit descriptor to the transmit pending queue. The transmit side generates and includes the HEC byte (if mode register 17 bit D9 = 0) and transmits the resulting 53 byte cell with an optional CRC10 included otherwise no further protocol carried out.

On receiving a transparent cell the receive side checks and removes the HEC byte before loading the remaining 52 bytes into the internal receive buffer. The receive side DMA then obtains a descriptor from the buffer free queue, writes all 52 bytes into the buffer and then writes out the descriptor to the buffer ready queue.

Note that the only updated field within the receive descriptor is the VCI field (the bytes received is not updated as it is always 52).

## **Transparent Payload Mode**

In this mode the host provides a multiple of 48 bytes of cell payload data within a single transmit descriptor to the transmit pending queue. The header information is obtained from the Circuit reference table, a HEC byte is generated (if mode register 17, bit 9 = 0) and the cell is transmitted. As with transparent cell mode, apart from including an optional CRC10, no further protocol is performed.

The receive operation is also similar to transparent cell mode but with only the 48 payload bytes being transferred by DMA to SAR memory. The CRC 10 can be checked if the cell is detected to be an OAM or Resource management cell.

# 3.4 Reassembly and Convergence Sub-layer Controller

This block is responsible for managing the reception of cells according to the specified Adaptation Layer protocol: AAL3/4 or AAL5.

The following adaptation layer functions are performed on a SAR-PDU basis:

- Preservation of SAR service data unit.

Checking the Segment Type Field,

- Error Detection and Handling.

CRC and Sequence Number Integrity Checking,

- Multiplexing / Demultiplexing using the MID field,

- Support of the Abort Function.

The following adaptation layer functions are performed on a CS-PDU basis:

- Detection of BTag, ETag fields,

- Detection of Incorrect Length Field,

- Detection of Alignment errors,

- Detection of errors using CRC 32 calculation.

## 3.5 Cell Stream Interface

The Cell Stream Interface will transmit and receive an asynchronous stream of ATM cells. Cells will be transmitted and received in 8-bit parallel form with separate synchronisation signals used to identify the start of a cell.

The ALC cell stream interface may be required to operate in one of two environments either in a Switch Device or a Termination Device.

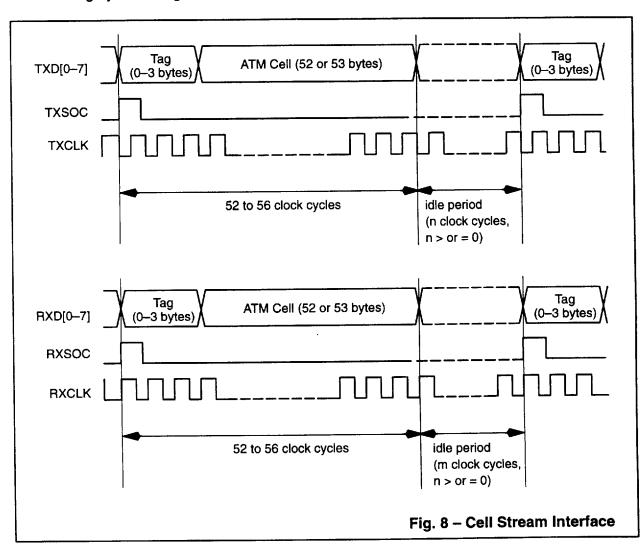

# 3.5.1 Termination Device Operation

In termination device operation the ALC is intended to connect to the Fujitsu MB86683 Network Termination Controller or equivalent device for physical media interfacing. Cells are transmitted and received header to trailer or with an idle period between each cell, see Fig. 8.

The idle period may be of any number of clock cycles including zero. There is no relationship between the transmit and receive sync pulses.

## 3.5.2 Switch Device Operation

In switch device operation, for example in hub and router applications, the ALC can be connected directly to an ATM switch fabric port such as the Fujitsu MB86680B Self-routing ATM Switch Element, or to a proprietary backplane structure.

In this environment the ALC will append a programmable routing Tag of up to 3 bytes to the start of each cell. In the receive direction the Tag is removed before protocol processing of the cell commences. In addition, the HEC field can optionally be omitted resulting in a 52 byte cell. Switch Device timing is also shown in Fig. 8.

### 3.5.3 Cell Stream and UTOPIA

The Fujitsu Cell Stream mode has been superceded by the UTOPIA specification from the ATM Forum, but is still supported for backward compatibilty. The mode selection is performed by tying the CS/UT pin high or low as required. By default, Fujitsu cell stream is selected by internal pull—up resistor.

## 3.5.4 Utopia Flow Control

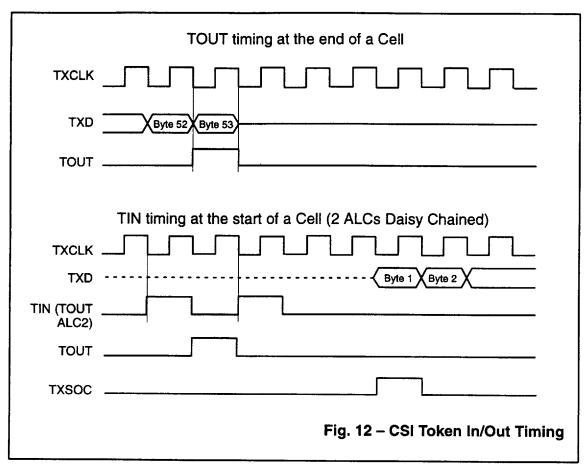

Forward and backward byte-level flow control is supported in both directions. The forward flow control signal indicates the validity of the current data. The backward flow control signal indicates whether data will be accepted in a particular cycle. Neither flow control signal is directly qualified by the other: they can change state independently. Unused flow control inputs should be tied off to their active levels. All signals are transmitted and sampled on the rising edge of the clock.

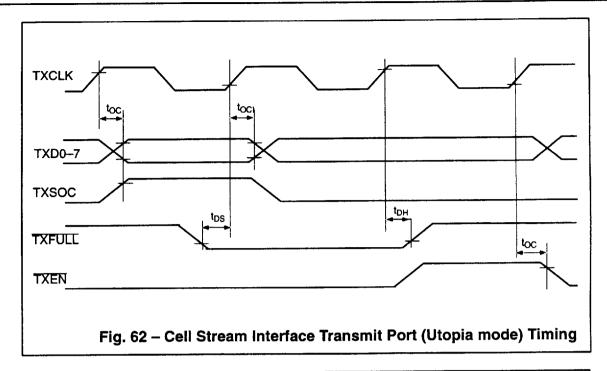

Timings for UTOPIA are illustrated in Fig. 10 and Fig. 11. Note that all of the flow control signals can change state independently.

## 3.5.5 Cell Stream Flow Control

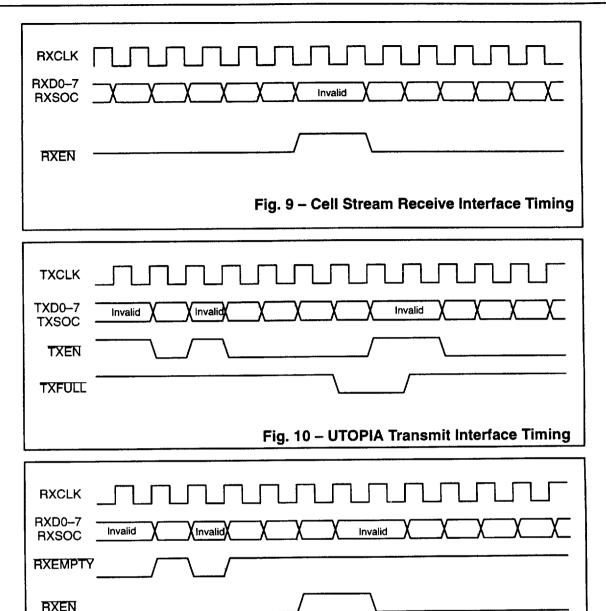

In Cell Stream mode the ALC will provide an indication that its receive buffer is full by using the RXEN output signal as shown in Fig. 9. The other flow control signals are not supported in Cell Stream mode.

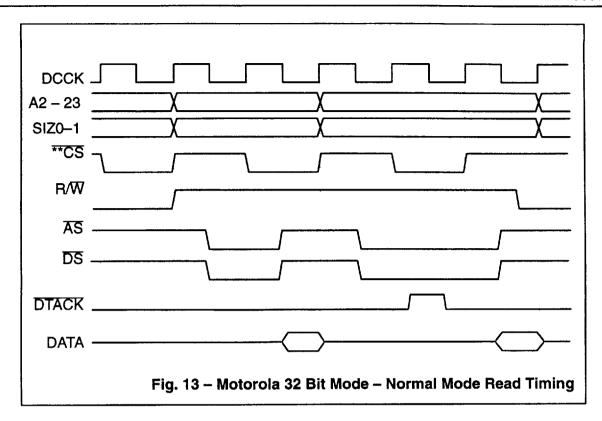

# 3.5.6 Transmit Multiplex Operations

A token passing mechanism is used when more than one ALC share the same cell stream interface. In this case the ALC should be wired in a daisy chain configuration using the TIN (Token In) and TOUT (Token Out). This mechanism is illustrated in Fig. 12.

TIN should be connected to the TOUT output of an ALC higher up the daisy chain. When the TIN input is inactive (low), the ALC stops transmitting data and places its TXD and TSN pins in high impedance.

Fig. 11 - UTOPIA Receive Interface Timing

The ALC will transmit a Token pulse, on TOUT, on the falling edge of TXCLK to indicate that it has completed a cell transfer or that it has no data to transmit.

Note that if one ALC is able to transmit cells continuously on this interface (ie. no gaps between cells) TOUT will only pulse at the end of a cell if TIN is inactive one clock period before the last byte in the cell.

## 3.5.7 TXDRV (TX cell stream Drive):

Earlier ALC devices needed pull down resistors on the TX cell stream interface because the selection of Cell Stream Daisy Chaining was controlled by a register. Using the TXDRV signal on MB86687 allows these resistors to be omitted.

This mode is selected by tying the TXDRV pin low. By default, it is deselected by an internal pull-up resistor and the register controls the operation

# 3.5.8 Receive Circuit Reference and VPI/VCI Filter Mechanism

The ALC constructs a 10 bit receive circuit value depending on the setting of the RID bit in register 17.

## RID 0

Receive Circuit Reference value is equal to VPB least significant bits of the VPI field concatenated with (10–VPB) least significant bits of the VCI field where VPB is the value of VPI bits to be used in the receive address mapping, specified by bits VPB2, VPB1 and VPB0 in register 16.

AF17-AF14 matched with VPI11-VPI8 for NNI mode

AF17-AF14 are not considered for UNI mode.

AF13—AF0 matched with unused VPI bits concatenated with unused VCI bits.

For VPI filter inactive (VPF=0) the mask bits for the unused VPI bits must be cleared to zero.

#### RID<sub>1</sub>

Receive Circuit Reference is equal to the value in the MID field (AAL3/4 only).

The Receive Circuit Reference value should be used during programming register 59 when enabling receive channels. When re-assembling a packet, this value is loaded into the receive circuit reference field in the receive descriptor.

The ALC performs filtering on the VPI and VCI bits not used for the receive circuit value. Bits AF17 and AF16 in register 16 together with bits AF15 – AF0 in register 56 make up the mask value to be used to filter incoming cells. Programming of the mask bits AF17–AF0 is dependent on the settings of the UNSEL bit in register 16 and the VPF bit in register 17.

## 3.6 Microprocessor Interface

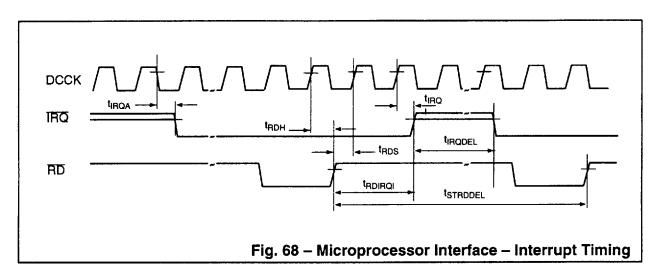

The Microprocessor Interface is responsible for supporting the following functions:

- Providing Host Processor access to all programmable ALC registers,

- Providing the Host Processor initialisation / test access to the Receive Status / Descriptor Tables,

- Managing the ALCs interrupt mechanism.

## 3.6.1 Interrupt Controller

The ALC will indicate certain abnormal conditions using the Interrupt signal. The cause of an interrupt is provided in the Interrupt status register.

Each interrupt condition can be individually masked to prevent external interrupt signal generation. A full description of each interrupt source is given in Appendix B., Fig. 42 and Fig. 43 as part of the interrupt status register description.

# 3.7 Segmentation and Reassembly Memory Interface

#### 3.7.1 Features

The SAR interface is responsible for accessing queues, tables and data stored in either dedicated dual port memory or within the host system memory. The SAR interface can support the following features:

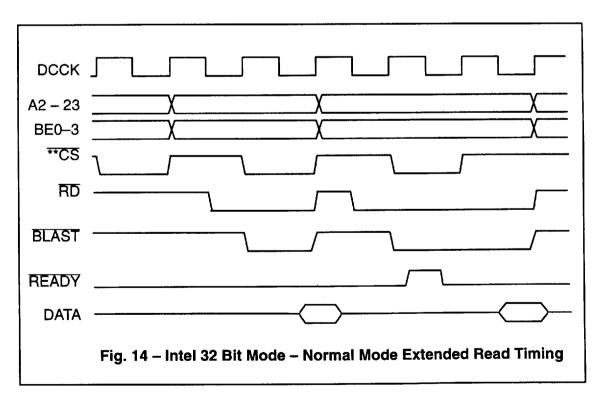

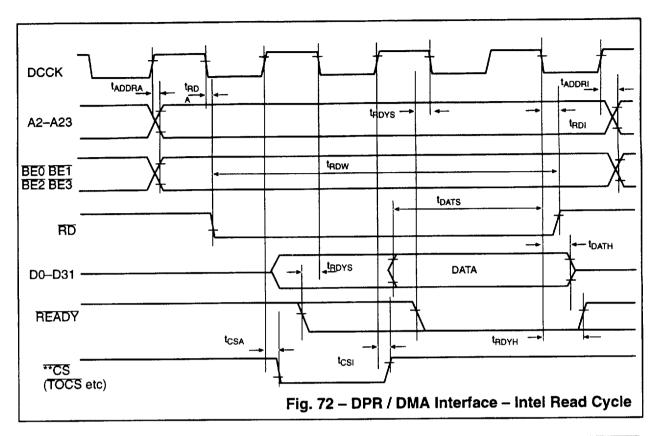

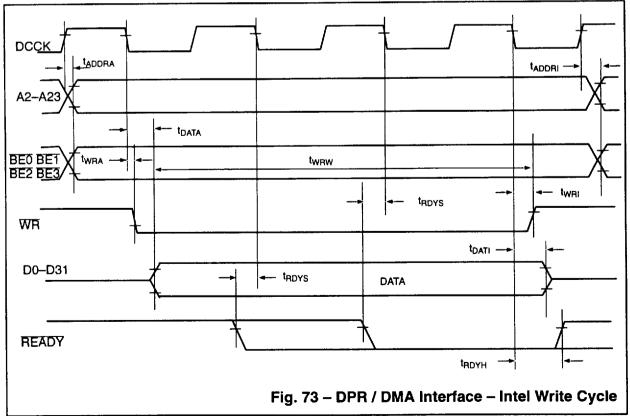

# Motorola or Intel compatible bus cycles

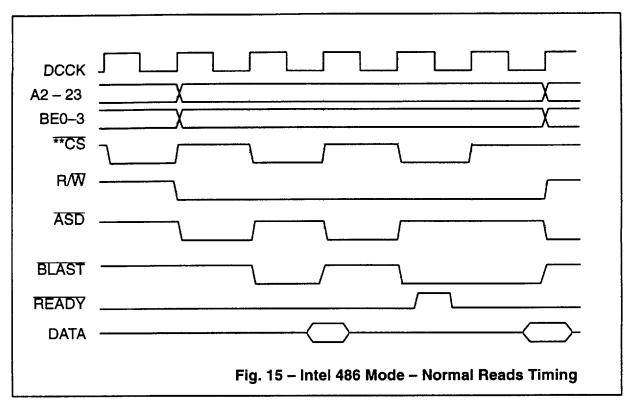

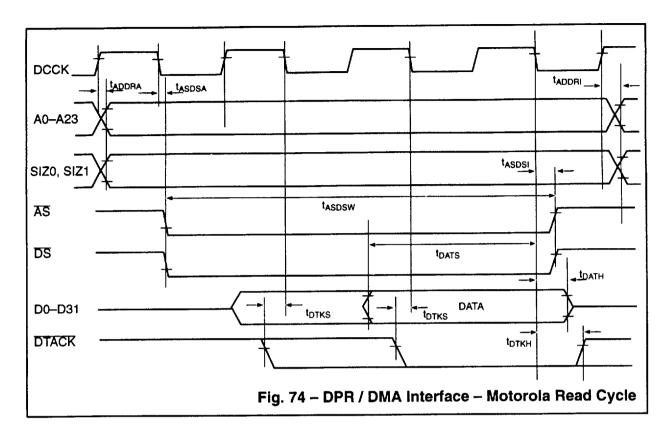

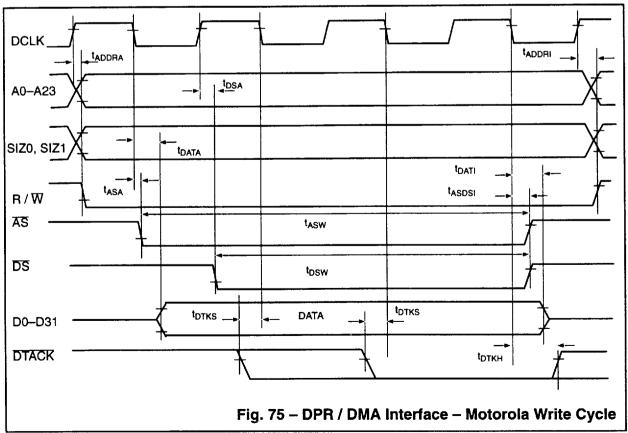

Examples of Motorola and Intel Mode Normal Read cycles are shown in Fig. 13 and Fig. 14 respectively.

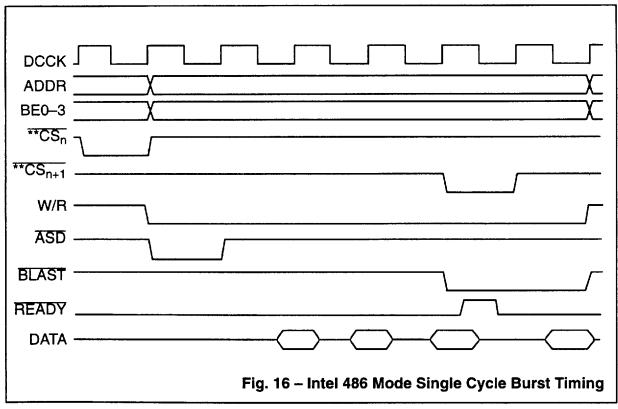

# Extended Intel (486) & Motorola (040) modes.

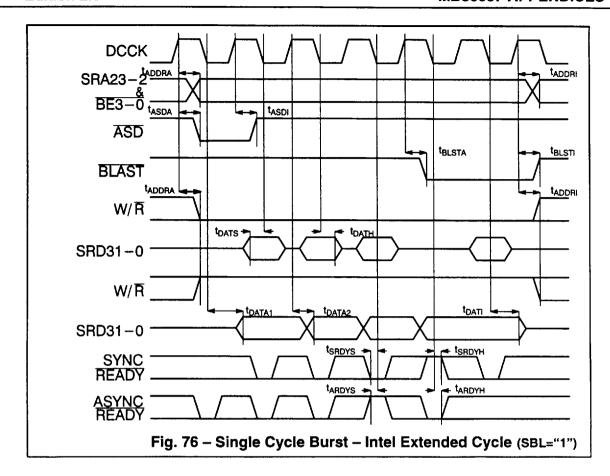

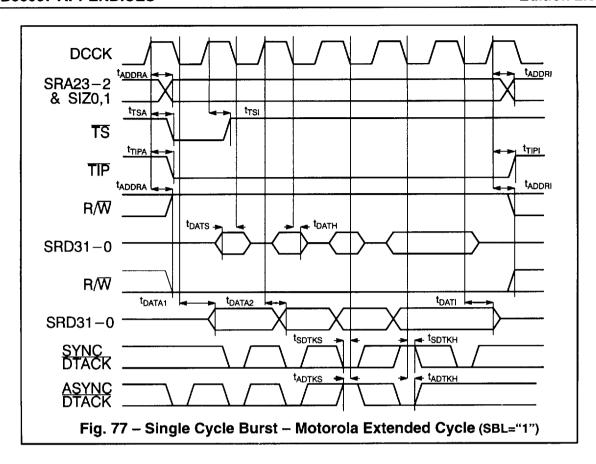

These modes allow Single Cycle data bursts. Examples of the Intel extended normal and burst read cycles are shown in Fig. 15 and Fig. 16 respectively.

## **Addressing Schemes**

- Little or Big Endian addressing schemes in Intel mode

- Big Endian addressing schemes in Motorola mode.

#### Other Features

- Direct connection to Dual Port RAM;

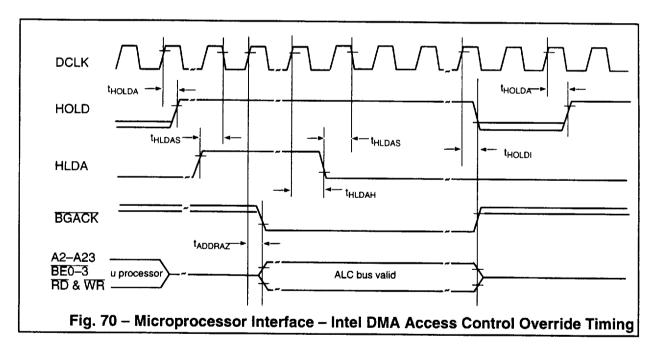

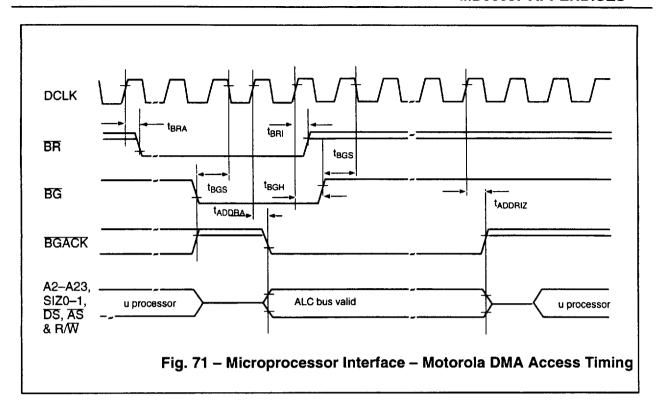

- Bus arbitration as required in DMA mode:

- DMA burst length limiting in the range

1 to 255 memory cycles.

- READY/DTACK extended cycles in Ready dependent SAR memory mode.

- Memory contention interrupt generation in response to READY/DTACK transition when using Fast Cycle Mode.

- SADRV (TX cell stream Drive) –

Using the SADRV signal on MB86687

allows pull—up resistors to be omitted.

Earlier ALC devices needed pull—up

resistors on all the address and

control signals because the selection

of DPR or DMA modes was controlled

by a register.

This mode is selected by tying the SADRV pin low. By default, it is deselected by an internal pull-up resistor and the register controls the operation

READY is sampled on the falling edge of DCCK at the end of state 3. The example shown uses a synchronous READY signal.

An asynchronous READY signal takes one extra clock cycle to take effect due to internal synchronisation.

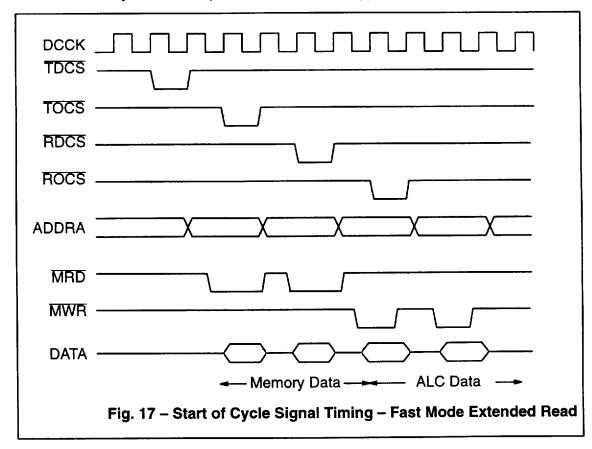

## 3.7.2 Start of Cycle Signals

There are four start of cycle signals. They are as follows:-

#### TOCS

Transmit Overhead Cycle Start output.

#### TDCS

Transmit Data Cycle Start output.

## • ROCS

Receive Overhead Cycle Start output.

#### • RDCS

Receive Data Cycle Start output.

These start of cycle signals are asserted before the associated operation. In normal mode, this will be one clock cycle before the next operation. In READY dependent mode where cycles are back to back, the signal will be asserted during the second clock of the previous cycle. In shared memory systems, this period may be indeterminate because an active start of cycle may be asserted for an operation that will occur after the bus has first been released and then regained. When stealing or forced bursting is enabled a single start of cycle pulse may precede a group of consecutive operations of the same type.

### **Parity Bits**

Parity generation and detection on a per byte basis is supported on the SAR memory interface using four bi-directional signals. A register bit determines if the parity generation/ checking is to be odd or even. If a parity error occurs an interrupt is generated.

## 3.7.3 DMA Cycle Optimisation

The ALC can be programmed to change the cycle ordering on its DMA interface to be optimal for different system configurations. This is achieved by progressively setting more bits in the most significant word of the DMA Mode Register. The settings are as follows:—

0H – cycles are compatible with 86A ready dependant cycles

- 1H cycles are compatible with 86A fast cycles with stealing on data cycles only

- 7H cycles are optimised for dual port RAM systems with stealing of data and overhead cycles

- 1FH cycles are optimised for shared memory systems where there may be different memory partitions. The cycles will be grouped according to their type.

## 3.7.4 Transmit DMA CACHE

The ALC uses shared or private memory to create and maintain queues of data packets, packet segmentation information and traffic management data.

To reduce the number of overhead cycles used to access these, a caching mechanism may be used whereby the parameters for up to 128 circuits can be stored on—chip.

The cache is operated in the following way and requires a small processor overhead to maintain a table of cached entries.

- The host software assesses the traffic requirements of each circuit and makes a decision about which circuits would benefit being in the cache.

- The host signals to the ALC that a circuit should be cached via the Circuit Reference Table using the cache start bit and address fields.

- The host then schedules a packet or packets via the TPQ mechanism.

- On its first pass through the data structures, the ALC fetches the appropriate parameters from the Circuit Reference Table and the current Transmit Descriptor and stores them on chip.

- Subsequently the ALC will process the internal copies of its data structures.

- Further queued packets will cause the ALC to fetch the new Transmit Descriptor information only.

- On completion of the packet, if no more packets are queued, the cache entry will remain valid but idle until a new packet is queued or the entry is overwritten with a new entry.

- Additional codes added to the Buffer Release Queue return codes will notify the host when all packets for a particular circuit have been assembled. At this time the host can choose to re-use the cache entry for another circuit.

Edition 2.0 MB86687

## 4. DEVELOPERS NOTES

## 4.1 Configuration Control Issues

This section is intended to give an overview of the ALC from a system programmers perspective. The following operations need to be performed by the host to configure the ALC.

- Set up the shared data structures,

- Set up queue addresses,

- Set up queue service rate parameters,

- Program ALC mode registers.

During normal operation the host is also required to perform the following operations.

Pass user data buffers to the ALC for transmission,

- Reclaim used transmit buffers from the ALC for reuse after transmission completes,

- Allocate receive buffer space for use by the ALC,

- Receive packets when completion is indicated by the ALC,

- Activate and de-activate virtual circuits,

- Respond to exception interrupts as required.

These operations are explained in more detail below.

## 4.2 Transmit Data Structures

A detailed view of the transmit side data structures is shown in Fig. 18. Before data can be transmitted the host has to programme the ALC with the base address of the following transmit data structures: Transmit Descriptor Table, Circuit Reference Table, Transmit Pending Queue and the Transmit Buffer Release Queue.

In addition the host has to initialise the appropriate entries in the Transmit Descriptor and Circuit Reference Tables.

## **Transmit Descriptor Table**

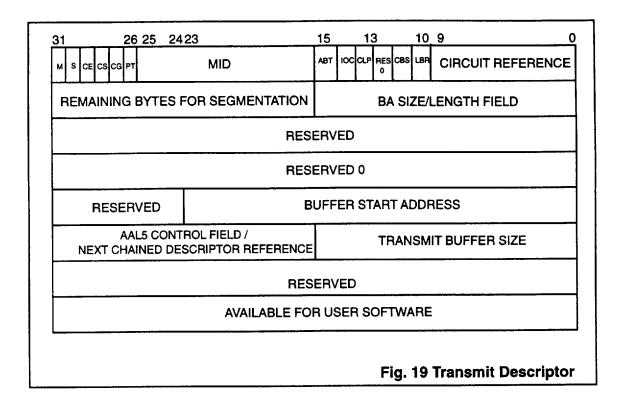

The Transmit Descriptor Table is composed of a contiguous list of Transmit Descriptors (TDs). The host composes a TD for each packet to be transmitted and adds the TD to the TD table. The table can contain up to 4096 TDs. A TD is composed of the following fields, see Fig. 19 on page 33.

### M (More)

The host sets this bit to 0 to indicate that the transmit buffer associated with this TD contains the End of Message segment of the CS-PDU. The ALC will append a CS-PDU trailer after the end of this buffer. All other TDs associated with the buffer should have M set to 1.

## S (Segmenting)

This bit is set by the ALC to indicate that segmentation is in progress on the transmit buffer. The host sets the S bit to zero before passing the TD to the Transmit Descriptor Table.

### CE (Chain End)

The host sets this bit to 0 to indicate that this is the last TD in the chain. If CE is set, the ALC assumes that the Next Chained Descriptor Reference field is valid.

## **CS** (Chain Start)

The host sets this bit to indicate that the associated transmit buffer is not the first buffer of a chain or stream of descriptors. This bit is used for AAL3/4 or for AAL5 when using external calculation of Convergence Sublayer parameters.

## CG (Congestion indication)

The host sets this bit to indicate that ATM cells generated from the associated buffer should have the congestion notification bit set in the Payload Type Field.

## PT (Pass Transparent)

The host sets this bit to indicate that the ALC should set the CG bit in the PTI field and CLP bit of the ATM cell header directly as coded in the Circuit Reference Table for each cell, otherwise the CG and CLP bits are as programmed in the Transmit Descriptor.

## MID (Multiplexing Identification)

The ALC writes this ten bit field into the ATM cell's MID field.

## ABT (Abort)

The host sets this bit to instruct the ALC to transmit an Abort cell as defined for streaming mode operation. When an abort AAL3/4 or AAL5 cell has been transmitted the following queued descriptor should not have the CS bit set ie. it should be the first descriptor in a new packet.

## **IOC (Interrupt On Completion)**

The host sets this bit to indicate that the ALC should generate an interrupt when segmentation of the packet is complete.

## **CLP (Cell Loss Priority bit)**

The host sets this bit to indicate that ATM cells generated from the associated buffer should have the CLP bit set = 1.

## **CBS (Copy Buffer Size)**

The host should set this bit if the Transmit Buffer Size field is the initial value for bytes for segmentation.

## LBR (Leaky Bucket Reset)

The host should set this bit if the leaky bucket variable capacity is to be re-initialised the first time data is re-assembled from this TD.

#### Circuit Reference

This field is a 10 bit index into the Circuit Reference Table. It is shifted left by 4 bits then added to the Circuit Reference Table base address (shifted left by 8 bits) to generate a pointer to the appropriate entry in the Circuit Reference Table. The circuit reference index could be either the VCI or MID of the connection.

## Remaining Bytes for Segmentation

This field is initially loaded with the total number of bytes in the packet for segmentation. This field is modified by the ALC during packet transmission. In streaming and chaining modes, the length of each buffer can be any number of bytes provided that the next streamed or chained buffer can fill any remaining partially assembled cell. In streaming mode a buffer that does not terminate on a cell boundary will be held by the ALC until a subsequent buffer is linked on.

### **BA Size / Length Field**

In AAL 3 /4 mode the ALC transmits this value in the BA Size field of the AAL 3/4 CS-PDU header. In AAL5 mode the AAL transmits this value in the AAL5 CS-PDU trailer LENGTH field.

#### Reserved 0

These fields are for internal ALC usage. They should be initialised to 0 and reset to 0 when the host retrieves the transmit descriptor through the transmit buffer release queue but otherwise should not be used by the host.

#### Reserved

These fields are for internal ALC usage and should not be used by the host.

#### **Buffer Start Address**

This 24 bit pointer provides the ALC with the start address of the associated transmit buffer. Any number of header bytes can be read from a user data buffer by writing the correct byte (non 32 bit aligned) address to this location.

# AAL5 Control Field / Next Descriptor Reference

In chaining mode the host programmes the next descriptor reference in the chain into this field. In AAL5 mode, this field contains the Control Field of the CS-PDU trailer only if this is the final TD in the chain.

### **Transmit Buffer Size**

This 16 bit value is set by the host. It specifies the number of bytes in the associated transmit buffer. This field is optionally used by the ALC, if the CBS bit is set, as the initial value of bytes for segmentation.

#### Available for User Software

This field is not used by the ALC and will not be used by future ALC devices. This field may be utilised by user software.

## Re-initialisation of Transmit Descriptors

| Field                        | Mode                                                            |          |           |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------|----------|-----------|--|--|--|--|--|--|

|                              | Message                                                         | Chaining | Streaming |  |  |  |  |  |  |

| Segmenting (S) bit           | 0                                                               | 0        | 0         |  |  |  |  |  |  |

| AAL5 Control/<br>Next Chain  | set AAL5: control in last TD  Next chain descriptor Set last TD |          |           |  |  |  |  |  |  |

| Buffer<br>Start Address      | Programmed by Host                                              |          |           |  |  |  |  |  |  |

| AAL3/4 BASIZE<br>AAL5 Length | set * AAL3/4: BASIZE in first TD AAL5: length in last TD *      |          |           |  |  |  |  |  |  |

| Bytes remaining              | Programmed by Host **                                           |          |           |  |  |  |  |  |  |

| Reserved 0                   | Program to 0                                                    |          |           |  |  |  |  |  |  |

Note \* In AAL5, if the MAAL5 bit is set, this value is computed automatically by the ALC.

Note \*\* If copy buffer size is set, this field will be refreshed by the ALC to the value in the Transmit Buffer Size field.

#### **Circuit Reference Table**

The Circuit Reference Table is composed of a list of contiguous Circuit Reference entries. There is a Circuit Reference for each active Virtual Circuit. Each Circuit Reference Table entry contains the ATM Cell header and the Leaky Bucket parameters for the relevant VC. The Circuit Reference is composed of the following fields, see Fig. 20.

## Routing Tag 0 - 3

Optional routing tag appended in applications where the ALC is interfacing directly with a Fujitsu Self Routing Switch Element MB86680B device or any similar device. Up to three octets of routing is supported.

- GFC Generic Flow Control,

- VPI Virtual Path Identifier,

- VCI Virtual Channel Identifier,

- PTI Payload Type Identifier,

- CLP Cell Loss Priority.

These form the ATM Header Field as defined by the UNI Specification. The ALC will code the PT bit of the PTI field according to the state of assembly of the SDU.

U, Leaky Bucket utilisation parameter

This field contains the average rate of cell

transmission for leaky bucket

management expressed as a ratio of the

peak rate. The coding is as follows:

| Bit no.            | 11 | 10  | 9   | 8   |   |

|--------------------|----|-----|-----|-----|---|

| Peak Rate<br>Ratio | 1  | 1/2 | 1/4 | 1/8 |   |

|                    |    |     |     |     | ł |

The host can select any combination of bits to generate the required average rate. If the ratio is programmed to 1, the peak and average rates will be identical which could be used for constant bit rate traffic. Average rates greater than 1 are not supported.

| 04                | · · · · | 00  | 07   | 04   | 22           |  | 2/                                                         | 110 |    | 16                                    | 15           |     | 10    |      |       |      | 7   | 6   | _       | 1  | 2   | 2   | 1   | _   |

|-------------------|---------|-----|------|------|--------------|--|------------------------------------------------------------|-----|----|---------------------------------------|--------------|-----|-------|------|-------|------|-----|-----|---------|----|-----|-----|-----|-----|

| 31                |         | 28  | 27   | 24   | 23 2019 1    |  |                                                            |     | 10 | 615 1211 8                            |              |     |       |      |       | ,    |     |     |         |    |     |     | _   |     |

|                   | 00      | 000 | 0000 |      | ROUTING TAGO |  |                                                            |     |    |                                       | ROUTING TAG1 |     |       |      |       |      | R   | ΓΙΝ | IG TAG2 |    |     |     |     |     |

| G                 | 3FC     |     |      | ٧    | Pl           |  |                                                            |     |    |                                       |              |     |       | VC   |       |      |     |     |         |    |     | PTI |     | CLP |

| E C H             | CHSHS   | СШУ | RESE | RVEC | CADDRESS     |  |                                                            |     |    | LEAKY BUCKET CAPACITY<br>CONSTANT (M) |              |     |       |      | SRS S |      |     |     | IQN A   |    |     | LT  |     |     |

| RESERVED RESERVED |         |     |      |      |              |  | RESERVED UTILISATION LEAKY BUCKET CAPACI (U) VARIABLE (M*) |     |    |                                       |              |     | ITY   |      |       |      |     |     |         |    |     |     |     |     |

|                   |         |     |      |      |              |  |                                                            |     |    |                                       |              | Fiç | j. 20 | ) Ci | rcui  | t Re | efe | ren | ıce     | Та | ble | eΕ  | ntr | у   |

## ECS (External Calculation of SPCS)

Single bit instruction to use external memory for AAL5, CRC32 and AAL3/4 length field and sequence number. This is used for non-cached entries when internal memory is not available: set by HOST. (Each cache entry uses the storage of 8 equivalent VC entries)

Additionally used in transparent cell and transparent payload to indicate to the ALC that the CRC10 should be calculated and placed in the last 10 bits of the payload.

# CHS (Cache Start)

Set by HOST.

## **CHSTS (Cache Status)**

Initialised to '0' by the HOST, set by ALC.

## **CEV (Chain End Valid)**

Initialised to '0' by the HOST, set by ALC

## **CADDRESS (Cache Address)**

(7 bit field): set by HOST; valid if the CHS bit is set.

## SRS (Sub-Rate Select)

These bits are used to select the required sub-rate of the nominal transmit queue peak rate. The coding is as follows.

| Bit<br>7 | no.<br>6 | Sub-rate<br>selected |

|----------|----------|----------------------|

| 0 1      |          | 25%                  |

| 1        | 0        | 50%                  |

| 1 1      |          | 100%                 |

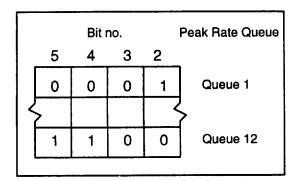

## **SQN (Service Queue Number)**

The host uses this field to assign the associated Virtual Circuit to one of the 12 peak rate queues. The coding is as follows:

Queue 1 corresponds to Low Priority and Queue 12 corresponds to High Priority Queue 4.

# **AALT (ATM Adaption Layer Type)**

This field is used to specify the AAL type for the VC. Two transparent modes can also be selected. The coding is as follows:

| 1 | 0 | AAL Type selected   |

|---|---|---------------------|

| 0 | 0 | AAL 3/4             |

| 0 | 1 | Transparent Payload |

| 1 | 0 | Transparent Cell    |

| 1 | 1 | AAL 5               |

# M (Leaky Bucket capacity constant)

M in the Circuit Reference Table entry is the bucket capacity used to implement leaky bucket averaging on a per VC basis. The host programmes this field with a Leaky Bucket capacity in the range of 0-255. The relationship between the bucket capacity (M), the utilization (U) and the maximum burst length (B) at the selected peak rate is given by:

$$M = (B-1)x(1-U)$$

for single leaky bucket method and by:

$$M = B \times (1 - U)$$

for double leaky bucket method.

#### Note:

If the resulting M value is not an integer then in the single leaky bucket case M should be rounded DOWN to the nearest integer and in the double leaky bucket case M should be rounded UP to the next integer.

Also, for the single leaky bucket case a minimum value of B is specified for each utilization value as given below:

U = 0.875 minimum allowed B = 9,

U = 0.75 minimum allowed B = 5,

U = 0.625 minimum allowed B = 4,

For all other values of U the minimum value allowed for B is 3.

# M\* (Leaky Bucket capacity variable)

The ALC uses this variable to implement leaky bucket averaging on a per virtual circuit basis. The host initially sets M\* to the same value as M, M\* is then modified by the ALC as the ALC implements the leaky bucket algorithm for that VC. The ALC uses the constant value M for reference when carrying out leaky bucket calculations. M\* may also be refreshed to M when the LBR bit is set in a TD.

#### Reserved

These fields are for internal ALC usage and should not be used by the host.

# 4.2.1 Transmit Pending Queue

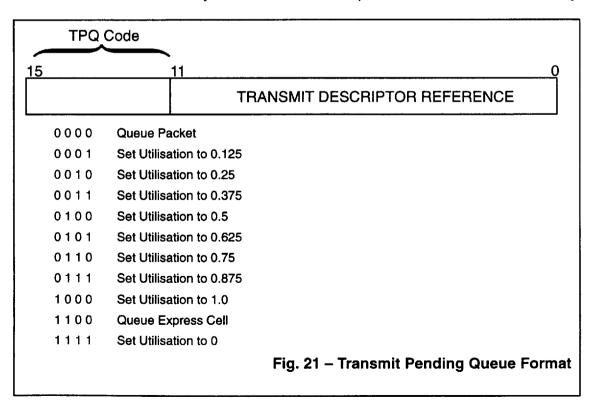

The transmit pending queue is used by the host to instruct the ALC to queue a transmit packet for segmentation. Each command passed to the queue includes a 12 bit index reference into the Transmit Descriptor table. A Transmit Pending Queue entry is shown in Fig. 21.

This queue is defined by registers 2 – 6. The Host Processor must assign values for the Transmit Pending Queue base, start address, end, read and write pointers. The initial values of the read and write pointers should be the start address to reflect an empty queue.

To pass a new entry to the TPQ the Host Processor should read the current value of the on-chip write register. This address should be used to store the new TPQ entry. The host should then update the write pointer register, wrapping around to the start address if necessary.

When the DMA Controller has available transmit bandwidth (or once every five segmentation periods), i.e a cycle where cell segmentation is not required, it reads the value of the Transmit Descriptor Reference addressed by its internal read pointer.

In addition, the Transmit Pending Queue can be used as follows:

#### Utilisation adjustment;

The U value in the CRT pointed to by the associated TD will be set to the given value.

This is not applicable to cached entries.

## Send Express Cell;

If an entry is placed on the queue with the 1100 coding then it will not be assigned to a rate queue but will be sent immediately.

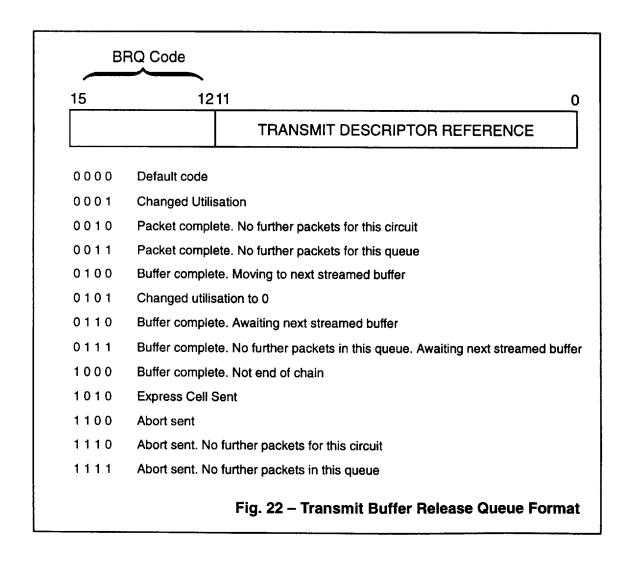

# 4.2.2 Transmit Buffer Release Queue

The ALC returns segmented transmit buffers to the host using the Buffer Release Queue. Each queue entry will contain a 12 bit reference index into the Transmit Descriptor table. A queue entry is shown in Fig. 22.

This queue is defined by registers 2 and 7 – 10. The Host Processor must assign values for the Buffer Release Queue base, start address, end, read and write pointers.

The initial values of the read and write pointers may be the start address to reflect an empty queue or the write pointer may be set to the read pointer minus 1 to reflect a pool of free buffers.

To release a buffer to the host the ALC increments the TBRQ write pointer and, if the IOC bit in the Transmit descriptor is set, generates an interrupt. The host may then choose to immediately acknowledge this action by updating the TBRQ read pointer or if using the queue as a pool of free buffers, only update the pointer when reusing the TD.

# 4.2.3 INCWRAP – Wrap and Increment Mechanism

When writing to the host-controlled queue registers, if the most significant bit of the control data bus is set, the ALC will automatically increment its internal copy of the pointer being written to regardless of the pointer value specified on the data bus.

Two status conditions are available when reading the host–controlled pointers:

#### • EMPTY condition

If this bit is set, it indicates that the ALC's pointer for the queue is at the same value as the host pointer's value returned by the read and that the queue is empty.

## • FULL condition

If this bit is set, it indicates that the host pointer and ALC pointer values are the same and that the queue is full. Edition 2.0 MB86687

#### 4.3 Receive Data Structures

A detailed view of the receive data structures is shown in Fig. 23. Before data can be received the host has to programme the ALC with the base address of following receive data structures: Receive Descriptor Table, Receive Buffer Free Queue and the Receive Buffer Ready Queue.

#### 4.3.1 Receive Descriptor Table

The Receive Descriptor Table is composed of a contiguous list of Receive Descriptors (RDs). The host is responsible for composing sufficient RDs to handle the expected number of receive packets.

Each time a start of packet cell is received the ALC will use the next entry in the Receive Buffer Free Queue to locate the relevant RD in the table. A typical RD is composed of the following fields, see Fig. 24 on page 43.

#### V (Valid)

The ALC sets this bit to 1 to indicate that the Next Chain Descriptor field in this descriptor is valid. This is used in chaining mode when the received packet does not terminate in the current receive buffer. When this bit is cleared to 0 it indicates that the chain of receive buffer descriptors terminates with this descriptor. The host is required to initialise this bit to 0 and also in chaining mode to clear this bit to 0 before returning the receive descriptor to the ALC through the buffer free queue.

# **Next Chain Descriptor Reference**

When receive buffer chaining is used this 12 bit field is programmed by the ALC with the descriptor reference of the next receive descriptor in the chain.

#### Reserved

These fields are for internal ALC usage and should not be accessed by the host.

| 31 | 28 27 24                              | 23              | 15  | 14     | 13 12        | 11 10                              | 9                    |  |  |

|----|---------------------------------------|-----------------|-----|--------|--------------|------------------------------------|----------------------|--|--|

|    | UNU                                   | v               | RES | SERVED | D            | NEXT CHAIN<br>DESCRIPTOR REFERENCE |                      |  |  |

|    | RESE                                  | CLP             | C – | (      | 3FC          | RECEIVE CIRCUIT<br>REFERENCE       |                      |  |  |

|    | UNU                                   | SED             |     |        |              | В                                  | UFFER SIZE           |  |  |

|    |                                       | RESE            | RV  | ED     |              |                                    |                      |  |  |

|    |                                       | AVAILABLE FOR U | JSE | ER S   | SOFT         | WARE                               |                      |  |  |

|    | BYTES RE                              | CEIVED          |     |        |              | REMAI                              | INING CAPACITY       |  |  |

|    | RESERVED                              | В               | UF  | FEF    | R STA        | RT ADI                             | DRESS                |  |  |

|    | AAL5 CONTROL FIELD /<br>AAL3 RESERVED |                 |     |        | TOTAL LENGTH |                                    |                      |  |  |

|    |                                       |                 |     |        |              | Fig                                | 24 Receive Descripto |  |  |

#### **Receive Circuit Reference**

This 10 bit field is programmed by the ALC with the receive channel supplying data to the associated receive buffer. This channel number will imply a particular VP/VC according to the programming of VPB2, VPB1 & VPB0 in Register 16. If chaining is used, this value is only valid in the first descriptor of the chain.

# **CLP (Cell Loss Priority)**

The ALC sets this bit to indicate that the last ATM cell re-assembled into the associated buffer had the CLP bit set = 1.

## CI (Congestion Indication)

The ALC sets this bit to indicate that the last ATM cell re—assembled into the associated buffer had the CI bit set = 1.

# **GFC (Generic Flow Control)**

The ALC sets this field to the GFC value in the last ATM cell reassembled into the associated buffer.

#### Unused

These fields should not be utilized by user software but may be cleared to 0 by the host.

#### **Buffer Size**

If the RDAU bit is set in Register 16, this value is automatically copied into the Remaining Capacity field when the RD is first accessed. The value is not modified by the ALC.

### **Available for User Software**

This field is not used by the ALC and will not be used by future ALC devices. This field may be utilized by user software.

## **Bytes Received**

This 16 bit field is programmed by the ALC with the number of bytes written to the associated receive buffer. This field should be initialized to 0 and reset to 0 before returning the descriptor for reuse through the buffer free queue. This count is always a multiple of 4 bytes and hence, will include up to 3 bytes of pad at the end of a packet.

# **Remaining Capacity**

This field indicates the number of unused bytes within the associated buffer. This field should be initialized to the buffer capacity and reset to the buffer capacity before returning the descriptor for reuse through the buffer free queue. This count is always a multiple of 4 bytes and hence, will include up to 3 bytes of pad at the end of a packet.

#### **Buffer Start Address**

This 24 bit pointer is programmed by the host with the start address of the receive buffer associated with this descriptor.

# AAL5 Control Field / AAL3 Reserved

When AAL5 is selected this field is used to hold the received AAL5 control value obtained from the incoming CS-PDU trailer. If chaining is enabled then this field is only valid in the initial receive descriptor of the chain. In all other descriptors in the AAL5 chain this field is reserved. In AAL 3 for all descriptors this field is reserved. In chaining mode this field should be initialized to 0 and reset to 0 before returning the descriptor for re—use through the buffer free queue.

# Total Length

This 16 bit value is programmed by the ALC with the total length field received in the CS-PDU trailer. If chaining is used then this field contains the total length only in the initial receive descriptor of the chain. In chaining mode this field should be initialized to 0 and reset to 0 before returning the descriptor for reuse through the buffer free queue.

## Re-initialisation of Receive Descriptors

| Field                      | Mode           |                |                |  |  |  |

|----------------------------|----------------|----------------|----------------|--|--|--|

|                            | Message        | Chaining       | Streaming      |  |  |  |

| V & next chain RD          | N/R            | 0              | N/R            |  |  |  |

| Bytes Received             | 0 *            | 0 *            | 0 *            |  |  |  |

| Remaining Capacity         | buffer size ** | buffer size ** | buffer size ** |  |  |  |

| BufferStart Address        | Pro            | grammed by H   | ost            |  |  |  |

| AAL5 Control/AAL3 Reserved | 0              | 0              | 0              |  |  |  |

| Total Length               | N/R            | 0              | N/R            |  |  |  |

N/R Reinitialisation not required

Note \* If RDAU is set in Register 16, Bytes Received is automatically cleared when the RD is first accessed; Reinitialisation is then not required.

Note \*\* If RDAU is set in Register 16, Buffer Size is automatically copied into Remaining Capacity when the RD is first accessed. Reinitialisation is then not required.

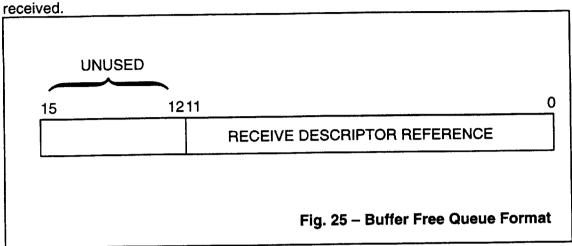

## 4.3.2 Receive Buffer Free Queue

The Receive Buffer Free Queue is used by the ALC to locate the next Receive Descriptor each time a new packet is Each queue entry contains a reference into the Receive Descriptor table. The format of a queue entry is shown in Fig. 25.

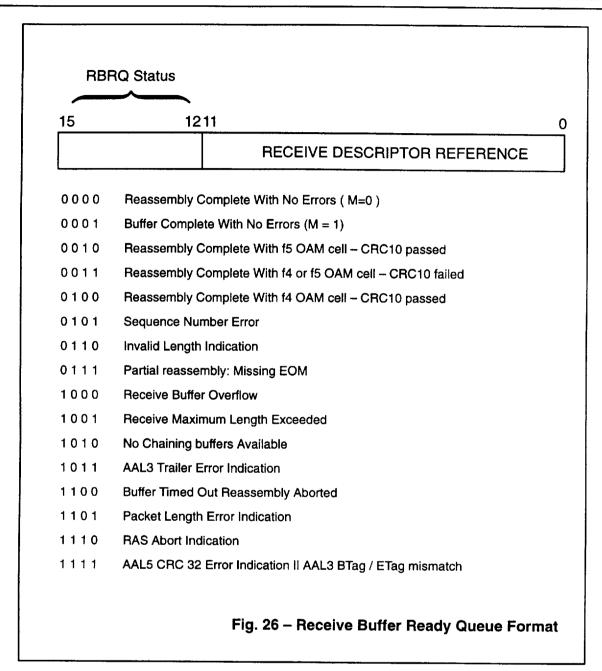

# 4.3.3 Receive Buffer Ready Queue

The ALC passes reassembled packets to the host using the Receive Buffer Ready Queue. Each queue entry contains a reference to the relevant Receive Descriptor. In addition the ALC writes the status of the received packet to the Buffer Ready Queue. The format of each queue entry is shown in Fig. 26.

# 4.3.4 Increment and Wrap Mechanism

This mechanism is similar to that used by the transmit queues and is described in section 4.2.3.

# 4.3.5 Receive Descriptor Table Access Mechanism

# Writing to the Table

The write to RSD table process operates in the following way. The host sets the data intended for the RSD by writing it to the Host Receive Descriptor/Status Table Write Register (Register 58) – (This will normally involve setting the ACT bit when a channel is about to be activated).

The host then writes to the Host Receive Descriptor/Status Table Access Register (Register 59). The HOSTR and RD/WR must be set to generate the internal write to the RSD table. The values in Register 58 together with the AAL bits from Register 59 are written into the RSD table at the address specified by the VCI values in Register 59.

The TAC interrupt will be generated in response to the write to Register 59 to inform the host that the RSD table has been updated.

# Reading from the Table

The read from RSD table process comprises the following sequence of events. The host writes to Register 59 setting HOSTR and clearing RD/WR. This causes the ALC to carry out an internal read to the RSD table using the address specified by the VCI value in Register 59.