# ter EL5181C, EL5281C, EL5283C, EL5481C, EL5482C Preliminary

8nS High-Speed Comparator Fafmily

#### **Features**

- 8ns Typ. Propagation delay

- · Low Power Consumption of <25mW/ comparator (at +5V)

- 5V to 12V input supply

- +2.7V to +5V output supply

- True To Ground Input

- · Rail to rail outputs

- · Active low latch

- Pin compatible 4nS family available (EL5185 family)

### **Applications**

- · Threshold Detection

- · High Speed Sampling Circuits

- · High speed Triggers

- · Line Receivers

- PWM Circuits

- · High SpeedV/F Converters

## **Ordering Information**

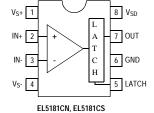

| Part No. | Temp. Range    | Package     | Outline # |

|----------|----------------|-------------|-----------|

| EL5181CN | -40°C to +85°C | 8-Pin DIP   | MDP0031   |

| EL5181CS | -40°C to +85°C | 8-Pin SOIC  | MDP0027   |

| EL5283CY | -40°C to +85°C | 10-Pin MSOP | MDP0043   |

| EL5281CS | -40°C to +85°C | 14-Pin SOIC | MDP0027   |

| EL5481CS | -40°C to +85°C | 16-Pin SOIC | MDP0027   |

| EL5482CM | -40°C to +85°C | 20-Pin SOL  | MDP0027   |

| EL5482CU | -40°C to +85°C | 24-Pin QSOP | MDP0040   |

# **General Description**

The EL5181C family of comparators are designed for operation in single supply and dual supply applications with 5V to 12V between V<sub>S</sub>+ and V<sub>S</sub>-. For single supplies, the inputs can operate from 0.1V below ground for use in ground sensing applications.

The output side of the comparator can be supplied from a single supply of 2.7V to 5V. The outputs swing is to each rail to allow direct connection to CMOS and TTL logic circuits.

These comparators exhibit very short delay times of typically 8ns with power a dissipation of less than 25mW per comparator.

The EL5181C, EL5283C, EL5281C and EL5481C also have latch inputs, holding the comparator output value when a low logic level is applied to the pin. The EL5482C has no latches. The EL5283C is a window comparator, with a single input pin and two range inputs. When the input is beyond the range, the output flags an out of bounds condition.

# EL5181C, EL5281C, EL5283C, EL5481C, EL5482C Preliminary

#### Absolute Maximum Ratings (TA = 25 °C)

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

$\begin{aligned} & \text{Analog Supply Voltage } (V_{S^+} \text{to } V_{S^-}) & +12 V \\ & \text{Digital Supply Voltage } (V_{SD} \text{ to GND}) & +7 V \end{aligned}$

Differential Input Voltage  $[(V_{S^{\text{-}}}) \text{ -0.2V}] \text{ to } [(V_{S}\text{+}) \text{ +0.2V}]$

2kV

#### Important Note:

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

ESD Voltage

#### **Electrical Characteristics**

$V_S = \pm 5V$ ,  $V_{SD} = 5V$ ,  $R_L = 2.3k\Omega$ ,  $C_L = 15pF$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified.

| Parameter           | Description                          | Condition                                                       | Min                    | Тур                    | Max                    | Units |

|---------------------|--------------------------------------|-----------------------------------------------------------------|------------------------|------------------------|------------------------|-------|

| V <sub>OS</sub>     | Input Offset Voltage                 | V <sub>CM</sub> =0V, V <sub>O</sub> =2.5V                       |                        | 0.5                    | 2.0                    | mV    |

| I <sub>B</sub>      | Input Bias Current                   |                                                                 |                        | 5                      | 10                     | μΑ    |

| C <sub>IN</sub>     | Input Capacitance                    |                                                                 |                        | 5                      |                        | pF    |

| I <sub>OS</sub>     | Input Offset Current                 | V <sub>CM</sub> =0V, V <sub>O</sub> =2.5V                       |                        | 50                     | 250                    | nA    |

| V <sub>CM</sub>     | Input Voltage Range                  |                                                                 | $(V_{S}-) - 0.1$       |                        | (V <sub>S</sub> +) -2V | V     |

| A <sub>VO</sub>     | Large Signal Voltage Gain            |                                                                 |                        | 5000                   |                        | V/V   |

| CMRR                | Common-Mode Rejection Ratio          | -5V <v<sub>CM&lt;+2.75V, V<sub>O</sub>=1.4V</v<sub>             |                        | 80                     |                        | dB    |

| PSRR                | Power Supply Rejection Ratio         | 4 4. 4                                                          |                        | 80                     |                        | dB    |

| V <sub>OH</sub>     | Output High Voltage                  | V <sub>IN</sub> >250mV                                          | V <sub>SD</sub> - 0.5V | V <sub>SD</sub> - 0.4V |                        | V     |

| $V_{OL}$            | Output Low Voltage                   | V <sub>IN</sub> >250mV                                          |                        | GND + 0.4V             | GND + 0.5V             | V     |

| $V_{LH}$            | Latch Input Voltage High             |                                                                 |                        |                        | 2.0                    | V     |

| $V_{LL}$            | Latch Input Voltage Low              |                                                                 | 0.8                    |                        |                        | V     |

| $I_{LH}$            | Latch Input Current High             | V <sub>LH</sub> =3.0V                                           |                        | 1                      | 20                     | μΑ    |

| $I_{LL}$            | Latch Input Current Low              | V <sub>LL</sub> =0.3V                                           |                        | 5                      | 20                     | μΑ    |

| I <sub>S</sub> +    | Positive Analog Supply Current       | (per comparator)                                                |                        | 3                      |                        | mA    |

| I <sub>S</sub> -    | Negative Analog Supply Current       | (per comparator)                                                |                        | 2.5                    |                        | mA    |

| $I_{ m DD}$         | Digital Supply Current               | (per comparator)                                                |                        | 2                      |                        | mA    |

| t <sub>pd</sub> +   | Positive Going Delay Time            | V <sub>OD</sub> =5mV, C <sub>L</sub> =15pF, I <sub>O</sub> =2mA |                        | 8                      | 10                     | nS    |

| t <sub>pd</sub> -   | Negative Going Delay Time            | V <sub>OD</sub> =5mV, C <sub>L</sub> =15pF, I <sub>O</sub> =2mA |                        | 8                      | 10                     | nS    |

| t <sub>d</sub> +    | Latch Disable to High Delay          |                                                                 |                        | 10                     |                        | nS    |

| t <sub>d</sub> -    | Latch Disable to Low Delay           |                                                                 |                        | 12                     |                        | nS    |

| t <sub>s</sub>      | Minimum setup time                   |                                                                 |                        | 2                      |                        | nS    |

| th                  | Minimum hold time                    |                                                                 |                        | 1                      |                        | nS    |

| t <sub>pw</sub> (D) | Minimum Latch Disable Pulse<br>Width |                                                                 |                        | 10                     |                        | nS    |