August 14, 2002

#### © Copyright International Business Machines Corporation 2001, 2002

All Rights Reserved Printed in the United States of America August 2002

The following are trademarks of the International Business Machines Corporation in the United States, or other countries, or both.

| HyperBGA | IBM Logo |

|----------|----------|

| IBM      | PowerPRS |

InfiniBand is a trademark of the InfiniBand Trade Association.

IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers (IEEE).

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this documents, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at <a href="http://www.ibm.com">http://www.ibm.com</a>

The IBM Microelectronics Division home page can be found at <a href="http://www.ibm.com/chips">http://www.ibm.com/chips</a>

prsq-64g.02title.fm August 14, 2002

# Contents

| List of Figures                                                    | 9    |

|--------------------------------------------------------------------|------|

| List of Tables                                                     | 11   |

| 1. General Information                                             | 13   |

| 1.1 Features                                                       | . 13 |

| 1.2 Description                                                    | . 13 |

| 1.3 Ordering Information                                           | . 14 |

| 1.4 Conventions and Notation                                       |      |

| 2. Architecture                                                    | 15   |

| 2.1 System Application                                             | . 15 |

| 2.2 Internal Structure                                             |      |

| 2.2.1 HSS Interface                                                |      |

| 2.2.2 Shared Memory                                                | . 18 |

| 2.2.3 Sequencer                                                    |      |

| 2.2.4 Address Managers                                             | . 18 |

| 2.2.5 Input Controllers                                            | . 19 |

| 2.2.6 Output Queue Access Managers                                 |      |

| 2.2.7 Output Queues                                                | . 19 |

| 2.2.8 Output Queue Scheduler and Credit Table                      |      |

| 2.2.9 Output Controllers                                           | . 20 |

| 2.3 Multiple-Device Configurations                                 | . 20 |

| 2.3.1 512-Gbps Configuration                                       |      |

| 2.3.2 256-Gbps Configuration                                       |      |

| 2.3.3 Master/Slave Synchronization with Multiple Devices           |      |

| 2.3.3.1 Sequencers                                                 |      |

| 2.3.3.2 Shared Memory Addresses                                    | . 23 |

| 3. Functional Description                                          | 25   |

| 3.1 Packet Type                                                    | . 25 |

| 3.1.1 Data Packets                                                 |      |

| 3.1.2 Control Packets                                              | -    |

| 3.1.3 Service Packets                                              |      |

| 3.1.4 Idle Packets                                                 | . 26 |

| 3.2 Physical Interface and Packet Processing                       |      |

| 3.3 Packet Format According to Packet Type                         | . 28 |

| 3.3.1 General Packet Format Information                            | . 28 |

| 3.3.1.1 Packet Header                                              |      |

| 3.3.1.2 Flow Control Flywheels                                     |      |

| 3.3.2 Flow Control Flywheels for Grants Carried in Ingress Packets |      |

| 3.3.2.1 Subport Grant Type/Subport Flywheel                        |      |

| 3.3.2.2 Grant Priority Flywheel                                    |      |

| 3.3.3 Ingress Idle Packet Format                                   | . 30 |

| 3.3.4 Ingress Data Packet and Control Packet Format                |      |

| 3.3.5 Ingress Service Packet Format                                | . 35 |

## Preliminary

|    | 3.3.6 Flow Control Flywheels for Grants Carried in Egress Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                                                                                           |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 3.3.6.1 Extended Output Queue Grant Flywheel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                                           |

|    | 3.3.6.2 Output Queue Grant Priority Flywheel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                              |

|    | 3.3.6.3 Subport Grant Type/Priority Flywheel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                              |

|    | 3.3.6.4 Subport Grant Port Flywheel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

|    | 3.3.7 Egress Idle Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|    | 3.3.8 Egress Data Packet and Control Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

|    | 3.3.9 Egress Service Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

|    | 3.4 Ingress Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|    | 3.4.1 Output Queue Grants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

|    | 3.4.2 Memory Grants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

|    | 3.4.3 Multicast Grants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                              |

|    | 3.4.4 Shared Memory Overrun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                              |

|    | 3.4.5 Flow Control Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |

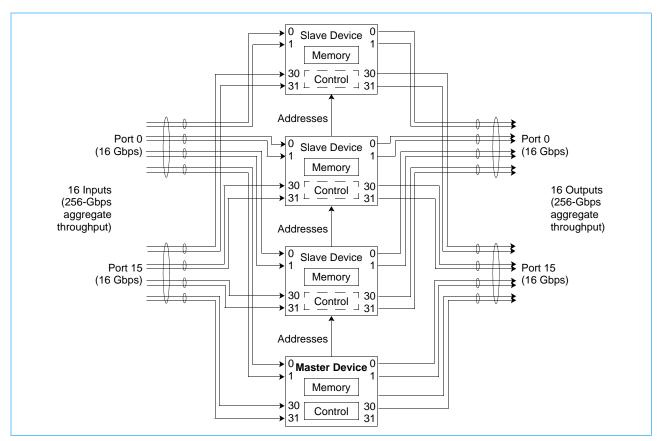

|    | 3.4.6 Best-Effort Discard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

|    | 3.4.6.1 Best-Effort Discard Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                              |

|    | 3.4.6.2 Best-Effort Discard Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                              |

|    | 3.4.6.3 Best-Effort Discard Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

|    | 3.5 Egress Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |

|    | 3.5.1 Send Grants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                              |

|    | 3.5.2 Send Grant Antistreaming<br>3.5.3 Credit Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|    | 3.6 Subport Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|    | 3.7 Flow Control Information Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                              |

|    | 3.8 Packet Reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                                                                                                           |

|    | 3.8 Packet Reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>54</b><br>55                                                                                                                                              |

|    | 3.8 Packet Reception<br>3.8.1 Data Packet Reception<br>3.8.2 Control and Service Packet Reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55<br>55<br>55                                                                                                                                               |

|    | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54<br>55<br>55<br>55<br><b>56</b>                                                                                                                            |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>55<br><b>55</b><br><b>56</b><br>56                                                                                                        |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>55<br><b>56</b><br>56<br>56                                                                                                               |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>55<br><b>56</b><br>56<br>56<br>56                                                                                                         |

|    | <ul> <li>3.8 Packet Reception</li> <li>3.8.1 Data Packet Reception</li> <li>3.8.2 Control and Service Packet Reception</li> <li>3.9 Packet Transmission</li> <li>3.9.1 Output Port Servicing</li> <li>3.9.2 Control and Service Packet Transmission</li> <li>3.9.3 Idle Packet Transmission</li> <li>3.9.4 Look-Up Table</li> </ul>                                                                                                                                                                                                                                                           | <b>54</b><br>55<br>55<br><b>56</b><br>56<br>56<br>56<br>56<br>56                                                                                             |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>55<br><b>56</b><br>56<br>56<br>56<br>56<br><b>56</b>                                                                                      |

|    | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission         3.9.1 Output Port Servicing         3.9.2 Control and Service Packet Transmission         3.9.3 Idle Packet Transmission         3.9.4 Look-Up Table         3.10 Side Communication Channel         3.11 Switchover Support                                                                                                                                                                                                              | <b>54</b><br>55<br>56<br>56<br>56<br>56<br>56<br>56<br><b>56</b><br>56<br><b>57</b>                                                                          |

|    | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission         3.9.1 Output Port Servicing         3.9.2 Control and Service Packet Transmission         3.9.3 Idle Packet Transmission         3.9.4 Look-Up Table         3.10 Side Communication Channel         3.11 Switchover Support         3.11.1 Scheduled Switchover Process                                                                                                                                                                  | 55<br>55<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>57<br>58                                                                                   |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>58<br>58                                                                      |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>56<br>56<br>56<br>56<br>56<br>56<br><b>57</b><br>58<br>59<br>60                                                                           |

|    | <ul> <li>3.8 Packet Reception</li> <li>3.8.1 Data Packet Reception</li> <li>3.8.2 Control and Service Packet Reception</li> <li>3.9 Packet Transmission</li> <li>3.9.1 Output Port Servicing</li> <li>3.9.2 Control and Service Packet Transmission</li> <li>3.9.3 Idle Packet Transmission</li> <li>3.9.4 Look-Up Table</li> <li>3.10 Side Communication Channel</li> <li>3.11 Switchover Support</li> <li>3.11.1 Scheduled Switchover Process</li> <li>3.11.1.2 Phase 1: Rerouting Traffic to One Switch Plane</li> <li>3.11.1.3 Phase 3: Resuming Traffic on Both Switch Planes</li> </ul> | <b>54</b><br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>57<br>57<br>58<br>59<br>60<br>60                                                    |

|    | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>57<br>57<br>58<br>59<br>60<br>60                                                    |

| 4  | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission         3.9.1 Output Port Servicing         3.9.2 Control and Service Packet Transmission         3.9.3 Idle Packet Transmission         3.9.4 Look-Up Table         3.10 Side Communication Channel         3.11 Switchover Support         3.11.1 Scheduled Switchover Process         3.11.1.2 Phase 1: Rerouting Traffic to One Switch Plane         3.11.1.3 Phase 3: Resuming Traffic on Both Switch Planes         3.11.2 Implementation   | 54<br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>57<br>57<br>58<br>59<br>60<br>60<br>61                                                                       |

| 4. | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission         3.9.1 Output Port Servicing         3.9.2 Control and Service Packet Transmission         3.9.3 Idle Packet Transmission         3.9.4 Look-Up Table         3.10 Side Communication Channel         3.11 Switchover Support         3.11.1 Scheduled Switchover Process         3.11.1.2 Phase 1: Rerouting Traffic to One Switch Plane         3.11.2 Phase 2: Modifying the Load-Balancing Configuration         3.11.2 Implementation | . 54<br>55<br>55<br>56<br>56<br>56<br>56<br>56<br>56<br>57<br>57<br>57<br>57<br>57<br>60<br>60<br>61<br>63                                                   |

| 4. | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission         3.9.1 Output Port Servicing         3.9.2 Control and Service Packet Transmission         3.9.3 Idle Packet Transmission         3.9.4 Look-Up Table         3.10 Side Communication Channel         3.11.1 Scheduled Switchover Process         3.11.1.2 Phase 1: Rerouting Traffic to One Switch Plane         3.11.1.2 Phase 2: Modifying the Load-Balancing Configuration         3.11.2 Implementation                               | <b>54</b><br>55<br>56<br>56<br>56<br>56<br>56<br>57<br>57<br>58<br>59<br>60<br>60<br>61<br><b>63</b><br>63                                                   |

| 4. | <ul> <li>3.8 Packet Reception</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>54</b><br>555<br>566<br>566<br>566<br>577<br>578<br>577<br>578<br>500<br>600<br>601<br>601<br>603<br>603<br>603<br>603<br>603                             |

| 4. | 3.8 Packet Reception         3.8.1 Data Packet Reception         3.8.2 Control and Service Packet Reception         3.9 Packet Transmission         3.9.1 Output Port Servicing         3.9.2 Control and Service Packet Transmission         3.9.3 Idle Packet Transmission         3.9.4 Look-Up Table         3.10 Side Communication Channel         3.11.1 Scheduled Switchover Process         3.11.1.2 Phase 1: Rerouting Traffic to One Switch Plane         3.11.1.2 Phase 2: Modifying the Load-Balancing Configuration         3.11.2 Implementation                               | 54         55         56         56         56         56         56         57         58         59         60         61         63         64         64 |

Packet Routing Switch

| 5. | Register Descriptions                               | 65   |

|----|-----------------------------------------------------|------|

|    | 5.1 SHI Internal Registers                          | 69   |

|    | 5.1.1 Internal PLL Programming Register             |      |

|    | 5.1.2 Internal PLL Status Register                  |      |

|    | 5.1.3 HSS PLL Programming Register                  |      |

|    | 5.1.4 HSS PLL Status Register                       |      |

|    | 5.1.5 Reset Register                                |      |

|    | 5.1.6 BIST Counter Register                         |      |

|    | 5.1.7 BIST Data Register                            |      |

|    | 5.1.8 BIST Select Register                          |      |

|    | 5.2 HSS Programming Registers                       |      |

|    | 5.2.1 HSS Global Register                           |      |

|    | 5.2.2 HSS Error Register                            |      |

|    |                                                     |      |

|    | 5.2.3 HSS PLL Unlock Register                       |      |

|    | 5.2.4 HSS TxPort Driver Enable Register             |      |

|    | 5.2.5 HSS TxPort Attachment Enable Register         |      |

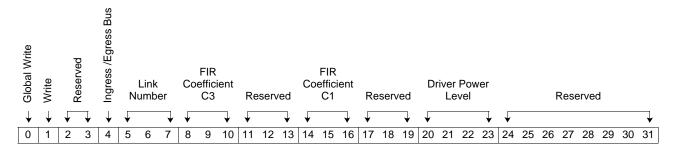

|    | 5.2.6 HSS TxPort Parameters Register                |      |

|    | 5.2.7 HSS TxPort BIST Request Register              |      |

|    | 5.2.8 HSS TxPort BIST Error Register                |      |

|    | 5.2.9 HSS TxPort Reset BIST Error Register          |      |

|    | 5.2.10 HSS RxPort Attachment Enable Register        | . 83 |

|    | 5.2.11 HSS RxPort Byte Alignment Done Register      |      |

|    | 5.2.12 HSS RxPort K28.5 Spacing OK Register         |      |

|    | 5.2.13 HSS RxPort LU Deskew Register                |      |

|    | 5.2.14 HSS RxPort Data Mode Register                |      |

|    | 5.2.15 HSS RxPort Data Valid Register               |      |

|    | 5.2.16 HSS RxPort Signal Lost Register              |      |

|    | 5.2.17 HSS RxPort Invalid K Character Register      |      |

|    | 5.2.18 HSS RxPort Synchronization Lost Register     |      |

|    | 5.2.19 HSS RxPort Code Violation Register           |      |

|    | 5.2.20 HSS RxPort BIST Request Register             |      |

|    | 5.2.21 HSS RxPort BIST Error Register               |      |

|    | 5.2.22 HSS RxPort Reset BIST Error Register         |      |

|    | 5.2.23 HSS RxPort BIST Wrap Register                |      |

|    | 5.2.24 HSS TxSpex Bus Driver Enable Register        |      |

|    | 5.2.25 HSS TxSpex Bus Attachment Enable Register    | 92   |

|    | 5.2.26 HSS TxSpex Bus Parameters Register           |      |

|    | 5.2.27 HSS TxSpex Bus BIST Request Register         |      |

|    | 5.2.28 HSS TxSpex Bus BIST Error Register           | . 96 |

|    | 5.2.29 HSS TxSpex Bus Reset BIST Error Register     | . 97 |

|    | 5.2.30 HSS RxSpex Bus Attachment Enable Register    | . 98 |

|    | 5.2.31 HSS RxSpex Bus Byte Alignment Done Register  | . 99 |

|    | 5.2.32 HSS RxSpex Bus K28.5 Spacing OK Register     | 100  |

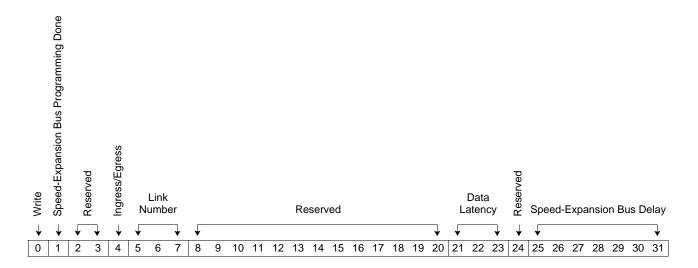

|    | 5.2.33 HSS RxSpex Bus Latency Programming Register  | 101  |

|    | 5.2.34 HSS RxSpex Bus Data Mode Register            |      |

|    | 5.2.35 HSS RxSpex Bus Signal Lost Register          |      |

|    | 5.2.36 HSS RxSpex Bus Invalid K Character Register  |      |

|    | 5.2.37 HSS RxSpex Bus Synchronization Lost Register |      |

|    | 5.2.38 HSS RxSpex Bus Code Violation Register       |      |

|    | 5.2.39 HSS RxSpex BIST Request Register             |      |

|    |                                                     |      |

### Preliminary

| 5.2.40 HSS RxSpex Bus BIST Error Register                                 | 109 |

|---------------------------------------------------------------------------|-----|

| 5.2.41 HSS RxSpex Bus Reset BIST Error Register                           | 110 |

| 5.2.42 HSS RxSpex BIST Wrap Register                                      |     |

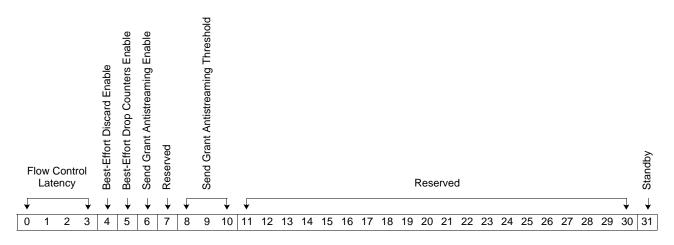

| 5.3 Functional Registers                                                  | 112 |

| 5.3.1 Configuration 0 Register                                            | 112 |

| 5.3.2 Configuration 1 Register                                            | 114 |

| 5.3.3 Threshold Access Register                                           | 116 |

| 5.3.4 Credit Table Access Register                                        | 118 |

| 5.3.5 Best-Effort Resources Access Register                               |     |

| 5.3.6 Status Register                                                     | 122 |

| 5.3.7 Interrupt Mask Register                                             | 124 |

| 5.3.8 Output Queue Enable Register                                        | 126 |

| 5.3.9 Input Controller Enable Register                                    | 126 |

| 5.3.10 Bitmap Filter Register                                             | 127 |

| 5.3.11 Color Detection Disable Register                                   |     |

| 5.3.12 Expected Color Received Register                                   | 128 |

| 5.3.13 Color Command Register                                             | 129 |

| 5.3.14 Bitmap Mapping Register                                            |     |

| 5.3.15 Output Queue Status Registers                                      |     |

| 5.3.16 Best-Effort Discard Alarm Register                                 | 133 |

| 5.3.17 Send Grant Violation Register                                      |     |

| 5.3.18 Header Parity Error Register                                       | 134 |

| 5.3.19 Flow Control Violation Register                                    | 134 |

| 5.3.20 Side Communication Channel Input Reporting Registers               | 135 |

| 5.4 Control Packet and Service Packet Transmission Registers              | 136 |

| 5.4.1 Egress Control Packet and Service Packet Payload Registers          | 136 |

| 5.4.2 Egress Control Packet and Service Packet Destination Register       | 137 |

| 5.5 Control Packet and Service Packet Reception Registers                 | 138 |

| 5.5.1 Ingress Control Packet or Command Service Packet Received Registers | 138 |

| 5.5.2 Ingress Control Packet and Service Packet Source Register           |     |

| 5.5.3 Ingress Control Packet and Service Packet Payload Registers         | 140 |

| 5.5.4 Ingress Event Service Packet Received Registers                     | 141 |

| 5.5.5 Ingress Event Service Packet Mask Registers                         | 141 |

| 5.6 Debug Facilities Registers                                            | 142 |

| 5.6.1 Debug Bus Select Register                                           | 142 |

| 5.6.2 Send Grant Disable Register                                         | 144 |

| 5.6.3 Force Send Grant Register                                           | 144 |

| 5.6.4 Send Grant Status Registers                                         | 145 |

| 5.6.5 Subswitch Element Occupancy (1) Registers                           | 146 |

| 5.6.6 Subswitch Element Occupancy (2) Registers                           | 147 |

| 5.6.7 Look-Up Table Registers                                             |     |

| 5.6.8 Blue Idle Packet or Data Packet Received Register                   | 149 |

| 5.6.9 Red Idle Packet or Data Packet Received Register                    | 149 |

| 5.6.10 Miscellaneous Debug Register                                       |     |

| 5.6.11 Force Packet Capture Ports Register                                |     |

| 5.6.12 Force Packet Capture Header Register                               |     |

| 5.6.13 Force Packet Capture Mask Register                                 |     |

| 5.6.14 Packet Captured Registers                                          |     |

| 5.6.15 HSS Debug Control Register                                         |     |

| 5.6.16 HSS Force Error Register                                           | 156 |

### Packet Routing Switch

| 6. Reset, Initialization, and Operation                    | 157   |

|------------------------------------------------------------|-------|

| 6.1 Reset Sequence                                         | . 157 |

| 6.2 Speed-Expansion Bus Initialization                     |       |

| 6.2.1 Synchronizing the Speed-Expansion Bus Links          |       |

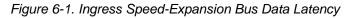

| 6.2.2 Setting the Speed-Expansion Bus Data Latency         |       |

| 6.2.2.1 The Source of Data Latency                         |       |

| 6.2.2.2 Setting Data Latency                               |       |

| 6.3 Port Initialization and Operation                      |       |

| 6.3.1 Initializing HSS Ports                               |       |

| 6.3.2 Deactivating HSS Ports                               |       |

| 6.4 Logic BIST Execution Sequence                          |       |

| 6.5 Memory BIST Execution Sequence                         | . 165 |

| 7. I/O Definitions and I/O Timing                          | 167   |

| 7.1 I/O Definitions                                        |       |

| 7.2 I/O Timing                                             |       |

| 7.2.1 HSS Signals                                          |       |

| 7.2.2 SHI Signals                                          | . 170 |

| 7.2.3 Syncln/SyncOut Signals                               | . 172 |

| 7.2.4 Flush Delay Measurement                              | . 172 |

| 8. Data and Flow Control Latencies                         | 173   |

| 8.1 Data Packet Transmission                               |       |

| 8.2 Send Grant Off to Egress Idle Packet                   |       |

| 8.3 Ingress Data Packet Received to Output Queue Grant Off |       |

| 8.4 Ingress Data Packet Received to Memory Grant Off       |       |

| 8.5 Ingress Data Packet Received to Melliory Grant Off     |       |

| 8.6 Subport Flow Control Latency                           |       |

| 8.6 Subport Flow Control Latency                           | . 170 |

| 9. Pin Information                                         | 177   |

| 10. Electrical Characteristics                             | 187   |

| 10.1 General Information                                   | . 187 |

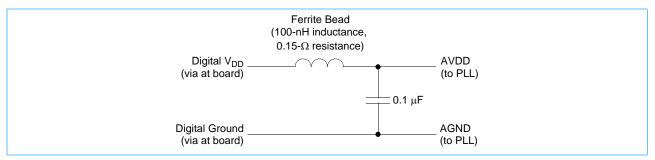

| 10.2 Internal PLL AVDD and AGND Pins                       | . 190 |

| 10.3 InfiniBand Compatibility                              |       |

| 11. Mechanical Information                                 | 191   |

|                                                            | -     |

| 12. Glossary                                               | 193   |

| 13. Related Documents                                      | 199   |

| Revision Log                                               | 201   |

Preliminary

# List of Figures

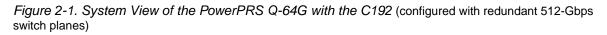

| Figure 2-1. System View of the PowerPRS Q-64G with the C192 | 15  |

|-------------------------------------------------------------|-----|

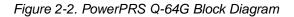

| Figure 2-2. PowerPRS Q-64G Block Diagram                    | 16  |

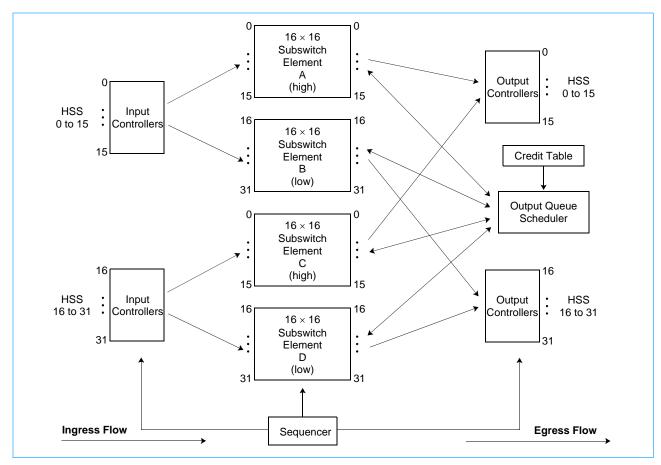

| Figure 2-3. 16 × 16 Subswitch Element Block Diagram         | 17  |

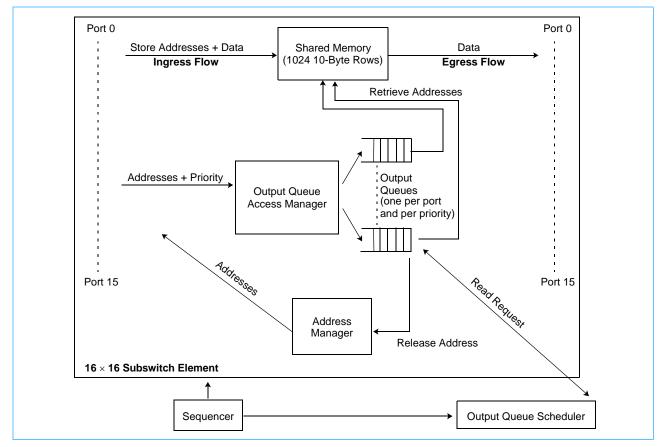

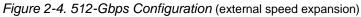

| Figure 2-4. 512-Gbps Configuration                          | 22  |

| Figure 2-5. 256-Gbps Configuration                          | 23  |

| Figure 3-1. Packet Format for a 16-Gbps Port                | 28  |

| Figure 3-2. Ingress Idle Packet Format                      | 31  |

| Figure 3-3. Ingress Data Packet and Control Packet Format   |     |

| Figure 3-4. Ingress Service Packet Format                   |     |

| Figure 3-5. Egress Idle Packet Format                       |     |

| Figure 3-6. Egress Data Packet and Control Packet Format    | 44  |

| Figure 3-7. Egress Service Packet Format                    | 46  |

| Figure 3-8. Best-Effort Discard Counters and Thresholds     | 51  |

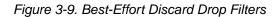

| Figure 3-9. Best-Effort Discard Drop Filters                | 52  |

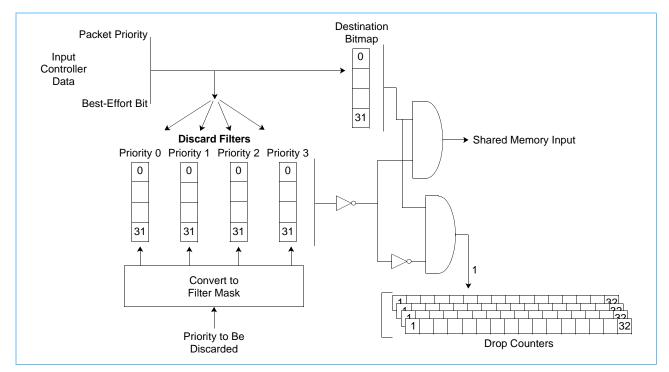

| Figure 3-10. Switchover Support Implementation              | 61  |

| Figure 6-1. Ingress Speed-Expansion Bus Data Latency        | 159 |

| Figure 6-2. Egress Speed-Expansion Bus Data Latency         | 160 |

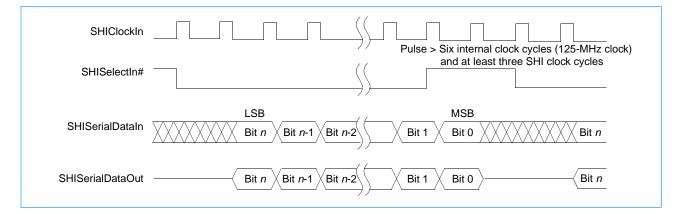

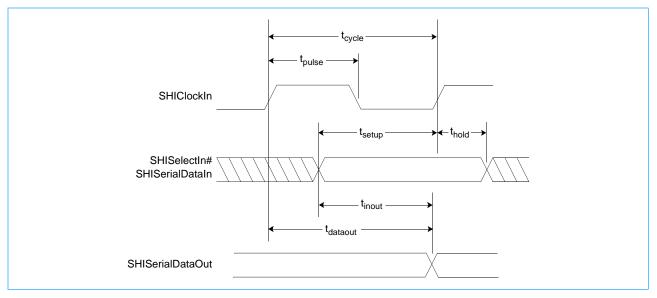

| Figure 7-1. SHI Signal Timing Diagram                       | 170 |

| Figure 7-2. SHI Signal-to-Clock Timing Diagram              | 171 |

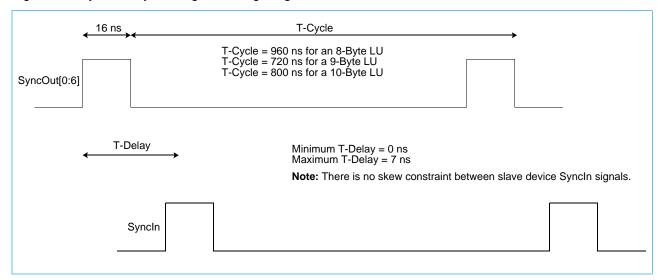

| Figure 7-3. SyncOut/SyncIn Signal Timing Diagram            | 172 |

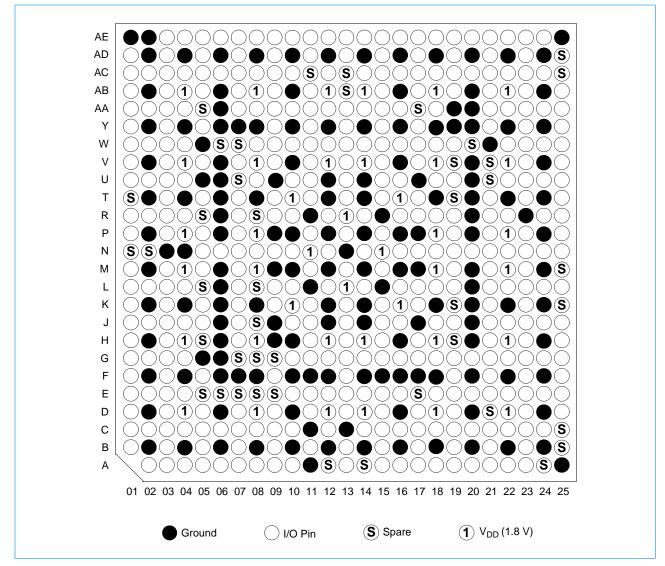

| Figure 9-1. Pinout                                          | 177 |

| Figure 10-1. Power Sequencing                               |     |

| Figure 10-2. Internal PLL AVDD and AGND Signals             |     |

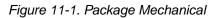

| Figure 11-1. Package Mechanical                             | 191 |

Preliminary

# List of Tables

| Table 2-1. Multiple-Device Configuration Summary                                                 | 21    |

|--------------------------------------------------------------------------------------------------|-------|

| Table 3-1. Ingress Idle Packet, Byte H0                                                          | 31    |

| Table 3-2. Ingress Idle Packet, Byte H0 Field Descriptions                                       | 31    |

| Table 3-3. Ingress Idle Packet, Bytes H1, H2, SCC, and FC                                        | 32    |

| Table 3-4. Ingress Data Packet and Control Packet, Byte H0                                       | 33    |

| Table 3-5. Ingress Data Packet and Control Packet, Byte H0 Field Descriptions                    | 34    |

| Table 3-6. Ingress Data Packet and Control Packet, Byte H1 in the 256-Gbps Configuration         | 35    |

| Table 3-7. Ingress Data Packet and Control Packet, Bytes H1 and H2 in the 512-Gbps Configuration | 35    |

| Table 3-8. Ingress Service Packet, Byte H0                                                       | 36    |

| Table 3-9. Ingress Service Packet, Byte H0 Field Descriptions                                    | 36    |

| Table 3-10. Egress Idle Packet, Byte H0                                                          | 39    |

| Table 3-11. Egress Idle Packet, Byte H0 Field Descriptions                                       | 40    |

| Table 3-12. Egress Idle Packet, Byte H1 on the High Channel in the 256-Gbps Configuration        | 41    |

| Table 3-13. Egress Idle Packet, Byte H1 on the High Channel in the 512-Gbps Configuration        | 41    |

| Table 3-14. Egress Idle Packet, Byte H2 on the High Channel in the 512-Gbps Configuration        | 42    |

| Table 3-15. Egress Idle Packet, Byte H1 on the Low Channel in the 256-Gbps Configuration         | 42    |

| Table 3-16. Egress Idle Packet, Bytes H1 and H2 on the Low Channel in the 512-Gbps Configuration | 43    |

| Table 3-17. Egress Idle Packet, SCC Byte                                                         | 43    |

| Table 3-18. Egress Idle Packet, FC Byte                                                          | 43    |

| Table 3-19. Egress Idle Packet, FC Byte Field Descriptions                                       | 44    |

| Table 3-20. Egress Data Packet and Control Packet, H0 Byte                                       | 45    |

| Table 3-21. Egress Data Packet and Control Packet, Byte H0 Field Descriptions                    | 45    |

| Table 3-22. Egress Service Packet, Byte H0                                                       | 46    |

| Table 3-23. Egress Service Packet, Byte H0 Field Descriptions                                    | 46    |

| Table 3-24. Best-Effort Discard Counters                                                         | 50    |

| Table 3-25. Flow Control Information Summary                                                     | 54    |

| Table 3-26. Packet Transmission Time                                                             | 56    |

| Table 3-27. Example of Byte Reordering Using the Look-Up Table                                   | 57    |

| Table 3-28. Registers and Bits Used for Switchover Support                                       | 58    |

| Table 3-29. Ingress Data Packet Protection Field                                                 | 58    |

| Table 5-1. Register Map                                                                          | 65    |

| Table 5-2. DebugBusOut[0:15] Pin Information by Debug Bus Select Field Value                     | . 142 |

| Table 6-1. Required Data Latency                                                                 | . 160 |

| Table 7-1. Signal Definitions                                                                    | . 167 |

| Table 7-2. Power Signals                                                                         | . 169 |

| Table 7-3. Test Signals                                                                          | . 169 |

| Table 7-4. HSS Interface Skew                                                                    | . 170 |

### **Packet Routing Switch**

# Table 7-6. Delay between ScanIn[2] and ScanOut[2] .....172 Table 8-1. Data Packet Transmission 173 Table 8-2. Send Grant Off to Egress Idle Packet ......174 Table 9-1. Ground, V<sub>DD</sub> and Spare Pin Locations ......178 Table 10-2. Recommended Operating Conditions 188 Table 10-3. Power Dissipation for Master Device 189 Table 10-4. Power Dissipation for Slave Device(s) 189 Table 10-7. PowerPRS Q-64G versus InfiniBand ......190

# 1. General Information

# 1.1 Features

Preliminary

- Nonblocking, self-routing, single-stage switch

- Either 16 or 32 input and output ports

- High performance:

- Throughput of 2 Gbps per port without speed expansion

- Aggregate throughput of up to 64 Gbps for one device

- Speed expansion:

- 16-Gbps logical interface using multiple devices configured for speed expansion

- 256-Gbps aggregate throughput for four devices configured for internal and external speed expansion (16 ports at 16 Gbps)

- 512-Gbps aggregate throughput for eight devices configured for external speed expansion (32 ports at 16 Gbps)

- Other configurations (employing up to seven devices) can be used in specific applications

- Serial data communication of up to 2.5 Gbps, compatible with InfiniBand<sup>™</sup> physical layer standards

- Multicast support without packet duplication in the shared memory

- Configurable number of traffic priorities (from one to four)

- Flow control based on a grant mechanism

- Programmable flow control thresholds

- Subport flow control support

- Support for redundant switch-plane operation, including a scheduled switchover facility that operates without packet loss

- Serial processor interface (serial host interface)

- Packet header of two or three bytes, containing destination bitmap, packet priority, and switch redundancy support information, all protected by a parity bit

- Shared memory comprised of a dynamically shared buffer with a total capacity of:

- Up to 4096 packets of 64, 72, or 80 bytes for eight devices

- Up to 2048 packets of 64, 72, or 80 bytes for four devices

- 8b/10b encoding for link synchronization and supervision

- Reception of control packets destined for the local processor on any input port

- Transmission of control packets from the local processor to any output port

- Detection of link liveness by reception of specific packets

- · Programmable byte shuffling in egress packets

- CMOS 7SF (SA-27E) technology ( $L_{drawn} = 0.18$   $\mu$ m,  $L_{eff} = 0.11 \ \mu$ m): 1.8-V LVCMOS-compatible I/O for low-speed signals

- IEEE<sup>®</sup> Standard 1149.1 boundary scan to facilitate circuit-board testing

- 624-ball IBM HyperBGA™ package

# **1.2 Description**

The IBM PowerPRS<sup>™</sup> Q-64G Packet Routing Switch is one of a family of third-generation switching devices designed for high-performance, nonblocking, fixed-length packet switching. It enables the development of scalable switch fabrics with an aggregate bandwidth of 256 to 512 Gbps.

The PowerPRS Q-64G receives packets on up to 32 input ports and routes them to up to 32 output ports

based on bitmap information contained in the packet header. To accomplish this, each PowerPRS Q-64G contains four  $16 \times 16$  subswitch elements connected internally for port expansion. The physical links between the PowerPRS Q-64G and the attached devices are high-speed serializers/ deserializers (HSSs; formerly Unilinks).

The PowerPRS Q-64G is designed to provide OC-192 attachment. To meet these transmission requirements and provide 16-Gbps throughput per port, multiple PowerPRS Q-64Gs are configured for speed expansion. There are two standard multiple-device configurations:

- 512-Gbps configuration (with eight devices providing 32 input and output ports)

- 256-Gbps configuration (with four devices providing 16 input and output ports)

Synchronization is not required between input ports. However, packets on a given port are always received or transmitted at a fixed rate according to the packet length. Four levels of packet priority provide quality-of-service support. A serial grant mechanism controls ingress and egress data flow.

The PowerPRS Q-64G supports redundant switch-plane operation. It includes color-coded scheduled switchover that operates without packet loss. Scheduled switchover is a system-level function that requires hardware and software interaction. The PowerPRS Q-64G performs the hardware assist for this function.

# 1.3 Ordering Information

| Part Number  | Description               | Single-Device Throughput | Aggregate Throughput                                                             |

|--------------|---------------------------|--------------------------|----------------------------------------------------------------------------------|

| IBM3247P4213 | IBM Packet Routing Switch | 64 Gbps                  | For OC-192 attachment:<br>256 Gbps (four devices) or<br>512 Gbps (eight devices) |

# **1.4 Conventions and Notation**

Throughout this document, standard IBM notation is used, meaning that bits and bytes are numbered in ascending order from left to right. For a four-byte word, bit 0 is the most significant bit (MSB) and bit 31 is the least significant bit (LSB).

Notation for bit encoding is as follows:

- Hexadecimal values are preceded by an x and enclosed in single quotation marks. For example: x'0A00'.

- Binary values in sentences appear in single quotation marks. For example: '1010'.

Differential pairs are designated by an \_P for the positive signal and an \_N for the negative signal at the end of the signal name. For example: PortDataIn[0]\_P and PortDataIn[0]\_N.

Nondifferential signals that are active low are designated by a # symbol at the end of the signal name. For example: InterruptOut#.

# 2. Architecture

# 2.1 System Application

The IBM PowerPRS Q-64G Packet Routing Switch enables the construction of nonblocking scalable switch fabrics through repeated instances of the same switch element. It is designed for a wide variety of applications, including campus, wide-area network (WAN) edge, access, and backbone switches. When connected to the IBM PowerPRS C192 Common Switch Interface, the Q-64G provides a complete redundant switch fabric for the attachment of OC-48 and OC-192 protocol engines. An example of this architecture is shown in *Figure 2-1*.

# 2.2 Internal Structure

The internal structure of the PowerPRS Q-64G is shown in *Figure 2-2,* which depicts a single device operating without speed expansion. *Figure 2-3* on page 17 shows the structure of a subswitch element.

Figure 2-3. 16 × 16 Subswitch Element Block Diagram

The main components of the PowerPRS Q-64G are:

- Thirty-two input controllers

- Thirty-two output controllers

- Four self-routing subswitch elements, each housing a shared memory bank and a control section comprised of:

- One address manager

- One output queue access manager

- Sixteen output queues (one per output port)

- Device control section, which includes a:

- Sequencer

- Output queue scheduler

- Credit table

- High-speed SerDes (HSS) interface between the PowerPRS Q-64G and attached devices

## 2.2.1 HSS Interface

The physical links between the PowerPRS Q-64G and attached devices are high-speed serializers/ deserializers. The HSS physical interface minimizes the number of pins. There is one HSS per PowerPRS Q-64G device port, or 32 HSSs per device. Each HSS is comprised of two pairs of differential lines; one

differential pair carries ingress flow and the other differential pair carries egress flow. Each pair of differential lines (that is, each device port) carries two packets and has a total throughput of 2 Gbps. Therefore, each HSS carries two ingress packets and two egress packets at a time. The PowerPRS Q-64G physical interface carries the two ingress or two egress packets in separate streams; one packet is carried on the high channel and one packet is carried on the low channel. See *Section 3.2 Physical Interface and Packet Processing* on page 27 for more information.

## 2.2.2 Shared Memory

Each PowerPRS Q-64G device includes four  $16 \times 16$  self-routing subswitch elements, denoted A, B, C, and D (see *Figure 2-2* on page 16). The four subswitch elements house the shared memory, which stores the packets that the PowerPRS Q-64G has received but has not yet transmitted. The shared memory on each subswitch element consists of 1024 10-byte rows, and has two read ports and two write ports.

Subswitch elements A and B store packets from input ports 0 to 15, and subswitch elements C and D store packets from input ports 16 to 31. For port expansion, each pair of subswitch elements is connected internally; that is, they are connected in parallel, in a single stage, to increase the number of ports without changing the port speed. This provides the  $32 \times 32$ -port device configuration. The *high* subswitch elements (A and C) store packets destined for output ports 0 to 15, and the *low* subswitch elements (B and D) store packets destined for output ports 16 to 31 (see *Figure 2-2* on page 16).

### 2.2.3 Sequencer

The sequencer controls the PowerPRS Q-64G internal data flow by granting shared memory access to the input and output ports. Sequencer operation is based on time-division multiplexing (TDM). The sequencer cycles concurrently among the input and output ports, granting shared memory access to two input ports and two output ports at a time (one from ports 0 to 15 and one from ports 16 to 31) and visiting each port once per cycle. During each shared memory access, one packet is transmitted to or from each of the port's two subswitch elements.

Packets are transmitted and stored in equal lengths called logical units (LUs). The standard PowerPRS Q-64G configurations include either four or eight devices, in which one device is the master and the rest of the devices are slaves. In these configurations, packets are divided into eight LUs (one master LU and seven slave LUs) and distributed over all the devices.

During each shared memory access, 8 to 10 bytes of data are processed (read or written) per subswitch element, depending on packet length. In the standard multiple-device configurations, processing an entire LU requires one shared memory access. The sequencer cycle equals the time required to process the data associated with one shared memory access. All sequencer cycles are equal in length.

The sequencer ensures that packets on a given port are always processed at a fixed interval according to their LU length; therefore, no synchronization is required between input ports. The slave device sequencers are synchronized to the master device sequencer so that all the LUs for a particular port (or packet) are processed at the same time. See Section 2.3.3 Master/Slave Synchronization with Multiple Devices on page 21 for more information.

## 2.2.4 Address Managers

Each subswitch element has an address manager that tracks the available shared memory addresses on the subswitch element and provides new store addresses to the input controllers. When an address manager provides a store address to an input controller, it removes that address from the available shared memory

address pool. After the packet is transmitted, the output queue returns the address to the address manager, which returns it to the available address pool. For multicast packets, one store address is sent to multiple output queues. The address manager tracks the number of output queues holding each store address and, when the count reaches zero, returns the address to the available shared memory address pool.

# 2.2.5 Input Controllers

The PowerPRS Q-64G has 32 input controllers, one input controller per port. Each input controller processes two packets at a time, one packet on the high channel and one packet on the low channel. When a packet arrives, the input controller of the master device extracts the header information (including packet priority and destination) from the master LU. It checks the master LU header integrity using a parity bit on the header bytes. If the packet is valid, the input controller stores it in the shared memory when access is granted by the sequencer.

An input controller stores a packet in the shared memory of one of its two subswitch elements, depending on the packet's destination. Packets stored in subswitch elements A and C are destined for output ports 0 to 15, and packets stored in subswitch elements B and D are destined for output ports 16 to 31 (see *Figure 2-2* on page 16). The input controller uses the store address provided by the address manager of the subswitch element. The input controller also forwards the shared memory address, packet priority, and packet destination to the output queue access manager. Packets arrive with a priority of 0 to 3, with 0 being the highest priority. Note that multicast packets have only one priority for all destinations.

In multiple-device configurations, the input controller on the master device forwards information such as the shared memory store address and subswitch element ID to the input controllers on the slave devices.

## 2.2.6 Output Queue Access Managers

Each subswitch element has an output queue access manager that receives the packet store address, priority, and destination from the input controllers and forwards the information to the output queues for the subswitch element. Each output queue access manager also maintains the counters that the PowerPRS Q-64G uses to control ingress traffic flow. For each output queue, a counter tracks the total number of packets enqueued for that output, regardless of priority. Another counter tracks the total number of packets stored in the shared memory, regardless of output or priority.

## 2.2.7 Output Queues

The output queues contain the shared memory addresses of packets awaiting transmission from the PowerPRS Q-64G. In each of the four subswitch elements, each of the 16 output ports has one output queue per priority. Each output queue is organized into two address banks: one bank holds addresses written by even ports and the other bank holds addresses written by odd ports. Packet addresses are organized in a first-in-first-out (FIFO) queuing structure in each address bank. Each output queue can store up to 1024 addresses.

A unicast packet address is stored in one output queue, and a multicast packet address is stored in two or more output queues.

#### 2.2.8 Output Queue Scheduler and Credit Table

The output queue scheduler determines which output queue will provide the next egress packet retrieve address and notifies each selected output queue in turn. Each selected output queue then forwards its next retrieve address to the shared memory.

The output queue scheduler selects an output queue using several pieces of information. For each subswitch element output port, the output queues provide an output queue status (that is, output queue empty), one per priority, to the output queue scheduler. The output queue scheduler also receives the send grants that control egress traffic flow to the attached devices. In general, the output queue scheduler selects the highest-priority of the occupied output queues (so that high-priority packets overtake low-priority packets). However, a fixed amount of bandwidth can be assigned to low-priority packets by altering priority scheduling in the credit table (see Section 3.5.3 Credit Table on page 53).

**Note:** As discussed in *Section 2.2.7* on page 19, each output queue contains two address banks (those written by even ports and those written by odd ports). If both address banks are occupied for a single priority, the output queue scheduler toggles between the two banks to select and notify the entire output queue. Packet addresses are processed on a FIFO basis within an address bank.

### 2.2.9 Output Controllers

The PowerPRS Q-64G has 32 output controllers, one output controller per port. Each port transmits two packets at a time, one packet on the high channel and one packet on the low channel. When access is granted by the sequencer, the output controller retrieves the next two packets to be transmitted on a port from the retrieve addresses that the output queue scheduler forwarded to the shared memory. The output controller inserts ingress and subport flow control information (that is, it inserts the grants) into the packet header before forwarding the packets to the physical interface for serialization.

Note that each output controller retrieves packets from two  $16 \times 16$  subswitch elements and merges the traffic to a single output port. Output controllers 0 to 15 transmit from subswitch elements A and C; output controllers 16 to 31 transmit from subswitch elements B and D (see *Figure 2-2* on page 16).

# 2.3 Multiple-Device Configurations

The PowerPRS Q-64G is designed to provide OC-192 attachment. To meet these transmission requirements and provide 16-Gbps throughput per port, multiple PowerPRS Q-64Gs are configured for speed expansion. There are two standard multiple-device configurations:

- 512-Gbps configuration (eight devices that provide 32 input and output ports)

- 256-Gbps configuration (four devices that provide 16 input and output ports)

In both of these multiple-device configurations, one device is the master and the rest of the devices are slaves. The master device performs packet routing and queueing and forwards packet synchronization and shared memory address information to the slave devices. Because the slave devices only store slave LUs and do not perform packet routing or queuing, their control sections are inactive to minimize power consumption.

*Table 2-1* on page 21 presents some of the features, including the shared memory capacity, of the two standard multiple-device configurations. Descriptions of these two configurations follow.

### Table 2-1. Multiple-Device Configuration Summary

| Device Configuration                                                                | Number of<br>Ports | Port Speed<br>(Gbps) | Packet Length<br>(bytes) | LU Size<br>(bytes) | Shared Memory<br>Capacity (packets) |

|-------------------------------------------------------------------------------------|--------------------|----------------------|--------------------------|--------------------|-------------------------------------|

| 512-Gbps configuration<br>(eight devices with external speed expansion)             | 32 × 32            | 16                   | 64, 72, or 80            | 8, 9, or 10        | 4096                                |

| 256-Gbps configuration<br>(four devices with internal and external speed expansion) | 16 × 16            | 16                   | 64, 72, or 80            | 8, 9, or 10        | 2048                                |

# 2.3.1 512-Gbps Configuration

In the 512-Gbps configuration, eight PowerPRS Q-64Gs are configured for external speed expansion (see *Figure 2-4* on page 22). For external speed expansion, multiple devices are connected in parallel and the like-numbered ports on all the devices are grouped. The total number of ports remains the same as on a single device, but the throughput per port equals the throughput per port for a single device times the number of devices. A single PowerPRS Q-64G features 32 ports at 2 Gbps per port; therefore, this configuration provides 32 ports at 16 Gbps per port (for an aggregate throughput of 512 Gbps). In this configuration, the eight devices are assembled on two switch cards.

# 2.3.2 256-Gbps Configuration

In the 256-Gbps configuration, four PowerPRS Q-64Gs are configured for both internal and external speed expansion (see *Figure 2-5* on page 23). For internal speed expansion, two ports within a device are paired. This doubles the port speed but halves the number of ports. Because a single PowerPRS Q-64G features 32 ports at 2 Gbps per port, this configuration provides 16 ports at 16 Gbps per port (for an aggregate throughput of 256 Gbps). In this configuration, the four devices are assembled on one switch card.

## 2.3.3 Master/Slave Synchronization with Multiple Devices

## 2.3.3.1 Sequencers

Each PowerPRS Q-64G contains a sequencer. When multiple devices are configured for external speed expansion, the slave device sequencers must be synchronized to the master device sequencer to ensure that the LUs for a particular port (or packet) are processed at the same time on all the devices. This synchronization is done with the Syncln (slave device input) and SyncOut (master device output) pins. The SyncIn/Out pin mode bit in the *Configuration 1 Register* (page 114) sets the operating mode for these pins.

**Note:** In the 256-Gbps and 512-Gbps configurations, LU (and packet) transmission requires one sequencer cycle.

Figure 2-5. 256-Gbps Configuration (internal and external speed expansion)

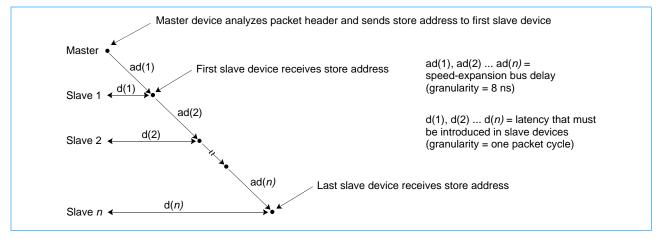

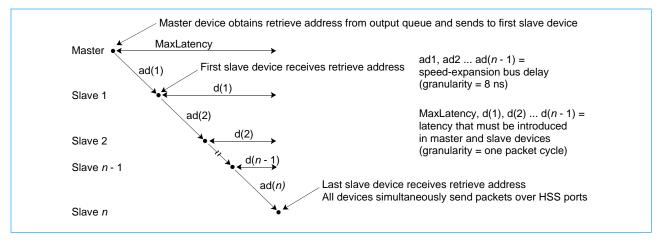

## 2.3.3.2 Shared Memory Addresses